车载移动电视接收的系统方案

移动通信车载电视课程设计报告

移动通信课程设计报告车载电视信道特性的分析目录1车载电视系统简介 (1)1.1模块介绍及原理 (1)1.2传输技术 (2)2车载电视的信道模型的研究 (3)2.1无线通信信道建模技术发展的研究 (3)2.2常用的信道模型研究 (4)2.3模型适用范围比较 (7)2.4结论 (7)2.5瑞利信道统计特性分析 (7)2.6 瑞利衰落信道模型 (9)2.7 Clarke模型 (15)2.8 Clarke模型常用仿真方法 (16)2.9仿真实验成果 (19)3高架桥信号传播模型的研究 (23)3.1桥下道路上传播的双径模型 (23)3.2双径传播模型 (26)3. 3桥下道路上传播的多径模型 (27)4感想与总结 (28)参考文献 (29)1车载电视系统简介车载电视系统,是指通过地面电视广播发射站天线发射无线电波,使用者可以在移动中由专业接收设备或电视机收看视频节目的传输形式。

它与传统模拟电视广播相比,最大特点是节目容量更大、画面和音质更清晰、收看更自由,在信号覆盖范围内影像清晰度高、声音好。

车载电视系统主要模块:发射模块和接收模块1.1模块介绍及原理1 发射模块发射模块由传输网络和发射台组成。

各发射台中又有调制器(包含单频网适配器)和发射机,还需要一个同步钟源(一般采用GPS),其主要任务是组成单频网,以便实现复杂地形条件下的地面广播覆盖。

单频网的功能,它就是在数字码流中插入一个 MIP包以传输同步信号,各节点的调制器将信号进行抗干扰处理后调制成IF信号,再由发射机将IF信号变频为RF信号后进行功率放大,最后才通过天线向空中发射。

因此,要想有高覆盖率的信号,天线的带宽是决定性因素。

此部分主要用到以下设备和软件:单频网规划和设计,城市覆盖测量,数字发机,调制器,单频网适配器,GPS同步钟源以及发射天线等。

2 接收模块高频头主要负责将射频信号转换成解调器可以接收的中频或基带调制信号;解调器收到这些信号后进行解码,输出为包含广播数据的码流;之后解复用把广播数据从其它码流信号中分离出来,并根据控制信息,从分离出来的信号中选择对应于本机的音、视频数据进行下载或实时播放;再对其它的多媒体信息进行处理后最终在车载电视上显示出来。

CMMB车载数字电视系统应用解决方案

CMMB车载数字电视系统应用解决方案作者:李倩来源:《无线互联科技》2014年第06期摘要:随着科学技术的发展和进步,多媒体技术在各个领域被广泛的应用。

中国移动多媒体广播是我国拥有自主产权的数字移动广播技术,它是我国多媒体技术中比较重要的一部分。

中国移动多媒体广播简称CMMB,目前,这种技术已经向汽车领域发展和应用,汽车与CMMB的合作使用已经成为了经济的一个重要增长点。

本文通过对CMMB车载数字电视系统进行研究,分析系统的优缺点,进而实现CMMB车载数字电视车载系统的完善和进步。

关键词:移动多媒体广播;移动电视;解决方案;车载数字电视;发展方向CMMB是我国拥有自主创新和知识产权的一项移动多媒体广播电视技术,已经在我国大面积地区进行普及和应用,建成了全球最大的多媒体广播电视网络。

近些年来,CMMB技术被广泛应用在汽车产业中,最典型的就是CMMB车载数字电视系统的应用。

随着时代的发展和科技的进步,对CMMB车载数字电视系统应用进行研究和提出解决方案是非常必要的。

1CMMB车载数字电视方案中国移动多媒体广播车载数字电视主要分为前装、准前装、后装这三个方案。

CMMB的前装方案是在车出厂前进行CMMB车载接收终端的预先安装和调整。

车载数字电视系统的设计和安装必须依照车的具体型号进行研发和生产,对产品的可靠性有非常高的要求[1]。

因此,在车载数字电视系统的研发中必须加大各个环节的检验和投入。

CMMB车载准前装方案是针对于应经生产的车进行方案提出的,是根据市场的需要将研究好的CMMB车载数字电视系统安装到整个车中,然后再进行销售。

CMMB车载后装方案是针对于已经销售出去的车辆提出的。

很多车辆在出厂时都没有CMMB这个功能,车主可以根据自己的需要进行安装,以实现CMMB的覆盖。

CMMB车载后装方案也是本文中重点讨论的问题。

2CMMB车载后装系统的解决方案目前,市面上大多数的CMMB终端都是针对后装产品的。

安装CMMB车载数字电视系统可以以车载空瓶或者头枕LED为载体,在行车过程中可以进行导航服务,休息时观看电影。

张海涛调研CMMB移动多媒体广播电视工作

用 , 而且 将 从 已 开 始 广 泛 应 用 的 后 装 市 场 向 汽 车原 厂 标 配 的前 装 市 场 发 展 。要

口 口 圈

CBg¥ VS  ̄

视

显 ] 兰

J

导航功能

茎 而M 协点 篙 的一 切 。 CB 人 第是 M

,

控 器

‘

面向移动接收终端提供 参考文献 :

} 完工检查[

. . . . . . . . . . .

1l _

技术 、 经营 、 管 理的复合 型人才 , 懂 懂 塑造 一 支 能 打 硬 仗 、 打 胜 仗 的 干 部 善

厂

’

. . . . . .

V

. . . . .

队 伍 。 局 有关 司 局耍 继 续 大 力 支 持 C 总 MMB的 发 展 , 强业 务 指 导 、 体 规 加 整

医蕊r— j V M B电视 安装C 盒j — ] — M

!

机制

,

建立 符合文化体 制改革要求 的现代 文化企业 制度 , 立适应 C 建 MMB

接电调试 . 接收信号测试 , 原车音响 系统捌试

发 展 的 企 业 精 神 和 企 业 文 化 。要 加 强 业 务 学 习 和 作 风 建 设 , 养 懂 宣 传 、 培 懂

择 加装视频转换解码 器 ■

中控无A 输入, V 需选

+

l 屏 I 成 线 电 线,控, 做 I完 布 (源 遥 1

’

1天 视 线. 频转接线等) } v

用户群体。 三要加强内 部管理, 加强队伍建设。 要完善规章制度, 格规范 严

要 求 , 强 安 全 播 出管 理 、 务 基 建 管 理 、 员 队 伍 管 理 等 , 善 激 励 惩 罚 加 财 人 完

法国迪康助力英诺科技成功推出日标车载数字电视方案

系统 的 PT输入 输 出为两路模拟 加一 P 路D V输 出,可通过 D V输 出接 1 3直连非

编 系 统 进 行 采 集 。采 用 铝 制 保 护 箱 收 取 后 为普 通 箱包 大 小 .仅 重 1k , 合 5g 适 制编小 组携 带运输 。适用 于现场 活动 ,

了中国广播 业者的要求 : 技术领先 、前

规 划 和 维 护 优 化 日益 增 加 的 市 场 需 求

验。他们独有 的专利 技术、高性价 比的 芯片 以及完善 的开发 工具 ,成 为我们不 断 向市 场推 出高 性能方 案的可 靠保 障。 在车载数字 电视领域 .迪 康的优 势非常

明显 。 因 此 ,我 们 希 望 通 过 与 这样 的 顶 尖 公 司 保 持 紧密 合 作 ,发 挥 各 自 的 技 术

演播室 H - 5 S 50

D t i o发 布 一 款 新 型 便 携 式 移 动 aa d ve 演 播 室 H 一 5 , 这 是 一 款 基 于 EP节 S 50 F

专长 .共 同推动这一市场 的繁荣。 ”

此 次英 诺 科技 采 用 的 DB 0 6 是 一 I 9M 8

系 统 测 量 参 数 :支 持 R S、R — S I S

接 收芯 片 DB 0 6 I8 9M成 功应 用 于 由英诺 科技有 限公 司开发的首款 日标车载数字

电视 方 案 中 。新 方 案 已于 近 日实 现 量 产 。 英 诺 科 技 有 限 公 司 总 经 理 吴 科 雷 先 生 说 道 : 迪 康 公 司 在 解 决 移 动 数 字 电 “ 视 接 收 中 的各 种 问题 方 面 拥 有 丰 富 的 经

一

H -50具 有 四路 的输 入 .可外 接 S 5 路 D lV A输入 ,适用于教育和会议 V/ G

车载移动电视CMMB系统概述

超强稳定性

生产上X光全测

Company Logo

XRX1184-50AV1A1性能特色

性能特色之一:超高灵敏度

超高 灵敏度

QPSK1/2LCEDPC闭 合输入电平≤

-101.2dBm

与市面上同类产品相比,灵敏度均高出4-5dBm

Company Logo

XRX1184-50AV1A1性能特色

性能特色之一:兼容多种卡式

您可以享受免费维修 服务

客户在使用我司模块过程中,如有质量或技术问题, 可即时联系我司,我司将派专人为您解决!

Company Logo

Company Logo

售后与质量保证

自产品售出之日起 出现问题 您的权益

15天内

出现国家三包所规定的性能故障 模块外观及脚位无损坏,无上锡的, 经由厂商检测确认故障确实。

您可选择退换货服务 或者我司派专人上门 维修

超过15天并在一年 保修期之内

出现国家三包所规定的性能故障,经由厂商 指定或特约维修点确认故障确实。

SMS1184

SMS1184提供了最好的 移动室内接收性能、高 灵敏度以及超强稳定性。 通过集成一个U波段 的调谐器和一个高性能 的解调器,SMS1184使 得终端客户可以设计最 小的封装,并实现大卡 升级以最低成本和最短 时间进入市场。

Company Logo

模块原理结构图二

后端

后端采用

TCC7920S芯片,使 模块拥有快捷强大 的解码功能。 使用CA芯片贴 片,保证使用的稳 定性大大降低客户 成本

Company Logo

新趋势--CMMB车载GPS功能一体化

车载GPS在如今不仅是单纯的导航工具,或者简单的 生活伴侣,多媒体播放的发展让GPS成为便捷的车载 娱乐终端; CMMB便是这样一款有强大视频播放功能的模块,用 户只需在车载内配上 XRX1184-50AV1A1移动电视播 放功能模块,即可让车主在寂寞的驾驶室里有了新的 乐趣。

现阶段CMMB信号的地面覆盖与接收

j C MMB被称为是一场技术创新引发的新媒体运动,由于它涵盖终端十分广泛的广播系统,满足了移动人群收听收看广播电视节目和接收信息的需求,是广播电视的补充和延伸,所以备受用户的广泛关注,业务的需求量急剧增加,推动了移动数字多媒体广播加速发展。

当前CMMB发展的主要任务为构建全国统一标准的传输覆盖网络、建立统一的条件接收和运营支撑体系、建立符合现代企业制度的合格的市场运营主体。

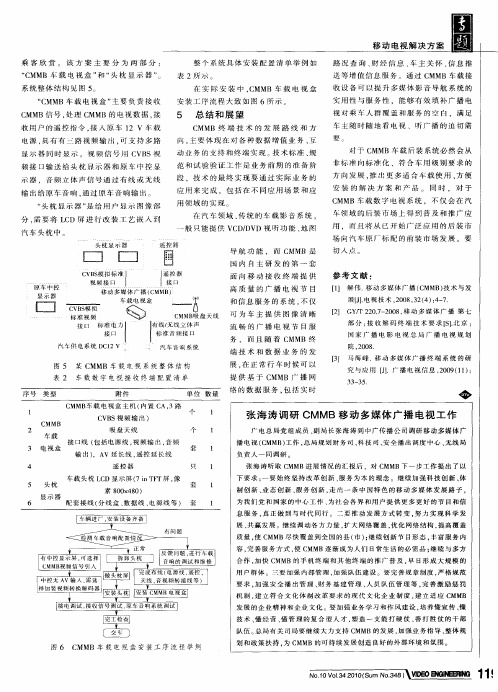

CMMB的技术路线(见图1)根据移动多媒体广播电视系统的技术体制、总体架构及体系结构,CMMB的技术路线为:现阶段CMMB信号的地面覆盖与接收◎江苏省宿迁市广电总台苗瑾周立梅杨振▲图1CMMB的技术路线图2CMMB 系统的组网方案0http://www.s at-chi http://blog.s i /wscmb6|6技术应用欢迎投稿:@2009年第19期(1)采用卫星和地面网络相结合的方式实现“天地一体”协同覆盖,信道传输采用ST iMi 技术。

(2)全国节目通过S 波段卫星对全国实现覆盖,卫星遮挡地区可采取地面同频增补方式,在城市人口密集区域采用U 波段增补。

(3)地方节目采用U 波段地面网络实现覆盖。

(4)电视业务视频压缩编码采用AVS 、H.264/AV C ,伴音压缩编码采用MPEG-4HE AAC ;广播业务音频压缩编码采用DRA 。

(5)数据广播采用可扩展的多协议封装复用传输,支持流模式、文件模式传输。

(6)加密授权系统对音视频流和数据广播流采用ISMACryp 进行加扰,系统前端支持同密,终端采用多密,系统支持单向、双向和基于电子钱包的授权管理方式。

(7)运营支撑系统原则上采用两级架构体系,对内容统一加密,统一管理,支持公共服务、基本服务和扩展服务,实现各类终端用户的合法注册。

CM MB U 波段地面覆盖网络现阶段,由于种种原因,CMMB 在实际执行中修改了原设计方案采用,将S 波段卫星覆盖网络改为主要采用UHF 在地面广播,目前全国各城市CMMB 均采用接收鑫诺卫星下行信号进行UHF 频率地面广播。

DTMB车载数字电视终端与实现

线接收的广播信号通过内部增益等电路变 立体声 FM射频输出电路,用户可选择启动 图2 系统硬件原理框图

换,输出 I F 模拟信号,经外围 A/ D变换电 该功能,通过车载FM收音机接收电视伴音。

路转换为中频数字信号,送入信道解调芯

LCD驱动电路中采用了芯片 MST7 2 0 ,

片。

它内置有 MCU、TCON、Sca l i n g Engi ne、

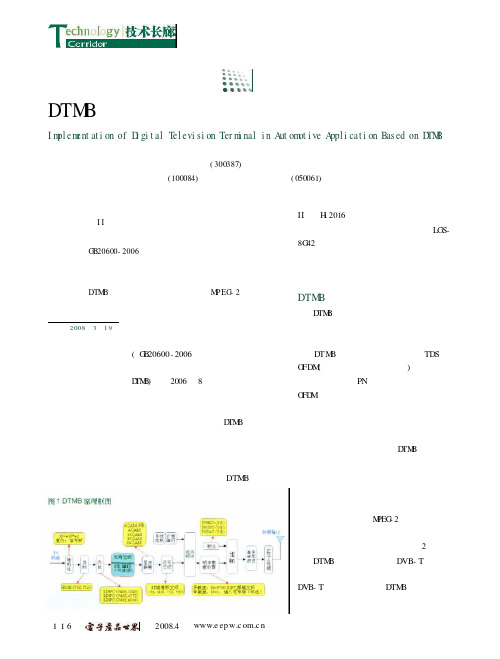

海尔集成电路设计有限公司开发的“爱国者 II 号”Hi 2016 解码芯片,信源解调部分使用 了北京凌讯华业科技有限公司研制的 LGS8G42解调芯片。该方案具有很强的适用性和 很高的性价比,相信会对加快中国数字电视 产业的发展起到很好的推动作用。

关键词:DTMB;车载数字电视;调制解调;MP EG- 2 解码

2音视频解码,同时负责控制上层应用软件。 台之上的五个软件层通过编程接口逐级调

面板操作与红外遥控采用了液晶驱动芯

支持 DTMB标准,适用于户内、户外、固定 片主控的方式。MST720 接收的红外信号分

及移动接收的电视终端,是适用于车载电视 为两类,一类是对LCD的控制信号,另一类

的理想芯片。LGS- 8G42 芯片接收数字 IF 信 是对Hi 2016的控制信号。当红外信号为后者 号,然后将其转换成基带信号,经过必要的 时,则采用 MST720 的 GPIO端口进行模拟,

DTMB是一种具有我国自主知识产权的 地面数字电视传输标准。根据地面数字多媒 体电视广播的服务需求、传输条件和信道特 征,DTMB 传输系统采用了创新的 TDS - OFDM( 时域同步正交频分复用) 调制方式。 使用特殊设计的 PN序列作为同步信号填充 OFDM保护间隔,实现了快速稳健的同步和 高效的信道估计,提高了频谱效率。在抗多 信道噪声、多径、多普勒衰落、时钟恢复、传 输效率等方面优于其它地面数字电视传输国 际标准,具备良好的性能。DTMB高度灵活

车载天线方案

车载天线方案车载天线是指安装在汽车上用于接收无线信号的天线。

随着车载设备的普及和无线通信技术的快速发展,车载天线方案在汽车行业中得到了广泛应用。

本文将介绍几种常见的车载天线方案,包括GPS定位天线、车载蜂窝网络天线和车载电视天线。

1. GPS定位天线方案随着GPS定位技术的广泛应用,车载GPS定位天线成为车辆导航系统中不可或缺的组成部分。

车载GPS定位天线一般安装在汽车的车顶或后视镜上,通过接收卫星信号获取车辆的准确位置信息。

目前,常见的车载GPS定位天线方案包括陶瓷天线和天线模块两种。

陶瓷天线是一种小型化、高灵敏、易安装的天线,常用于车载GPS定位系统。

它具有较高的天线增益和较低的失真率,能够提供准确的定位信息。

另外,陶瓷天线还具备抗干扰能力强、耐温性好等优点,适用于各类车辆环境。

天线模块是一种集成了GPS定位功能的天线系统,它可以提供更为便利的安装和使用体验。

天线模块一般由GPS天线和定位芯片组成,通过与车载设备进行连接,实现定位功能。

天线模块具有较高的灵敏度和稳定性,能够在复杂的道路环境中提供可靠的定位服务。

2. 车载蜂窝网络天线方案随着移动通信技术的快速发展,车载蜂窝网络天线成为车辆通信系统中的重要组成部分。

车载蜂窝网络天线主要用于接收和发送移动网络信号,实现车辆与外部通信的无缝连接。

常见的车载蜂窝网络天线方案包括4G 天线和5G天线。

4G天线是目前车载通信系统中最为常见的天线方案之一。

它可以支持4G网络的高速数据传输和稳定连接,适用于车辆导航、智能车载终端等应用场景。

4G天线一般安装在车辆的车顶或后窗上,通过与车载设备进行连接,实现无线通信功能。

5G天线是未来车载通信系统的发展方向之一。

随着5G技术的成熟和商用,车载5G天线将能够提供更高的数据传输速率和更低的延迟,为车辆行驶过程中的通信需求提供更好的支持。

车载5G天线一般采用多天线阵列技术,能够实现波束赋形,提高通信质量和覆盖范围。

3. 车载电视天线方案车载电视天线是指安装在汽车上接收电视信号的天线。

车载电视

4、对比度

5、可视角度

6、响应时间

7、色彩

车载液晶电视的选择 1、 尺寸的选择

2、 安装方式的选择

3、 电视电压的选择

4、 液晶屏的选择

5、 倒屏的选择

6、 防爆处理

展开编辑本段采用的技术 移动数字信号采用当今世界最先进的数字电视单频网技术(DTTBigital Television Terrestrial Broadcasting,即地面数字电视广播方式系统,是数字电视传播的三种方式之一),通过无线数字信号发射、地面接收方法进行电视节目的传播。凡移动中的交通工具(如轨道交通、水上巴士、汽车等)或渴望所及的人流集散场所(如车站、码头、各类购物、休闲场所等),只要安装相应的接收设备,依靠适宜尺寸的液晶显示屏,均可接收到为移动电视所独家供给的各类数字电视资讯信息。 车载电视是放置在汽车上面观看的电视编辑本段车载液晶电视 如何选择车载液晶电视? 车载液晶电视顾名思义是采用液晶屏(LCD)作为显示载体的车载电视,相对传统的CRT车载电视,车载液晶电视有着非常明显的技术优势,随着2008年LCD屏价格持续走低,目前车载液晶电视已经完全取代传统的CRT车载电视。 车载液晶电视主要具有以下一些突出特点:体积小、重量轻、完全平面、低耗电,无闪烁无失真。选择车载液晶电视先了解一些基本的参数指标。编辑本段车载液晶电视参数指标1、点距

移动接收卫星电视的天线自动跟踪系统分析

移动接收卫星电视的天线自动跟踪系统分析1. 引言1.1 研究背景移动接收卫星电视的天线自动跟踪系统是一种能够实现在移动环境下同步卫星信号的技术装备,具有较高的实用性和市场前景。

在传统的卫星电视接收系统中,天线需要通过人工调整来对准卫星信号源,这种方式存在人工操作复杂、精度低、受环境影响较大等问题。

研究和开发一种自动跟踪系统已成为当前卫星电视领域的重要研究方向。

随着移动通信和卫星通信技术的不断发展,人们对移动接收卫星电视的需求逐渐增加。

无论是行车中观看直播节目,还是露营时享受卫星电视节目,都需要一种方便、高效的天线自动跟踪系统来保证信号的稳定接收。

研究移动接收卫星电视的天线自动跟踪系统具有非常重要的现实意义和应用前景。

通过引入先进的技术手段和算法,实现天线的自动跟踪,并能够在复杂的环境条件下实现稳定的信号接收,将为移动卫星电视系统的发展带来新的机遇和挑战。

1.2 研究目的本文旨在探讨移动接收卫星电视的天线自动跟踪系统的研究目的。

随着卫星通信技术的不断发展,卫星电视成为人们获取信息和娱乐的重要途径之一。

传统固定天线容易受到地形、建筑等外界因素的影响,造成信号接收不稳定。

针对这一问题,研究移动接收卫星电视的天线自动跟踪系统具有重要的意义。

研究目的在于解决移动通信设备对卫星信号稳定性的要求。

移动接收卫星电视的天线自动跟踪系统能够根据实时位置信息,自动调整天线方向,确保信号接收稳定。

研究目的在于提高卫星通信系统的效率和可靠性。

通过自动跟踪系统的引入,可以减少人工干预,提高系统运行效率,降低故障风险,增强系统的可靠性。

本文旨在探讨移动接收卫星电视的天线自动跟踪系统的研究目的,旨在提高卫星电视信号接收的稳定性和可靠性,为移动通信设备的发展提供技术支持和保障。

1.3 研究意义移动接收卫星电视的天线自动跟踪系统具有重要的研究意义。

首先,随着移动通信和卫星通信技术的快速发展,人们对移动接收卫星电视的需求日益增加。

自动跟踪系统可以实现接收天线自动调整姿态,保证信号的稳定性和清晰度,提高用户体验。

UHF车载型发射与接收系统用户使用手册[内芯]

![UHF车载型发射与接收系统用户使用手册[内芯]](https://img.taocdn.com/s3/m/ab32084469eae009581bec47.png)

PLUSTEK-2010 UHF 数字化音视频通讯指挥系统车载型发射与接收系统说明书科技有限责任公司安全事项请阅读以下简明的规则。

以便您能够更好、更安全地使用PLUS TEK-2010数字化无线音视频指挥系统。

不遵守这些规则可能会导致危险或触犯法律。

本系统使用DC 12V/A C220V,请注意安全用电。

机内有数字无线发射与接收模块、多媒体数据编解码模块、功率放大器等配件,未经厂家授权,请勿拆卸。

设备应放置干燥、通风、无腐蚀性气体场合,避免潮湿、腐蚀带来的设备损害。

注意保持机体清洁,机体清洁时,应断开电源,用清洁的棉布擦拭。

请勿在加油站内或禁止使用无线设备的场所使用本设备,在燃料或化学制品附近时请不要使用本设备。

只有合格的维修人员才可以安装或修理本设备。

目录安全事项 (2)1、前言 (5)1.1本书目的 (5)1.2读者对象 (5)1.3注意事项 (5)1.4环境保护 (6)2、产品简介 (6)2.1产品概述 (6)2.2产品技术特点 (7)3、电气/物理结构 (7)3.1设备介绍 (7)3.2车载发射机面板 (9)3.2.1车载发射机前面板 (9)3.2.2车载发射机后面板 (10)3.3中心接收机面板 (11)3.3.1中心接收机前面板 (11)3.3.2中心接收机后面板 (12)4、设备安装 (13)4.1车载发射机 (13)4.1.1车载发射机组件 (13)4.1.2车载发射机安装方法 (14)4.2中心接收机 (14)4.2.1接收机组件 (14)4.2.2全向玻璃钢天线安装 (15)4.2.3接收机安装方法 (15)5、基本操作手册 (16)5.1车载发射机控制 (16)5.2中心接收机菜单控制 (17)5.3视频监控 (17)5.3.1通过网络进行多媒体的实现 (17)5.3.1.1通过局域网实现 (17)5.3.1.2通过外网实现 (19)6、包装单 (20)6.1、车载发射机设备 (20)6.2、中心接收机设备 (20)7、附录 (21)7.1 保修说明 (21)7.1.1售后服务规定 (21)7.1.2非保修范围情况说明 (22)1、前言1.1本书目的《PL UST EK-2010 U HF数字化音视频指挥系统用户操作手册》描述了安装和配置PL UST EK-2010 U HF数字化音视频指挥系统的具体方法。

车载影音系统集成解决方案

等 自主 品 牌 , 产 品 也 逐 渐 从 低 端 向 中 、

高 端 发 展 。然 而 , 管 中 国 电 子 产 业 制 尽 造 能 力 全 球 领 先 , 车 电 子 或 车 载 电 子 汽 娱 乐 系 统 几 乎 全 被 国 外 公 司 的 方 案 所 占领 . 国 厂 商 只 能 在 收 音 机 、 星 导 中 卫 航 、多媒 体 影音 播 放 及 数 字 电视 四大 功 能 中 的 单 一 功 能 上 提 供 后 装 市 场 的 产 品 ,将 四大 功 能 集 成 于 一 体 的 系 统 还 鲜 有 成熟 的产 品面 世 。 从 实 用 性 的 角 度 看 ,上 述 四大 功 能 的排 序 应 该 是 收 音 机 、 星 导 航 、 媒 体 卫 多 影 音 播 放 及 数 字 电视 ,但 从 技 术 复 杂 程 度 看 , 好 相 反 , 完 成 了 最 复 杂 的 数 字 正 在 电 视 和 多 媒 体影 音播 放功 能后 ,增 加 卫 星 导航 和收 音 机 功 能 相对 比较 容 易 。 中 国数 字 电视 市 场 培 育 了一 大 批 与 数 字 电 视 产 业 相 关 的 集 成 电路 设 计 公 司 、 机 设 计 生 产 公 司 、 端 系 统 设 计 公 整 前

移 动 电视 解 决 方案

1

S 言 I

载影 青 娱 乐 系 统 的需 求 。 将 收 音 机 、 星 导 航 、 媒 体 影 音 播 卫 多 放 及 数 字 电视 四大 功 能 集 成 在 一 个 整 机

共 用 的 鞭 状 天 线 可 以 实 现 在 收 音,

2 0 年 . 中 国 已成 为 世 界上 第 一 大 09

电 视/ 航 模 式下 切 换 。倒 车 影 像 可通 过 导 U B接 口接 人 系统 .液 晶屏 在 挂 倒 档 时 S

广州数字电视移动直播车传输系统测试方案

【 中图分类号 】T 9 8 N 4

【 文献标识码 】B

广州市委市政府将“ 数字移动直播演播 车” 目列 为 项

一

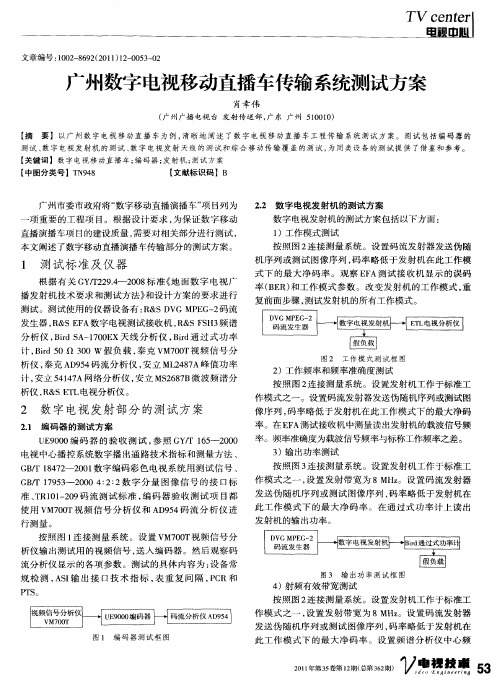

22 数 字 电视 发 射 机 的测 试 方 案 .

项重 要的工程项 目。根据设 计要求 , 为保证数 包括 以下方 面 : 1 )工作模式测试 按 照图 2 连接测量系统 。设置码 流发射器发送伪 随 机 序列或测试 图像序列 , 码率 略低 于发射机 在此工作模 式 下 的最大 净码 率 。观察 E A测试接 收机 显示 的误码 F 率 ( E 和工作 模式参 数 。改 变发射机 的工作模 式 , B R) 重

图 1 编码器测试框 图

此 工作模 式 下 的最 大净 码率 。设 置频谱 分析 仪 中心频

2 1 年第 3 卷第 1 期 ( 01 5 2 总第 3 2 ) 6期

1 电 视 技 蠢 /

de c, E n

l 丁V e tr c n e

l 电顽£心 l 1

率 为发 射 频率 , B 分辨 力 带 宽 ) R W( 设置 为 1k z V W 信号 中心频率 F 处信号 幅度记为A 。测量发射带外最 H ,B C C ( 示带 宽 ) 显 设置 为 1k z H 。分别 读取 高段 、 端信号载 低 波频率 朋 P和 F P 射频有效带宽为 F P和F P之差 。 L, 日 L 5 信号带肩测试 ) 按照图 2 连接测量 系统 。设置发射机工作于标准工 大信号 幅度值A X, MI 带外发射为A X与A 的差 。 MI C 1 ) Q幅度不平衡度测试 o V 按照 图4 连接测量 系统 。设置发射机工作 于标准工

测试 。测试使用 的仪 器设 备有 : & V E 一 码流 R SD G MP G 2 发生器 , & F R SE A数字 电视 测试 接收机 , & S 频谱 R SF H3

车载移动电视

• 当前,国家为移动电视业发展提供了一个良好的环境。国家允许有资金、资源和节目优势的境内资本,包括民营资本,参 与合作经营,实现多元筹资。而且还对数字电视的相关投资运营项目采取减免税政策。

• 车载移动电视的传播环境主要是交通工具里,具有一定的封闭性。单一频道使受众处于“强迫收视”状态, 在一定程度上都会接触节目的画面和声音

• 传播受众的开放性与指向性 • 车载移动电视的受众是开放的,流动的。所以他拥有庞大的受众群体,市场开发潜力巨大。但受

众的匿名性和随机性较强。

• 从另一个角度来说,车载移动电视针对特殊群体,包括各类乘客,指向性较强。

• 但车载移动电视发展初期的资本需求是巨大的,例如每辆公交车安装终端的成本约1万元人民币,以一个二三线城市为基 准,铺设设备的基本费用也高达到千万元人民币。国内三大车载电视运营商华视传媒、巴士在线、世通华纳拥有着雄厚的 民间资本并与风投资本的有效结合再通过上市等方式筹集大量的资金,迅速带动车载移动电视业的蓬勃发展。

• 2006年中国数字电视行业《数字电视地面广播传输系统帧结构、信道编码和调试》的标准出台。2006年8 月国家标准管理委员会颁布了这一具有自主知识产权的中国数字电视地面广播传输系统标准,于2007年8月 1日实施,并在规定中指出,数字电视地面传输国家标准针对的是地面无线电视的基础标准。

• 地面标准是在清华大学DMB-T标准、上海交大的ADTB-T和广播科学研究院StiMi三种标准融合的基础上建 立的,支持高清晰度电视、标准清晰度电视很多媒体数据广播等多种业务。改标准以“数字电视地面多媒 体广播(DTMB)”之名向国际电联申请为国际标准。由于该标准牵涉面大,技术难度高,所以出台的时间 表一变再变,直到近期才进入实质性的收官阶段。但对于其标准的优劣和选择业内一直存在激烈争论。

南京地铁车载视讯系统介绍

本文链接:/Periodical_tdjccl200803016.aspx 授权使用:颜泽铃(hntl),授权号:60e3f448-e998-49e1-a3f7-9e4b000f3121 下载时间:2010年12月13日

情况。安装在司机操纵台右上方。 (3)车载视讯系统的安装 南京地铁加装电客车车载视讯系统项目于2005年 初启动,第一列车的改装工作于2005年8月开始,此 时南京地铁电客车的生产已开始第15列的组装,这就 预示着南京地铁电客车车载视讯系统的安装,大部分 列车只能在小型车辆基地进行现车拆装;主要进行拆 卸坐椅、二位端电气柜、拆窗立罩上铣床铣出线孔、 墙板开孔安装铆螺母、拆司机室顶板、拆司机台下安 装柜、车下布线、车上布线、引上线、接线端子的压 接、连接器的组成;安装接收天线、DVB—T接收机 顶盒、电源适配器、视音频分配器、INFO—TV资讯播 出系统、小键盘控制器、19英寸液晶显示屏、7英寸 液晶显示屏等;只有3列车是在生产基地将车载视讯 系统的线缆和一些安装件预安装在车内,其他设备还 是要到小型车辆基地进行现车拆装。 本车显示屏的视音频电缆和电源线在车顶弯梁处 布线;分至邻车的移动电视系统控制线和视音频电缆 在S—END2一CAB—A角引至车下,穿过金属软管固 定在车下线槽A侧,通过车端连接器与邻车视音频分 配器相连。 2结束语 南京地铁电客车车载视讯系统突出个性化,便于 运营管理,预制信息和即时信息相结合,满足运营功 能要求,集广告、电视、即时新闻、娱乐于一体,对 资源进行开发,提高地铁运营服务质量而安设地铁电 客车车载视讯系统。

第28卷第3期 2 0 0 8年6月 文章编号:1008—7842(2008)03—0054—02

铁道机车车辆

RAⅡ:WAY LOCOM(y11、咂&CAR

CMMB车载数字电视系统应用解决方案

专业 专注 hp w wv . t: w .ec tf taa l

【 期 专 题 : 动 电视 解 决 方 案 】 本 移

1 1 i na 2 Mr d :充分重 视和 了解 中 18 联发科技发力电视产业 “ a 2 三网融合”

国 市 场 觅 求商机

CMMB 载数 字 电视 系统应 用 解 决 方 案 车

c arc ei t s n a ana e a dia v ntg s ea h outo .An x mpl i gy n n he c u l nsa lto p o e s h a t rsi a d dv tg s nd s d a a e c s l i n c e a e s ie i t a t a i tla in r c s .

。 【 关键词 】移动多媒体广播 ; 车载数字电视 ; 解决方案 ; 移动电视 ; 车载影音 系统

【 图分 类号 】T 9919 中 N 4 .7

磐

MA Ha —f n ,CHE Xu n i eg NG a

瓢

【 文献 标 识 码 】A

【 章编 号 】0 2 89 (0 0 1— 17 0 文 10 — 6 2 2 1 )0 0 1— 3

Ap l a i n S l t n o p i t o u i fCM M B h ce Di i l lv so y t m c o o Ve i l g t e i n S se a Te i

、

(hn racsig C roai ,B in 0 0 1 hn ) C iaBod at op rt n e ig 1 0 3,C ia n o j

【 b tat hn bl Mu i e i Bod at g ( MMB i C iaso n it l ta poet r hso dg a m bl A src l ia Moi hm da ra csn C C e i ) s hn w n l cul rpr i t f itl o i ee y g i e

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

车载移动电视接收的系统方案Dr.Axel ZimmermannDr.Ing. Wolfgang Sautter在柏林推出的DVB T(地面数字广播)数字电视也已经影响到汽车娱乐系统中的电视接收。

现在,汽车电视接收机不仅能够接收模拟电视信号(它仍将在城市以外的地区继续存在数年),而且也能够接收和处理DVB T信号。

Hirschmann Electronics已经开发出基于FPGA的“混合电视接收机”,以满足此类新兴的需求。

新的混合接收机还采用了改进的分集算法,获得更好的模拟接收质量。

最初规划的模拟电视发射机是面向固定的家庭用户,在屋顶上安装定向天线就可以收到清晰的图像。

然而,用于移动电视接收的天线通常安放得都更低。

不仅天线高度不一,而且由于接收的信号随着汽车的运行路线不断地变化,在这种情况下也无法使用定向天线。

另外,由于信号经建筑物或其它车辆的散射和折射,接收的信号会相互叠加。

这样会导致信号的损失(Rayleigh幅度分布)。

德国(柏林)第一代DVB T网络是为便携接收而不是移动接收而设计的。

因此,要获得令人满意的车内电视接收效果需要具有多天线的“分集”系统。

例如,使用“扫描分集”技术,系统自行控制在不同天线之间切换,选择具有最高接收电平的天线。

对于模拟电视,因为视频和声音的载波相差5MHz,且受到不同源的干扰,所以可以分别对视频和声音进行这种切换。

Hirschmann的接收机为叠加接收信号的模拟电视设计了一个改良的专用过程。

首先扫描信号,然后对时间同步,之后测算每个独立信号的质量。

采用这种测试方法确定“权重因子”。

这些权重因子乘以每个接收信号。

这种处理过程得到的信号比单一的最佳接收信号具有更好的信噪比。

DVB T接收机天线采用MRC(最大比值合并)分集。

采用这种方式,将最佳的载波信号组合形成输出信号,即使车辆的运行速度超过100Km/h(60mph)也能确保汽车电视获得良好的接收质量。

频率分集的作用独立于天线分集:在接收过程中,Hirschmann混合电视接收机无需对用户部分作任何操作,就扫描发射机情况。

如果发现某个信道承载同样的内容,但接收质量更好,设备会自动切换到这个新的信道。

这样用户就可以在旅行过程中连续不断地观看节目,而不必当汽车经过某个发射台覆盖范围时手动调谐。

接收机体系电路框图是采用三路接收的Hirschmann混合电视接收机示例。

虽然系统可以增减可能的接收通道数量,一般推荐两至四个通道。

接收通道数量越多会改善接收质量,但同时也会增减系统硬件和软件复杂性。

调谐器使用的输入信号是从集成天线接收到的RF信号――碟形天线通常通过受控放大器接到单独的调谐器上。

调谐器是混合调谐器,可接收任何标准的模拟信号和DVB T信号。

对于模拟接收,调谐器中会集成相应的解调器。

在模拟接收过程中,模数转换器扫描模拟视频和音频信号,将其送往混合接收机的FPGA器件。

在DVB-T接收过程中,编码正交频分复用器(COFDM)解调器将送出MPEG数据流。

独立的COFDM解调器连接在一起,实现所需的MRC分集,优化MPEG数据流。

MPEG解码器从MPEG 数据流中提取出视频、音频和数据信号。

然后这些信号也送往FPGA。

MPEG解码器连接着外部SDRAM存储器。

用FPGA进行数字信号处理所有的数字信号处理,包括模拟视频和声音的天线分集、基带声音处理、电文译码和其它数据内容如视频节目系统(VPS)、管理和存储SDRAM存储器中的这些信息以及通过串口和控制主机通信等,都可以在Altera Cyclone EP1C12 FPGA中完成。

Cyclone FPGA不仅提供了逻辑和算术功能,其中的RAM也可以用于诸如FIFO等功能。

Hirschmann分集接收机的设计者充分利用Altera的开发工具,创建支持系统功能所需的复杂单元。

例如,Altera的FIR编译器能自动生成有限冲激响应滤波器(FIR),SOPC Builder工具能生成控制器系统。

该控制器包括Nios嵌入处理器,以及RAM、串口和SDRAM 控制器。

FPGA的配置数据存放在EPCS4串行Flash存储器中,当接收机打开时加载到FPGA 中。

FPGA处理的图形数据发送给数模转换器,在电视屏上显示模拟信号。

从FPGA送出的音频数字信号送给MOST接收机,然后送给MOST总线。

当用户通过MMI输入控制指令,这些指令也会通过MOST总线发送给收发信机。

主机控制器和接收机的可配置部分之间进行通信,管理整个系统的控制功能。

低成本的FPGAHirschmann电视接收机中使用的低成本Cyclone EP1C12器件有12,000多个逻辑单元和234Kbit的嵌入存储器。

该系列中的所有五个器件都有汽车温度范围(-40°C至+125°C)的产品。

这些器件中的嵌入存储器由多个4,608bit的存储块组成,可以快速地访问本地的数据存储器资源。

每个存储块支持多种配置,包括真双口和单口RAM、ROM和FIFO。

由于Cyclone FPGA提供了专用接口,能够很容易地配置为同DDR-SDRAM或FCRAM通信。

该接口具有高达266Mbps的快速可靠的数据传送性能。

Cyclone器件系列具有八个低偏移的全局时钟网,它们分布在整个芯片内,由四个专用时钟管脚馈入。

对于整个系统的时钟管理,器件的PLL(每个有三个输出抽头)也能够胜任频率合成和相位偏移的工作。

内嵌处理器的FPGA系统Cyclone FPGA显然是为基于处理器的应用进行了优化,尤其是能从嵌入软核处理器如Altera的Nios处理器中受益的应用。

典型的Nios控制器系统由一个CPU、片内RAM和ROM、一个外部存储控制器和许多串行和并行接口组成。

这样一个基于Nios的系统需要大约1,500个逻辑单元(LE),占用Cyclone EP1C12器件有效逻辑资源的12.5%。

所有的Nios模块都可以通过多主交换阵列连接到Avalon总线上。

Nios处理器是一款五级流水线的16或32位RISC处理器,基于数据和地址总线完全分离的Harvard结构。

Avalon 交换阵列完全支持以上种总线。

Nios处理器的同步接口,低的资源利用率和优化的性能使之极其适合于在可编程逻辑中实现。

其它的特性包括多达512个寄存器的大型寄存器组和多达64个优先级可调的中断。

Nios处理器的用户也可自行为Nios处理器设计增加专用指令。

这些指令是由用户定义在硬件中实现的处理器命令。

例如,在软件中估计需要80个时钟周期的乘法功能若以专用指令执行只需要两个周期。

这样就能将诸如加速信号处理任务等各种功能集成到指令集中,能够处理多达五条不同的指令。

系统设计者使用Altera的SPOC Builder工具自动创建Nios 系统单元之间的接口逻辑,为其分配一个空闲的操作码,并生成所有所需的C和汇编器的宏。

Nios处理器的设计环境包括参数化硬件描述和自适应的软件开发环境。

Altera器件如Cyclone、Stratix、Stratix GX和HardCopy器件能够实现Nios处理器。

典型的FPGA内的Nios处理器性能在50至125MIPS之间。

Nios软核处理器支持的操作系统包括ATI Nucleus,uC/OSII和KROS。

可编程系统(SOPC)设计设计者使用Altera的SOPC Builder工具能以简单的按部就班的方式生成期望的系统。

首先,选择用于处理的CPU――本例中是Nios结构。

然后设置不同的结构特性配置处理器。

最重要的参数包括:数据总线宽度寄存器组大小硬件支持的算术功能(如乘法)性能或尺寸优化支持操作系统专用指令(除法,浮点单元,FFT和其它)CPU经裁剪符合预期的系统需求,设计者只需要建立Nios控制系统所需的接口。

辅以图形用户接口,由齐全的不同模块的库构建所需的系统。

接口库包括器件使用的IP核和Altera IP合作者提供的模块。

也可以将专用模块添加到模块列表中,以后该模块就可以成为特定用户群的标准块。

每个IP模块用各自编程掩码进行参数配置。

在这一过程中,模块会根据设置的数据总线宽度进行调整,对它的功能进行控制,或对特定的应用进行优化。

例如,FIR滤波器的抽头和系数可以调整,以满足分集电视接收机的特定需求。

下一步是将功能模块和CPU连接。

首先,以图形方式生成内部总线系统,连接接口模块和CPU,分配地址范围和中断。

这样就设置了整个系统所需的必要单元,系统也随之实现。

在硬件方面,Altera SOPC Builder生成网络列表,VHDL或Verilog描述和仿真环境。

在软件方面,SOPC Builder自动创建程序头文件,库以及接口并入程序环境所需的驱动。

最后一步是将Nios设计集成到PLD中,编写应用程序,将系统及库和操作系统合成在一起,对目标系统进行编程。

所有这些步骤都将在Quartus II集成开发环境中完成,该环境也可用于最后的验证和调试阶段。

数字电视开发的下一目标未来Hirschmann计划将其它的数字标准如ISDB T(日本)和ATSC(USA)集成到该系统中。

Hirschmann也在研究“天线底部接收机”的概念,即接收机位于天线的底部。

这种布置可以不需要RF馈线和放大器,从而进一步改善接收质量。

将接收机的部分硬件转换为软件,这样可以通过软件对不同的广播服务进行配置。

这样的软件无线电是基于一致的硬件平台,这样整个系列接收机的衍生品可以在很大的频率范围内由软件进行调整、配置和使用。

软件无线电的概念要求在天线上之间扫描广播信号,然后在数字域上进行全部的后续处理。

现在,还无法实现这种意义上的软件无线电,因为无法达到所需的系统处理性能,最重要的是根本无法提供模数变换器所需的很高的采样频率。

不过,以近乎中频工作的软件无线电子集现在可能已经很明确了。

由于这种无线电技术具有令人满意的质量和便利的特性,很可能很快就会配置到新的轿车中。

作者Dr. Axel Zimmermann在Stuttgart大学攻读电子工程。

他在不同的制造公司有多年可编程逻辑应用工程师的工作经验,现在负责为Altera GmbH协调中欧的汽车项目。

是Altera GmbH的区域销售经理。

Dr.Ing.Wolfgang Sautter自1998年,一直在德国Neckartenzlingen的Hirschman Electronics GmbH & C. KG的汽车通信系统部担任开发工程师。

他在其它项目中,负责移动电视接收机的开发。