基于VerilogHDL设计的多功能数字钟

用Verilog语言编写的多功能数字钟

《数字电子技术课程设计》报告专业班级:姓名:学号:设计日期:一.设计题目多功能数字钟电路设计二.设计任务及要求多功能数字钟应该具有的功能有:显示时—分—秒、整点报时、小时和分钟可调等基本功能。

整个钟表的工作应该是在1Hz信号的作用下进行,这样每来一个时钟信号,秒增加1秒,当秒从59秒跳转到00秒时,分钟增加1分,同时当分钟从59分跳转到00分时,小时增加1小时,小时的范围为0~23时。

在实验中为了显示的方便,由于分钟和秒钟显示的范围都是从0~59,所以可以用一个3位的二进制码显示十位,用一个四位的二进制码(BCD 码)显示个位,对于小时因为他的范围是从0~23,所以可以用一个2位的二进制码显示十位,用一个4位的二进制码(BCD码)显示个位。

实验中由于七段码管是扫描的方式显示,所以虽然时钟需要的是1Hz 时钟信号,但是扫描需要一个比较高频率的信号,因此为了得到准确的1Hz 信号,必须对输入的系统时钟50Mhz进行分频。

对于整点报时功能,本实验设计的是当进行正点的倒计时5秒时,让LED来闪烁进行整点报时的提示。

调整时间的按键用按键模块的S1和S2,S1调节小时,每按下一次,小时增加一个小时;S2调整分钟,每按下一次,分钟增加一分钟。

另外用S8按键作为系统时钟复位,复位后全部显示00—00—00。

管脚分配如下表:三.基于Verilog HDL语言的电路设计、仿真与综合(一)顶层模块本程序采用结构化设计方法,将其分为彼此独立又有一定联系的三个模块,如图1所示:LocationPIN_R16Option Value VCC S1INPUT Location PIN_P14Option Value VCC S2INPUT Location PIN_J3Option Value VCCCPINPUT Location PIN_M4Location PIN_F3Location PIN_F4Option Value SEL[2..0]OUTPUT Location PIN_L14Option Value LEDOUTPUTLocation PIN_N4Location PIN_G4Location PIN_H4Location PIN_L5Location PIN_L4Location PIN_K4Location PIN_K5Option Value LEDAG[6..0]OUTPUTCP CPoutf enpininst1CPoutS1S2RETHour[5..0]Minute[5..0]Second[5..0]LEDkongzhiqi inst2VCCRETINPUT CPout Hour[5..0]Minute[5..0]Second[5..0]SEL[2..0]LEDAG[6..0]xianshi inst图1:顶层结构框图(二)子模块 1.分频器分频器的作用是对50Mhz 的系统时钟信号进行分频,得到频率为1000hz 的信号,作为显示器的输入信号。

Verilog HDL 多功能电子钟

基于verilog HDL语言的数字电子钟设计摘要:本课程设计完成了数字电子钟的设计,数字电子钟是一种用数字显示秒、分、时的计时装置,由于十足集成电路技术的发展,使数字钟走时准确、多功能化且性能稳定等优点。

在本次设计中,系统开发平台为MAX+plusⅡ,硬件描述语言是Verilog HDL。

依据Verilog HDL语言设计由计时,闹铃,秒表,报时等7大模块组成的多功能数字电子钟。

根据输入,观察输出及仿真。

设计方案和设计平台完成了程序编写和程序调试,通过运行程序及时序波形的仿真有效验证了设计的正确性,初步实现了设计目标。

关键词多功能数字电子钟;Verilog HDL;MAX +plusⅡ;专用集成电路;Based on Verilog HDL languagedigital electric clock designThe student's name: HThe guide teacher: XAbstract:The course is designed to finished the design of digital electric clock, digital electric clock is a kind of digital display second, points, when the timer, because dye-in-the-wood integrated circuit technology development, and make a digital clock keeps good time, more functional and stable performance, etc. In this design, system developing platform for MAX + plus Ⅱ, hardware description language is Verilog HDL. According to the design scheme and design platform completed programming and program test, through to run the program in time sequence waveform simulation verified effectively the correctness of design, and then realized the design goal.Keywords:application-specific integrated circuit, Verilog HDL, Multi-function digital electric clock; MAX + plus Ⅱ目录1 引言1.1课题设计的背景、目的1.2 课题设计环境2 Verilog HDL简介3 多功能电子钟的7大模块设计及仿真芯片生成3.1 计时模块3.2 闹铃设置模块3.3 校时模块3.4 秒表功能模块3.5 整点报时模块3.6 闹铃屏蔽及响铃功能模块3.7 秒表提示功能模块4 7大模块组合的多功能电子钟的设计及仿真4.1 功能描述4.2 源程序(基于Verilog HDL语言)4.3 模块仿真5 结束语参考文献1 引言数字电子钟的时间周期为24小时,具有显示时,分,秒的功能,并设置有闹钟,日历,时间调节等功能。

VerilogHDL语言数字时钟

VerilogHDL语言数字时钟EDA与数字系统设计报告实验名称:带有设臵时间功能和闹钟功能的数字钟一、设计内容和要求实验要求使用Verilog HDL进行多功能时钟的设计具体要求如下:1.能将基本的小时、分钟、及秒钟显示在数码管上2.能利用拨码开关进行时间的校正3.具有整点报时和闹钟的功能二、设计原理1.工作原理多功能数字钟系统共包括三个模块,即分频器模块、计数器模块和显示译码模块。

多功能数字钟的功能可以从整体上分为三类,分别是正常计时、时钟校对和闹钟设臵,所以考虑在系统中设臵一个模式控制信号mode。

模式控制信号对应一个按键,每按一次按键相当于工作模式进行一次变换,多次按下则数字钟将在正常计时、时间校对和闹钟设臵三个工作模式下依次循环。

在设计中,时钟校对和闹钟设臵工作模式都需要对时间进行设臵,通常是对小时和分钟进行设臵,所以需要在系统中设臵一个时间设臵信号set,对应一个按键,每按一次相当于在小时设臵和分钟设臵之间进行转换。

时间设臵时,分钟和小时计时单位之间互相独立,不存在进位关系。

同时设臵一个时间调整信号accum,每按一次与accum对应的按键,相当于对需要调整的分钟或小时的数字进行加1操作。

数字钟的计时输出信号时必不可少的,用hour,min和sec信号分别表示需要显示的小时、分钟和秒钟的计时结果,上述计时结果将通过译码显示模块进行译码后,连接到外部的七段数码显示器。

在带有闹钟设臵功能的数字钟中,闹钟输出信号也是必不可少的,到达到闹钟设臵的时间后,要向外部扬声器发送一个闹铃信号,设臵alert。

另外,我们还提供了闹钟铃声信号voice,当voice为0的时候,闹钟处于静音状态下,即使时间达到闹钟设定的时间也不会发声,当voice为1的时候,可以正常闹铃,voice信号对应一个拨码开关。

本设计中的小时、分钟和秒钟的计时结果采用BCD码表示方法。

采用这种表示方法便于对数结果的高位和低位分别进行译码。

用Verilog语言编写的多功能数字钟

这次的闹钟电路设计和多功能数字钟有一些相似的地方,不同在于整体构思和细

节上要求的差异。

构思根据要求采用的是状态机设计方法。从一个状态进入另一个状态最适合这个

设计了。细节上和数字钟也有很大的差异。中间的控制逻辑有时候需要反馈。前

后都是有联系的,并不是独立存在的。

本次设计基本上完成的所以的要求,但是由于时间紧急,一些细节并不是很完美,

分频器的作用是对 50Mhz 的系统时钟信号进行分频,得到频率为 1hz 的信号,

作为时钟的输入信号。

2

2.控制器和计数器 控制器的作用是,调整小时和分钟的值,并能实现清零功能。计数器的

作用是实现分钟和秒钟满 60 进 1,小时则由 23 跳到 00。当到达 59 分 55 秒的时 候,LED 灯会闪烁来进行报时。

end 2:

begin state<=2; s=1;

end 3:

begin s=0; if(k1==0) //时调整

7

begin

if(nz_h_l==3)

begin

nz_h_l=0;

if(nz_h_h==2)nz_h_h=0;

else nz_h_h=nz_h_h+1;

end

else nz_h_l=nz_h_l+1;

end

else if(k3==0) finish=1;

//设置完成

else if(k4==0) spker_en=1; //停止声响

end

8

4: begin s=0; if(k4==0) begin on_off<=!on_off;state=0;end end

endcase end end endmodule 3.显示器 显示器的作用是将时:分的值在数码管上依次显示出来。从分频器输出的 1Khz 的信号作为数码管的扫描信号。SEL 表示 6 个数码管选择位,它的取值表示八个 数码管,从左至右依次是 111~000。seg 表示七段数码管,它的取值决定特定位 数上显示的数字。

基于VerilogHDL语言多功能数字钟设计毕业设计论文

多功能数字钟NJUST多功能数字钟设计基于VerilogHDL语言学院:电子工程与光电技术学院学号:************姓名:指导教师:2014年11月21日星期五摘要:基于FPGA平台,运用Verilog语言编写设计一多功能数字钟,包括基本的时钟,校时校分,整点报时功能。

扩展闹钟,秒表,万年历,键盘输入功能。

Abstract:FPGA-based platform, using Verilog language to design amulti-functional digital clock, including basic function of clock, school hours, school minutes,the whole point timekeeping. And extended function of alarm clock, stopwatch, calendar, keyboard input.关键词:多功能数字钟,可编程逻辑器件,EDA设计,VerilogKeywords:multi-functional digital clock, FPGA, EDA disign, Verilog目录1 设计要求 (2)2 设计方案选择及思路分析 (2)3 各子模块设计原理和分析 (3)3.1 分频模块 (3)3.2 时分秒模块 (5)3.3 时分调整模块 (6)3.4 报时模块 (7)3.5 扫描显示模块 (8)3.6 秒表模块 (9)3.7 闹钟模块 (10)3.8 万年历模块 (12)3.9 键盘扫描模块 (13)4 调试仿真 (15)5 编程下载 (16)6 结论 (17)7 参考文献 (17)8 实验感想 (17)9 源代码 (18)11 设计要求基于FPGA可编程逻辑器件,用quatusII软件设计一个多功能数字钟,其基本要求如下:1.有基础的计时显示功能,即时、分、秒显示在6个七段管上2.K0,K1,K2,K3分别为系统使能(暂停),时钟清零,校时,校分开关。

多功能数字钟

3 需求分析与系统设计说明

3.1 需求分析

现代社会的标志之一就是信息产品的广泛使用, 而且是产品的性能越来越强, 复杂程度 越来越高, 更新步伐越来越快。 支撑信息电子产品高速发展的基础就是微电子制造工艺水平 的提高和电子产品设计开发技术的发展。 前者以微细加工技术为代表, 而后者的代表就是电 子设计自动化(electronic design automatic,EDA)技术。 本设计采用的 verilog 是一种全方位的硬件描述语言,具有极强的描述能力,能支持系 统行为级、寄存器传输级和逻辑门级三个不同层次的设计;支持结构、数据流、行为三种描 述形式的混合描述、覆盖面广、抽象能力强,因此在实际应用中越来越广泛。 ASIC 是专用 的系统集成电路,是一种带有逻辑处理的加速处理器。而 FPGA 是特殊的 ASIC 芯片,与其他 的 ASIC 芯片相比,它具有设计开发周期短、设计制造成本低、开发工具先进、标准产品无 需测试、质量稳定以及可实时在线检测等优点。 钟表的数字化给人们生产生活带来了极大的方便, 而且大大地扩展了钟表原先的报时功 能。诸如定时自动报警、定时启闭电路、定时开关烘箱、通断动力设备,甚至各种定时电气 的自动启用等,所有这些,都是以钟表数字化为基础的。因此,研究数字钟及扩大其应用, 有着非常现实的意义。

顶层时钟模块 (二) (二)顶层时钟模块

设计原理: module top_clock (Hour,Minute,Second,_1Hz,nCR,AdjMinKey,AdjHrKey); input _1Hz,nCR,AdjMinKey,AdjHrKey; output [7:0] Hour,Minute,Second; wire [7:0] Hour,Minute,Second; supply1 Vdd; wire MinCP,HrCP; counter60 UT2(Second,nCR,Vdd,_1Hz); counter60 UT1(Minute,nCR,Vdd,~MinCP); counter24 UT3(Hour[7:4],Hour[3:0],nCR,Vdd,~HrCP); assign MinCP=~AdjMinKey?(Second==8'h59):_1Hz; assign HrCP= ~AdjHrKey?({Minute,Second}== 16'h5959):_1Hz; Endmodule 顶层模块仿真波形如下:

用Verilog语言编写的多功能数字钟

《数字电子技术课程设计》报告专业班级:姓名:学号:设计日期:一.设计题目多功能数字钟电路设计二.设计任务及要求多功能数字钟应该具有的功能有:显示时—分—秒、整点报时、小时和分钟可调等基本功能。

整个钟表的工作应该是在1Hz信号的作用下进行,这样每来一个时钟信号,秒增加1秒,当秒从59秒跳转到00秒时,分钟增加1分,同时当分钟从59分跳转到00分时,小时增加1小时,小时的范围为0~23时。

在实验中为了显示的方便,由于分钟和秒钟显示的范围都是从0~59,所以可以用一个3位的二进制码显示十位,用一个四位的二进制码(BCD 码)显示个位,对于小时因为他的范围是从0~23,所以可以用一个2位的二进制码显示十位,用一个4位的二进制码(BCD码)显示个位。

实验中由于七段码管是扫描的方式显示,所以虽然时钟需要的是1Hz 时钟信号,但是扫描需要一个比较高频率的信号,因此为了得到准确的1Hz 信号,必须对输入的系统时钟50Mhz进行分频。

对于整点报时功能,本实验设计的是当进行正点的倒计时5秒时,让LED来闪烁进行整点报时的提示。

调整时间的按键用按键模块的S1和S2,S1调节小时,每按下一次,小时增加一个小时;S2调整分钟,每按下一次,分钟增加一分钟。

另外用S8按键作为系统时钟复位,复位后全部显示00—00—00。

管脚分配如下表:三.基于Verilog HDL语言的电路设计、仿真与综合(一)顶层模块本程序采用结构化设计方法,将其分为彼此独立又有一定联系的三个模块,如图1所示:LocationPIN_R16Option Value VCC S1INPUT Location PIN_P14Option Value VCC S2INPUT Location PIN_J3Option Value VCCCPINPUT Location PIN_M4Location PIN_F3Location PIN_F4Option Value SEL[2..0]OUTPUT Location PIN_L14Option Value LEDOUTPUTLocation PIN_N4Location PIN_G4Location PIN_H4Location PIN_L5Location PIN_L4Location PIN_K4Location PIN_K5Option Value LEDAG[6..0]OUTPUTCP CPoutf enpininst1CPoutS1S2RETHour[5..0]Minute[5..0]Second[5..0]LEDkongzhiqi inst2VCCRETINPUT CPout Hour[5..0]Minute[5..0]Second[5..0]SEL[2..0]LEDAG[6..0]xianshi inst图1:顶层结构框图(二)子模块 1.分频器分频器的作用是对50Mhz 的系统时钟信号进行分频,得到频率为1000hz 的信号,作为显示器的输入信号。

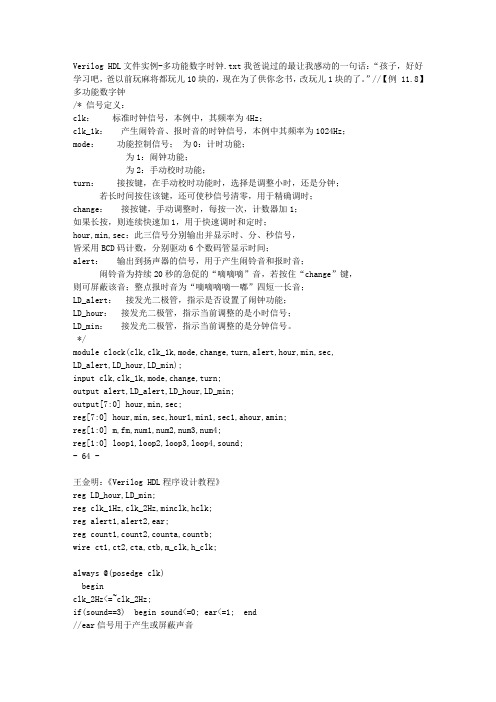

Verilog HDL文件实例-多功能数字时钟

Verilog HDL文件实例-多功能数字时钟.txt我爸说过的最让我感动的一句话:“孩子,好好学习吧,爸以前玩麻将都玩儿10块的,现在为了供你念书,改玩儿1块的了。

”//【例 11.8】多功能数字钟/* 信号定义:clk:标准时钟信号,本例中,其频率为4Hz;clk_1k:产生闹铃音、报时音的时钟信号,本例中其频率为1024Hz;mode:功能控制信号;为0:计时功能;为1:闹钟功能;为2:手动校时功能;turn:接按键,在手动校时功能时,选择是调整小时,还是分钟;若长时间按住该键,还可使秒信号清零,用于精确调时;change:接按键,手动调整时,每按一次,计数器加1;如果长按,则连续快速加1,用于快速调时和定时;hour,min,sec:此三信号分别输出并显示时、分、秒信号,皆采用BCD码计数,分别驱动6个数码管显示时间;alert:输出到扬声器的信号,用于产生闹铃音和报时音;闹铃音为持续20秒的急促的“嘀嘀嘀”音,若按住“change”键,则可屏蔽该音;整点报时音为“嘀嘀嘀嘀—嘟”四短一长音;LD_alert:接发光二极管,指示是否设置了闹钟功能;LD_hour:接发光二极管,指示当前调整的是小时信号;LD_min:接发光二极管,指示当前调整的是分钟信号。

*/module clock(clk,clk_1k,mode,change,turn,alert,hour,min,sec,LD_alert,LD_hour,LD_min);input clk,clk_1k,mode,change,turn;output alert,LD_alert,LD_hour,LD_min;output[7:0] hour,min,sec;reg[7:0] hour,min,sec,hour1,min1,sec1,ahour,amin;reg[1:0] m,fm,num1,num2,num3,num4;reg[1:0] loop1,loop2,loop3,loop4,sound;- 64 -王金明:《Verilog HDL程序设计教程》reg LD_hour,LD_min;reg clk_1Hz,clk_2Hz,minclk,hclk;reg alert1,alert2,ear;reg count1,count2,counta,countb;wire ct1,ct2,cta,ctb,m_clk,h_clk;always @(posedge clk)beginclk_2Hz<=~clk_2Hz;if(sound==3) begin sound<=0; ear<=1; end//ear信号用于产生或屏蔽声音else begin sound<=sound+1; ear<=0; endendalways @(posedge clk_2Hz) //由4Hz的输入时钟产生1Hz的时基信号clk_1Hz<=~clk_1Hz;always @(posedge mode) //mode信号控制系统在三种功能间转换 begin if(m==2) m<=0; else m<=m+1; endalways @(posedge turn)fm<=~fm;always //该进程产生count1,count2,counta,countb四个信号 begincase(m)2: begin if(fm)begin count1<=change; {LD_min,LD_hour}<=2; endelsebegin counta<=change; {LD_min,LD_hour}<=1; end{count2,countb}<=0;end1: begin if(fm)begin count2<=change; {LD_min,LD_hour}<=2; endelsebegin countb<=change; {LD_min,LD_hour}<=1; end{count1,counta}<=2'b00;enddefault: {count1,count2,counta,countb,LD_min,LD_hour}<=0; endcaseend- 65 -程序文本always @(negedge clk)//如果长时间按下“change”键,则生成“num1”信号用于连续快速加1 if(count2) beginif(loop1==3) num1<=1;elsebegin loop1<=loop1+1; num1<=0; endendelse begin loop1<=0; num1<=0; endalways @(negedge clk) //产生num2信号if(countb) beginif(loop2==3) num2<=1;elsebegin loop2<=loop2+1; num2<=0; endendelse begin loop2<=0; num2<=0; endalways @(negedge clk)if(count1) beginif(loop3==3) num3<=1;elsebegin loop3<=loop3+1; num3<=0; endendelse begin loop3<=0; num3<=0; endalways @(negedge clk)if(counta) beginif(loop4==3) num4<=1;elsebegin loop4<=loop4+1; num4<=0; endendelse begin loop4<=0; num4<=0; endassign ct1=(num3&clk)|(!num3&m_clk); //ct1用于计时、校时中的分钟计数assign ct2=(num1&clk)|(!num1&count2); //ct2用于定时状态下调整分钟信号assign cta=(num4&clk)|(!num4&h_clk); //cta用于计时、校时中的小时计数assign ctb=(num2&clk)|(!num2&countb); //ctb用于定时状态下调整小时信号always @(posedge clk_1Hz) //秒计时和秒调整进程if(!(sec1^8'h59)|turn&(!m))beginsec1<=0; if(!(turn&(!m))) minclk<=1;- 66 -王金明:《Verilog HDL程序设计教程》end//按住“turn”按键一段时间,秒信号可清零,该功能用于手动精确调时else beginif(sec1[3:0]==4'b1001)begin sec1[3:0]<=4'b0000; sec1[7:4]<=sec1[7:4]+1; endelse sec1[3:0]<=sec1[3:0]+1; minclk<=0;endassign m_clk=minclk||count1;always @(posedge ct1) //分计时和分调整进程beginif(min1==8'h59) begin min1<=0; hclk<=1; endelse beginif(min1[3:0]==9)begin min1[3:0]<=0; min1[7:4]<=min1[7:4]+1; endelse min1[3:0]<=min1[3:0]+1; hclk<=0;endendassign h_clk=hclk||counta;always @(posedge cta) //小时计时和小时调整进程if(hour1==8'h23) hour1<=0;else if(hour1[3:0]==9)begin hour1[7:4]<=hour1[7:4]+1; hour1[3:0]<=0; endelse hour1[3:0]<=hour1[3:0]+1;always @(posedge ct2) //闹钟定时功能中的分钟调节进程if(amin==8'h59) amin<=0;else if(amin[3:0]==9)begin amin[3:0]<=0; amin[7:4]<=amin[7:4]+1; endelse amin[3:0]<=amin[3:0]+1;always @(posedge ctb) //闹钟定时功能中的小时调节进程if(ahour==8'h23) ahour<=0;else if(ahour[3:0]==9)begin ahour[3:0]<=0; ahour[7:4]<=ahour[7:4]+1; endelse ahour[3:0]<=ahour[3:0]+1;always //闹铃功能if((min1==amin)&&(hour1==ahour)&&(amin|ahour)&&(!change))- 67 -程序文本//若按住“change”键不放,可屏蔽闹铃音if(sec1<8'h20) alert1<=1; //控制闹铃的时间长短else alert1<=0;else alert1<=0;always //时、分、秒的显示控制case(m)3'b00: begin hour<=hour1; min<=min1; sec<=sec1; end//计时状态下的时、分、秒显示3'b01: begin hour<=ahour; min<=amin; sec<=8'hzz; end//定时状态下的时、分、秒显示3'b10: begin hour<=hour1; min<=min1; sec<=8'hzz; end//校时状态下的时、分、秒显示endcaseassign LD_alert=(ahour|amin)?1:0; //指示是否进行了闹铃定时assign alert=((alert1)?clk_1k&clk:0)|alert2; //产生闹铃音或整点报时音always //产生整点报时信号alert2beginif((min1==8'h59)&&(sec1>8'h54)||(!(min1|sec1)))if(sec1>8'h54) alert2<=ear&clk_1k; //产生短音else alert2<=!ear&clk_1k; //产生长音else alert2<=0;endendmodule。

基于Verilog HDL的闹钟设计

封面删除~你懂的摘要随着微电子技术、计算机技术、半导体技术的发展,很多传统的数字门电路的设计已经被可编程逻辑器件替代。

而对于传统的模拟控制技术,也被数字控制系统所取代。

数字系统在各个领域显示出了无穷的魅力与优势,如今已经被广泛应用于实际工程中。

本文利用Verilog HDL 语言自顶向下的设计方法设计多功能数字钟, 实现时、分、秒的计时和校时,以及整点报时和闹钟的功能。

突出了其作为硬件描述语言的良好的可读性、可移植性和易理解等优点, 并通过ModelSim SE 6.5 完成综合、仿真。

通过Verilog HDL语言完成数字钟的层次化设计。

关键词:数字电子时钟,有限状态机,功能仿真AbstractAs the microelectronics, computer technology, semiconductor technology, many traditional design of digital gate programmable logic device has been replaced. As for the traditional analog control, digital control systems have also been replaced. Digital systems in various fields has shown infinite charm and advantages, and now has been widely used in practical projects. In this paper, Verilog HDL, the design of top-down multi-functional digital clock designed to achieve the hours, minutes, seconds, time and school, as well as the whole point timekeeping and alarm functions. Highlighted as a hardware description language, good readability, portability and ease of understanding, etc., and through the ModelSim SE 6.5 complete the comprehensive, simulation. Completed by Verilog HDL, the level of the digital clock design.Key words: Digital electronic clock, finite state machine, functional simulation.目录第1章绪论 (1)1.1时钟的发展简史 (1)1.2设计目的 (1)1.3Verilog HDL硬件描述语言 (2)1.4Modelsim仿真工具 (5)第2章数字电路设计方法 (7)2.1数字系统设计简介 (7)2.2有限状态机 (9)第3章数字钟的层次化设计 (13)3.1功能要求 (13)3.2数字钟系统的工作原理 (13)3.3 模块的设计 (13)3.4程序设计 (14)第4章功能仿真 (19)4.1 仿真前准备 (19)4.2 功能仿真 (20)第5章总结 (23)参考文献 (26)第1章绪论1.1时钟的发展简史设计目的公元1300年以前,人类主要是利用天文现象和流动物质的连续运动来计时。

基于Verilog HDL多功能时钟的设计

基于Verilog HDL多功能时钟的设计本实验设计采用Verilog HDL语言进行的课程设计。

多功能时钟具有计时,调时,数字跑表功能。

代码如下:顶层模块:/*clk50mhz:输入频率为50mhzmadd:调时为分钟加数,高电平有效,秒表时为暂停信号;hadd:调试时为小时加数,高电平有效;rst :清零信号;mode1,mode2:模式开关,选择功能键;cout1……cout6:数码管输出;*/module clock(clk50mhz,madd,hadd,rst,mode1,mode2,cout1,cout2,cout3,cout4,cout5,cout6); input clk50mhz,madd,hadd,rst;input mode1,mode2;output reg [3:0] cout1,cout2,cout3,cout4,cout5,cout6;wire [3:0] a,b,c,d,e,f;wire [3:0]aa,bb,cc,dd,ee,ff;shizhong x2(clk50mhz,hadd,madd,rst,a,b,c,d,e,f);miaobiao x3(clk50mhz,madd,rst,aa,bb,cc,dd,ee,ff);always @(mode1 or mode2)beginif ({mode1,mode2}==2'b00)begin{cout1,cout2,cout3,cout4,cout5,cout6}<={f,e,d,c,b,a};endelse if({mode1,mode2}==2'b10)begin{cout1,cout2,cout3,cout4,cout5,cout6}<={ff,ee,dd,cc,bb,aa};endendendmodule子模块:时钟,调时模块:module shizhong(clk50mhz,hadd,madd,rst,a,b,c,d,e,f);input clk50mhz,rst,hadd,madd;output reg [3:0] a,b,c,d,e,f;reg [25:0]counter_1hz;wire clk1hz;assign clk1hz=counter_1hz[25];always@(posedge clk50mhz)begincounter_1hz<=(counter_1hz==50000000)?0:(counter_1hz+1);endalways@(posedge clk1hz)beginif(rst) begin {a,b,c,d,e,f}<=24'b0; endelse if(madd) begin c<=c+1;if(c==9) begin d<=d+1;c<=0; endif(d==5&&c==9) d<=0;endelse if(hadd) begin e<=e+1;if(e==9) begin f<=f+1;e<=0; endif(f==2&&e==4) begin f<=0;e<=0;endendelse beginif(a==9) begin a<=0;b<=b+1; end else a<=a+1;if(b==5&&a==9) begin c<=c+1;b<=0; endif(c ==9&&b==5&&a==9) begin d<=d+1;c<=0; endif((d==5&&c==9)&&(b==5&&a==9)) begin e<=e+1;d<=0; endif(e==9&&(d==5&&c==9)&&(b==5&&a==9)) begin f<=f+1; e<=0;endif((f==2&&e==3)&&(d==5&&c==9)&&(b==5&&a==9)) begin f<=0;e<=0; end endendendmodule子模块:秒表模块:module miaobiao(clk50mhz,madd,rst,aa,bb,cc,dd,ee,ff);input clk50mhz,madd,rst;output reg [3:0] aa,bb,cc,dd,ee,ff;reg [18:0]counter_100hz;wire clk100hz;assign clk100hz=counter_100hz[18];always@(posedge clk50mhz)begincounter_100hz<=(counter_100hz==500000)?0:(counter_100hz+1);endalways@(posedge clk100hz)beginbeginif(rst) begin {aa,bb,cc,dd,ee,ff}<=24'b0; endelse if(madd)beginif(aa==9) begin aa<=0;bb<=bb+1; end else aa<=aa+1;if(bb==9&&aa==9) begin cc<=cc+1;bb<=0; endif(cc==9&&bb==9&&aa==9) begin dd<=dd+1;cc<=0; endif((dd==5&&cc==9)&&(bb==9&&aa==9)) begin ee<=ee+1;dd<=0; endif(ee==9&&(dd==5&&cc==9)&&(bb==9&&aa==9)) begin ff<=ff+1; ee<=0;endif((ff==5&&ee==9)&&(dd==5&&cc==9)&&(bb==9&&aa==9)) begin ff<=0;ee<=0; end endendendendmodule。

用verilog-HDL多功能数字钟

用verilog-HDL多功能数字钟Verilog HDL实验报告基于Verilog HDL语言的多功能数字钟设计一、试验目的设计一个有如下功能的数字钟:(1)计时功能:包括时、分、秒。

(2)定时与闹钟功能:能在所设定的时间发出铃音。

(3)校时功能:对小时、分钟和秒钟进行手动校时。

(4)整点报时功能:每到整点能够发出“嘀嘀嘀嘀嘟”四短一长的报时。

二、试验原理ALERT HOUR[7..0]MIN[7..0]SEC[7..0]LD_ALERT LD_HOUR LD_MINCLK CLK_1K MODE TURN CHANGEclockCLK CLK_1K MODE TURN CHANGEALERTHOUR[7..0]MIN[7..0]SEC[7..0]LD_ALERT LD_HOUR LD_MIN多功能数字钟端口示意图数字钟设有五个输入端,分别为时钟输入(CLK )、模式(MODE )、产生声音的时钟信号(CLK_1K )、切换(TURN )和调时(CHANGE )键。

输出共七个,其中HOUR[7..0]、MIN[7..0]和SEC[7..0]采用BCD 计数方式,分别驱动2个数码管。

硬件电路原理图如下:三、试验内容1. 代码/*信号定义:clk: 标准时钟信号,其频率为4Hz;clk_1k:产生闹铃声、报时音的时钟信号,其频率为1024Hz;mode:功能控制信号;为0:计时功能;为1:闹钟功能;为2:手动校时功能;turn:接按键,在手动校时功能时,选择是调整小时还是分钟;若长时间按住改建,还可使秒信号清零,用于精确调时;change: 接按键,手动调整时,每按一次,计数器加1;如果长按,则连续快速加1,用于快速调时和定时;hour,min,sec:此三信号分别输出并显示时、分、秒信号,皆采用BCD码计数,分别驱动6个数码管显示时间;alert:输出到扬声器的信号,用于产生闹铃音和报时音;闹铃音为持续20秒的急促的“嘀嘀嘀”音,若按住“change”键,则可屏蔽该音;整点报时音为“嘀嘀嘀嘀嘟”四短一长音;LD_alert:接发光二极管,指示是否设置了闹钟功能;LD_hour:接发光二极管,指示当前调整的是小时信号;LD_min:接发光二极管,指示当前调整的是分钟信号*/moduleclock(clk,clk_1k,mode,change,turn,alert,hour,min,sec,LD_alert,LD_hour,LD_mi n);input clk,clk_1k,mode,change,turn;output alert,LD_alert,LD_hour,LD_min;output[7:0] hour,min,sec;reg[7:0] hour,min,sec,hour1,min1,sec1,ahour,amin;reg[1:0] m,fm,num1,num2,num3,num4;reg[1:0] loop1,loop2,loop3,loop4,sound;reg LD_hour,LD_min;reg clk_1Hz,clk_2Hz,minclk,hclk;reg alert1,alert2,ear;reg count1,count2,counta,countb;wire ct1,ct2,cta,ctb,m_clk,h_clk;always @(posedge clk)beginclk_2Hz<=~clk_2Hz;if(sound==3) begin sound<=0; ear<=1; end //ear信号用于产生或屏蔽声音else begin sound<=sound+1; ear<=0; endendalways @(posedge clk_2Hz) //由4Hz的输入时钟产生1Hz的时基信号clk_1Hz<=~clk_1Hz;always @(posedge mode) //mode信号控制系统在三种功能间转换begin if(m==2) m<=0; else m<=m+1; endalways @(posedge turn)fm<=~fm;always //产生count1,count2,counta,countb四个信号begincase(m)2:begin if(fm)begin count1<=change; {LD_min,LD_hour}<=2; endelsebegin counta<=change; {LD_min,LD_hour}<=1; end{count2,countb}<=0;end1:begin if(fm)begin count2<=change; {LD_min,LD_hour}<=2; endelsebegin countb<=change; {LD_min,LD_hour}<=1; end{count1,counta}<=2'b00;enddefault:{count1,count2,counta,countb,LD_min,LD_hour}<=0;endcaseendalways @(negedge clk) //如果长时间按下“change”键,则生成“num1”信号用于连续快速加1if(count2) beginif(loop2==3) num2<=1;elsebegin loop2<=loop2+1; num2<=0;endendelse begin loop2<=0; num2<=0; endalways @(negedge clk) //产生num2信号if(count1) beginif(loop3==3) num3<=1;elsebegin loop3<=loop3+1; num3<=0; endendelse begin loop3<=0; num3<=0; endalways @(negedge clk)if(counta) beginif(loop4==3) num4<=1;elsebegin loop4<=loop4+1; num4<=0; endendelse begin loop4<=0; num4<=0; endassign ct1=(num3&clk)|(!num3&m_clk); //ct1用于计时、校时中的分钟计数assign ct2=(num1&clk)|(!num1&count2); //ct2用于在定时状态下调整分钟信号assign cta=(num4&clk)|(!num4&h_clk); //cta用于计时、校时中的小时计数assign ctb=(num2&clk)|(!num2&countb); //ctb用于在定时状态下调整小时信号always @(posedge clk_1Hz) //秒计时和秒调整进程if(!(sec1^8'h59)|turn&(!m))beginsec1<=0;if(!(turn&(!m))) minclk<=1;end//按住“turn”按键一段时间,秒信号可清零,该功能用于手动精确调时else beginif(sec1[3:0]==4'b1001)begin sec1[3:0]<=4'b0000; sec1[7:4]<=sec1[7:4]+1; endelse sec1[3:0]<=sec1[3:0]+1; minclk<=0;endassign m_clk=minclk||count1;always @(posedge ct1) //分计时和分调整进程beginif(min1==8'h59) begin min1<=0; hclk<=1; endelse beginif(min1[3:0]==9)begin min1[3:0]<=0; min1[7:4]<=min1[7:4]+1; endelse min1[3:0]<=min1[3:0]+1; hclk<=0;endendassign h_clk=hclk||counta;always @(posedge cta) //小时计时和小时调整进程if(hour1==8'h23) hour1<=0;else if(hour1[3:0]==9)begin hour1[7:0]<=hour1[7:4]+1; hour1[3:0]<=0; endelse hour1[3:0]<=hour1[3:0]+1;always @(posedge ct2) //闹钟定时功能中的分钟调节进程if(amin==8'h59) amin<=0;else if(amin[3:0]==9)begin amin[3:0]<=0; amin[7:4]<=amin[7:4]+1; endelse amin[3:0]<=amin[3:0]+1;always @(posedge ctb) //闹钟定时功能中的小时调节进程if(ahour==8'h23) ahour<=0;else if(ahour[3:0]==9)begin ahour[3:0]<=0; ahour[7:4]<=ahour[7:4]+1; endelse ahour[3:0]<=ahour[3:0]+1;always //闹铃功能if((min1==amin)&&(hour1==ahour)&&(amin|ahour)&&(!change))//若按住“change”键不放,可屏蔽闹铃音if(sec1<8'h20) alert1<=1; //控制闹铃的时间长短else alert1<=0;else alert1<=0;always //时、分、秒的现实控制case(m)3'b00: begin hour<=hour1; min<=min1; sec<=sec1; end//计时状态下的时、分、秒显示3'b01: begin hour<=ahour; min<=amin; sec<=8'hzz; end//定时状态下的时、分、秒显示3'b10: begin hour<=hour1; min<=min1; sec<=8'hzz; end//校时状态下的时、分、秒显示endcaseassign LD_alert=(ahour|amin)?1:0; //指示是否进行了闹铃定时assign alert=((alert1)?clk_1k&clk:0)|alert2; //产生闹铃音或整点报时音always //产生整点报时信号alert2beginif((min1==8'h59)&&(sec1>8'h54)||(!(min1|sec1)))if(sec1>8'h54) alert2<=ear&clk_1k; //产生短音else alert2<=!ear&clk_1k; //产生长音else alert2<=0;endendmodule2. 仿真图四、小结及体会为了做多功能数字钟,我借了多本关于Verilog HDL的程序设计书。

课程设计---基于Verilog HDL数字时钟设计与实现

课程设计---基于Verilog HDL数字时钟设

计与实现

简介

本课程设计旨在通过使用Verilog硬件描述语言(HDL)设计和实现数字时钟。

学生将研究如何使用Verilog语言来描述数字电路,并将其应用于设计和实现一个简单的数字时钟电路。

设计目标

- 研究使用Verilog HDL来描述和设计数字电路

- 实现一个简单的数字时钟电路

- 熟悉数字时钟的工作原理和设计流程

实施步骤

1. 了解数字时钟的原理和工作方式

2. 研究Verilog HDL语言的基本语法和使用方法

3. 设计并实现时钟的各个功能模块,如时钟显示模块、时钟计数模块等

4. 使用仿真工具验证设计的正确性

5. 进行实际的硬件验证,将设计烧录到FPGA开发板上并进行测试

实验要求

1. 设计的数字时钟应具备基本的时分秒显示功能

2. 时钟应具备可调节的时间设置功能

3. 需要使用FPGA开发板进行实际硬件验证

4. 实验报告应包含设计原理、设计流程、仿真结果和实际硬件验证结果

参考资料

1. Verilog HDL教程

2. FPGA开发板用户手册

3. 相关学术论文和文献

以上为课程设计---基于Verilog HDL数字时钟设计与实现的文档简介。

本课程设计将帮助学生学习Verilog HDL语言并应用于设计和实现数字时钟电路。

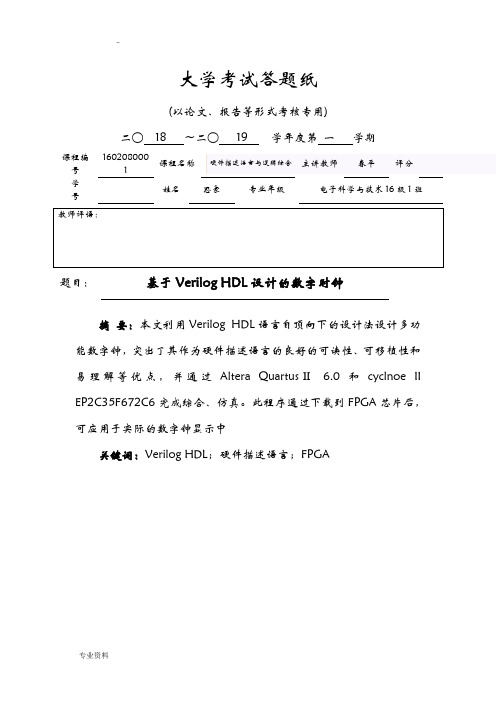

基于veriloghdl设计的数字时钟

大学考试答题纸(以论文、报告等形式考核专用)二○ 18 ~二○ 19 学年度第 一 学期 课程编号 1602080001课程名称 学 号姓名 思豪 专业年级 电子科学与技术16级1班题目:基于Verilog HDL 设计的数字时钟摘 要:本文利用Verilog HDL 语言自顶向下的设计法设计多功能数字钟,突出了其作为硬件描述语言的良好的可读性、可移植性和易理解等优点,并通过Altera Quartus Ⅱ 6.0和cyclnoe II EP2C35F672C6完成综合、仿真。

此程序通过下载到FPGA 芯片后,可应用于实际的数字钟显示中关键词:Verilog HDL ;硬件描述语言;FPGA目录一、实验任务 (3)实验目的 (3)实验要求 (3)二、设计思路 (3)三、实验结果 (10)四、总结与收获 (14)一、实验任务实验目的1.深入了解基于quartus ii工具的复杂时序逻辑电路的设计。

2.理解并熟练利用EDA工具进行综合设计。

3.熟练掌握芯片烧录的流程及步骤。

4.掌握Verilog HDL 语言的语法规及时序电路描述法。

实验要求设计一个带秒表功能的24 小时数字钟,它包括以下几个组成部分:①显示屏,由6 个七段数码管组成,用于显示当前时间(时:分,秒)或设置的秒表时间;②复位键复位所有显示和计数③设置键,用于确定新的时间设置,三个消抖按键分别用于时分秒的设置④秒表键,用于切换成秒表功能基本要求(1) 计时功能:这是本计时器设计的基本功能,每隔一秒计时一次,并在显示屏上显示当前时间。

(2) 秒表功能:设置时间,进行倒计时功能(3) 设置新的计时器时间:按下设置键后,用户能通过时分秒三个消抖按键对时间进行设置。

二、设计思路1、总原理框图:原理如上图所示,时钟由分频器模块,数码管显示模块,计时器模块三个模块构成,每个模块实现如下的不同功能,最后通过在顶层模块的调用,来实现时钟功能。

2.顶层模块:顶层模块调用三个字模块,并且定义输入输出口,代码输入所示:modulemyclock2(daojishi,stop,clk,reset,shi,fen,miao,miaoout1,miaoout2,fenout1,fenout2,shiout1,s hiout2);input clk,reset,stop,shi,fen,miao,daojishi;output[6:0] miaoout1,miaoout2,fenout1,fenout2,shiout1,shiout2;wire[3:0] miao1,miao2,fen1,fen2,shi1,shi2;wire clk_1hz;divider_1HZ divider1hz(clk_1hz,reset,clk);count count1(daojishi,shi,fen,miao,stop,miao1,miao2,fen1,fen2,shi1,shi2,reset,clk_1hz); decode4_7 d0(miaoout1,miao1);decode4_7 d1(miaoout2,miao2);decode4_7 d2(fenout1,fen1);decode4_7 d3(fenout2,fen2);decode4_7 d4(shiout1,shi1);decode4_7 d5(shiout2,shi2);endmodule输入输出端口类型功能表:三个子模块的原理和代码:(1)分频模块:分频模块的作用主要是要获得各种频率的时钟信号。

基于Verilog HDL设计的数字时钟

深圳大学考试答题纸(以论文、报告等形式考核专用)二○18 ~二○19 学年度第一学期课程编1602080001 评分刘春平课程名称主讲教师硬件描述语言与逻辑综合号学电子科学与技术16级1班姓名李思豪专业年级号设计的数字时钟Verilog HDL基于题目:摘要:本文利用V erilog HDL语言自顶向下的设计方法设计多功能数字钟,突出了其作为硬件描述语言的良好的可读性、可移植性和易理解等优点,并通过Altera QuartusⅡ6.0和cyclnoe IIEP2C35F672C6完成综合、仿真。

此程序通过下载到FPGA芯片后,可应用于实际的数字钟显示中关键词:Verilog HDL;硬件描述语言;FPGA1目录一、实验任务 (3)实验目的 (3)实验要求 (3)二、设计思路 (3)三、实验结果 (10)四、总结与收获 (14)2一、实验任务实验目的1.深入了解基于quartus ii工具的复杂时序逻辑电路的设计。

理解并熟练利用EDA工具进行综合设计。

2.熟练掌握芯片烧录的流程及步骤。

3.掌握Verilog HDL 语言的语法规范及时序电路描述方法。

4.实验要求设计一个带秒表功能的24 小时数字钟,它包括以下几个组成部分:①显示屏,由6 个七段数码管组成,用于显示当前时间(时:分,秒)或设置的秒表时间;②复位键复位所有显示和计数③设置键,用于确定新的时间设置,三个消抖按键分别用于时分秒的设置④秒表键,用于切换成秒表功能基本要求(1) 计时功能:这是本计时器设计的基本功能,每隔一秒计时一次,并在显示屏上显示当前时间。

(2) 秒表功能:设置时间,进行倒计时功能(3) 设置新的计时器时间:按下设置键后,用户能通过时分秒三个消抖按键对时间进行设置。

二、设计思路、总原理框图:13原理如上图所示,时钟由分频器模块,数码管显示模块,计时器模块三个模块构成,每个模块实现如下的不同功能,最后通过在顶层模块的调用,来实现时钟功能。

数字系统设计与verilog_HDL课程设计--实用多功能数字钟

数字系统设计与verilogHDL课程设计设计题目:实用多功能数字钟专业:电子信息科学与技术摘要本课程设计利用QuartusII软件Verilog VHDL语言的基本运用设计一个多功能数字钟,经分析采用模块化设计方法,分别是顶层模块、alarm、alarm_time、counter_time、clk50mto1、led、switch、bitel、adder、sound_ddd、sound_ddd_du模块,再进行试验设计和软件仿真调试,分别实现时分秒计时、闹钟闹铃、时分秒手动校时、时分秒清零,时间保持和整点报时等多种基本功能。

单个模块调试达到预期目标,再将整体模块进行试验设计和软件仿真调试,已完全达到分块模式设计功能,并达到设计目标要求。

关键字:多功能数字钟、Verilog、模块、调试、仿真、功能目录1.课程设计的目的及任务............................................................. 错误!未定义书签。

1.1 课程设计的目的 (4)1.2 课程设计的任务与要求 (4)2.课程设计思路及其原理 (4)3.QuartusII软件的应用 (5)3.1工程建立及存盘 (5)3.2工程项目的编译 (6)3.3时序仿真 (6)4.分模块设计、调试、仿真与结果分析 (7)4.1 clk50mto1时钟分频模块 (7)4.2 adder加法器模块 (7)4.3 hexcounter16 进制计数器模块 (8)4.4 counter_time 计时模块 (8)4.5 alarm闹铃模块 (9)4.6 sound_ddd嘀嘀嘀闹铃声模块 (9)4.7 sound_ddd_du嘀嘀嘀—嘟声音模块 (10)4.8 alarm_time闹钟时间设定模块 (10)4.9 bitsel将输出解码成时分秒选择模块 (11)4.10 switch去抖模块 (11)4.11 led译码显示模块 (12)4.12 clock顶层模块 (12)5.实验总结 (14)5.1调试中遇到的问题及解决的方法 (14)5.2实验中积累的经验 (14)5.3心得体会 (14)6.参考文献 (15)1.1 课程设计的目的通过课程设计的锻炼,要求学生掌握V erilog HDL语言的一般设计方法,掌握VerilogHDL语言的基本运用,具备初步的独立设计能力,提高综合运用所学的理论知识独立分析和解决问题的能力,基于实践、源于实践,实践出真知,实践检验真理,培养学生的创新精神。

基于verilogHDL的数字时钟

*****顶层模块信号定义:clk : 基准时钟信号输入;keysel : 校时状态/正常计时状态选择键输入;key_s : 校秒信号选择键输入;key_m : 校分信号选择键输入;key_h : 校时信号选择键输入;keyclr : 计时清零键;keyen : 计时开始键;buzzout : 声响输出;sled : 4位数码管段码输出;sl : 4位数码管位码输出;seg : 单个数码管输出;********************************************************* ******/moduleclock(clk,keysel,key_s,key_m,key_h,keyen,keyclr,sled,sl,seg,buzzout);output[7:0] sled;output[3:0] sl;output[7:0] seg;output buzzout;input clk;input keysel,key_s,key_m,key_h,keyen,keyclr;reg[24:0] count;wire[23:0] min;wire sec;wire sec_s,sec_m,sec_h,sec_narmal;divclk Q1(clk,sec_narmal,sec_s,sec_m,sec_h);modifyQ2(clk,keysel,key_s,key_m,key_h,sec,sec_narmal,sec_s,sec_m,sec_h);counttime Q3(sec,keyclr,keyen,min);display Q4(clk,sec,min,sled,sl,seg);music Q5(clk,min,buzzout,sec_narmal);endmodule*****分频模块信号定义:clk : 基准时钟信号输入;sec_narmal : 周期为1的信号输出;sec_s : 周期为0.5s的信号输出;sec_m : 周期为0.05s的信号输出;sec_h : 周期为0.0005s的信号输出;********************************************************* ******/module divclk(clk,sec_narmal,sec_s,sec_m,sec_h);input clk;output sec_narmal,sec_s,sec_m,sec_h;reg[23:0] count1;reg[22:0] count2;reg[19:0] count3;reg[12:0] count4;reg sec_narmal,sec_s,sec_m,sec_h;always@(negedge clk)begincount1=count1+1'b1;if(count1==24'd1*******)begincount1=24'h0;sec_narmal=~sec_narmal;endendalways@(negedge clk)begincount2=count2+1'b1;if(count2==23'd6000000)begincount2=23'h0;sec_s=~sec_s;endendalways@(negedge clk)begincount3=count3+1'b1;if(count3==20'd600000)begincount3=20'h0;sec_m=~sec_m;endendalways@(negedge clk)begincount4=count4+1'b1;if(count4==13'd6000)begincount4=13'h0;sec_h=~sec_h;endendendmodule/********************************************************* *****计时处理模块信号定义:sec : 计时信号输入;keyclr : 计时清零键;keyen : 计时开始键;min : 计时结果输出;********************************************************* ******/module counttime(sec,keyclr,keyen,min);input sec;input keyclr,keyen;output[23:0] min;reg[23:0] min;always@(posedge sec)beginif(!keyclr)beginmin=24'h0;endelseif(!keyen)beginmin=min+1'b1;if(min[3:0]==4'ha)beginmin[3:0]=4'h0;min[7:4]=min[7:4]+1'b1;if(min[7:4]==4'h6)beginmin[7:4]=4'h0;min[11:8]=min[11:8]+1'b1;if(min[11:8]==4'ha)beginmin[11:8]=4'h0;min[15:12]=min[15:12]+1'b1;if(min[15:12]==4'h6)beginmin[15:12]=4'h0;min[19:16]=min[19:16]+1'b1;if(min[19:16]==4'ha)beginmin[19:16]=4'h0;min[23:20]=min[23:20]+1'b1;endif(min[23:16]==8'h24)min[23:16]=0;endendendendendendendmodule/********************************************************* *****校时模块信号定义:clk : 基准时钟信号输入;keysel : 校时状态/正常计时状态选择键输入key_s : 校秒信号选择键输入key_m : 校分信号选择键输入key_h : 校时信号选择键输入sec_narmal : 周期为1的信号输出;sec_s : 周期为0.5s的信号输出;sec_m : 周期为0.05s的信号输出;sec_h : 周期为0.0005s的信号输出;sec : 计时信号输出;********************************************************* ******/modulemodify(clk,keysel,key_s,key_m,key_h,sec,sec_narmal,sec_s,sec_m,sec _h);input clk;input keysel;input key_s,key_m,key_h;input sec_narmal,sec_s,sec_m,sec_h;output sec;reg sec;always@(negedge clk)beginif(!keysel)beginif(!key_s)sec=sec_s;if(!key_m)sec=sec_m;if(!key_h)sec=sec_h;endelsesec=sec_narmal;endendmodule/********************************************************* *****报时模块信号定义:clk : 基准时钟信号输入;min : 当前计时结果输入;buzzout : 声响输出;********************************************************* ******/module music(clk,min,buzzout,sec_narmal);input clk,sec_narmal;input[23:0] min;output buzzout;reg[3:0] high,med,low;reg buzzout_reg;reg[24:0] count1,count2;reg[15:0] count_end,count_now;reg[7:0] counter;reg clk_4HZ;always@(posedge clk)beginif(count1<22'd3000000)count1=count1+1'b1;elsebegincount1=0;clk_4HZ=~clk_4HZ;endendalways@(posedge clk)beginif(count_now!=count_end)begincount2=25'h0;count_now=count_end;endcount2=count2+1'b1;if((min[15:0]>=16'h5945)&&(min[15:0]<=16'h5959))beginif((count2==count_end)&&(min[23:16]==8'h11))begincount2=25'h0;buzzout_reg=!buzzout_reg;endendif((min[15:0]>=16'h5950)&&(min[15:0]<=16'h5959)) beginif(min[23:16]!=8'h11)beginbuzzout_reg=!(count2[10]&sec_narmal);endendendalways@(posedge clk_4HZ)begincase({high,med,low})9'b000000001:count_end=16'hbb9a;9'b000000010:count_end=16'ha72f;9'b000000011:count_end=16'h94f2;9'b000000100:count_end=16'h8e78;9'b000000101:count_end=16'h7d63;9'b000000110:count_end=16'h6fb5;9'b000000111:count_end=16'h637f;9'b000001000:count_end=16'h5dfb;9'b000010000:count_end=16'h53bb;9'b000011000:count_end=16'h4a95;9'b000100000:count_end=16'h4651;9'b000101000:count_end=16'h3eb1;9'b000110000:count_end=16'h37da;9'b000111000:count_end=16'h31bf;9'b001000000:count_end=16'h2ef2;9'b010000000:count_end=16'h29d4;9'b011000000:count_end=16'h2543;9'b100000000:count_end=16'h232f;9'b101000000:count_end=16'h1f58;9'b110000000:count_end=16'h1bed;9'b111000000:count_end=16'h18df;endcaseendalways@(posedge clk_4HZ)beginif(counter==57)counter=0;elsecounter=counter+1'b1;case(counter)0:{high,med,low}=9'b000001000;1:{high,med,low}=9'b000001000;2:{high,med,low}=9'b000001000;3:{high,med,low}=9'b000001000;4:{high,med,low}=9'b000010000;5:{high,med,low}=9'b000010000;6:{high,med,low}=9'b000010000;7:{high,med,low}=9'b000010000;8:{high,med,low}=9'b000011000;9:{high,med,low}=9'b000011000;10:{high,med,low}=9'b000011000;11:{high,med,low}=9'b000011000;12:{high,med,low}=9'b000001000;13:{high,med,low}=9'b000001000;14:{high,med,low}=9'b000001000;15:{high,med,low}=9'b000001000;16:{high,med,low}=9'b000001000;17:{high,med,low}=9'b000001000;19:{high,med,low}=9'b000001000; 20:{high,med,low}=9'b000010000; 21:{high,med,low}=9'b000010000; 22:{high,med,low}=9'b000010000; 23:{high,med,low}=9'b000010000; 24:{high,med,low}=9'b000011000; 25:{high,med,low}=9'b000011000; 26:{high,med,low}=9'b000011000; 27:{high,med,low}=9'b000011000; 28:{high,med,low}=9'b000001000; 29:{high,med,low}=9'b000001000; 30:{high,med,low}=9'b000001000; 31:{high,med,low}=9'b000001000; 32:{high,med,low}=9'b000011000; 33:{high,med,low}=9'b000011000; 34:{high,med,low}=9'b000011000; 35:{high,med,low}=9'b000011000; 36:{high,med,low}=9'b000100000; 37:{high,med,low}=9'b000100000; 38:{high,med,low}=9'b000100000; 39:{high,med,low}=9'b000100000; 40:{high,med,low}=9'b000101000; 41:{high,med,low}=9'b000101000; 42:{high,med,low}=9'b000101000; 43:{high,med,low}=9'b000101000; 44:{high,med,low}=9'b000001000; 45:{high,med,low}=9'b000001000; 46:{high,med,low}=9'b000001000; 47:{high,med,low}=9'b000011000; 48:{high,med,low}=9'b000011000; 49:{high,med,low}=9'b000011000; 50:{high,med,low}=9'b000011000; 51:{high,med,low}=9'b000100000; 52:{high,med,low}=9'b000100000; 53:{high,med,low}=9'b000100000; 54:{high,med,low}=9'b000100000;56:{high,med,low}=9'b000101000;57:{high,med,low}=9'b000101000;endcaseendassign buzzout=buzzout_reg;endmodule/********************************************************* *****显示模块信号定义:clk : 基准时钟信号输入;min : 当前计时结果输入;sec : 计时的秒信号输入;sled_reg : 数码管短码输出;sl_reg : 数码管位码输出;seg_reg : 单个数码管输出;********************************************************* ******/module display(clk,sec,min,sled_reg,sl_reg,seg_reg);input clk;input sec;input[23:0] min;output[7:0] sled_reg;output[3:0] sl_reg;output[7:0] seg_reg;reg[7:0] sled_reg;reg[3:0] sl_reg;reg[7:0] seg_reg;reg[15:0] count;reg[3:0] ledbuf;always@(negedge clk)begincount=count+1'b1;endalways@(count[11:10])begincase(count[11:10])2'h0:ledbuf=min[3:0];2'h1:ledbuf=min[7:4];2'h2:ledbuf=min[11:8];2'h3:ledbuf=min[15:12];endcasecase(count[11:10])2'h0:sl_reg=4'b0111;2'h1:sl_reg=4'b1011;2'h2:sl_reg=4'b1101;2'h3:sl_reg=4'b1110;endcaseendalways@(ledbuf)begincase(ledbuf)4'h0:sled_reg=8'hc0;4'h1:sled_reg=8'hf9;4'h2:sled_reg=8'ha4;4'h3:sled_reg=8'hb0;4'h4:sled_reg=8'h99;4'h5:sled_reg=8'h92;4'h6:sled_reg=8'h82;4'h7:sled_reg=8'hf8;4'h8:sled_reg=8'h80;4'h9:sled_reg=8'h90;4'ha:sled_reg=8'h88;4'hb:sled_reg=8'h83;4'hc:sled_reg=8'hc6;4'hd:sled_reg=8'ha1;4'he:sled_reg=8'h86;4'hf:sled_reg=8'h8e;endcaseif((count[11:10]==2'b10)&sec)sled_reg=sled_reg&8'h7f; endalways@(min[23:16])begincase(min[23:16])8'h0:seg_reg=8'h3f;8'h1:seg_reg=8'h06;8'h2:seg_reg=8'h5b;8'h3:seg_reg=8'h4f;8'h4:seg_reg=8'h66;8'h5:seg_reg=8'h6d;8'h6:seg_reg=8'h7d;8'h7:seg_reg=8'h07;8'h8:seg_reg=8'h7f;8'h9:seg_reg=8'h6f;8'h10:seg_reg=8'h77;8'h11:seg_reg=8'h7c;8'h12:seg_reg=8'hbf;8'h13:seg_reg=8'h86;8'h14:seg_reg=8'hdb;8'h15:seg_reg=8'hcf;8'h16:seg_reg=8'he6;8'h17:seg_reg=8'hed;8'h18:seg_reg=8'hfd;8'h19:seg_reg=8'h87;8'h20:seg_reg=8'hff;8'h21:seg_reg=8'hef;8'h22:seg_reg=8'hf7;8'h23:seg_reg=8'hfc;endcaseendendmodule。

基于Verilog HDL设计的数字时钟

深圳大学考试答题纸(以论文、报告等形式考核专用)二○18 ~二○19 学年度第一学期课程编1602080001 课程名称号学姓名李思豪专业年级电子科学与技术16级1班号题目:基于Verilog HDL设计的数字时钟摘要:本文利用Verilog HDL语言自顶向下的设计方法设计多功能数字钟,突出了其作为硬件描述语言的良好的可读性、可移植性和易理解等优点,并通过Altera QuartusⅡ 6.0和cyclnoe II EP2C35F672C6完成综合、仿真。

此程序通过下载到FPGA芯片后,可应用于实际的数字钟显示中关键词:Verilog HDL;硬件描述语言;FPGA目录一、实验任务 (3)实验目的 (3)实验要求 (3)二、设计思路 (3)三、实验结果 (10)四、总结与收获 (14)一、实验任务实验目的1.深入了解基于quartus ii工具的复杂时序逻辑电路的设计。

2.理解并熟练利用EDA工具进行综合设计。

3.熟练掌握芯片烧录的流程及步骤。

4.掌握Verilog HDL 语言的语法规范及时序电路描述方法。

实验要求设计一个带秒表功能的24 小时数字钟,它包括以下几个组成部分:①显示屏,由6 个七段数码管组成,用于显示当前时间(时:分,秒)或设置的秒表时间;②复位键复位所有显示和计数③设置键,用于确定新的时间设置,三个消抖按键分别用于时分秒的设置④秒表键,用于切换成秒表功能基本要求(1) 计时功能:这是本计时器设计的基本功能,每隔一秒计时一次,并在显示屏上显示当前时间。

(2) 秒表功能:设置时间,进行倒计时功能(3) 设置新的计时器时间:按下设置键后,用户能通过时分秒三个消抖按键对时间进行设置。

二、设计思路1、总原理框图:原理如上图所示,时钟由分频器模块,数码管显示模块,计时器模块三个模块构成,每个模块实现如下的不同功能,最后通过在顶层模块的调用,来实现时钟功能。

2.顶层模块:顶层模块调用三个字模块,并且定义输入输出口,代码输入所示:modulemyclock2(daojishi,stop,clk,reset,shi,fen,miao,miaoout1,miaoout2,fenout1,fenout2,shiout1,shiout2) ;input clk,reset,stop,shi,fen,miao,daojishi;output[6:0] miaoout1,miaoout2,fenout1,fenout2,shiout1,shiout2;wire[3:0] miao1,miao2,fen1,fen2,shi1,shi2;wire clk_1hz;divider_1HZ divider1hz(clk_1hz,reset,clk);count count1(daojishi,shi,fen,miao,stop,miao1,miao2,fen1,fen2,shi1,shi2,reset,clk_1hz); decode4_7 d0(miaoout1,miao1);decode4_7 d1(miaoout2,miao2);decode4_7 d2(fenout1,fen1);decode4_7 d3(fenout2,fen2);decode4_7 d4(shiout1,shi1);decode4_7 d5(shiout2,shi2);endmodule输入输出端口类型功能表:三个子模块的原理和代码:(1)分频模块:分频模块的作用主要是要获得各种频率的时钟信号。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

3' b101: Disp_Temp=4' b1010;

#(60000*HALF_PERIOD) S1_in=1;

3' b110: Disp_Temp=SECH;

end

3' b111: Disp_Temp=SECL;

//产 生 调 节 分 钟 信 号

endcase

initial

end

begin

always@(Disp_Temp) //显示转换

新

图 1 多功能数字钟端口功能图

Clk: 10KHZ 的系统基准时钟输入。作为七段码管 扫描频率。将其 10000 分频可得到 1HZ 的数字钟工作 频率。将其 8 分频和 4 分频分别分时送入扬声器, 使 其产生嘀( 1.25KHZ) 、嗒( 2.5KHZ) 的报时声。

Rst: 系统复位信号, 低电平有效。复位后显示 00- 00- 00。

Abstr act: In this paper, the process of designing multifunctional digital clock by the Verilog HDL top- down design method is pre- sented, which has shown the readability, portability and easily understanding of Verilog HDL as a hard description language. Circuit synthesis and simulation are performed by Altera QuartusⅡ 4.1 and ModelSim SE 6.0. The program can be used in the truly digital clock display by downloading to the FPGA chip. Keywor ds: Ver ilog HDL; har dwar e descr iption language; FPGA

//产 生 调 节 小 时 信 号

3' b001: Disp_Temp=HOURL;

initial

3' b010: Disp_Temp=4' b1010;

begin

3' b011: Disp_Temp=MINH;

S1_in=1;

3' b100: Disp_Temp=MINL;

#(35000*HALF_PERIOD) S1_in=0;

//产生 10KHZ 时钟 initial

术

else Spk<=0; end

begin

Clk_in=0;

创

else if(MINH==0 && MINL==0 && SECH==0 && SECL==0)

Forever #HALF_PERIOD Clk_in= ̄Clk_in; end

新

//产生复位信号

您的论文得到两院院士关注 文章编号:1008- 0570(2006)04- 2- 0079- 03

片 上 系 统 SOC

基于 Ve rilo g HDL 设计的多功能数字钟

De s ig n o f Mu ltifu n ctio n a l Dig ita l Clo ck Ba s e d o n Ve rilo g HDL

else MINL<=MINL+1;

4' b1010: Display=7' b1000000; //-

end

default: Display=7' b0000000; //全灭

else SECH<=SECH+1;

endcase

end else SECL<=SECL+1;

end endmodule

end

体公司使用, 成为一种强大的设计工具。该数字钟就

是采用 Verilog HDL 描述。

模块源代码如下:

module clock(Clk,Rst,S1,S2,Display,Sel,Spk);

input Clk;

//产生 10KHZ 时钟输入

input Rst;

//复位输入

input S1;

//小时调节输入

本文提出了以 Verilog HDL 语言为手段, 设计了 多功能数字钟。其代码具有良好的可读性和易理解 性, 源程序经 Altera 公司的 QuartusⅡ 4.1 和 ModelSim SE 6.0 软件完成综合、仿真, 目标器件选用 Altera Cy- clone EP1C6Q240C8 器件。

Verilog HDL 是 工 业 和 学 术 界 的 硬 件 设 计 者 所 使 用的两种主要的 HDL 之一, 另一种是 VHDL。现在它 们 都 已 成 为 IEEE 标 准 。 两 者 各 有 特 点 , 但 Verilog HDL 拥 有 更 悠 久 的 历 史 、更 广 泛 的 设 计 群 体 , 资 源 也 远比 VHDL 丰富, 且非常容易学习掌握。

- 80 - 360元 / 年 邮局订阅号: 82-946

《 现场总线技术应用 200 例》

您的论文得到两院院士关注

片 上 系 统 SOC

HOURH<=0;

4' b0100: Display=7' b1100110; //4

end

4' b0101: Display=7' b1101101; //5

else HOURL<=HOURL+1;

4' b0110: Display=7' b1111101; //6

end

4' b0111: Display=7' b0000111; //7

else MINH<=MINH+1;

4' b1000: Display=7' b1111111; //8

end

4' b1001: Display=7' b1101111; //9

技 术

1 引言

功能。下面介绍一下各主要引脚的功能:

创

硬件描述语言 HDL ( Hardware Des- cription Lan- guage) 是一种用形式化方法来描述数字电路和系统的 语言。目前, 电子系统向集成化、大规模和高速度等方 向发展, 以硬件描述语言和逻辑综合为基础的自顶向 下的电路设计方法在业界得到迅猛发展, HDL 在这种 形势下显示出了巨大的优势, 展望将来 HDL 在硬件设 计 领 域 的 地 位 将 与 C 和 C++在 软 件 设 计 领 域 的 地 位 一样, 在大规模数字系统的设计中, 它将逐步取代传 统的逻辑状态表和逻辑电路图等硬件描述方法, 而成 为主要的硬件描述工具。

//系统复位

begin

SECL<=0;

SECH<=0;

MINL<=0;

MINH<=0;

HOURL<=0;

HOURH<=0;

end

else

begin

if(! S1) //调节小时 begin if(HOURL==9) begin HOURL<=0; HOURH<=HOURH+1; end else begin if(HOURH==2&& HOURL==3) begin HOURL<=0; HOURH<=0; end else HOURL<=HOURL+1; end end else if(! S2) //调节分钟 begin if(MINL==9) begin MINL<=0; if(MINH==5) MINH<=0; else MINH<=MINH+1; end else MINL<=MINL+1; end else if(SECL==9) //一般运行状态 begin SECL<=0; if(SECH==5) begin SECH<=0; if(MINL==9) begin MINL<=0; if(MINH==5) begin MINH<=0; if(HOURL==9) begin HOURL<=0; HOURH<=HOURH+1; end else if(HOURH==2 && HOURL==3) begin HOURL<=0;

片 上 系 统 SOC

中 文 核 心 期 刊《 微 计 算 机 信 息 》( 嵌 入 式 与 S OC )2006 年 第 22 卷 第 4-2 期

3 程序设计

Verilog HDL 语言具有结 构 清 晰 、文 法 简 明 、功 能

强 大 、高 速 模 拟 和 多 库 支 持 等 优 点 , 被 近 90%的 半 导

Spk: 输出到扬声器, 产生嘀、嗒的报时声。 Sel: 七段码管扫描驱动。因为是八个七段码 管, 所以 Sel 为三位总线。扫描频率为 10KHZ, 由于人眼的 视觉效果, 呈现在眼前的便是整体的时- 分- 秒显示。 Display: 七段码管显示输出。

《 P LC 技术应用 200 例》

邮局订阅号: 82-946 360 元 / 年 - 79 -

Spk<=Music_Count[1]; //嗒

initial

else Spk<=0;

begin

end

Rst_in=1;

always@(Sel)

#(2*HALF_PERIOD) Rst_in=0;

begin

#(10*HALF_PERIOD) Rst_in=1;

case(Sel)

end

3' b000: Disp_Temp=HOURH;

器

术

reg Clk_1HZ;

创 reg[2:0] Music_Count; //产生扬声器声音频率的分 频计数器

新

reg[3:0] SECL,SECH;

reg[3:0] MINL,MINH;

reg[3:0] HOURL,HOURH;

reg[3:0] Disp_Temp;

always@(posedge Clk)

(天津工业大学) 李 俊 一 牛 萍 娟

Li, J unyi Niu ,P ingjuan