7 实验七计数器

实验七同步机构报告

实验七:同步机构实验报告一、实习内容模拟实现用同步机构避免发生进程执行时可能出现的与时间有关的错误。

二、实习目的进程是程序在一个数据集合上运行的过程,进程是并发执行的,也即系统中的多个进程轮流地占用处理器运行。

我们把若干个进程都能进行访问和修改的那些变量称为公共变量。

由于进程是并发地执行的,所以,如果对进程访问公共变量不加限制,那么就会产生“与时间有关”的错误,即进程执行后所得到的结果与访问公共变量的时间有关。

为了防止这类错误,系统必须要用同步机构来控制进程对公共变量的访问。

一般说,同步机构是由若干条原语——同步原语——所组成。

本实习要求学生模拟PV操作同步机构的实现,模拟进程的并发执行,了解进程并发执行时同步机构的作用。

三、实习题目模拟PV操作同步机构,且用PV操作解决生产者——消费者问题。

[提示]:(1) PV操作同步机构,由P操作原语和V操作原语组成,它们的定义如下:P操作原语P (s):将信号量s减去1,若结果小于0,则执行原语的进程被置成等待信号量s的状态。

V操作原语V (s):将信号量s加1,若结果不大于0,则释放一个等待信号量s的进程。

这两条原语是如下的两个过程:procedure p (var s: semaphore);begin s: = s-1;if s<0 then W (s)end {p}procedure v (var s: semaphore);egin s: = s+1;if s 0 then R (s)end {v}其中W(s)表示将调用过程的进程置为等待信号量s的状态;R(s)表示释放一个等待信号量s的进程。

在系统初始化时应把semaphore定义为某个类型,为简单起见,在模拟实习中可把上述的semaphore直接改成integer。

(2) 生产者——消费者问题。

假定有一个生产者和一个消费者,生产者每次生产一件产品,并把生产的产品存入共享缓冲器以供消费者取走使用。

实验七微生物数量的测定

实验七微生物数量的测定一、实验目的1.掌握在液态和固态培养基上进行微生物计数的方法。

2.掌握稀释系数的计算方法。

3.了解红外辐射计数器的检测功能和操作方法。

二、实验原理在液体培养基上进行微生物计数的方法属于定量分析中的一项基本技术,其主要原理为先将微生物和加有营养物质的液体平均混合,然后分别取出适当体积,经过一定的稀释,将其等量分配到不同的培养皿内,然后在液体培养基上进行生长,最后根据各个培养皿内微生物生长的数量来计算初始菌落的数目。

其中,常用的标准液体培养基有肉汤、营养琼脂、拟南芥培养基等。

但该方法存在的问题在于,微生物生长的速度会因培养基的不同而有很大区别,如在肉汤培养基上生长较慢,需要长达24小时才能形成充分的菌落,而在营养琼脂培养基上生长则较快,并且易于观察。

此外,该方法要求使用无菌技术,并且在取样时需要注意尽量避免空气中污染菌落的产生,否则将会导致不准确的计数结果。

2.微生物计数固体培养基法在固体培养基上进行微生物计数的方法是将微生物标本均匀涂于固体培养基上,然后生长出菌落进行计数。

与液体培养基相比,该方法在菌落的形成方面更直观,且繁殖数目相对更多,故计数更为准确。

常用的固体培养基有营养琼脂、马铃薯葡萄糖琼脂、血液琼脂等。

但该方法存在的问题在于,菌落大小、形状、颜色等因素均可能影响计数结果,在计数时需要注意与目测直接形状相同的菌落合并计算,否则会造成漏计或重复计数的情况。

稀释是将一定量的菌液,通过逐步加入相等体积的稀释液而逐渐降低其菌落总体载量的过程。

通过分析稀释液与菌落的比例,就可以得到相对菌落的绝对数量。

其中,稀释系数是指菌液按递减顺序与相应稀释液的混合比例。

4.红外辐射计数器红外辐射计数器是一种基于消光和反射原理的微生物计数仪器,其原理是通过辐射源向样品发射一定频率的红外辐射,并接收样品的反射光信号,在计算机系统的驱动下对数码化数据进行处理,最终得到表示原始样品生化物数量的结果。

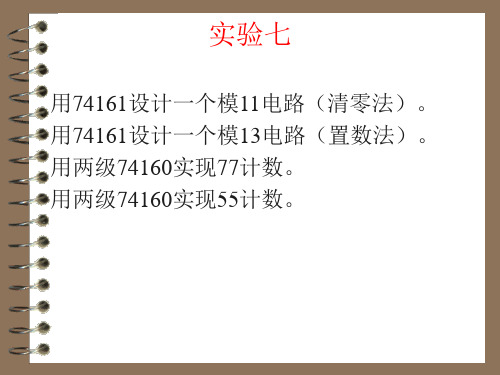

实验7 计数器实验

班级姓名学号一、实验项目:计数器二、使用集成块型号:74LS00、74LS161、74LS74.三、实验内容:1、测试74LS161十六进制计数器的逻辑功能。

CP脉冲输入端;CR异步清零端;LD同步置数端;CT T、CT P计数允许控制端;CO进位输出端。

D3、D2、D1、D0数据输入端;Q3、Q2、Q1、Q0输出端;2、利用直接清零法,使用计数器74LS161和与非门74LS00构成十二进制计数器,并画出状态图。

3、用预置数据法,使用计数器74LS161和与非门74LS00构成构成七进制计数器,并画出状态图。

4、采用级联法,使用两片74LS161和与非门74LS00构成二十四进制计数器,画出逻辑电路图,根据逻辑图连线。

利用单脉冲输入源给CP端加入脉冲信号,观察输出Q3Q2Q1Q0端的状态变化,并画出状态图。

5、用74LS74D触发器构成两位二进制异步加法计数器。

6、用74LS74D触发器构成两位二进制异步减法计数器,将左图电路中的低位触发器的Q端和高位的CP端相连接,构成减法计数器。

置数和清零的区别:清零的信号是立即产生的,比如都对于十进制来说,若采用清零法,则应该利用9的二进制,1001的下一位1010来产生脉冲信号,将输出端的第一位和第三位通过与非门得到低电平将161清零,也就是说我们利用的真正状态是10的二进制。

而如果我们采用置数法,因为芯片的设计原因,在计数器进入9的二进制1001后,输出端并没有立即置数,而是保持该状态不变,直到下一个时钟脉冲的上升沿到来为止,这个1001是一个稳定的状态,我们利用它的第0位和第三位通过与非门得到低电平将161置位为0000,才能形成十进制,那么我们利用的真正状态是9的二进制,而不是10,这就是清零与置数的根本区别。

单片机实验-扩展存储器读写实验

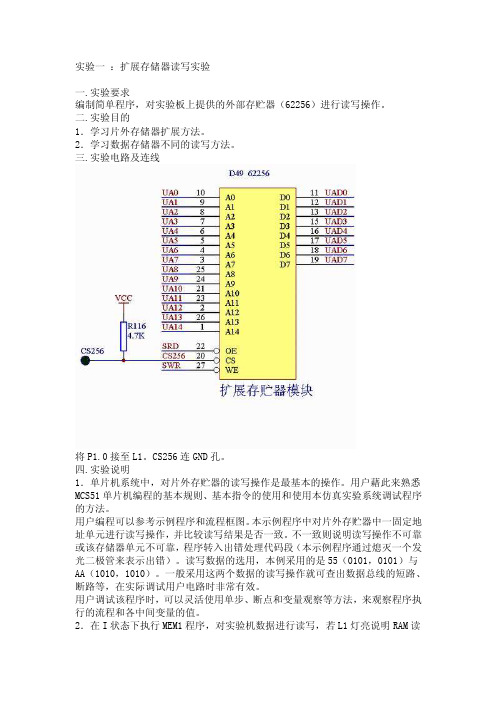

实验一:扩展存储器读写实验一.实验要求编制简单程序,对实验板上提供的外部存贮器(62256)进行读写操作。

二.实验目的1.学习片外存储器扩展方法。

2.学习数据存储器不同的读写方法。

三.实验电路及连线将P1.0接至L1。

CS256连GND孔。

四.实验说明1.单片机系统中,对片外存贮器的读写操作是最基本的操作。

用户藉此来熟悉MCS51单片机编程的基本规则、基本指令的使用和使用本仿真实验系统调试程序的方法。

用户编程可以参考示例程序和流程框图。

本示例程序中对片外存贮器中一固定地址单元进行读写操作,并比较读写结果是否一致。

不一致则说明读写操作不可靠或该存储器单元不可靠,程序转入出错处理代码段(本示例程序通过熄灭一个发光二极管来表示出错)。

读写数据的选用,本例采用的是55(0101,0101)与AA(1010,1010)。

一般采用这两个数据的读写操作就可查出数据总线的短路、断路等,在实际调试用户电路时非常有效。

用户调试该程序时,可以灵活使用单步、断点和变量观察等方法,来观察程序执行的流程和各中间变量的值。

2.在I状态下执行MEM1程序,对实验机数据进行读写,若L1灯亮说明RAM读写正常。

3.也可进入LCA51的调试工具菜单中的对话窗口,用监控命令方式读写RAM,在I状态执行SX0000↓ 55,SPACE,屏幕上应显示55,再键入AA,SPACE,屏幕上也应显示AA,以上过程执行效果与编程执行效果完全相同。

注:SX是实验机对外部数据空间读写命令。

4.本例中,62256片选接地时,存储器空间为0000~7FFFH。

五.实验程序框图实验示例程序流程框图如下:六.实验源程序:ORG 0000HLJMP STARTORG 0040HSTART:MOV SP,#60HMOV DPTR,#0000H ;置外部RAM读写地址MOV A,#55H ;测试的数据一MOV B,AMOVX @DPTR,A ;写外部RAMMOVX A,@DPTR ;读外部RAMXRL A,B ;比较读回的数据JNZ ERRORMOV A,#0AAH ;测试的数据二MOV B,AMOVX @DPTR,AMOVX A,@DPTRXRL A,BJZ PASS ;测试通过ERROR: SETB P1.0 ;测试失败,点亮LEDSJMP $PASS: CPL P1.0 ;LED状态(亮/灭)转换MOV R1,#00H ;延时DELAY: MOV R2,#00HDJNZ R2,$DJNZ R1,DELAYLJMP START ;循环测试END实验二P1口输入、输出实验一.实验要求1.P1口做输出口,接八只发光二极管,编写程序,使发光二极管循环点亮。

计数器的实验观察与分析

计数器的实验观察与分析计数器是一种常见的电子设备,用于计算和显示一个或多个事件的数量。

本次实验的目的是观察和分析一个四位数的数字计数器的工作原理和性能。

实验步骤如下:1. 实验装置:一台四位数的数字计数器、一个交流电源和连接电线。

2. 连接电路:将交流电源的正极和数字计数器的Vcc引脚连接,将交流电源的负极和数字计数器的地引脚连接。

3. 调整电源电压:将交流电源的电压调整到合适的范围,例如5V。

4. 计数电路:将计数器的输入引脚与电源连接。

5. 数字显示:将计数器的输出引脚与七段数码管连接。

6. 实验观察:打开交流电源,观察数字计数器的工作情况。

记录显示在四位数码管上的数字变化。

根据观察数据,进行以下分析和讨论:1. 计数范围:观察实验当中计数器最高能计数到的数。

根据实验结果,推断该计数器的计数范围。

2. 计数方式:观察数字的计数变化模式,判断计数器采用的计数方式是递增还是递减。

通过改变输入引脚的电压,可以验证计数器的计数方式。

3. 计数精度:观察实验过程中数字计数器是否存在计数误差。

将计数器与其他测量设备(如计时器)进行对比,以确定计数器的计数精度。

4. 显示方式:观察数字计数器的显示方式。

是否采用了七段数码管进行数字显示,或者是采用其他显示器件。

5. 重置功能:观察数字计数器是否具备重置功能。

通过改变输入引脚的电压,验证计数器的重置功能。

通过上述的实验观察和分析,我们可以了解到数字计数器的基本工作原理、计数范围、计数方式、计数精度、显示方式以及是否具备重置功能等。

这些了解对于进一步应用数字计数器有很大帮助,例如在电子测量、物理实验、工业自动化等领域都有广泛应用。

6. 计数范围:根据实验结果观察到的最高数字,可以推断出该计数器的计数范围。

比如,如果实验结果显示的最高数字是9,则可以推断该计数器的范围为0-9。

如果最高数字是F(十六进制),则范围为0-F。

7. 计数方式:观察数字的计数变化模式可以推断出计数器采用的计数方式是递增还是递减。

电子线路基础数字电路实验7 时序逻辑电路设计

实验七时序逻辑电路设计一、实验目的1. 学习用集成触发器构成计数器的方法。

2. 熟悉中规模集成十进制计数器的逻辑功能及使用方法。

3. 学习计数器的功能扩展。

4. 了解集成译码器及显示器的应用。

二、实验原理计数器是一种重要的时序逻辑电路,它不仅可以计数,而且用作定时控制及进行数字运算等。

按计数功能计数器可分加法、减法和可逆计数器,根据计数体制可分为二进制和任意进制计数器,而任意进制计数器中常用的是十进制计数器。

根据计数脉冲引入的方式又有同步和异步计数器之分。

1. 用D触发器构成异步二进制加法计数器和减法计数器:图10—1是用四只D触发器构成的四位二进制异步加法计数器,它的连接特点是将每只D触发器接成T'触发器形式,再由低位触发器的Q端和高一位的CP端相连接,即构成异步计数方式。

若把图10—1稍加改动,即将低位触发器的Q端和高一位的CP端相连接,即构成了减法计数器。

图10—1本实验采用的D触发器型号为74LS74A,引脚排列见前述实验。

2. 中规模十进制计数器中规模集成计数器品种多,功能完善,通常具有予置、保持、计数等多种功能。

74LS182同步十进制可逆计数器具有双时钟输入,可以执行十进制加法和减法计数,并具有清除、置数等功能。

引脚排列如图10—2所示。

其中LD−−置数端;CP u−−加计数端;CP D−−减计数端;DO−−非同步进位输出端;CO−−非同步借位输出端;Q A、Q B、Q C、Q D−−计数器输出端;D A、D B、D C、D D−−数据输入端;CR−−清除端。

表10—1为74LS192功能表,说明如下:当清除端为高电平“1”时,计数器直接清零(称为异步清零),执行其它功能时,CR置低电平。

当CR为低电平,置数端LD为低电平时,数据直接从置数端D A、D B、D C、D D置入计数器。

当CR为低电平,LD为高电平时,执行计数功能。

执行加计数时,减计数端CP D接高电平,计数脉冲由加计数端Cp u输入,在计数脉冲上升沿进行842编码的十进制加法计数。

计数器的应用实验总结

计数器的应用实验总结介绍计数器是一种常见的应用,广泛应用于各个领域。

在本次实验中,我们对计数器的应用进行了研究和总结。

本文将对实验的目的、实验过程、实验结果以及对计数器应用的总结进行详细阐述。

实验目的本次实验的目的是通过研究计数器的应用,探索其在实际生活和工程中的应用价值。

我们希望能够深入了解计数器的原理和相关知识,并通过实验验证计数器在不同场景下的应用效果。

实验过程1.确定实验步骤:我们首先确定了实验步骤,包括材料准备、实验环境搭建、实验操作等。

2.材料准备:我们准备了一台计算机、一块开发板、若干导线和一个计数器模块作为实验所需材料。

3.实验操作:我们按照设定的实验步骤进行操作,将计数器模块与开发板进行连接,并通过编程的方式设置计数器的初始值和计数方式。

4.实验观察:在实验过程中,我们观察了计数器模块的工作状态,并记录相关数据。

5.数据分析:根据实验获得的数据,我们进行了详细的数据分析和处理,得出了一些结论。

实验结果通过本次实验,我们获得了以下实验结果:1.计数器模块能够准确地记录计数次数,并且可以根据设置的计数方式进行自动计数。

2.不同的计数方式对计数器的性能影响较大,有些计数方式可能会导致计数器出现误差。

3.计数器模块的精度与其技术规格有关,选择合适的计数器模块可以提高计数器的性能。

计数器应用总结计数器在生活和工程中有着广泛的应用。

以下是对计数器应用的总结:1.计步器:计步器是计数器的一个常见应用,用于记录行走步数。

可以通过计步器来监控日常运动量,帮助人们进行健康管理。

2.生产计数:在生产线上,可以使用计数器来记录生产数量,帮助工厂管理生产进度和产品质量。

3.交通流量统计:计数器可以用于统计道路上的车辆流量,为交通管理提供数据支持,帮助进行交通规划和拥堵预测。

4.频率计数:计数器可以用于测量信号的频率,广泛应用于电子设备测试和通信领域。

5.时间测量:计数器也可以用于测量时间,如秒表和倒计时器等,广泛应用于运动比赛和实验室实验等场景。

实验报告七

选预置数D3D2D1D0=0000;

写出D5-1的二进制数码:D4=0100;

再根据D4数码写出置数信号表达式: Q2 ; LD

最后根据置数信号表达式画出连线图。

例 用 74LS160的置数法构成七进制加法计数器

741LS60的有效状态是10个状态,在此选后七个状态为循环 计数状态即0011~1001。所以选预置数为:D3D2D1D0=1001 ; 74LS160是同步置数的,选

1) 异步清零:当 RD 0 时,不管其他输入端的状态如何, 不论有无时钟脉冲CP,计数器输出将被直接置零(Q3Q2QlQ0= 0000),称为异步清零。 2) 同步并行预置数:当 RD 1, LD 0 时,在输入时钟脉 冲CP上升沿的作用下,并行输入端的数据d3d2d1d0被置入计数 器的输出端,即Q3Q2QlQ0=d3d2d1d0。由于这个操作要与CP上 升沿同步,所以称为同步预置数。 3)计数功能:当 RD LD EP ET 1 时,在CP端输入 计数脉冲,计数器进行二进制加法计数。 4)保持功能:当 R D LD 1 ,且 EP ET 0 ,即两个 使能端中有0时,则计数器保持原来的状态不变。这时,如 EP=0、ET=1,则进位输出信号CO保持不变;如ET=0则不 管EP状态如何,进位输出信号CO为低电平0。

集成计数器产品多数是二进制和十进制计数器,如果需要其 他进制的计数器,可用现有的二进制或十进制计数器,利用 其清零端或预置数端,外加适当的门电路连接构成任意进制 计数器。如果手边有M进制的集成计数器,要构成N进制的计 数器,当M>N时用一片M进制的计数器就可以实现;当M<N时 则需要多片M进制的计数器下面分别介绍实现的方法。

LD CO ;

最后根据置数信号表达式画出连线图。

实验七-小规模-SSI-计数器及其应用

实验七小规模SSI 计数器及其应用一、实验目的1. 熟悉触发器的逻辑功能。

2. 掌握小规模时序逻辑电路的设计方法、安装及调试。

3. 学会用状态转换表、状态转换图和时序图来描述时序逻辑电路的逻辑功能。

二、实验器件1. 数字信源状态分析实验箱。

2. 74LS00、 74LS20、 74LS74、 74LS112。

3. 双踪示波器、数字万用表。

三、实验原理1、SSI 时序逻辑电路设计原则和步骤:SSI 时序逻辑电路设计原则是:当选用小规模集成电路时,所用的触发器和逻辑门电路的数目应最少,而且触发器和逻辑门电路输入端数目也应为最少,所设计出的逻辑电路应力求最简,并尽量采用同步系统。

同步时序电路设计步骤如下:(1) 根据设计要求,画出状态图和状态表。

(2) 状态编码。

把状态表中各个字符表示的状态规定一个二进制代码,并使代码与各触发器的状态相对应。

(3) 选定触发器的类型。

不同逻辑功能的触发器驱动方式不同,所以用不同类型触发器设计出的电路也不同。

因此,在设计具体电路前必须根据需要选定触发器的类型。

(4) 根据代码形式的状态表和所选用的触发器直接写出输出方程。

或者根据状态表画出每个输出的卡诺图,写出输出方程。

(5) 对照所选触发器的状态方程,画出逻辑电路图。

(6) 检查设计的电路能否自启动。

四、实验内容1.试用 D 触发器和门电路设计一个四位扭环形计数器,并能自启动。

状态转换图如图 10 所示:图 10四位扭环形计数器状态转换图状态转移表为:表 9 四位扭环形计数器状态转移表根据状态转移表画出卡诺图,并确定状态转移方程:图11 四位扭环形计数器卡诺图据此逻辑电路图如下:U1A74LS74N1D21Q5~1Q6~1CLR11CLK 3~1PR4U1B74LS74N2D122Q9~2Q8~2CLR 132CLK 11~2PR10U2A74LS74N1D21Q5~1Q6~1CLR 11CLK 3~1PR4U2B74LS74N2D122Q9~2Q8~2CLR132CLK 11~2PR10V110kHz 5VU4A7408NVCC5.0VU3A 7432NXLA1C Q T1F图 12 四位扭环形计数器逻辑电路图由图12四位扭环形计数器逻辑电路图可得仿真结果如下图:图13 四位扭环形计数器仿真结果由图12四位扭环形计数器逻辑电路图和图13四位扭环形计数器仿真结果可得:电路可以自启动。

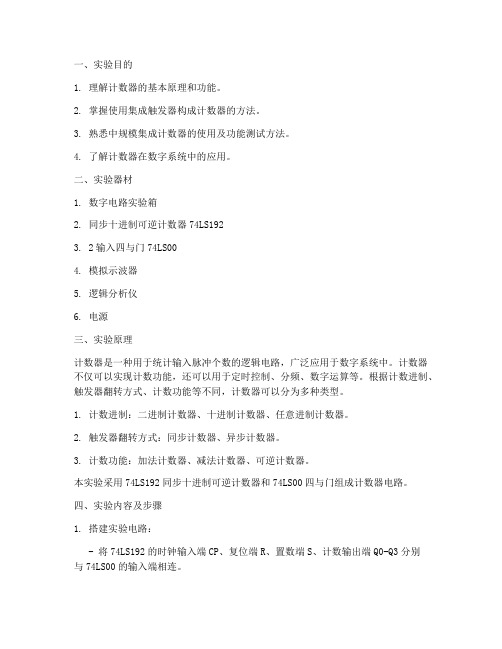

计数器实验报告

一、实验目的1. 理解计数器的基本原理和功能。

2. 掌握使用集成触发器构成计数器的方法。

3. 熟悉中规模集成计数器的使用及功能测试方法。

4. 了解计数器在数字系统中的应用。

二、实验器材1. 数字电路实验箱2. 同步十进制可逆计数器74LS1923. 2输入四与门74LS004. 模拟示波器5. 逻辑分析仪6. 电源三、实验原理计数器是一种用于统计输入脉冲个数的逻辑电路,广泛应用于数字系统中。

计数器不仅可以实现计数功能,还可以用于定时控制、分频、数字运算等。

根据计数进制、触发器翻转方式、计数功能等不同,计数器可以分为多种类型。

1. 计数进制:二进制计数器、十进制计数器、任意进制计数器。

2. 触发器翻转方式:同步计数器、异步计数器。

3. 计数功能:加法计数器、减法计数器、可逆计数器。

本实验采用74LS192同步十进制可逆计数器和74LS00四与门组成计数器电路。

四、实验内容及步骤1. 搭建实验电路:- 将74LS192的时钟输入端CP、复位端R、置数端S、计数输出端Q0-Q3分别与74LS00的输入端相连。

- 将74LS192的时钟输入端CP接至实验箱的时钟信号输出端。

- 将74LS192的复位端R和置数端S接至实验箱的控制信号输出端。

- 将74LS192的计数输出端Q0-Q3分别连接至逻辑分析仪的输入端。

2. 功能测试:- 测试计数器的计数功能:观察逻辑分析仪显示的计数输出波形,验证计数器能否实现计数功能。

- 测试计数器的复位功能:通过控制实验箱的控制信号,观察逻辑分析仪显示的计数输出波形,验证计数器能否实现复位功能。

- 测试计数器的置数功能:通过控制实验箱的控制信号,观察逻辑分析仪显示的计数输出波形,验证计数器能否实现置数功能。

3. 计数器应用:- 利用计数器实现定时功能:将计数器的计数输出端Q0-Q3分别连接至74LS00的输入端,通过组合逻辑电路实现定时功能。

- 利用计数器实现分频功能:将计数器的计数输出端Q0-Q3分别连接至74LS00的输入端,通过组合逻辑电路实现分频功能。

数电实验-实验七

中山大学数字电路与逻辑设计实验报告SUN YAT-SEN UNIVERSITY院(系)学号17339072专业实验人欧雪莹实验题目:实验七译码显示电路一.实验目的(1)掌握中规模集成译码器的逻辑功能和抵用方法(2)熟悉数码管的使用二.实验器件(1)数字电路实验箱、数字万用表、示波器。

(2)器件:74LS48,74LS194,74LS73,74LS00三.实验内容(1)使用显示内容决定显示位置的方法显示学号(2)使用显示位置决定显示内容的方法显示学号四.实验原理1.数码显示译码器BCD码七段译码驱动器-----74LS48,用来驱动共阴极。

在实验箱上使用了两个四位数码管,对应已经连接好74LS48,实验时无需再练线,74LS48只保留引出了A0、A1、A2、A3四个引脚。

2.四节拍发生器在第一个脉冲的上升沿到达后,置入0111,在CP作用下依次为1011,1101,1110,在第四个CP下降沿到达后又使Q=1,实现第二个循环。

2.扫描式显示利用数码管的余辉效应和人眼的视觉暂留效应,虽然在某一时刻只有一个数码管在显示,但人眼看到的是多个数码管“同时”被点亮的效果。

由选通信号控制多路开关,先后送出由高位到低位(或由低位到高位)一位十进制的BCD码。

3.具体实验方法有两种,一是内容决定显示位置。

二是位置决定显示内容。

下面是具体的设计过程:(1)显示内容决定显示位置将脉冲信号输入74LS197作为十六进制计数器,输出分别连入两块4位数码管的位选端,做到控制数码管从第1位到第4位扫描的同时在第5位到第8位扫描。

并将74LS197的低三位输出作为译码器74LS138的输入,译码器输出分别接到74LS48对应输入端即可实现0~7的译码。

通过对74LS197的输出做逻辑运算在(当输出位1001时,将其运算为0,输入到74LS48对应端口)实现9的译码。

(2)显示位置决定显示内容通过74LS194作为四节拍顺序脉冲发生器,输出分别连入两块4位数码管的位选端,做到控制数码管从第1位到第4位扫描的同时在第5位到第8位扫描。

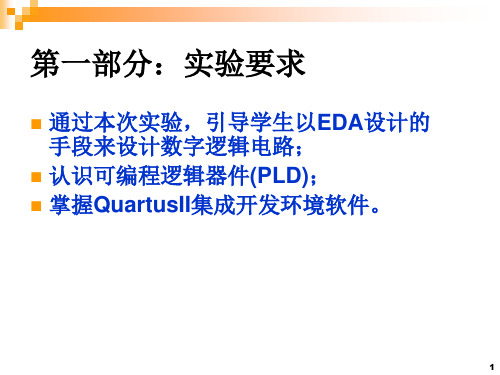

实验七基于QuartusII原理图输入数字电路设计

74138逻辑测试电路原理图设计完毕!

26

四、全程编译

在下拉菜单“Processing” 中选择“Start Compilation”,启动全程编 译

编译完成后的 信息报告窗口

27

关于全程编译

QuartusII的编译器由一系列处理模块构成; 这些模块负责对设计项目的检错、逻辑综合、结构综合、输

出结果的编辑配置,以及时序分析; 在这一过程中,将设计项目适配到FPGA/CPLD目标器件中,

同时产生多用途的输出文件,如功能和时序信息文件,器件 编程的目标文件; 编译器首先检查出工程设计文件中可能的错误信息,以供设 计者排除,然后产生一个结构化的网表文件表达的电路原理 图文件; 启动全程编译:

任何组合逻辑电路都可以用“与门-或门”二级电路实现; 任何时序逻辑电路都可以由组合逻辑电路加上存储元件

(触发器、锁存器构成); 人们由此提出乘积项可编程电路结构,原理结构如下:

3

低密度PLD可编程原理【早期器件】

低密度(简单) PLD,通常内部等 效门数少于500个, 只能实现通用数字 逻辑(如74系列) 的一些功能

28

五、时序仿真

工程编译完成后,设计结果是否满足设计要求, 可以通过时序仿真来分析;

时序仿真主要包含如下的设置步骤:

打开波形编辑器;

顺 序 并

设置仿真时间区域; 波形文件存盘;

不 将端口节点信号选入波形编辑器中;

是 唯 一

编辑输入波形(输入激励信号); 总线数据格式设置

的 启动仿真器

将本机D:\Altera目录下的License.Dat文件 中的MAC号即完成破解; 右图所示为查看本机MAC地址(实际地址) 的方法。

实验七 中规模集成计数器的应用

实验七 中规模集成计数器的应用一、实验目的1.熟悉中规模集成电路计数器的功能及应用。

2.进一步熟悉数字逻辑实验箱中的译码显示功能。

二、实验原理计数器是一种中规模集成电路,其种类有很多。

如果按照触发器翻转的次序分类,可分为同步计数器和异步计数器两种;如果按照计数数字的增减可分为加法计数器、减法计数器和可逆计数器三种;如果按照计数器进位规律又可分为二进制计数器、十进制计数器、可编程N 进制计数器等多种。

常用计数器均有典型产品,不须自己设计,只要合理选用即可。

本实验选用四位二进制同步计数器74LS161做计数器,该计数器外加适当的反馈电路可以构成十六进制以内的任意进制计数器。

图1是它的逻辑符号,它除了具有二进制加法计数功能外,还具有预置数、清零、保持的功能。

图中LD 是预置数控制端,0D 、1D 、2D 、3D 是预置数据输入端,r C 是清零端,T CT 、P CT 是计数器使能控制端,0C 是进位信号输出端,它的主要功能有:(1)异步清零功能 若r C =0(输出低电平),则输出0Q 1Q 2Q 3Q =0000,与其它输入信号无关,也不需要CP 脉冲的配合,所以称为“异步清零”。

(2)同步并行置数功能 在r C =1,且LD =0的条件下,当CP 上升沿到来后,触发器0Q 1Q 2Q 3Q 同时接收0D 1D 2D 3D 输入端的并行数据。

由于数据进入计数器需要CP 脉冲的作用,所以称为“同步置数”,由于4个触发器同时置入,又称为“并行”。

(3)保持功能 在r C =LD =1的条件下,T CT 、P CT 两个使能端只要有一个低电平,计数器将处于数据保持状态,与CP 及0D 1D 2D 3D 输入无关。

(4)计数功能 当r C =LD =T CT =P CT =1时,电路为四位二进制加法计数器。

在CP 脉冲作用下,电路按自然二进制递加,状态变化在0000~1111间循环。

74LS161的功能表详见表一所示。

计数器及其应用实验报告实验总结

计数器及其应用实验报告实验总结下载提示:该文档是本店铺精心编制而成的,希望大家下载后,能够帮助大家解决实际问题。

文档下载后可定制修改,请根据实际需要进行调整和使用,谢谢!本店铺为大家提供各种类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by this editor. I hope that after you download it, it can help you solve practical problems. The document can be customized and modified after downloading, please adjust and use it according to actual needs, thank you! In addition, this shop provides you with various types of practical materials, such as educational essays, diary appreciation, sentence excerpts, ancient poems, classic articles, topic composition, work summary, word parsing, copy excerpts, other materials and so on, want to know different data formats and writing methods, please pay attention!一、引言计数器作为数字电路中常见的元件,在数字电子技术中有着广泛的应用。

数电实验7——计数器. 报告docx

深圳大学实验报告课程名称:数字电子技术实验项目名称:计数器学院:光电工程学院专业:光源与照明指导教师:**报告人:黄学号:2016 班级:实验时间:2018年12月19日实验报告提交时间:教务处制三、实验原理:计数器器件是应用较广的器件之一,它有很多型号,各自完成不同的功能,可根据不同的需要选用。

本实验选用74LS162做实验器件。

74LS162引脚图见图1。

74LS162是十进制BCD同步计数器。

Clock是时钟输入端,上升沿触发计数触发器翻转。

允许端P和T都为高电平时允许计数,允许端T为低时禁止Carry产生。

同步预置端Load加低电平时,在下一个时钟的上升沿将计数器置为预置数据端的值。

清除端Clear为同步清除,低电平有效,在下一个时钟的上升沿将计数器复位为0。

74LS162的进位位Carry在计数值等于9时,进位位Carry为高,脉宽是1个时钟周期,可用于级联。

四、实验内容与步骤:(一)实验内容:1、用1片74LS162和1片74LS00采用复位法构一个模7计数器。

用单脉冲做计数时钟,观测计数状态,并记录。

用连续脉冲做计数时钟,观测并记录Q D,Q C,Q B,Q A的波形。

2、用1片74LS162和1片74LS00采用置位法构一个模7计数器。

用单脉冲做计数时钟,观测并记录Q D,Q C,Q B,Q A的波形。

3、用2片74LS162和1片74LS00构成一个模60计数器。

2片74LS162的Q D,Q C,Q B,Q A分别接两个译码显示的D,B,C,A端。

用单脉冲做计数时钟,观测数码管数字的变化,检验设计和接线是否正确。

(二)实验接线及测试结果:1、复位法构成的模7计数器接线图及测试结果(1)复位法构成的模7计数器接线图图9.1 复位法7进制计数器接线图1 图9.2 复位法7进制计数器接线图2 图中,AK1是按单脉冲按钮,LED0,LED1,LED2和LED3是逻辑状态指示灯,100kHz 是连续脉冲源。

实验七-8421码检测电路

实验七8421码检测电路的设计姓名:张跃佳班级:电自2班学号:实验时间:2015.12.24【实验目的】1.了解检测电路的工作原理2.进一步掌握同步时序逻辑电路的设计方法【实验仪器及器件】1.实验箱、万用表、示波器2.74LS73、74LS74、74LS00、74LS20、74LS197【实验原理】本实验要求设计一个8421BCD码(串行输入)检测电路。

此电路是用来检测串行的8421码传输过程中是否发生错误。

假定8421BCD码传送过程中是由低到高串行送数,例如十进制2(代码为0010)是按0、1、0、0次序传送的。

如果在传送过程中代码发生错误,出现非法数码(不在0000到1001之间的代码)则检测电路发生一脉冲信号。

实验所用触发器为JK触发器,要求自己设计、自己安装和测试。

设计提示本实验的设计关键是建立原始状态图和状态表。

根据要求8421BCD码是由低位到高位传送,该电路每四个码元检测一次,当电路收到第四个码元时,若判断是非法码,则输出为1,否则输出为0.可见此电路为米里时序电路。

设检测电路初始状态为S,当电路接收第一个码元后,根据输入是0还是1,将分别转到两个不同的新状态S1和S2,从S1或S2出发,接收到第二个码元后,又根据是0还是1,又转到两个不同的新状态,类推到接收到的第三、四码元后电路执行统一的动作。

在接收到第四个码元后,根据接收的代码判断是否是非法码而确定其输出是否为1,并且电路回到初始状态S,准备接受新的一组码组。

根据上面的分析很容易做出原始状态和状态表了。

这样做出的元素状态表有15个状态,经过化简后只剩下6个状态。

化简后的状态如表(一)。

由简化状态表,根据状态分配原则,可得许多分配方案,其中一种分配方案如表(二),得到的结果是:⎪⎪⎩⎪⎪⎨⎧======131312,23221,21K Q J Q X K Q Q J Q X K Q J13Q XQ F =表(一)简化状态表XS 01A B/0 B/0B C/0 D/0C E/0 F/0D F/0 F/0E A/0 A/0F A/0 A/1表(二)分配方案的一种Q 2Q 1Q 3 0001 11 100 A D C B1 F E X X【实验内容】本检测电路是同步时序电路。

实验七数据选择与译码显示..

7

2015~2016秋冬 浙江大学计算机学院实验教学中心

掌握数据选择器的工作原理和逻辑功能 掌握数据选择器的使用方法 掌握数码管显示控制方法和4位数码管扫描显示方法 掌握按键去抖原理和实现方法

数据选择器设计及应用

2018/10/10

2

实验设备

装有ISE的计算机系统 Spartan III实验板 1台 1套

CF DP {A~G,DP}

七段数码管显示控制电路图

时分复用显示控制方法示意图

数据选择器设计及应用

2018/10/10

7

共阳连接:8个LED正极连在一起,负极低电平时点亮 共阴连接:8个LED负极连在一起,正极高电平时点亮

数据选择器设计及应用

2018/10/10

8

位控制信号 0111 计数器

1011

数据选择器设计及应用 2018/10/10 11

module displayswitch(clk, btn_in, digit_anode, segment); // port declaration, and define variable: disp_num initial disp_num <= 16'b1010_1011_1100_1101; // display "AbCd" always@(posedge btn_in[0]) disp_num[ 3: 0]<= disp_num[ 3: 0] + 4'd1; always@(posedge btn_in[1]) disp_num[ 7: 4]<= disp_num[ 7: 4] + 4'd1; always@(posedge btn_in[2]) disp_num[11: 8]<= disp_num[11: 8] + 4'd1; always@(posedge btn_in[3]) disp_num[15:12]<= disp_num[15:12] + 4'd1; display DISPLAY_0(clk, disp_num, digit_anode, segment); endmodule module display(clk, disp_num, digit_anode, segment); // port declaration, and define variable: cnt, num always @(posedge clk) begin // increment counter case (cnt[11:10]) // display each digit according to cnt[11:10] endcase case (num) // display 0~F accroding to num endcase end endmodule

实验七 4位十进制频率计原理与设计

实验七 4位十进制频率计原理与设计一、实验目的1、深入学习数字系统设计的方法与步骤2、设计4位十进制频率计,学习较复杂的数字系统设计方法。

二、实验仪器PC机,操作系统为Windows2000/XP,本课程所用系统均为WindowsXP,Quartus II 5.1设计平台,GW48系列SOPC/EDA实验开发系统。

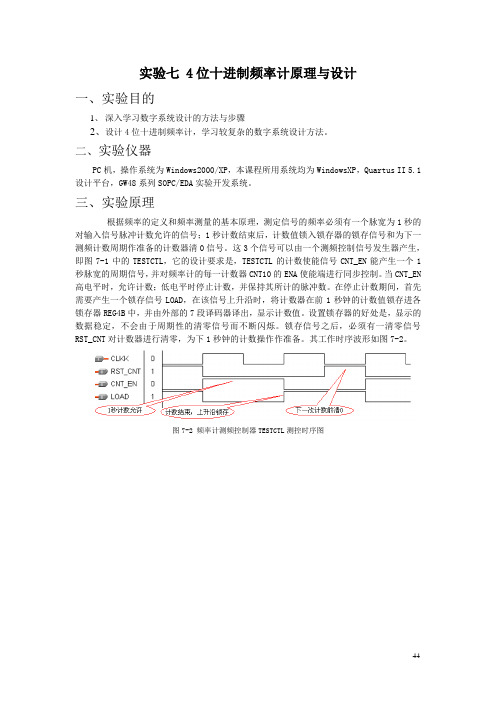

三、实验原理根据频率的定义和频率测量的基本原理,测定信号的频率必须有一个脉宽为1秒的对输入信号脉冲计数允许的信号;1秒计数结束后,计数值锁入锁存器的锁存信号和为下一测频计数周期作准备的计数器清0信号。

这3个信号可以由一个测频控制信号发生器产生,即图7-1中的TESTCTL,它的设计要求是,TESTCTL的计数使能信号CNT_EN能产生一个1秒脉宽的周期信号,并对频率计的每一计数器CNT10的ENA使能端进行同步控制。

当CNT_EN 高电平时,允许计数;低电平时停止计数,并保持其所计的脉冲数。

在停止计数期间,首先需要产生一个锁存信号LOAD,在该信号上升沿时,将计数器在前1秒钟的计数值锁存进各锁存器REG4B中,并由外部的7段译码器译出,显示计数值。

设置锁存器的好处是,显示的数据稳定,不会由于周期性的清零信号而不断闪烁。

锁存信号之后,必须有一清零信号RST_CNT对计数器进行清零,为下1秒钟的计数操作作准备。

其工作时序波形如图7-2。

图7-2 频率计测频控制器TESTCTL测控时序图图7-1 4位十进制频率计顶层文件原理图四、实验步骤1、根据附录7-1、7-2、7-3以及图7-1描述的4位十进制频率计的工作原理,利用Quartus II 5.1对以上三者的程序进行文本编辑输入和仿真测试并根据图7-1,写出频率计的顶层文件,并给出其测频时序波形,及其分析。

2、频率计设计硬件验证。

编译、综合和适配频率计顶层设计文件,并编程下载进入目标器件中。

本实验目标器件是EP1K30TC144-3,实验电路选择模式0,4个数码管(数码4-1:PIO31-PIO16)显示测频输出;待测频率输入FIN由clock0输入,频率可选4Hz、256HZ . . .或更高;1HZ测频控制信号F1HZ可由clock2输入(用电路帽选选1Hz)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验七、计数器

一、实验目的

1、掌握计数器74LS162的功能;

2、掌握计数器的级联方法;

3、熟悉任意模计数器的构成方法;

4、熟悉数码管的使用。

二、实验说明

计数器器件是应用较广的器件之一。

它有很多型号,各自完成不同的功能,使用中根据不同的需要选用。

本实验选用74LS162做实验用器件。

74LS162是十进制BCD同步计数器。

Clock是时钟输入端,上升沿触发计数器翻转。

允许端P和T都为高电平时允许计数,允许端T为低时禁止进位(Carry)产生。

同步预置端Load加低电平时,在下一个时钟的上升沿将计数器置为预置数据端的值。

清除端Clear为同步清除,低电平有效,在下一个时钟的上升沿将计数器复位为0。

在计数值等于9时,进位位Carry为高,脉宽是一个时钟周期,可用于级联。

三、实验所用仪器和芯片

1、同步4位BCD计数器74LS162 2片

2、二输入四与非门74LS00 1片

3、TEC-5(实验系统 1台

4、示波器 1台

四、实验内容

1、用1片74LS162和1片74LS00采用复位法(反馈清零法)构造一个模7计数器。

用单脉冲做计数时钟,观测计数状态,并记录。

用连续脉冲(50KHz)做计数时钟,观测并记录Qd,Qc,Qb,Qa的波形。

2、用1片74LS162和1片74LS00采用置位法(同步预置法)构造一个模7计数器。

用单脉冲做计数时钟,观测计数状态,并记录。

用连续脉冲(50KHz)做计数时钟,观测并记录Qd,Qc,Qb,Qa的波形。

*3、用2片74LS162和1片74LS00构成一个模60计数器。

2片74LS162的Qd,Qc,Qb,Qa分别接两个数码管的D,C,B,A。

用单脉冲做计数时钟,观测数码管数字变化,检验设计和接线是否正确。

五、实验报告要求

1、画出复位法构成的模7计数器的电路图;写出单脉冲作计数脉冲时,QD,Qd,Qc,Qb,Qa的状态转移表。

用连续脉冲(50KHz)做计数时钟,观测并记录Qd,Qc,Qb,Qa的波形。

2、画出置位法构成的模7计数器的电路图;写出单脉冲作计数脉冲时, QD, Qd, Qc, Qb, Qa的状态转移表。

用连续脉冲(50KHz)做计数时钟,观测并记录Qd,Qc,Qb,Qa的波形。

*3、画出模60计数器接线图。