第九章 有限状态机

有限状态机

1.1概述有限状态机是指输出取决于过去输入部分和当前输入部分的时序逻辑电路。

有限状态机又可以认为是组合逻辑和寄存器逻辑的一种组合。

状态机特别适合描述那些发生有先后顺序或者有逻辑规律的事情,其实这就是状态机的本质。

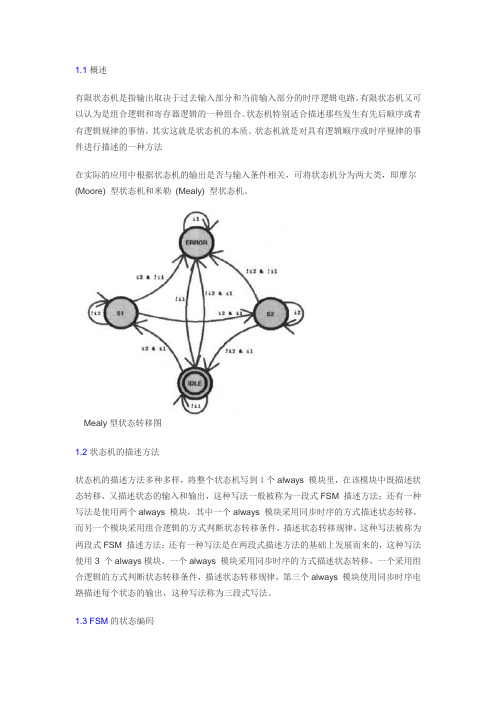

状态机就是对具有逻辑顺序或时序规律的事件进行描述的一种方法在实际的应用中根据状态机的输出是否与输入条件相关,可将状态机分为两大类,即摩尔(Moore) 型状态机和米勒(Mealy) 型状态机。

Mealy型状态转移图1.2状态机的描述方法状态机的描述方法多种多样,将整个状态机写到1个always 模块里,在该模块中既描述状态转移,又描述状态的输入和输出,这种写法一般被称为一段式FSM 描述方法;还有一种写法是使用两个always 模块,其中一个always 模块采用同步时序的方式描述状态转移,而另一个模块采用组合逻辑的方式判断状态转移条件,描述状态转移规律,这种写法被称为两段式FSM 描述方法;还有一种写法是在两段式描述方法的基础上发展而来的,这种写法使用3 个always模块,一个always 模块采用同步时序的方式描述状态转移,一个采用组合逻辑的方式判断状态转移条件,描述状态转移规律,第三个always 模块使用同步时序电路描述每个状态的输出,这种写法称为三段式写法。

1.3 FSM的状态编码二进制码(Binary)和格雷码(Gray)属于压缩状态编码,这种编码的优点是使用的状态向量最少,但是需要较多的逻辑资源用来状态译码。

二进制码从一个状态转换到相邻状态时,可能有多个比特位发生变化,易产生中间状态转移问题,状态机的速度也要比采用其它编码方式慢。

格雷码两个相邻的码值仅有一位就可区分,这将会减少电路中相邻物理信号线同时变化的情况,因而可以减少电路中的电噪声。

Johnson码也有同样的特点,但是要用较多的位数。

独热码(One-hot)指对任意给定的状态,状态寄存器中只有l位为1,其余位都为0。

《有限状态机应用》课件

验证状态转移逻辑

通过测试用例验证状态转移逻辑的正确性和 完整性。

软件测试中的状态判定逻辑

分析状态判定需求

对软件的状态判定需求进行分析,明确判定条件和 结果。

设计状态判定算法

根据判定需求,设计出合理的状态判定算法。

验证状态判定逻辑

通过测试用例验证状态判定逻辑的准跳转的目标页面或状

态。

跳转过程实现

02 执行跳转操作,如使用HTML的锚点链接、使用

JavaScript进行页面跳转等。

跳转结果处理

03

在跳转完成后,处理跳转结果,如加载新页面、更新

UI等。

PART 05

有限状态机在软件测试中 的应用

软件测试中的状态管理

定义软件的状态

有限状态机是一种抽象的数学模型, 用于描述系统在有限数量的状态之间 转换的行为。

它由一组状态、一组输入事件和一个 状态转换函数组成,根据输入事件在 状态之间进行转换。

有限状态机的特点

有限性

系统只有有限个状态,并且每个状态都有一个明 确的含义和行为。

确定性

对于给定的输入事件,状态转换函数总是确定一 个唯一的状态转换。

状态的跳转

总结词

阐述在不同状态下如何进行逻辑处理 和跳转。

详细描述

在有限状态机中,每个状态的转移都 伴随着一定的逻辑处理。这部分内容 将详细介绍在不同状态下如何进行逻 辑处理以及如何根据处理结果决定状 态的跳转方向。

PART 03

有限状态机在游戏开发中 的应用

游戏中的状态管理

状态定义

明确游戏中的各个状态,如待机、游戏进行 、胜利、失败等。

离散性

系统的状态转换是离散的,即在任意时刻只能从 一个状态转换到另一个状态。

程序设计之有限状态机

程序设计之有限状态机程序设计之有限状态机状态机?以前听说过,忘了是老师说的,还是老大说得了。

当时的认识也就是字面的意思,无非是和状态以及状态转换有关系。

也许在写过或者读过的一些代码中有遇到过有限状态机的程序,但是当时是一定没有想到这就是状态机吧。

最近在学习一些东西的时候竟然多次遇到,觉得还是有必要写点关于程序设计中有限状态机的东西。

,这里是一篇对状态机从定义到实现都有很好解释的文章,摘录部分如下:*************************************************************** ************************依据状态之间是否有包含关系,分以下两种(1)常规状态机。

状态机中的所有状态是不相交的、互斥的。

(2)层次状态机。

状态机中的状态之间要么是互斥的,要么是真包含的,可以用树性结构来描述这些状态集,包含其它状态的状态称为枝节点,不包含其它状态的状态称为叶节点,为方便单树描述,总是设计一个状态包含所有的状态节点,称为根节点。

状态机的状态只能停留在叶节点,而不能停留在枝节点,每个枝节点需要指定一个子节点为它的默认子节点,以便状态机进入枝节点的时候能够停留到叶节点。

一般都用switch/case if/else方式实现。

在少量状态(3个及其以下)的时候,不需要引入专门的状态机模块。

常规状态机模块实现涉及到的结构由上而下为:顶层结构是状态机:当前状态id,缺省操作,状态表,状态表:状态数组状态结构:状态id,状态名,进入操作,退出操作,缺省操作,状态事件表(数组)状态事件结构:操作,事件,下一状态的id*************************************************************** ************************从代码易读及美观角度来说,建议用switch/case来实现。

从经验来看,在一些稍大的程序设计中一般都会有状态机的实现,特别是在分层实现,协议栈实现,编解码方面。

《有限状态机应用》课件

有限状态机的组成要素

状态

有限状态集合,表示系统的当 前情况。

事件

触发状态转换的输入信号或条 件。

转换

定义了状态之间的关系和条件, 描述了从一个状态到另一个状 态的转变。

有限状态机的应用领域

交通信号灯

控制车辆行驶方向和红绿灯变化。

自动售货机

根据用户选提供相应的商品。

电梯

控制电梯的运行和楼层选择。

2 可扩展性

考虑到未来可能的需求变化,设计状态机具有较高的可扩展性和灵活性。

3 可读性

使用清晰的命名和注释,使状态机的逻辑易于理解和维护。

总结

有限状态机是一种强大的工具,用于描述系统的行为和处理复杂的逻辑。掌 握有限状态机的应用和设计原则,可以帮助我们更好地理解和构建各种系统。

有限状态机应用

有限状态机是一种用于描述系统行为的数学模型。它由状态、事件和转换组 成,并在各个应用领域具有广泛的应用。

什么是有限状态机

有限状态机是一种数学模型,用于描述具有有限个状态和状态之间相互转换的系统。它可以用于模拟现实世界中的 各种行为和过程。

有限状态机的基本概念

有限状态机由状态、事件和转换组成。状态表示系统所处的不同情况,事件触发状态的变化,而转换定义了状态之 间的关系和条件。

有限状态机的实际案例

1

自动跳转

网页中的轮播图切换,自动根据设定的时间间隔跳转到下一张图片。

2

游戏AI

计算机游戏中的敌人行为模式,根据玩家的操作和游戏状态做出相应的反应。

3

电子支付

根据用户的输入和交易状态,完成相应的支付过程。

有限状态机的设计原则

1 简洁性

设计状态和转换尽量简洁,避免不必要的复杂性。

有限状态机

什么是有限状态机FSM简介有限状态机(以下用FSM指代)是一种算法思想,简单而言,有限状态机由一组状态、一个初始状态、输入和根据输入及现有状态转换为下一个状态的转换函数组成。

在Gof的23种设计模式里的state模式是一种面向对象的状态机思想,可以适应非常复杂的状态管理。

现在,FSM被普遍用于搜索引擎的分词、编译器实现和我们普遍关注的游戏开发中。

游戏开发中,通常用FSM实现NPC控制,如当NPC受到攻击时根据健康、力量等选择逃跑还是反攻的行为,一般是用FSM实现的。

FSM的实现方法有很多种,不能简单地说孰优孰劣,但现代开发中,一般都比较推荐面向对象的实现方式:因为可重用性和健壮性更高,而且当需求变更的时候,也有很好的适应性。

实践理论从实践中来,也要回到实践中去。

我们现在通过实例来探索一下FSM的实现吧。

首先假设有这样一个世界(World),世界里只有一台永不缺乏动力的汽车(Car),汽车是次世代的,没有油门方向盘之类的落后设备,只有两个互斥的按钮——停止(Stop)和行进(Run),随着时间的流逝,汽车根据驾驶员的操作走走停停。

下面的代码可以实现这种功能:while True:key = get_key() # 按下什么键if key == "stop":stop(car)elif key == "run":go(car)keep(car) # 保持原态完成了功能而且直观、简洁的程序员万岁!但这时候客户(策划或者玩家)觉得走走停停太没意思了,他们想要掉头、左转和右转的功能,我们就要在while 循环里增加更多的if...else分支;他们想要更多的车,我们就要要在每一个分枝里增加循环;他们不仅仅想要Car了,他们还要要玩Truck,这时我们就需要在分枝的循环里判断当前的车是否支持这个操作(如Truck的装卸货物Car 就不支持);他们……这个while循环终于无限地庞大起来,我们认识到这样的设计的确是有点问题的,所以我们尝试用另一种方法去实现FSM。

2-基本状态机

第九章状态机状态机的本质就是对具有逻辑顺序或时序规律事件的一种描述方法方法。

状态机的三个基本要素状态机的三个基本要素::状态状态::也叫状态变量。

在逻辑设计中,使用状态划分逻辑顺序和时序规律。

比如:设计伪随机码发生器时,可以用移位寄存器序列作为状态;在设计电机控制电路时,可以以电机的不同转速作为状态;在设计通信系统时,可以用信令的状态作为状态变量等。

输出输出::输出指在某一个状态时特定发生的事件。

如设计电机控制电路中,如果电机转速过高,则输出为转速过高报警,也可以伴随减速指令或降温措施等。

输入输入::指状态机中进入每个状态的条件。

有的状态机没有输入条件,其中的状态转移较为简单,有的状态机有输入条件,当某个输入条件存在时才能转移到相应的状态一、状态机状态机分为::状态机分为有限状态机((Finite State Machine,FSM)√ 有限状态机无限状态机((Infinite State Machine,ISM) 无限状态机易维护。

FSM设计要清晰易懂设计要清晰易懂、、易维护有限状态机的设计什么是有限状态机((FSM ) 什么是有限状态机FSM的种类和不同点设计举例什么是有限状态机?什么是有限状态机?-有限状态机是由寄存器组和组合逻辑构成的硬件时序电路;-其状态其状态((即由寄存器组的1和0的组合状态所构成的有限个状态有限个状态))只能在同一时钟跳变沿的情况下才能从一个状态转向另一个状态;-究竟转向哪一状态不但取决于各个输入值究竟转向哪一状态不但取决于各个输入值,,还取决于当前状态于当前状态。

-状态状态机可用于产生在时钟跳变沿时刻开关的复杂的机可用于产生在时钟跳变沿时刻开关的复杂的控制逻辑控制逻辑,,是数字逻辑的控制核心是数字逻辑的控制核心。

Moore 状态机下一个状态= F(当前状态当前状态,,输入信号)输出信号= G(当前状态);下一状态的逻辑输出逻辑G状态寄存器输入输出当前状态激励信号时钟同步的状态机结构(Moore 状态机)F时钟信号clk clk输入Moore型状态机Mealy 状态机下一个状态= F(当前状态当前状态,,输入信号);输出信号= G(当前状态当前状态,,输入信号);下一状态输出逻辑输入时钟同步的状态机结构(Mealy 状态机)的逻辑FG状态寄存器时钟信号clkclk 输入输出当前状态激励信号Mealy型状态机带流水线输出的Mealy 状态机下一个状态= F(当前状态当前状态,,输入信号);输出信号= G(当前状态当前状态,,输入信号);输出输出输输出流带流水线输出的Mealy 状态机下一状态的逻辑F逻辑G 状态寄存器时钟信号clkclk 输入入当前状态激励信号水线寄存器clk 输入有限状态机的Verilog 描述定义模块名和输入输出端口定义模块名和输入输出端口;;定义输入定义输入、、输出变量或寄存器输出变量或寄存器;;定义时钟和复位信号定义时钟和复位信号;;定义状态变量和状态寄存器;定义状态变量和状态寄存器;用时钟沿触发的always 块表示状态转移过程块表示状态转移过程;;在复位信号有效时给状态寄存器赋初始值在复位信号有效时给状态寄存器赋初始值;;描述状态的转换过程描述状态的转换过程::符合条件符合条件,,从一个状态到另外一个状态一个状态,,否则留在原状态否则留在原状态;;验证状态转移的正确性验证状态转移的正确性,,必须完整和全面必须完整和全面。

有限状态机要点课件

输入与输出的关系

输入与输出之间的关系可以是简单或 复杂的。在有限状态机中,输入通常 触发状态转移和/或输出结果的变化 。例如,在密码锁有限状态机中,输 入正确的密码会导致有限状态机进入 “已解锁”状态并打开门,而输入错 误的密码会导致有限状态机进入“锁 定”状态并保持门关闭。

03

有限状态机的实现方式

移的结果。

03

状态图的示例

一个简单的状态图可能包括开机、关机、待机等状态,以及相应的转移

和输入/输出。

转移图

转移图的定义

转移图是描述有限状态机从一个 状态转移到另一个状态的图形表 示法。转移图通常由状态、转移

条件和转移结果组成。

转移图的组成

转移图中的每个节点代表一个状 态,边缘代表从一个状态转移到 另一个状态的条件和结果。转移 条件通常是输入信号或内部事件

案例三:密码锁的实现方式

总结词

密码锁的实现方式也可以用有限状态机来描述。

详细描述

密码锁通常有一个特定的密码,当输入密码时,锁会处 于不同的状态。例如,当输入的密码与正确的密码匹配 时,锁会打开;否则,锁会保持关闭状态。此外,密码 锁还可以处于锁定状态,此时无法输入密码,需要先解 锁才能输入密码。这些状态之间的转换对应于不同的操 作,例如输入密码、锁定/解锁等。

特点

有限状态机具有有限个状态,每个状态对应系统的一个特定配置或模式。它根 据输入符号或事件的触发,从当前状态转移到下一个状态。

有限状态机的应用场景

01

02

03

04

硬件设计

用于描述数字电路的行为和交 互,以及逻辑电路的功能。

软件工程

用于设计模式识别、文本处理 、协议解析等算法,以及实现

状态转移逻辑。

2014.9状态机讲义

有限状态机设计●有限状态机的概念是一种由状态寄存器和组合逻辑电路按照一定方式组成的、能够根据控制信号按照预先设定的状态进行状态间转移的同步时序逻辑电路模型。

有限状态机模型可用于构建各种同步时序逻辑电路。

●有限状态机的类型及特点根据电路内部组成方式的不同,有三种类型:①MOORE型状态机:状态机的输出信号只是当前状态的函数,与输入信号无关。

输出的变化与当前状态的变化及时钟同步。

②MEALY型状态机:状态机的输出信号是当前状态和输入信号的函数,与输入信号有关。

输出信号的变化不仅随当前状态的改变而改变,而且输入的变化也会立即导致输出信号发生变化。

③带流水线的MEALY型状态机:在MEALY型状态机的输出端加上了一个寄存器,使输出端的信号经寄存后再输出,达到与时钟同步的目的。

输出信号是当前状态和输入信号的函数,且与时钟同步。

三种模型的结构图如下所示:时钟CS NS OLMOORE 型状态机结构图复位MEALY 型状态机结构图时钟复位带流水线的MEALY 型状态机结构图时钟输出寄存器复位有限状态机的功能描述方法状态转换图、状态转换表、流程图例1:一个MOORE 型状态机的状态转换图:时钟和复位信号:reset ,clk输入:in输出:out in=1S0/0S1/1in=1reset=1in=0in=0例2:一个MEALY 型状态机的状态转换图in=1S0S1in=1reset=1in=0in=0in=1/out=1in=0/out=0in=1/out=0in=0/out=1in=0/out=0S0S1in=1/out=0reset=1in=0/out=1in=1/out=1例3:一个带流水线的MEALY 型状态机的状态转换图用硬件描述语言设计有限状态机的步骤:①画状态转换图(表):确定输入变量、输出变量和状态数,按照命题要求画出状态转换图或状态转换表;②状态化简:合并等价状态;③状态编码:根据状态的个数对状态进行编码;(不需画状态卡诺图及划简状态卡诺图)④用硬件描述语言对状态图(表)进行描述。

第九章 有限状态机

when write=>if (ready=‘1’) then

next_state<=idle; else next_state<=write; end if; End case; End process;

State_rigister:

Process( clk ) begin if ( clk’event and clk=‘1’) then present_state<=next_state; end if;

9.3 有限状态机的同步输出和复位

从有限状态机的结构可以知道,时钟信号和复位 信号对每一个有限状态机来说都是很重要的,特别是 时钟信号是不可缺少的。 8.2.1同步输出信号 无论是MOORE型有限状态机还是MEALY型有 限状态机,它们的输出信号都是经由组合逻辑电路输 出的,因此输出信号会产生“毛刺”现象。对于同步 电路输出来说,由于“毛刺”只是发生在时钟跳变沿 之后的一小段时间里,因此在下一个时钟跳变沿没到 来时“毛刺”已经消失,所以这时“毛刺”现象不会 对电路产生影响。

但是如果设计人员在设计电路的过程中,需要 把有限状态机的输出作为使能信号,片选信号,复 位信号或时钟信号等来使用时,“毛刺”现象将会 对电路设计造成很大的影响,甚至烧毁电路板。因 此在这种情况下,我们必须保证有限状态机的输出 信号没有“毛刺”产生。 在设计中消除“毛刺”现象的方法很多,这里 介绍一种信号来同步输出信号的消除“毛刺”现象 的方法。利用的方法是用时钟信号将有限状态机的 输出信号加载到另一个寄存器中,该寄存器一般是 由D触发器构成的,它的时钟信号就是有限状态机 的时钟信号。

2、有限状态机逻辑通常十分适用于可编程逻辑器件。通过恰当 的VHDL描述和EDA工具的综合,一般可以生成性能极优的有限 状态机,使其在执行时间、运行速度和占用资源等方面优于由 CPU实现的设计方案。 有限状态机分为两类: Moore型----输出信号仅与当前状态有关

有限状态机应用

传输层协议

传输层协议

有限状态机在传输层协议中用于管理 端到端的数据传输。有限状态机能够 处理连接建立、数据传输和连接关闭 等过程,并提供可靠的数据传输服务 。

总结词

有限状态机在传输层协议中提供可靠 的数据传输服务,确保端到端通信的 稳定性和可靠性。

详细描述

在传输层协议中,有限状态机用于管 理端到端的数据传输。有限状态机能 够处理连接建立、数据传输和连接关 闭等过程,并提供可靠的数据传输服 务。通过状态转换,有限状态机能够 识别不同的通信事件并根据需要采取 相应的处理措施,确保数据传输的稳 定性和可靠性。这有助于提高通信系 统的性能和可靠性。

02

特性

有限状态机具有有限数量的状态,并且每个状态 都有一个或多个转移条件,触发状态之间的转换。

状态机的组成

状态

表示系统的一种状态,每 个状态都有一个唯一的标 识符。

动作

在状态机转换过程中执行 的操作,可以是系统的行 为或输出。

事件

表示系统状态的转移条件, 事件的发生会导致状态机 的状态转换。

状态机的分类

微处理器控制

微处理器的控制逻辑通常使用有限 状态机来实现,以管理内部操作和与 外部世界的交互。

VS

微处理器的指令执行、内存访问和输 入/输出操作都由有限状态机控制。 这些状态机管理微处理器的内部状态, 并根据指令和数据在各种状态之间进 行转换。例如,指令解码器就是一个 有限状态机的例子,它根据当前的指 令码状态来选择下一个状态和要执行 的指令。

01

网络层

在网络层中,有限状态机用于描述路由 器的状态转换,如TCP/IP协议中的TCP 连接状态机。

02

03

传输层

传输层中的有限状态机用于实现可靠 的数据传输,如TCP协议中的发送和接 收状态机。

有限状态机设计

9.1 一般有限状态机的设计

9.1.1 用户自定义数据类型定义语句

TYPE m_state IS ( st0,st1,st2,st3,st4,st5 ) ; SIGNAL present_state,next_state : m_state ;

布尔数据类型的定义语句是: TYPE BOOLEAN IS (FALSE,TRUE) ;

TYPE my_logic IS ( '1' ,'Z' ,'U' ,'0' ) ; SIGNAL s1 : my_logic ; s1 <= 'Z' ;

9.1 一般有限状态机的设计

9.1.1 用户自定义数据类型定义语句

子类型SUBTYPE的语句格式如下: SUBTYPE 子类型名 IS 基本数据类型 RANGE 约束范围;

S3

S4/0

S3/0

S4

S5/0

S1/0

S5

S0/0

S6/0

S6

S0/1

S2/0

简化后状态图

程序代码: LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY CHK2 IS PORT(CLK, RESET: IN STD_LOGIC; S_IN: IN STD_LOGIC; FD: OUT STD_LOGIC); END CHK2; ARCHITECTURE a OF CHK2 IS TYPE STATE_TYPE IS (S0, S1, S2,S3,S4,S5,S6); SIGNAL state: STATE_TYPE; BEGIN PROCESS (CLK,RESET) BEGIN IF RESET= '1' THEN state <= S0; ELSIF CLK'EVENT AND CLK = '1' THEN CASE state IS WHEN S0 =>FD <='0'; IF S_IN='1' THEN state <= S1;ELSE STATE <= S0; END IF; WHEN S1 =>FD<='0'; IF S_IN='1' THEN state <=S2;ELSE STATE <=S0; END IF; 接下页

有限状态机及其扩展

= (1 {})(2 {});

q0 = (q10, q20) Q1Q2;

((q1, q2), (a1, a2)) =

(q1, q2)

(q1, q2)

(q1, q2) 无定义

1(q1, a1)=q1,a2 = ,a11

2(q2, a2)=q2,a1 = ,a22

/ctr:= 0 1

A

2

B

A

3

4

C[ctr<3]/[ctr:=ctr+1]

B,C[ctr<3]/[ctr:=ctr+1]

身份认证系统(具有条件和变量机制的有限状态机)

(最大允许错误次数为3)(err:报警状态; ctr:计数变量) X[con]/Y[exec]含义在于:所标注的状态转移关系在输入x且条件con成立下,转移至下一状态,并输出y且执行

一个有限状态机包括:一个有限状态集,用于描述系统中的不 同状态;一个输入符号集,用于表征系统所接收的不同输

入信息;一个状态转移函数,用于表述系统在接收不同输

入下,从一个状态转移到另外一个状态的规则。

状态转移函数:刻画其行为的最关键部分, 一个从Q到Q的二 元函数。状态转移函数通常可以用关系矩阵、状态转移 表或状态转移图的形式来表示。

状态转移关系集合

(closed, rear) =closed ; (closed,both)=closed ; (closed, neither)=closed;(closed,front)=open

(open, rear) = pen; (open,both) =open; (open, front) = open;(open, neither) = closed

有限状态机

有限状态机是由寄存器组和组合逻辑构成的硬件时序电路,其状态(即由寄存器组的1和0的组合状态所构成的有限个状态)只可能在同一时钟跳变沿的情况下才能从一个状态转向另一个状态,究竟转向哪一状态还是留在原状态不但取决于各个输入值,还取决于当前所在状态。

状态机特别适合描述那些有发生有先后顺序,或者有逻辑规律的事情——其实这就是状态机的本质。

状态机的本质就是对具有逻辑顺序或时序规律事件的一种描述方法。

这个论断的最重要的两个词就是“逻辑顺序”和“时序规律”,这两点就是状态机所要描述的核心和强项,换言之,所有具有逻辑顺序和时序规律的事情都适合用状态机描述。

很多初学者不知道何时应用状态机。

这里介绍两种应用思路:第一种思路,从状态变量入手。

如果一个电路具有时序规律或者逻辑顺序,我们就可以自然而然地规划出状态,从这些状态入手,分析每个状态的输入,状态转移和输出,从而完成电路功能;第二种思路是首先明确电路的输出的关系,这些输出相当于状态的输出,回溯规划每个状态,和状态转移条件与状态输入。

无论那种思路,使用状态机的目的都是要控制某部分电路,完成某种具有逻辑顺序或时序规律的电路设计。

其实对于逻辑电路而言,小到一个简单的时序逻辑,大到复杂的微处理器,都适合用状态机方法进行描述。

请读者打开思路,不要仅仅局限于时序逻辑,发现电路的内在规律,确认电路的“状态变量”,大胆使用状态机描述电路模型。

由于状态机不仅仅是一种电路描述工具,它更是一种思想方法,而且状态机的HDL 语言表达方式比较规范,有章可循,所以很多有经验的设计者习惯用状态机思想进行逻辑设计,对各种复杂设计都套用状态机的设计理念,从而提高设计的效率和稳定性。

//1-paragraph method to decribe FSM//Describe state transition, state output, state input condition in only 1 always block //Westor Wang, Dec. 2006//Verilog Training -- How to write FSM bettermodule state1 ( nrst,clk,i1,i2,o1,o2,err);input nrst,clk;input i1,i2;output o1,o2,err;reg o1,o2,err;reg [2:0] NS; //NextStateparameter [2:0] //one hot with zero idleIDLE = 3'b000,S1 = 3'b001,S2 = 3'b010,ERROR = 3'b100;//1 always block to describe state transition, state output, state input condition always @ (posedge clk or negedge nrst)if (!nrst)beginNS <= IDLE;{o1,o2,err} <= 3'b000;endelsebeginNS <= 3'bx;{o1,o2,err} <= 3'b000;case (NS)IDLE: beginif (~i1) begin{o1,o2,err}<=3'b000;NS <= IDLE; endif (i1 && i2) begin{o1,o2,err}<=3'b100;NS <= S1; endif (i1 && ~i2) begin{o1,o2,err}<=3'b111;NS <= ERROR;endendS1: beginif (~i2) begin{o1,o2,err}<=3'b100;NS <= S1; endif (i2 && i1) begin{o1,o2,err}<=3'b010;NS <= S2; endif (i2 && (~i1)) begin{o1,o2,err}<=3'b111;NS <= ERROR;endendS2: beginif (i2) begin{o1,o2,err}<=3'b010;NS <= S2; endif (~i2 && i1) begin{o1,o2,err}<=3'b000;NS <= IDLE; endif (~i2 && (~i1))begin{o1,o2,err}<=3'b111;NS <= ERROR;end endERROR: beginif (i1) begin{o1,o2,err}<=3'b111;NS <= ERROR;endif (~i1) begin{o1,o2,err}<=3'b000;NS <= IDLE; endendendcaseendendmodule//2-paragraph method to describe FSM//Describe sequential state transition in 1 sequential always block//State transition conditions in the other combinational always block//Package state output by task. Then register the output//Westor Wang, Dec. 2006//Verilog Training -- How to write FSM bettermodule state2 ( nrst,clk,i1,i2,o1,o2,err);input nrst,clk;input i1,i2;output o1,o2,err;reg o1,o2,err;reg [2:0] NS,CS;parameter [2:0] //one hot with zero idleIDLE = 3'b000,S1 = 3'b001,S2 = 3'b010,ERROR = 3'b100;//sequential state transitionalways @ (posedge clk or negedge nrst)if (!nrst)CS <= IDLE;elseCS <=NS;//combinational condition judgmentalways @ (nrst or CS or i1 or i2)beginNS = 3'bx;ERROR_out;case (CS)IDLE: beginIDLE_out;if (~i1) NS = IDLE;if (i1 && i2) NS = S1;if (i1 && ~i2) NS = ERROR; endS1: beginS1_out;if (~i2) NS = S1;if (i2 && i1) NS = S2;if (i2 && (~i1)) NS = ERROR; endS2: beginS2_out;if (i2) NS = S2;if (~i2 && i1) NS = IDLE;if (~i2 && (~i1)) NS = ERROR; endERROR: beginERROR_out;if (i1) NS = ERROR;if (~i1) NS = IDLE;endendcaseend//output tasktask IDLE_out;{o1,o2,err} = 3'b000;endtasktask S1_out;{o1,o2,err} = 3'b100;endtasktask S2_out;{o1,o2,err} = 3'b010;endtasktask ERROR_out;{o1,o2,err} = 3'b111;endtaskendmodule//3-paragraph method to describe FSM//Describe sequential state transition in the 1st sequential always block //State transition conditions in the 2nd combinational always block//Describe the FSM out in the 3rd sequential always block//Westor Wang, Dec. 2006//Verilog Training -- How to write FSM bettermodule state3 ( nrst,clk,i1,i2,o1,o2,err);input nrst,clk;input i1,i2;output o1,o2,err;reg o1,o2,err;reg [2:0] NS,CS;parameter [2:0] //one hot with zero idleIDLE = 3'b000,S1 = 3'b001,S2 = 3'b010,ERROR = 3'b100;//1st always block, sequential state transitionalways @ (posedge clk or negedge nrst)if (!nrst)CS <= IDLE;elseCS <=NS;//2nd always block, combinational condition judgment always @ (nrst or CS or i1 or i2)beginNS = 3'bx;case (CS)IDLE: beginif (~i1) NS = IDLE;if (i1 && i2) NS = S1;if (i1 && ~i2) NS = ERROR; endS1: beginif (~i2) NS = S1;if (i2 && i1) NS = S2;if (i2 && (~i1)) NS = ERROR; endS2: beginif (i2) NS = S2;if (~i2 && i1) NS = IDLE;if (~i2 && (~i1)) NS = ERROR; endERROR: beginif (i1) NS = ERROR;if (~i1) NS = IDLE;endendcaseend//3rd always block, the sequential FSM outputalways @ (posedge clk or negedge nrst)if (!nrst){o1,o2,err} <= 3'b000;elsebegin{o1,o2,err} <= 3'b000;case (NS)IDLE: {o1,o2,err}<=3'b000;S1: {o1,o2,err}<=3'b100;S2: {o1,o2,err}<=3'b010;ERROR: {o1,o2,err}<=3'b111;endcase endendmodule。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

when read=> we <=‘0’;

re<=‘1’; when write=> we <=‘1’; re<=‘0’; end case; end process; End state_machine;

从上面的描述 中,可以总结出用VHDL描述有限 状态机的步骤:

1.用定义的状态类型去定义信号,状态类型为可枚举 类型; 2.在进程中描述有限状态转移,由于状态是当前状态 和输入信号的函数,所以将它们作为进程的敏感信号。 3.在进程中描述状态寄存器的逻辑,状态寄存器功能 是将状态转化为现代。由于转化时在时钟边 ,感想时 钟应为敏感量。 4.在进程中描述输出逻辑,由于输出逻辑是根据当前 状态给输出信号进行赋值,所以进程的敏感信号是当 前状态信号。

但是如果设计人员在设计电路的过程中,需要 把有限状态机的输出作为使能信号,片选信号,复 位信号或时钟信号等来使用时,“毛刺”现象将会 对电路设计造成很大的影响,甚至烧毁电路板。因 此在这种情况下,我们必须保证有限状态机的输出 信号没有“毛刺”产生。 在设计中消除“毛刺”现象的方法很多,这里 介绍一种信号来同步输出信号的消除“毛刺”现象 的方法。利用的方法是用时钟信号将有限状态机的 输出信号加载到另一个寄存器中,该寄存器一般是 由D触发器构成的,它的时钟信号就是有限状态机 的时钟信号。

设计步骤:

1.根据有限状态机与控制器的对应关系。 首先根据控制器的控制步来确定有限状态机的状态。

◆空闲状态IDLE

◆判断状态DECISION

◆读状态READ

◆写状态WRITE

2.根据状态画出状态转移图。

状态转移图是一个非常重要的概念,它表明了有限 状态机的状态和转移条件,有了状态转移图就可以很 容易地写出有限状态机的VHDL描述。

State_rigister: Process( clk ) begin

if ( clk‟event and clk=„1‟) then

present_state<=next_state; end if; End process; End state_machine;

(3) 三进程描述方式是把次态逻辑,状态寄存器和 输出逻辑方在一个进程中,那么这个进程的敏感 信号量应该是时钟clk。

Library ieee;

Use ieee.std_logic_1164.all;

Entity store_controller is port ( ready : in std_logic;

clk : in std_logic;

read_write : in std_logic; we, re : out std_loigc); End store_controller; Architecture state_machine of store_controller is type state_type is ( idle, decision, read, write ); signal present_state, next_state : state_type; Begin State_transfer: process( prestent_state, ready, read_write )

Begin

nextstate_logic: process( prestent_state, ready, read_write )

begin

case

present_state

is

when idle=>if (ready=‘1’) then next_state<=decision; else next_state<=idle; end if; when decision=>if (read_write=‘1’) then next_state<=read; else next_state<=write; end if; when read=>if (ready=‘1’) then next_state<=idle;

三进程描述方式

双进程描述方式

形式2

形式3

单进程描述方式

进程1:描述次态逻辑、状态寄存器和输出逻辑。

利用三进程描述方法和双进程描述方式的 形式来描述有限状态机时,可以把有限状态的 组合逻辑部分和时序逻辑部分分开,这样有利 于有限状态机的组合逻辑部分和时序逻辑部分 进行测试。

不同的描述方式对于综合的结果影响很大, 一般来说,三进程描述方式和双进程描述方式 中的形式和单进程描述方式的综合结果是比较 好的,而双进程描述方式中的形式2和形式3并 不常用。

9.3 有限状态机的同步输出和复位

从有限状态机的结构可以知道,时钟信号和复位 信号对每一个有限状态机来说都是很重要的,特别是 时钟信号是不可缺少的。 8.2.1同步输出信号 无论是MOORE型有限状态机还是MEALY型有 限状态机,它们的输出信号都是经由组合逻辑电路输 出的,因此输出信号会产生“毛刺”现象。对于同步 电路输出来说,由于“毛刺”只是发生在时钟跳变沿 之后的一小段时间里,因此在下一个时钟跳变沿没到 来时“毛刺”已经消失,所以这时“毛刺”现象不会 对电路产生影响。

9.2.2一个MOORE型有限状态机的描述

现要求设计一个存储控制器,它能够根据微处理 器的读周期或者写周期,分别对存储器输出写使能信 号WE和读使能信号RE。该控制器的输入信号有三个: 微处理的准备就绪信号READY,微处理的读写信号 READ—WRITE和时钟信号CLK。

工作过程:

READY有效(或上电复位时)控制器开始工 作并在下一个时钟周期到来时判断本次工作是读M还 是写M(READ-WRITE有效为读,无效时为写) 控 制器的输出写使能信号WE在操作中有效,而读写使 能信号RE在读操作中有效。 读写完毕后READY标 态本次处理任务完成,回到空闲状态。

/read idle read ready read decision

/read_write

read_write read /ready /ready write

3.状态机的输出逻辑

所处状态 idle decision read write re 0 0 1 0 we 1 0 0 1

4.用VHDL语言进行描述

(2)双进程描述方式

第一种形式最好,原因是该描述用两个进程组合 逻辑和时序逻辑分开。

将三进程描述方式中的NEXTSTATE-LOGIC和 OUTPUT-LOGIC合成一个进程STATE-TRANSFEN的 的双进程描述方式的VHDL描述。

这种方式比三进程描述方式要简单得多,VHDL 源代码也要短一些,这样就会使摸拟过程速度加快, 而对综合结果却没有什么影响,因此一般情况下,我 们常采用这种双进程描述方式。 下面用双进程方式描述存储控制器的VHDL程序。

第九章 有限状态机

9.1 概述

有限状态机主要功能是用来实现一个数字电路设计中的控制 部分,它与CPU的功能相似。状态机优于CPU的地方:

1、CPU在实现控制功能的过程中,需要很多的操作指令步骤和 硬件操作单元(如ALU);而有限状态机中,控制状态存储在多 个触发器中,表示状态转移和控制功能的代码存储在门级网络中。

(1)三进程描述方式

Library ieee;

Use ieee.std_logic_1164.all;

Entity store_controller is port ( ready : in std_logic; clk : in std_logic; read_write : in std_logic; we, re : out std_loigc); End store_controller; Architecture state_machine of store_controller is type state_type is ( idle, decision, read, write ); signal present_state, next_state : state_type;

begin

case

present_state is

Hale Waihona Puke when idle=>we<=„0‟; re<=„0‟

if (ready=„1‟) then next_state<=decision; else next_state<=idle; end if; when decision=> we<=„0‟; re<=„0‟ if (read_write=„1‟) then next_state<=read; else else next_state<=read; end if; when write=> we<=„1‟; re<=„0‟ if (read_write=„1‟) then

2、有限状态机逻辑通常十分适用于可编程逻辑器件。通过恰当 的VHDL描述和EDA工具的综合,一般可以生成性能极优的有限 状态机,使其在执行时间、运行速度和占用资源等方面优于由 CPU实现的设计方案。 有限状态机分为两类: Moore型----输出信号仅与当前状态有关

Mealy型----输出信号不仅与当前状态有关,还与所有的输入信号 有关

注意:由于附加了一个时钟同步的寄存器,所以 这时的输出信号将比不加寄存器时的输出信号晚一个 时钟周期。 用时钟信号同步输出信号的MOORE型有限状态机 VHDL描述——存储控制器。

Library ieee; Use ieee.std_logic_1164.all; Entity store_controller is port ( ready : in std_logic; clk : in std_logic; read_write : in std_logic; we, re : out std_loigc); End store_controller; Architecture state_machine of store_controller is