高速信号抖动容限测试技术

基于直接数字合成技术的高速串行信号接收端容限测试新方法

般的数字信号 源能 够对 比较单一 公式或者算 法去任意定义 。

升时间 , 均可以通过泰克的S r l p es ei X rs a

的规 律性变化的数字信号进行模拟 ,如

直接合成信号源除 了能够 合成含任 软件方便快捷的进行定义 ,并可以实时

信号中含有随机噪声 ,或者信号 的抖 动 何抖动规律 或者噪声的信号 ,建立随机 模拟实现效果 ,如 图 3 所示。 以单一的正弦规 律或 者三角波规律 变化 抖 动和确定性 抖动 的影 响模 型 , 以定量 对于去加重信号的直接合成方法完

技术正在 改变这一切 , 接合成工具 可 成一 个 测 试信 号 ,拥有 所 需 的全 部 时 在相对 宽的频率范 围内 ,而降低频谱 的 直

S( 。 以帮助设计人 员创建现实程度更高 的信 序 、幅度和失真 特点 ,而不是像一 般的 尖峰值 ,一般称为 S C 扩 频时钟)

号 ,并 极 大 地 减 少 复 杂 的 测 试 设 置 和 多 数字信号 源那…

一

维普资讯

专题特写:高速串行数据测试

传 统数 字信 号源 对串行信 号特性 进行模 以定义任 何波形 ,这些样点可 以从示波

拟 的方 法

一

对于合成信号的速率 、抖动注入的

器 采 集 的 实 际 波 形 中 获 得 ,也 可 以 采 用 频 率 和 幅 度 、噪 声 的 幅 度 以 及 信 号 的 上

改善接收机 串行信号完 全 由简单 的二 进制数 l 实际工作环境中高速串行信号的模拟特性 偿传输线对高频分量的衰减 ,

和0 组成 。为什 么要 使用直接数 字合成

由于传输介 质的衰减 以及反射会导 输入上的信号保真度。 但必须在设计阶段

在调 模拟波形来表 示数字数据呢 ?这是 因为 致信号 不同程度 的劣化 ,具体 表现为抖 全面评估串行设备对去加重的响应 。 调节去加 在数字信号 中隐含 的是 模拟事件 。书本 动 的增 大 ,信号 幅度 的衰 减等 。在实 际 试过程中可 以根据实际的情况 , 上理想的数 字信号的零上升时 间和完美 工作环境 中 ,随着信号速 率的提高 ,传 重的比例以获得最好的传输效果。

一种高速SERDES抖动容限的高效仿真验证方法

一种高速SERDES抖动容限的高效仿真验证方法邵刚;田泽;李世杰;吕俊盛【摘要】文中针对高速SERDES总线接收端的验证提出了一种抖动容限验证方法,有效降低了流片风险。

由于受温度、布线、信道寄生的影响较大,高速SERDES需要保证在恶劣信道,尤其是大的抖动干扰时仍能稳定工作,设计阶段对接收电路抗抖动特性的评估是一个复杂的验证过程,鲜有报道。

文中基于对PCIE,SRIO,FC等信道和协议的研究,提出一种快速高效的RX端抖动容限的验证评估方法。

经验证采用该模型能方便准确地评估RX的特性,经电路流片后,实际测试表明,采用该方法评估的抖动容限结果与测试结果精确符合,可在设计阶段显著优化RX的性能,并大幅降低流片的风险。

%Aiming at high speed SERDES bus validation at the receiving end,put forward a jitter tolerance verification method,effectively reducing the risk of a flow chip. For many factor can affect SERDES,such as temperature,wiring and the parasitic of channel,it needs to work stably in many cases,the assessment of jitter characteristics for the receiving circuit in design phase is a complex validation process, with few reports. Based on the protocol of PCIE,SRIO and FC,a fast and efficient verification and evaluation method is proposed for RX end jitter tolerance. The model proposed in this method can accurately assess the convenient characteristics of RX. The test result indicates that the jitter tolerance evaluated by the model can tally with the test resultsaccurately,significantly optimizing the performance of RX in design stage and reducing the risk of flow chip largely.【期刊名称】《计算机技术与发展》【年(卷),期】2015(000)007【总页数】4页(P217-220)【关键词】SERDES;抖动容限;验证;CDR;时钟恢复电路【作者】邵刚;田泽;李世杰;吕俊盛【作者单位】中航工业西安航空计算技术研究所,陕西西安 710065;中航工业西安航空计算技术研究所,陕西西安 710065;中航工业西安航空计算技术研究所,陕西西安 710065;中航工业西安航空计算技术研究所,陕西西安 710065【正文语种】中文【中图分类】tP301高速数据通路是计算机通信的基础,制约着计算机和其他通信系统的I/O处理能力,而高速SERDES接口芯片的研究是其中非常重要的部分。

Agilent USB3.0物理层测试方案

USB3.0物理层测试方案一、 USB3.0简介USB的规范最早由USB协会(USB-IF)在1996年推出,经过10多年的发展,已经成为PC及其外设上应用最为成功的接口。

USB1.0的速度不够时,USB协会在2000年推出了USB2.0标准。

目前普遍应用的是USB2.0的规范,USB 2.0 的最高速率指标定义是480Mbps,但实际上因各种限制因素,真实的数据吞吐速率不超过 35MB/s。

现在移动硬盘、高清视频等的应用中需要传输的数据量越来越大,文件的尺寸越来越大,存储或传输的时间也相应变长。

与此同时,SATA、HDMI、Displayport等也以其高传输数据速率的优势在抢夺一部分传统USB的市场。

因此,为了满足高速数据传输的要求,USB协会在2008年底正式发布了USB3.0的规范。

目前USB3.0的测试规范正在制定过程中,预计在2010年3月份左右会正式发布。

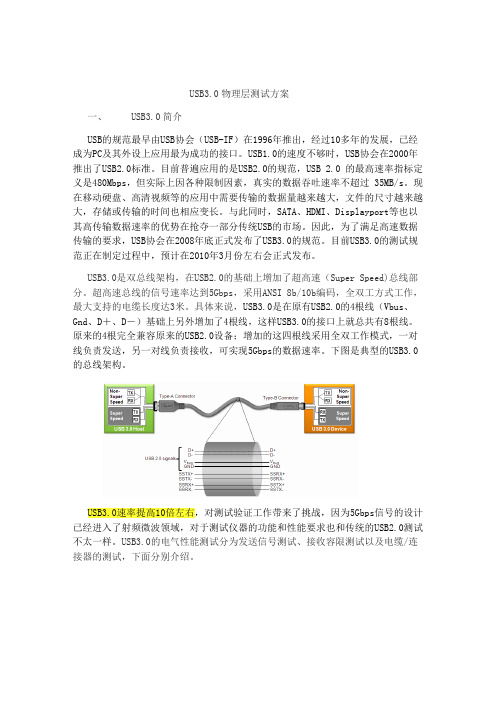

USB3.0是双总线架构,在USB2.0的基础上增加了超高速(Super Speed)总线部分。

超高速总线的信号速率达到5Gbps,采用ANSI 8b/10b编码,全双工方式工作,最大支持的电缆长度达3米。

具体来说,USB3.0是在原有USB2.0的4根线(Vbus、Gnd、D+、D-)基础上另外增加了4根线,这样USB3.0的接口上就总共有8根线。

原来的4根完全兼容原来的USB2.0设备;增加的这四根线采用全双工作模式,一对线负责发送,另一对线负责接收,可实现5Gbps的数据速率。

下图是典型的USB3.0的总线架构。

USB3.0速率提高10倍左右,对测试验证工作带来了挑战,因为5Gbps信号的设计已经进入了射频微波领域,对于测试仪器的功能和性能要求也和传统的USB2.0测试不太一样。

USB3.0的电气性能测试分为发送信号测试、接收容限测试以及电缆/连接器的测试,下面分别介绍。

二、 USB3.0的发送信号测试在进行发送端测试时,要求测试对象发出特定的测试码型,实时示波器对该码型进行眼图分析,测量信号的幅度、抖动、平均数据率及上升∕下降时间。

HDMI原理及测试方法

13

2009-9-21

高速信号完整性工程师培训课程

HEAC-HDMI Ethernet and Audio Return Channel

14

2009-9-21

高速信号完整性工程师培训课程

高速串行信号的一致性测试的要求

•

Harmonic dB

HDMI 1.3/1.4实际最高Data Rate=2.97Gbps, HDMI 1.2实际最高Data Rate=1.485Gbps • 对于HDMI 2.97Gbps,由于其是非归零码,基频为 2.97/2=1.485GHz,5次谐波为1.485*5=7.425GHz 规范推荐使用8Ghz示波器进行测试。 • 对于HDMI 1.485Gbps,5次谐波为3.7GHz • 规范推荐使用4Ghz示波器进行测试。

12 2009-9-21 高速信号完整性工HEAC 定义的信号

•

低幅度的以太网信号

– – – – 只有200mVp-p 相对于 1Vp-p 的普通以太网信号 差分200mVp-p 除了幅度以外,完全遵循以太网标准 125Mbps的 数据传输率

•

双向的以太网传输

– 支持发送和接收数据流 – 在收发器中内嵌混合堆叠电路

7

2009-9-21

高速信号完整性工程师培训课程

TMDS Data与Clock的关系

• •

在每个TMDS时钟周期上发送10个数据位 TMDS 数据速率可以提高到340Mpps

– 数据速率理论上可以高达 1.65Gbps(1.2),在实际应用中的最高速率是 1920*1080P/50Hz/24bit下是1.485Gbps – 数据速率可以高达 3.4Gbps(1.3),在实际应用中的最高速率是 1920*1080P/50Hz/48bit下是2.97Gbps – 在HDMI 1.4规范中实际应用的数据速率同样是2.97Gbps 4096*2160/24Hz/24bit

抖动测试方法

抖动测试方法

在2.5G设备开局时,经常需要测试设备的抖动指标。

一个信号由于系统的时钟、芯片的门限等的影响,因此引起了输出数据的前后移动,当前后移抖动的频率大于10HZ时,我们就认为,这一种现象是一种抖动,抖动不能很大,否则会对下游站产生很不利的影响。

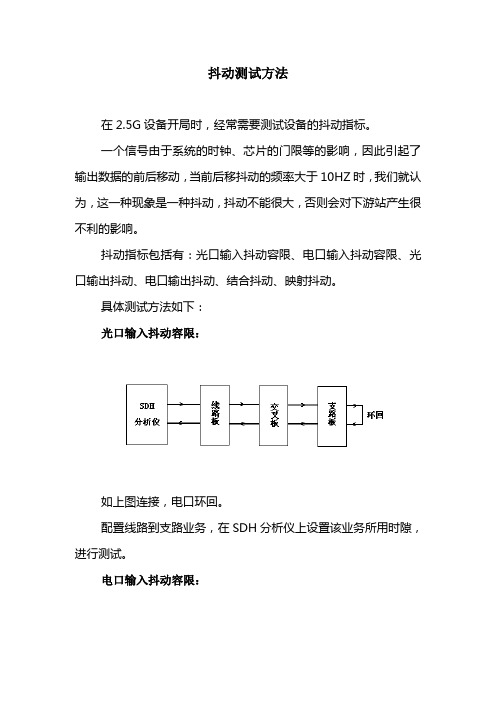

抖动指标包括有:光口输入抖动容限、电口输入抖动容限、光口输出抖动、电口输出抖动、结合抖动、映射抖动。

具体测试方法如下:

光口输入抖动容限:

如上图连接,电口环回。

配置线路到支路业务,在SDH分析仪上设置该业务所用时隙,进行测试。

电口输入抖动容限:

如上图连接,光发电收。

配置线路到支路业务,在SDH分析仪上设置该业务所用时隙,进行测试。

光口输出抖动:

如上图连接,电口环回。

配置线路到支路业务,在SDH分析仪上设置该业务所用时隙,进行测试。

电口输出抖动:

如上图连接,光口环回。

配置线路到支路业务,在SDH分析仪上设置该业务所用时隙,进行测试。

映射抖动、结合抖动:

如上图连接,电发光收。

配置线路到支路业务,在SDH分析仪上设置该业务所用时隙,进行测试。

2M端口的抖动测试

四、2M 端口的抖动容限测试

1 指标含义

一个信号由于系统的时钟、芯片的门限等的影响,因此引起了输出数据的前后移动,当前后移动的频率大于10HZ 时,我们就认为,这一种现象是一种抖动,抖动不能很大,否则会对下游站产生很不利的影响。

频率偏差的最大值称为抖动峰-峰值,用它来衡量抖动大小,单位为UI ,表示单位时隙。

它在数值上等于传输速率的倒数。

2 测试仪表

SDH/PDH 传输分析仪、SDH 待测设备、2M 线缆

3 测试框图

4 测试步骤

1)、按[其它]键,设置“耦合”方式。

2)、按[发送]键,进入PDH 发射部分的设置菜单。

用方向键和软键设置信号速率、帧结构和图形。

3)、用软键进入抖动设置菜单。

4)、按[开始/结束]键,进行抖动容限的扫描测量。

按[结果]键,再用方向键和软键显示在抖动容限下的误码和设备抖动转移特性。

5)、如不在被测设备的入口人为地插入抖动,则可进行被测设备的输出抖动测量。

注意事项

测外接设备的抖动需要加滤波,传输分析仪本身自环不需要加滤波。

1)输出抖动幅度

当系统无输入抖动时,输出口的信号抖动称为输出抖动。

在本试验中,用带通滤波器(F1-F4)对2M 支路的输出进行测试,输出抖动幅度不应超过:0.75UI(数字段),1.5UI(全程)。

2)输入抖动容限

SDH分析仪 发射 SDH分析仪 接收 发送接收接收发送

12环回SDH1SDH2

A 0

A 1

A 2F 0F1F2F3F4f 0J p-p /UI

斜率20dB/10倍频程。

高速信号完整性工程师培训认证课程-Displayport

Flying Lead Probe

• • • • •

支持DisplayPort 线宽 – X1, X2, X4 热插拔监测 全辅助通道解码 支持泰克逻辑分析仪 实时滤波简化综合测量

Interposer Probe

26

2011/1/21

Tektronix Innovation Forum 2009

Tektronix 反汇编汇编

2011/1/21

Tektronix Innovation Forum 2009

辅钟 (Manchester II 编码)

– 链接速率: 1 Mbps

• 源端是主 接收端是从 • 时间通知热插拔检测 (HPD)

– DisplayPort 数据构造 (DPCD) 记录

简化最新的 DisplayPort 一致性测试

- Tektronix DisplayPort 1.1 测试方案

日程

• 简介 • 源端测试

• 接收端测试

• 线缆测试 • 协议分析

• 概要

• 额外资源

2

2011/1/21

Tektronix Innovation Forum 2009

简介

•

• •

DisplayPort 是一个新的数字显示标准接 口

辅助通道观测

主链接观测

FuturePlus Systems

27 2011/1/21

Tektronix Innovation Forum 2009

Tektronix 带来专业的 DisplayPort 测试

Tektronix DisplayPort 一致性测试

•

ET-DP-TPA-P (Plug Fixture)

16

信号完整性分析基础系列之十——理解串行数据测试中的总体抖动算法

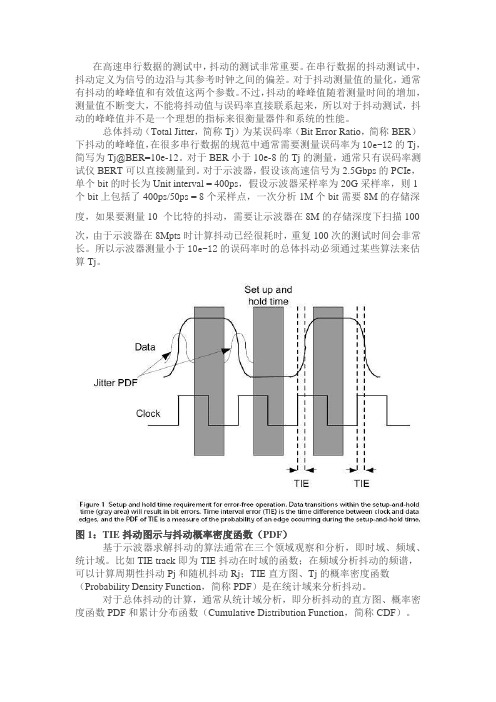

在高速串行数据的测试中,抖动的测试非常重要。

在串行数据的抖动测试中,抖动定义为信号的边沿与其参考时钟之间的偏差。

对于抖动测量值的量化,通常有抖动的峰峰值和有效值这两个参数。

不过,抖动的峰峰值随着测量时间的增加,测量值不断变大,不能将抖动值与误码率直接联系起来,所以对于抖动测试,抖动的峰峰值并不是一个理想的指标来很衡量器件和系统的性能。

总体抖动(Total Jitter,简称Tj)为某误码率(Bit Error Ratio,简称BER)下抖动的峰峰值,在很多串行数据的规范中通常需要测量误码率为10e-12的Tj,简写为Tj@BER=10e-12。

对于BER小于10e-8的Tj的测量,通常只有误码率测试仪BERT可以直接测量到。

对于示波器,假设该高速信号为2.5Gbps的PCIe,单个bit的时长为Unit interval = 400ps,假设示波器采样率为20G采样率,则1个bit上包括了400ps/50ps = 8个采样点,一次分析1M个bit需要8M的存储深度,如果要测量10个比特的抖动,需要让示波器在8M的存储深度下扫描100次,由于示波器在8Mpts时计算抖动已经很耗时,重复100次的测试时间会非常长。

所以示波器测量小于10e-12的误码率时的总体抖动必须通过某些算法来估算Tj。

图1:TIE抖动图示与抖动概率密度函数(PDF)基于示波器求解抖动的算法通常在三个领域观察和分析,即时域、频域、统计域。

比如TIE track即为TIE抖动在时域的函数;在频域分析抖动的频谱,可以计算周期性抖动Pj和随机抖动Rj;TIE直方图、Tj的概率密度函数(Probability Density Function,简称PDF)是在统计域来分析抖动。

对于总体抖动的计算,通常从统计域分析,即分析抖动的直方图、概率密度函数PDF和累计分布函数(Cumulative Distribution Function,简称CDF)。

抖动产生及测试

抖动产生及测试一、信号完整性测试手段抖动测试、波形测试、眼图测试,是三种常用的信号完整性测试。

1.抖动测试:抖动测试现在越来越受到重视,因为专用的抖动测试仪器,比如TIA(时间间隔分析仪)、SIA3000,价格非常昂贵,使用得比较少。

使用得最多是示波器加上软件处理,如TEK 的TDSJIT3 软件。

通过软件处理,分离出各个分量,比如RJ 和DJ,以及DJ 中的各个分量。

对于这种测试,选择的示波器,长存储和高速采样是必要条件,比如2M 以上的存储器,20GSa/s 的采样速率。

不过目前抖动测试,各个公司的解决方案得到结果还有相当差异,还没有哪个是权威或者行业标准。

2.波形测试首先是要求主机和探头一起组成的带宽要足够。

基本上测试系统的带宽是测试信号带宽的3 倍以上就可以了。

实际使用中,有一些工程师随便找一些探头就去测试,甚至是A 公司的探头插到B 公司的示波器去,这种测试很难得到准确的结果。

波形测试是信号完整性测试中最常用的手段,一般是使用示波器进行,主要测试波形幅度、边沿和毛刺等,通过测试波形的参数,可以看出幅度、边沿时间等是否满足器件接口电平的要求,有没有存在信号毛刺等。

由于示波器是极为通用的仪器,几乎所有的硬件工程师都会使用,但并不表示大家都使用得好。

波形测试也要遵循一些要求,才能够得到准确的信号。

其次要注重细节。

比如测试点通常选择放在接收器件的管脚,如果条件限制放不到上面去的,比如BGA封装的器件,可以放到最靠近管脚的PCB 走线上或者过孔上面。

距离接收器件管脚过远,因为信号反射,可能会导致测试结果和实际信号差异比较大;探头的地线尽量选择短地线等。

最后,需要注意一下匹配。

这个主要是针对使用同轴电缆去测试的情况,同轴直接接到示波器上去,负载通常是50 欧姆,并且是直流耦合,而对于某些电路,需要直流偏置,直接将测试系统接入时会影响电路工作状态,从而测试不到正常的波形。

3.眼图测试眼图测试是常用的测试手段,特别是对于有规范要求的接口,比如E1/T1、USB、10/100BASE-T,还有光接口等。

高速SerDes抖动成因及其测试方法分析

7 07 ) 10 7 ( 西安航 空计算技 术研 究所 ,西安

摘 要 :高速 Sr s(E Ale/ Srle) 备 在 高速 芯 片 IO 接 口互联 上 已经 占有统 治性地 位 。然 而随 着 串行 e De SR azr i DE e azr 设 ii / 链 路 速率 不 断提 高 , 随之 而 来的抖 动等 因素 对 高速 Sr s 品 率构成 极大威 胁 。本 文首先 对 Sr s e De成 e De 的结构 进行介 绍 , 然后 对高速 Sr e 中信号抖动进行定性分析 , eD s 最后提 出了几种重要的 Sr s e De 测试方法 , 对高速 Sre 的测试具有一定参考价值。 e s d

【信号完整性测试方法】时域测试(波形、眼图、抖动、TDR、时序)要求 及 仪器设备

【信号完整性测试方法】时域测试(波形、眼图、抖动、TDR、时序)要求及仪器设备信号完整性测试方法简介信号完整性设计,在电路板设计过程中备受重视。

熟悉各类测试方法的特性,按照测试对象的特征和需求,选用合适些测试方法,对于选择方案,验证效果能够大大提高效率。

目前信号完整性的测试方法较多,从大的方向有频域测试、时域测试、其它测试。

(3类方法不是任何情况下都适合使用,信号完整性的测试方法,需要用到的仪器也很多。

)时域测试时域测试涵盖波形测试、眼图测试、抖动测试、TDR测试、时序测试。

01波形测试波形测试:是信号完整性测试最基础的方法,通常使用示波器进行测试。

测试波形的幅度、毛刺、边沿等。

通过测试波形的特征,分析幅度、边沿时间等指标是否满足要求。

波形测试需要遵循一定要求,才能保证测试误差尽量小。

⏹主机和探头一起配套的带宽要满足要求。

基板上测试系统的带宽应该在测试信号带宽的3倍以上。

在工程实践中,有的工程师随意找些探头就测试,不同厂家的探头匹配不同厂家的示波器,综合情况测试系统的误差就会很大。

⏹其次,需要注重细节。

如测试点一般选择在接收器件的附近,若条件限制无法测试,像BGA封装这类的器件,需要放在靠近Pin脚的PCB走线上或者Via上。

间隔接收器件PIn脚太远,信号发射,可能会促使测试结果和实际真实信号差异较大。

探头的接地线,也尽可能选择短的地线等。

⏹最后,应该考虑匹配。

主要关于使用同轴电缆测试的应用场景,同轴接到示波器上,负载常规是50Ω阻抗的直流耦合,对于有的电路,需要直流偏置,直接将测试系统接入会导致电路工作状态有影响,最终导致测试不到正常的波形。

02眼图测试眼图测试:针对有相关规范要求的接口(USB、SATA、HDMI、光接口)等。

通过具有MASK的示波器(含通用示波器、采样示波器、信号分析仪)。

这类示波器内部具有的时钟提取功能,能够显示眼图。

然而对于没有MASK的示波器,需要使用外接时钟实现触发。

高速信号抖动容限测试技术

Pre-Emphasis BitAlyzer • 基本的误码仪和示 • 配合BERTScope 码型发生器使用 波器 • 最低码速率100K, • 提高输出加重以克 服通道损耗 适合于卫通应用 • Rx端容限中使用 Linear Equalizator • 复杂线性均衡 • 信道模拟

ቤተ መጻሕፍቲ ባይዱ1.5G/1.6G

Vertical slice

Eye height at 1012 BER level

Beyond the BERT...

使用BERTScope深入分析误码率事件

规范要求的接口一致性验证

模板测试

看到BER Contour之后,可以进行Mask测试,看看是否满足一定误码率 前提下的Mask要求。 如果BER Contour压到Mask的话,可以通过将设置BERTScope的 sampler到压点的位置上,进而深入分析误码出现的规律。

BERTScope

PatternPro

PPG4001 40 Gb/s Pattern Generator

X

X X

X X X

03/2014 ©Tektronix 65W-28713-3

27

误码率分析工具带来的启示 – 误码定位

如果是数字调制呢?

误码率分析工具带来的启示 – 误码率带状图

误码率分析工具带来的启示 – 无误码间隔图 (Error Free Interval)

将busrt中的最小无误码长度 设为1,实际观察的就是连续 出现误码的统计 如果连续出现的误码不相关? 判定连续误码的相关,找到系 统问题 1500 bit的前向纠错 突发长度统计中基本都是 1500bit的倍数 FEC算法出现问题

高速公路机电工程质量试验检测方法

闭路电视监视系统 ,使用信号发生器代替视频源发送标准信

号 ,使用 视 频测 量 仪在 站所 接 收信 号测 试 ,此 单项 仪 器测 试需 与 其他 测 试项 目分 开 ,单 独 进行 ,因发 送接 收备 配一 人 ,若 同 时现

高速 公 路 机 电工 程 质 量 试验 检 测方 法

机 电工程检测 贯穿于高 速公路机 电工程建设 全过程 ,是对机 电设施 的运行 状况

进行综合评价 ,检测工作是质量 管理的技术保障 。

安徽 省高速公 略试验检测科研 中心 沈国栋

机 电工 程检 测贯 穿 于高 速公 路 机 电工程 建设 全 过程 ,是对 机 电设 施 的运 行状 况 进行 综合 评 价 ,检 测 工作 是质 量 管理 的技 术 保 障 。公 证 与 严谨 的 检测 是公 路机 电工程 质 量 管理 的技 术 保 障 ,是 工 程 项 目连 续质 量 控制 链 中不 可 或缺 的重 要 一环 。机 电工程 施 工 过 程 中任 何 一个 环节 的 质量 控 制都 离 不开 科 学公 正 的试 验检 测 数

行测试。

要 检测 安 装 的工 艺与 质 量 ,包括 设 备安 装 位置 、牢 固性 、接 地性

能 、保 障措 施 、安装 环境 等 。外 观 检查 指对 设 备外 观 的 完好 性 、

清 洁度 等 进行 检 查 。本 文重 点 阐述 机 电工程 检 测 的重 点和 针 对一 些 常见 问题 的防 治思 路 。

l 、设 备 可靠 性 、维 护方 便 l 生和维 护成 本 。

2 、设 备 的升级 能力 和 可扩艮 _ 生,避免 系统 过早 淘汰 。

面向空间辐照环境的星载高速数字接口芯片设计方1

面向空间辐照环境的星载高速数字接口芯片设计方法高速串行接口通常也称为SerDes接口,已逐步取代传统并行接口而成为当前数字传输的主流接口技术。

在空间应用中,SerDes接口由于体积小的优势,已成为星载计算机和通信设备间重要接口。

然而,由于SerDes接口传输速度快,外层空间电离辐照在接口芯片内部产生的单粒子翻转(SEU)或单粒子瞬态(SET)效应很容易引起接口芯片的物理编码子层(PCS)模块及物理介质接入子层(PMA)模块出错,从而出现显著的误码,因此为了保证可靠性,星载设备必须采用经过抗辐照加固的高速接口芯片。

在判断辐照加固成效方面,高速SerDes接口等新一代的抗辐照高速元器件在轨翻转主要采用绘制饱和翻转截面值的方法,拟合出器件的在轨翻转率。

在轨翻转率可以评价器件在轨道空间中的翻转发生概率,但无法直接评价电路在空间中无错误传输的安全阈值。

采用在轨翻转率曲线上首次发生传输错误事件的入射粒子能量作为辐照的单比特错误阈值(On SET),用来评价接口类电路能够保证的无错误传输的粒子线性能量转移(LET)阈值能量大小。

经典的低速数字接口芯片采用全局三模冗余(GTMR)及增大节点电容的设计加固方法牺牲了电路的工作速率,因此不适合用于高速SerDes接口的设计加固。

主要的SerDes加固方式包括工艺加固及编码部分三模冗余(TMR)设计加固,或者二者结合方法。

文献[12]中的SerDes接口采用抗辐照加固的绝缘体上硅(SOI)工艺进行设计,其出现单比特错误的LET阈值约为2 MeV·cm2/mg,连续错误比特致复位的辐照阈值约为20 MeV·cm2/mg,单位器件饱和翻转截面值约10-5 cm2。

文献[13]中的SerDes芯片采用抗辐照加固的体硅CMOS工艺,并对数字编码进行TMR设计加固,其单比特错误辐照阈值为1 MeV·cm2/mg,连续性错误辐照阈值为10 MeV·cm2/mg,单位器件饱和翻转截面值约为10-4 cm2。

一款功能全面的M8020A比特误码率测试仪技术资料

Keysight J-BERT M8020A高性能比特误码率测试仪技术资料版本 2.0(新增内容: 集成可调节码间干扰ISI)永远从容应对下一个设计说明是德科技高性能 J-BERT M8020A 能够对速度高达 16 或 32 Gb/s 的单通道和多通道器件进行快速、精确的接收机表征。

M8020A 提供目前最全面的综合功能,可以简化您的测试设置。

并且,在线自动信号条件校准可以确保精确、可重复的测量结果,通过交互式的链路训练,它可以充当您的被测器件的链路伙伴。

集如此众多优势于一身,J-BERT M8020A 将会加速您的设计验证。

主要特性:–数据速率高达 8.5 和 16 Gb/s,可扩展至 32Gb/s–在 5 插槽 AXIe 机箱内可提供 1 至 4 个比特误码率测试仪通道–综合和校准的抖动注入:RJ、P J1、P J2、SJ、BUJ、正弦干扰(共模和差摸)、SSC (三角波、任意波形和剩余噪声) 和时钟/2–8 分接去加重,正值和负值–集成和可调 ISI–PCI Express 交互式链路培训–内置时钟恢复和均衡–所有选件和模块均可升级应用:J-BERT M8020A 以研发和测试工程师为设计对象,帮助他们表征和验收芯片、器件、电路板以及在消费类产品、计算机、移动计算机、数据中心和通信行业内具有 16 Gb/s 和 32 Gb/s 串行 I/O 端口的系统。

J-BERT M8020A 可以测试各种流行总线标准,例如 PCI Express ®、SATA/SAS、DisplayPort、USB 超高速、MIPI ® M-PHY ®、SD UHS-II、光纤通道、QPI、存储器总线、背板、中继器、有源光纤、Thunderbolt (雷电) 连接器标准、10/40 GbE/SFP+/QSFP、100GbE/CFP2。

M8000 系列比特误码率 (BER) 测试解决方案开发下一代计算机、消费电子产品或通信设备时,简化时效性测试十分必要。

高速信号测试基础知识(去加重-预加重)

去加重 de-emphasis

去加重技术的思想跟预加重技术有点类似,只是实现方法有点不同, 预加重是增加信号上升沿和下降沿处的幅度,其它地方幅度不变;而去加 重是保持信号上升沿和下降沿处的幅度不变,其他地方信号减弱。

去加重补偿后的信号摆渡比预加重补偿后的信号摆幅小,眼图高度低 ,功耗小,EMC辐射小。

。

目录

高速串行信号LVDC 抖动的分析

1

2 3 4 5

眼图的说明

其它 PCIe信号测试实例

PCIe信号的测试

测试准备:

16G以上带宽示波器;

TCA_SMA转换头; 高速测试线缆-PCIe;

测试夹具CLB。

测试软件RT-eye

PCIe测试过程

测试步骤:

择Analyze->RT-Eye Compliance and Analysis启动软件,点击Run Wizard进入导航界面;或者选择Measurements->Wizard进入导航界面; Step 1中选择探头类型,使用SMA线缆选择Single-Ended ; Step 2选择信号通道,一般高速串行信号单端连接,选择Ch1和Ch3 ; Step 3选择PCIe信号速率,根据实际选择PCIE:2.5G或5.0G; Step 4选择测试项目,一般默认全选; Step 5选择默认Yes ; Step 6选择默认Yes; Step 7选择测试结果显示图像内容,选择默认全部; 观察示波器捕捉信号,确认正常后,保持示波器Run状态,Mode为

Single Run,点击Start开始测试。

Pcie测试步骤

实测pcie_5G信号结果

USB信号测试结果

谢谢!

串行传输的基本框图

1.由硬件上数据线路的减少到速度越来越高. 2. 包含数据和时钟. 3. 电压越来越低. 250--450mv 4. LVDS是由电流驱动,恒定3.5mA. 则 3.5mAX100欧=350mv

高速OC-48SDHSONET光收发模块的抖动测量(转载)

⾼速OC-48SDHSONET光收发模块的抖动测量(转载)SDH/SONET(同步数字序列/同步光纤⽹络)需要⾼稳定、⾼精度的同步来处理经过⽹元的数据。

⽹络产⽣的任何相位变化或者说抖动都会恶化传输质量,提⾼误码率,或者造成数据丢失。

所以,理解抖动和它对⽹络性能的影响就变得⾄关重要。

下⾯将详细讨论对⽤于SDH/SONET⽹络中的OC-48(2.5Gbps)光收发模块的抖动测量⽅法以及测试性能。

图1 ⽤⽰波器和相位检测器来测量抖动的实验装置图2 ⽤多速率SONET/SDH测试仪来测量抖动产⽣的装置图3 抖动容限和抖动传递的测量装置如何测量抖动通常抖动是⽤单位间隔(UI)来度量的,⼀个UI代表⼀个时钟周期的相位变化。

抖动的百分⽐按下式计算:抖动 = (Tj/T0) x 100%式中是Tj抖动的幅度,T0是时钟周期。

⼀个单位间隔表⽰100%的抖动。

在这⾥需要注意到单位间隔是与⽐特率⽆关的。

因此,在不同的速率等级下,对⽹元的抖动幅度进⾏⽐较是可⾏的。

在没有施加抖动的情况下,⼀个SONET/SDH⽹元的OC-N/STS-N输出端⼝的抖动就是模块产⽣的抖动。

抖动参数有两种定义:●峰峰抖动:测得的最⼤抖动幅度,●均⽅根抖动:抖动信号的均⽅根值,表征了抖动的强度。

对抖动的规范适⽤于⽹元的整个系统。

在OC-48的速率下,Telcordia GR-253标准有关抖动产⽣的规范规定,在使⽤通带为12KHz〜20MHz的滤波器时,⽹络设备的抖动峰峰值⼩于100 mUIp-p,抖动的均⽅根值⼩于10 mUIrms。

测量抖动容限和抖动传递特性也是需要的。

●抖动容限:灵敏度降低1dB时,⽹元OC-N/STS-N输⼊端⼝施加的正弦抖动信号的峰峰幅值。

抖动容限这个性能指标表征了时钟和数据恢复电路(CDR)在有外加抖动的情况下正确恢复输⼊⽐特序列的能⼒。

●抖动传递:在OC-N/STS-N输出端抖动与OC-N/STS-N输⼊端抖动的⽐值随频率的变化关系。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Pre-Emphasis BitAlyzer • 基本的误码仪和示 • 配合BERTScope 码型发生器使用 波器 • 最低码速率100K, • 提高输出加重以克 服通道损耗 适合于卫通应用 • Rx端容限中使用 Linear Equalizator • 复杂线性均衡 • 信道模拟

1.5G/1.6G

高速信号抖动容限测试技术

目录

通信系统与误码率 误码率测试原理 误码率分析工具带来的启示 抖动容限测试的意义 泰克误码率分析仪BERTScope产品系列

通信系统与误码率

信源

CRC校验 信道编码

交织

误码测试的原理

误码率测试中存在的问题

信源编码与解码 基带通信 载波调制与解调 信道编码与解码 射频传输与接收 误码控制要求,CRC与FEC

预测系统未来变化趋势

BER等高线

Beyond the BERT...

使用BERTScope深入分析误码率事件

Jitter 1

Horizontal slice Bertscan, d-d, ber bathtub Eye width at 1012 BER level

2 3 BER Contour Eye Height

误码率分析工具带来的启示 – 误码定位

如果是数字调制呢?

误码率分析工具带来的启示 – 误码率带状图

误码率分析工具带来的启示 – 无误码间隔图 (Error Free Interval)

将busrt中的最小无误码长度 设为1,实际观察的就是连续 出现误码的统计 如果连续出现的误码不相关? 判定连续误码的相关,找到系 统问题 1500 bit的前向纠错 突发长度统计中基本都是 1500bit的倍数 FEC算法出现问题

扩频时钟(SSC) 可靠和锁定带SSC的信号 测量SSC波形

PLL Testing with CRU

25

13-DEC-2013

BERTScope系列产品概览

Clock Recovery BERTScope • 配合BERT和示波 • 主要产品BSA系列 器使用 • BERT和示波器的结 合,基于BER的分析、• 抖动频率测量 • SSC测试 测试平台 • 主要应用于高速串行 和通信的芯片、系统 测试 • 可单独作为信号源使 用 28.6G 26G 17.5G 17.5G 12.5G 12.5G 8.5G

PCIE GEN1,2,3

SATA I,II,III USB3 Display Port XFP/XFI 10GBase-KR Optical Serial Bus...

Test for compliance

Use Search mode to find device limits

Integrated Solution

BERTScope

PatternPro

PPG4001 40 Gb/s Pattern Generator

X

X X

X X X

03/2014 ©Tektronix 65W-28713-3

27

Байду номын сангаас

Vertical slice

Eye height at 1012 BER level

Beyond the BERT...

使用BERTScope深入分析误码率事件

规范要求的接口一致性验证

模板测试

看到BER Contour之后,可以进行Mask测试,看看是否满足一定误码率 前提下的Mask要求。 如果BER Contour压到Mask的话,可以通过将设置BERTScope的 sampler到压点的位置上,进而深入分析误码出现的规律。

BERTScope时钟恢复仪

1

Jitter Spectrum 集成抖动测量 抖动频率范围200Hz 到90 MHz 数据率1.2 到11.2 Gb/s

2

4

从闭合的眼图中恢复时钟 在时钟路径上集成了均衡 无分接的高灵敏度模块

3

灵活的校准的环路带宽和 peaking 针对USB3.0抖动传输函数 提供高带宽的loop bandwidth

12.5G 32G

A Full Range of BERT Testers from Tektronix Summary

BERTScope Series PatternPro Series

BSA286C 28.6Gb/s. 1-channel Bit Error Rate Tester

抖动容限测试的意义

接收机时钟恢复

锁相环的结构

关于时钟恢复(锁相环)的考虑

19

TPI4000 Series Overview

环路带宽其他特性的影响

20

其他特性的影响,如SSC

21

接收机抖动容限测试的意义

22

TPI4000 Series Overview

Stressed Eye

自动化Jitter Tolerance一致性测试方案

BA1600 1.6Gb/s. 1-channel Bit Error Rate Tester

PED3202 40 Gb/s, 2-channel Error Detector

PPG3204 32 Gb/s, 4-channel Pattern Generator

Application/Usage Single Channel BERT <28.6Gb/s >28.6Gb/s Multi-channel BERT/PG/ED Built-in Analysis Integrated Compliance Testing Separate PG or ED

误码率分析工具带来的启示 – 突发长度与无误码间隔图

无误码间隔出现在1500,3000, 4500,由此可以判定误码应该 是系统性问题

误码率分析工具带来的启示 – 误块率

误码率分析工具带来的启示 – 2D误码率显示

误码率分析工具带来的启示 – FEC模拟

定位抖动来源

抖动分离-RJ/DJ