外文翻译---关于直接数字频率合成器

直接数字频率合成的优缺点

直接数字频率合成的优缺点直接数字频率合成(Direct Digital Frequency Synthesis,DDFS)是一种通过数字信号处理技术生成高频信号的方法。

DDFS 可以用于各种应用,包括实验室测试、通讯和雷达系统等。

本文将讨论 DDFS 的优缺点。

优点稳定性DDFS 系统中只能从数字源获得频率,所以频率精度非常高。

DDFS 的准确性可以通过采用高质量的晶体振荡器和时钟同步技术来进一步提高。

此外,由于数字元件的稳定性,DDFS 的频率是非常稳定的。

灵活性DDFS 提供了比传统频率合成器更高的灵活性。

传统频率合成器需要使用不同的电路元件来生成不同的频率。

而 DDFS 只需要更改一个寄存器的值就可以改变输出的频率。

这使得 DDFS 可以快速地切换到所需的频率。

精度DDFS 提供比传统频率合成器更高的频率精度。

通过使用高质量的时钟和数字信号处理技术,DDFS 可以实现更准确的频率合成。

这对于许多应用非常重要,特别是在需要极高精度的测量中。

缺点失真DDFS 的一个主要问题是可能造成频率和幅度失真。

失真主要由于 DDS 中非线性项的存在,所以如果 DDS 的输入信号过大或一些不必要的转换发生,则可能会引起失真。

算法复杂性DDFS 的另一个缺点是算法的复杂性。

DDS需要执行许多乘法,幅度控制和相位控制等方面的处理。

算法处理需要大量的计算资源和存储器,并且在高频率合成模式下需要很高的速度。

噪声DDFS 可能会产生高质量的频率,但其输出信号中可能会存在一些噪声。

这是因为数字钳位器是离散的,在连续函数之间插入折线。

这种折线可能会导致噪声。

结论总体而言,DDFS 是非常有用的高精度频率合成技术。

它提供比传统模拟技术更高的稳定性、精度和灵活性。

然而,如此高度的精细度和稳定性需要更多的计算资源和存储器,并且需要处理单元更加复杂。

此外,当噪声存在时,可能需要额外的滤波和缓冲来获得可接受的输出信号质量。

传统的频率合成器与 DDFS 之间相互竞争,这取决于应用程序和准确度要求。

直接数字频率合成器原理

直接数字频率合成器原理直接数字频率合成器(Direct Digital Frequency Synthesizer,简称DDFS)是一种用于产生高精度、稳定的频率信号的电子设备。

它通过数字电路实现频率的直接合成,可以产生任意频率的信号,并且具有快速调谐、高精度以及低相位噪声等优点。

本文将介绍DDFS的工作原理及其在实际应用中的重要性。

一、工作原理DDFS的核心组成部分是相位累加器(Phase Accumulator)、频率控制字(Frequency Control Word)和查表器(Look-up Table)。

相位累加器通过不断累加频率控制字的值,从而产生一个随时间线性增加的相位值。

查表器中存储了正弦波的采样值,通过查表器可以根据相位值得到对应的正弦波样本。

最后,通过数模转换器将数字信号转换为模拟信号输出。

具体来说,DDFS的工作原理如下:1. 频率控制字:频率控制字是一个二进制数,用于控制相位累加器的累加速度。

频率控制字的大小决定了相位累加器每个时钟周期累加的值,从而决定了输出信号的频率。

2. 相位累加器:相位累加器是一个寄存器,用于存储当前的相位值。

相位累加器的值会在每个时钟周期根据频率控制字的大小进行累加。

相位累加器的位数决定了相位的分辨率,位数越多,相位分辨率越高,输出信号的频率分辨率也越高。

3. 查表器:查表器中存储了一个周期内的正弦波样本值(或余弦波样本值),通过查表器可以根据相位累加器的值得到对应的正弦波样本值。

4. 数模转换器:数模转换器将数字信号转换为模拟信号输出。

通常使用的是高速数模转换器,能够将数字信号以高速率转换为模拟信号输出。

二、应用领域DDFS在许多领域中都有广泛的应用,其中包括通信、雷达、测量、音频处理等。

1. 通信领域:在通信系统中,DDFS被广泛应用于频率合成器、频率调制器和频率解调器等模块中。

通过DDFS可以快速、精确地合成所需的信号频率,实现高速数据传输和频谱分析等功能。

DDS 直接数字频率合成器 实验报告

直接数字频率合成器(DDS)实验报告课程名称电类综合实验实验名称直接数字频率合成器设计实验日期2015.6.1—2013.6.4学生专业测试计量技术及仪器学生学号114101002268学生姓名陈静实验室名称基础实验楼237教师姓名花汉兵成绩摘要直接数字频率合成器(Direct Digital Frequency Synthesizer 简称DDFS 或DDS)是一种基于全数字技术,从相位概念出发直接合成所需波形的一种频率合成技术。

本篇报告主要介绍设计完成直接数字频率合成器DDS的过程。

其输出频率及相位均可控制,且能输出正弦波、余弦波、方波、锯齿波等五种波形,经过转换后在示波器上显示。

经控制能够实现保持、清零功能。

除此之外,还能同时显示出频率控制字、相位控制字和输出频率的值。

实验要求分析整个电路的工作原理,并分别说明了各子模块的设计原理,依据各模块之间的逻辑关系,将各电路整合到一块,形成一个总体电路。

本实验在Quartus Ⅱ环境下进行设计,并下载到SmartSOPC实验系统中进行硬件测试。

最终对实验结果进行分析并总结出在实验过程中出现的问题以及提出解决方案。

关键词:Quartus Ⅱ直接数字频率合成器波形频率相位调节AbstractThe Direct Digital Frequency Synthesizer is a technology based on fully digital technique, a frequency combination technique syntheses a required waveform from concept of phase. This report introduces the design to the completion of the process of direct digital frequency synthesizer DDS. The output frequency and phase can be controlled, and can output sine, cosine, triangle wave, square wave, sawtooth wave, which are displayed on the oscilloscope after conversation. Can be achieved by the control to maintain clear function. Further can simultaneously display the value of the frequency, the phase control word and the output frequency. The experimental design in the Quartus Ⅱenvironment, the last hardware test download to SmartSOPC experimental system. The final results will be analyzed, the matter will be put forward and the settling plan can be given at last.Key words:Quartus ⅡDirect Digital Frequency Synthesizer waveform Frequency and phase adjustment目录一、设计内容 (4)二、设计原理 (4)2.1 DDS概念 (4)2.2 DDS的组成及工作原理 (4)三、设计要求 (6)3.1 基本要求 (6)3.2 提高要求 (6)四、设计内容 (6)4.1 分频电路 (6)4.2 频率预置与调节电路 (10)4.3 累加器 (12)4.4 波形存储器(ROM) (13)4.5 测频电路 (19)4.6 译码显示电路 (21)4.7 消颤电路 (22)4.8 总电路 (23)五、电路调试仿真与程序下载 (24)六、示波器波形图 (25)七、实验中遇到的问题及解决方法 (25)八、电路改进 (26)九、实验感想 (28)十、参考文献 (28)一、设计内容设计一个频率及相位均可控制的具有正弦和余弦输出的直接数字频率合成器(Direct Digital Frequency Synthesizer 简称DDFS 或DDS)。

DDS(DirectDigitalSynthesizer)直接数字式频率合成器

DDS(DirectDigitalSynthesizer)直接数字式频率合成器1. 什么叫DDS直接数字式频率器DDS(Direct Digital Synthesizer),实际上是⼀种分频器:通过编程频率控制字来分频系统(SYSM CLOCK)以产⽣所需要的频率。

DDS 有两个突出的特点,⼀⽅⾯,DDS⼯作在数字域,⼀旦更新频率控制字,输出的频率就相应改变,其跳频速率⾼;另⼀⽅⾯,由于频率控制字的宽度宽(48bit 或者更⾼),频率分辨率⾼。

2. DDS⼯作原理图1 是DDS 的内部结构图,它主要分成3 部分:相位累加器,相位幅度转换,()。

图 1,DDS的结构(1)相位累加器⼀个正弦波,虽然它的幅度不是线性的,但是它的相位却是线性增加的。

DDS 正是利⽤了这⼀特点来产⽣正弦信号。

如图 2,根据DDS 的频率控制字的位数N,把360° 平均分成了2的N次等份。

图2,相位累加器原理假设系统时钟为Fc,输出频率为Fout。

每次转动⼀个⾓度360°/2N,则可以产⽣⼀个频率为Fc/2N的正弦波的相位递增量。

那么只要选择恰当的频率控制字M,使得 Fout / Fc= M / 2N,就可以得到所需要的输出频率Fout,Fout = Fc*M / 2N。

(2)相位幅度转换通过相位累加器,我们已经得到了合成Fout 频率所对应的相位信息,然后相位幅度转换器把0°~360°的相位转换成相应相位的幅度值。

⽐如当DDS 选择为2V p-p 的输出时,45°对应的幅度值为0.707V,这个数值以⼆进制的形式被送⼊DAC。

这个相位到幅度的转换是通过查表完成的。

(3)DAC输出代表幅度的⼆进制数字信号被送⼊DAC 中,并转换成为模拟信号输出。

注意DAC 的位数并不影响输出频率的分辨率。

输出频率的分辨率是由频率控制字的位数决定的。

直接数字式频率合成技术(DDS)是⼀种先进的全数字频率合成技术,它具有多种数字式调制能⼒(如相位调制、频率调制、幅度调制以及I/Q正交调制等),在通信、导航、雷达、电⼦战等领域获得了⼴泛的应⽤。

名词解释DSP,FPGA,CPLD,RAM,PLL,SOC,SOPC,DDS

名词解释1.DSPDSP数字信号处理(Digital Signal Processing,简称DSP)是一门涉及许多学科而又广泛应用于许多领域的新兴学科。

DSP(digital signal processor)是一种独特的微处理器,是以数字信号来处理大量信息的器件。

其工作原理是接收模拟信号,转换为0或1的数字信号,再对数字信号进行修改、删除、强化,并在其他系统芯片中把数字数据解译回模拟数据或实际环境格式。

它不仅具有可编程性,而且其实时运行速度可达每秒数以千万条复杂指令程序,远远超过通用微处理器,是数字化电子世界中日益重要的电脑芯片。

它的强大数据处理能力和高运行速度,是最值得称道的两大特色。

2.FPGA是英文Field-Programmable Gate Array的缩写,即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。

它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

目前以硬件描述语言(Verilog 或VHDL)所完成的电路设计,可以经过简单的综合与布局,快速的烧录至FPGA 上进行测试,是现代IC 设计验证的技术主流。

这些可编辑元件可以被用来实现一些基本的逻辑门电路(比如AND、OR、XOR、NOT)或者更复杂一些的组合功能比如解码器或数学方程式。

在大多数的FPGA里面,这些可编辑的元件里也包含记忆元件例如触发器(Flip-flop)或者其他更加完整的记忆块。

3.CPLDCPLD(Complex Programmable Logic Device)复杂可编程逻辑器件,是从PAL和GAL器件发展出来的器件,相对而言规模大,结构复杂,属于大规模集成电路范围。

是一种用户根据各自需要而自行构造逻辑功能的数字集成电路。

其基本设计方法是借助集成开发软件平台,用原理图、硬件描述语言等方法,生成相应的目标文件,通过下载电缆(“在系统”编程)将代码传送到目标芯片中,实现设计的数字系统。

外文翻译数字频率合成器

附录2:外文原文,译文Modulating Direct Digital Synthesizer In the pursuit of more complex phase continuous modulation techniques, the control of the output waveform becomes increasingly more difficult with analog circuitry. In these designs, using a non-linear digital design eliminates the need for circuit board adjustments over yield and temperature. A digital design that meets these goals is a Direct Digital Synthesizer DDS. A DDS system simply takes a constant reference clock input and divides it down a to a specified output frequency digitally quantized or sampled at the reference clock frequency. This form of frequency control makes DDS systems ideal for systems that require precise frequency sweeps such as radar chirps or fast frequency hoppers. With control of the frequency output derived from the digital input word, DDS systems can be used as a PLL allowing precise frequency changes phase continuously. As will be shown, DDS systems can also be designed to control the phase of the output carrier using a digital phase word input. With digital control over the carrier phase, a high spectral density phase modulated carrier can easily be generated.This article is intended to give the reader a basic understanding of a DDS design, and an understanding of the spurious output response. This article will also present a sample design running at 45MHz in a high speed field programmable gate array from QuickLogic.A basic DDS system consists of a numerically controlled oscillator (NCO) used to generate the output carrier wave, and a digital to analog converter (DAC) used to take the digital sinusoidal word from the NCO and generate a sampled analog carrier. Since the DAC output is sampled at the reference clock frequency, a wave form smoothing low pass filter is typically used to eliminate alias components. Figure 1 is a basic block diagram of a typical DDS system generation of the output carrier from the reference sample clock input is performed by the NCO. The basic components of the NCO are a phase accumulator and a sinusoidal ROM lookup table. An optional phase modulator can also be include in the NCO design. This phase modulator will add phase offset to the output of the phase accumulator just before the ROM lookup table. This will enhance the DDS system design by adding the capabilities to phase modulate the carrier output of the NCO. Figure 2 is a detailed block diagram of a typical NCO design showing the optional phase modulator.FIGURE 1: Typical DDS System.FIGURE 2: Typical NCO Design.To better understand the functions of the NCO design, first consider the basic NCO design which includes only a phase accumulator and a sinusoidal ROM lookup table. The function of these two blocks of the NCO design are best understood when compared to the graphical representation of Euler’s formula ej wt = cos( wt) + jsin( wt). T hegraphical representation of Euler’s formula, as shown in Figure 3, is a unit vector rotating around the center axis of the real and imaginary plane at a velocity of wrad/s. Plotting the imaginary component versus time projects a sine wave while plotting the real component versus time projects a cosine wave. The phase accumulator of the NCO is analogous, or could be considered, the generator of the angular velocity component wrad/s. The phase accumulator is loaded, synchronous to the reference sample clock, with an N bit frequency word.This frequency word is continuously accumulated with the last sampled phase value by an N bit adder. The output of the adder is sampled at the reference sample clock by an N bit register. When the accumulator reaches the N bit maximum value, the accumulator rolls over and continues. Plotting the sampled accumulator values versus time produces a saw tooth wave form as shown below in Figure 3. FIGURE 3 Euler’s Equation Represented GraphicallyThe sampled output of the phase accumulator is then used to address a ROM lookup table of sinusoidal magnitude values. This conversion of the sampled phase to a sinusoidal magnitude is analogous to the projection of the real or imaginary component in time. Since the number of bits used by the phase accumulator determines the granularity of the frequency adjustment steps, a typical phase accumulator size is 24 to 32 bits. Since the size of the sinusoidal ROMtable is directly proportional to the addressing range, not all 24 or 32 bits of the phase accumulator are used to address the ROM sinusoidal table. Only the upper Y bits of the phase accumulator are used to address the sinusoidal ROM table, where Y < N bits and Y is typically but not necessarily equal to D, and D is the number of output magnitude bits from the sinusoidal ROM table.Since an NCO outputs a carrier based on a digital representation of the phase and magnitude of the sinusoidal wave form, designers have complete control over frequency, phase, and even amplitude of the output carrier. By adding a phase port and a phase adder to the basic NCO design, the output carrier of the NCO can be M array phase modulated where M equals the number of phase port bits and where M is less than or equal to the Y number of bits used to address the sinusoidal ROM table. For system designs that require amplitude modulation such as QAM, a magnitude port can be added to adjust the sinusoidal ROM table output. Note that this port is not shown in Figure 2 and that this feature is not demonstrated in the sample QuickLogic FPGA design. Finally, frequency modulation is a given with the basic NCO design. The frequency port can directly adjust the carrier output frequency. Since frequency words are loaded into the DDS synchronous to the sample clock, frequency changes are phase continuous.Although DDS systems give the designer complete control ofcomplex modulation synthesis, the representation of sinusoidal phase and magnitude in a non-linear digital format introduces new design complexities. In sampling any continuous-time signal, one must consider the sampling theory and quantization error.To understand the effects of the sampling theory on a DDS system, it is best to look at the DDS synthesis processes in both the time and frequency domain. As stated above, the NCO generates a sinusoidal wave form by accumulating the phase at a specified rate and then uses the phase value to address a ROM table of sinusoidal amplitude values. Thus, the NCO is essentially taking a sinusoidal wave form and sampling it with the rising or falling edge of the NCO input reference sampling clock. Figure 4 shows the time and frequency domain of the NCO processing. Note that this representation does not assume quantization.Based on the loaded frequency word, the NCO produces a set of amplitude output values at a set period. The frequency domain representation of this sinusoid is an impulse function at the specified frequency. The NCO, however, outputs discrete digital samples of this sinusoid at the NCO reference clock rate. In the time domain, the NCO output is a function of the sampling clock edge strobes multiplied by the sinusoid wave form producing a train of impulses at the sinusoid amplitude. In the frequency domain, the sampling strobes of the reference clock produce a train of impulses at frequencies of K times theNCO clock frequency where K = ... - 1, 0, 1, 2 .... Since the sampling clock was multiplied by the sinusoid in the time domain, the frequency domain components of the sinusoid and the sampling clock need to be convolved to produce the frequency domain representation of the NCO output.The frequency domain results are the impulse function at the fundamental frequency of the sinusoid and the alias impulse functions occurring at K times the NCO clock frequency plus or minus the fundamental frequency. The fundamental and alias component occur at: K*Fclk - FoutK*Fclk + FoutWhere K = ... -1, 0 , 1, 2 ..... and K = 0 is the NCO sinusoid fundamental frequencyFout is the specified NCO sinusoid output frequencyFclk is the NCO reference clock frequencyFIGURE 4 NCO Output Representation Time and Frequency Domain The DAC of the DDS system takes the NCO output values and translates these values into analog voltages. Figure 4 shows the time and frequency domain representations of the DAC processing starting with the NCO output. The DAC output is a sample and hold circuit that takes the NCO digital amplitude words and converts the value into an analog voltage and holds the value for one sample clock period. The timedomain plot of the DAC processing is the convolution of the NCO sampled output values with a pulse of one sample clock period. The frequency domain plot of the sampling pulse is a sin(x)/x function with the first null at the sample clock frequency. Since the time domain was convolved, the frequency domain is multiplied. This multiplication dampens the NCO output with the sin(x)/x envelope. This attenuation at the DAC output can be calculated as follows and a sample output spectrum is shown in Figure 5:Atten(F) = 20log[(sin(pF/Fclk)/pF/Fclk)] Where F is the output frequency Fclk is the sample clock frequencyFIGURE 5: DAC Output Representation in Time and Frequency Domain Aside from the sampling theory, the quantization of the real values into digital form must also be considered in the performance analysis of a DDS system. The spurious response of a DDS system is primarily dictated by two quantization parameters. These parameters are the phase quantization by the phase accumulator and the magnitude quantization by the ROM sinusoidal table and the DAC.As mentioned above, only the upper Y bits of the phase accumulator are used to address the ROM lookup table. It should be noted, however, that using only the upper Y bits of the phase accumulator introduces a phase truncation. When a frequency word containing a non-zero value in the lower (N-Y-1:0) bits is loaded into the DDS system, the lowernon-zero bits will accumulate to the upper Y bits and cause a phase truncation. The frequency at which the phase truncation occurs can be calculated by the following:Ftrunc = FW(N-Y- 1:0)/2N-Y* Fclk.A phase truncation will periodically (at the Ftrunc rate) phase modulate the output carrier forward 2p/28 to compensate for frequency word granularity greater than 2Y. The phase jump caused by the accumulation of phase truncated bits produces spurs around the fundamental.These spurs are located plus and minus the truncation frequency from the fundamental frequency and the magnitude of the spurs will be - 20log(2Y)dBc. A sample output of a phase truncation spur is shown in Figure 5.In a typical NCO design, the ROM sinusoidal table will hold a ¼ sine wave (0 , p/2) of magnitude values. The ROM table is generated by taking all possible phase value addresses and map to a real magnitude sine value rounded to the nearest D bits. Thus, the maximum error output is ±- ½ LSB giving a worst case spur of -20log(2D)dBc.Like the NCO ROM table, a DAC quantizes the digital magnitude values. A DAC, however, outputs an analog voltage corresponding to the digital input value. When designing the NCO sinusoidal ROM table, one should take some empirical data on the DAC linearity to betterunderstand the interaction between the ROM table and the DAC. The quantization for a DAC is specified against an ideal linear plot of digital input versus analog output. Two linearity parameters, differential and integral linearity, are used to specify a DAC’s p erformance.Differential linearity is the output step size from bit to bit. A DAC must guarantee a differential linearity of a maximum 1 LSB. When an input code is increased, the DAC output must increase. If the DAC voltage does not increase versus an increase digital input value, the DAC is said to be missing codes. Thus, a 10 bit DAC that has a differential linearity of greater that 1 LSB is only accurate to 9 or less bits. The number of accurate output bits will specify the DDS spurious performance as -20log(2dl) where dl is the number differential linear bits..Integral linearity is a measure of the DAC’s overall linear performance versus an ideal linear straight line. The straight line plot can be either a “best straight line” where DC offsets are pos sible at both the min and max outputs of the DAC, or the straight line can cross the end points of the min and max output values. A DAC will tend to have a characteristic curve that is traversed over the output range. Depending on the shape and symmetry (symmetry about the half way point of the DAC output) of this curve, output harmonics of the DDS fundamental output frequency will be produced. As these harmonics approach andcross the Nyquist frequency of Fclk/2, the harmonics become under sampled and reflect back into the band of interest, 0 to Fclk/2. This problem is best illustrated by setting the NCO output to Fclk/4 plus a slight offset. The third harmonic will fall minus 3 folds the small offset from the fundamental and the second harmonic will cross the Nyquist frequency by 2 folds the small offset leaving a reflected image back in the band of interest A sample plot of this frequency setup is shown in Figure 5.Other DAC characteristic that will produce harmonic distortion is any disruption of the symmetry of the output wave form such as a different rise and fall time. These characteristics can typically be corrected by board components external to the DAC such as an RF transformer, board layout issues, attenuation pads etc.Given the complexities of the DDS system, engineers should consider implementing the design using separate devices for the numerically controlled oscillator, the digital to analog converter, and the low pass filter. This approach allows for signal observation at many points in the system, yet is compact enough to be practical as an end-solution. Alternatively, the discrete implementation can serve as a prototyping vehicle for a single-chip mixed signal ASIC.The author developed a version of the design using a Harris HI5721 evaluation board for the DAC. The NCO at the heart of the DDS design,and a random generator to test signal modulation, was implemented into about 65% of a QuickLogic field programmable gate array (FPGA). This FPGA, a QL16x24B 4000-gate device, was chosen for its high performance, ease-of-use, and powerful development tools.The NCO design included following:Developed in Verilog with the 8 bit CLA adder schematiccaptured and net listed to Verilog32 bit frequency word input32 phase accumulator pipelined over 8 bits8 bit phase moudulation word input8 bit sine ROM look-up tableThe design was described mostly in Verilog, with an 8 bit carry look ahead adder modified from QuickLogic’s macro library netlisted to Verilog. The whole design cycle was less than four days (two days to describe the design and a day and a half to prototype the hardware). Everything worked perfectly the first time, with the design running at an impressive 45MHz as predicted by the software simulation tools.Plots used in the article to illustrate DDS performance parameters were provided from the test configuration.Figure 6 below shows the external IO interface to the NCO design .The function of each signal is described in the following table.Signal Function TableFigure 6: The External IO InterfaceTop LevelThe top level of the NCO design instantiates the functional blocks of the NCO design and the PN generator block.PN GeneratorThis module is not part of the NCO design but is used to produce a sample random data pattern to modulate the carrier output. This module uses the PNCLK input to clock two Gold code 5 bit PN generators. The outputs of the PN generators are IDATA and QDATA outputs.The lower level block of this NCO design consist of a synchronous frequency word input register, a synchronous phase word input register, a 32 bit pipe lined phase accumulator, an 8 bit phase adder, and a sin lockup table. A detailed description of each of the NCO blocks and thePN generator are provided in the following sections.Load Frequency WordThe load frequency word block is a synchronizing loading circuit. The FREQWORD[31:0] input drives a the data input to the 32 bit fwreg register that is sampled on the rising edge of the FWWRN write strobe. The FWWRN strobe also drives the data input to a metastable flip flop fwwrnm that is used in conjunction with a synchronous register fwwrns to produce a FWWRN rising edge strobe. This rising edge strobe loadp1 is then piped for an additional 3 clock cycles producing the load strobes loadp2, loadp3, and loadp4. The load strobes are used to signal when to update the synchronous pipe line 8 bit registers pipefw1, pipefw2, pipefw3, and pipefw4 to the sampled frequency word content. The pipe line registers are concatenated to produce the 32 bit synchronous frequency word output SYNCFREQ[31:0] that is staggered to compensate for the 32 bit pipe lined phase adder.Phase Word AccumulatorThe phase accumulator block is a 32 bit accumulator that is pipe lined in 8 bit sections. This module instanciates a schematic captured carry lock ahead CLA adder that has a carry in and carry out port. The synchronous frequency word, staggered to match the pipe lined accumulator, is loaded into the B input of the CLA adders. The sum output of the CLA adders are registered in the pipe registered with theoutput tied back to the A input of the CLA adders. The carry output of the CLA adders is registered in the pipec registers with the output tied to the next most significant CLA adder carry input. The most significant sum output register pipe4 is assigned to the PHASE output port giving a phase value quantized to 8 bits. A digital sine and cosine value is also calculated from the pipe4 register and brought out of the chip as SIN and COS.Load Phase WordThe load phase word block is a synchronizing loading circuit. The PHASEWORD[7:0] input drives the data input to the 32 bit pwreg register that is sampled on the rising edge of the PWWRN write strobe. The PWWRN strobe also drives the data input to a metastable flip flop pwwrnm that is used in conjunction with a synchronous register pwwrns to produce a FWWRN rising edge strobe. This rising edge strobe load is used to signal when to update the synchronous phase word register phswd. The phswd register is assigned to the synchronous phase word output SYNCPHSWD[7:0].Phase ModulatorThe phase modulator block is used to phase offset the phase accumulator 8 bit quantized output with the synchronous phase word from the load phase word block. This module instantiates a CLA adder with the A input tied to the synchronous phase output and the B inputtied to the phase accumulator output. The sum output of the adder is registered in the mphsreg register and assigned to the MODPHASE output port. A modulated version of the sine and cosine values are calculated and brought out of the chip as MSIN and MCOS.Sine LockupThis module takes the modulated phase value form the phase modulator block and translated the quantized 8 bit value into a sine wave form amplitude value quantized to 8 bits. The translation from phase to amplitude is performed by a sine ROM table that in instantiated in this module. The ROM table is reduced to a ¼ of the symmetrical sine wave form and the MSB of the sine wave form is equivalent to the modulated phase module performs the calculations to reconstruct a complete period of the sine wave form f rom the ¼ representation of the ROM table and the MSB of the modulated phase input. To better understand the processing of this module, consider the following. The modulated phase value is a 0 to 2p value quantized to 8 bits 2p/28. The quantized value for p/2, p, 3p/2, and 2p are 0x3F, 0x7F, 0xBF, and 0xFF. The amplitude values for 0 to p/2 is stored in the ROM table. The amplitude values for p/2 to p are the ROM table output in the reverse order. The amplitude values for p to 3p/2 are the same output as the amplitude value from 0 to p/2 with the output from the ROM table inverted. Finally the amplitude value for 3p/2 to 2p are the same as for pto 3p/2 with the ROM table accessed in reverse.This module manages the address values to the ROM table and the amplitude outputs to form the complete period of the sine wave form. The first process of generating the sine wave function is the addressing of the ROM table such that phase angles p/2 to p and 3p/2 to 2p are addressed in the reverse order. Reverse addressing is accomplished by simply inverting the ROM table address input vector. The phase modulated address input is inverted when the MODPHASE[6] is one and is then registered in the phaseadd register. The phase address is used to address the ROM sine table with the output registered in the qwavesin_ff register. To construct the negative amplitude values of the sine wave form, the MSB of the modulate phase word input is registered twice in modphase_msb1_ff and modphase_msb2_ff, compensating for the two cycle latency of the phaseadd and qwavesin_ff registers. The delayed MSB bit is used to invert the ROM table output when one. The altered ROM table output and the invert of the delayed modulated phase word MSB are finally registered in by the dac_ff register and then assigned to the DACOUT output port.Sine ROM TableThis module is the sine wave form ROM table. This table converts the phase word input to a sine amplitude output. To conserve area, only ¼ of the symmetrical sine wave form is stored in the ROM. The sine valuesstored in this table are the 0 to p/2 unsigned values quantized to 8 bits. Thus, the ROM table requires a 6 bit phase address input and outputs a 7 bit amplitude output. The sinlup module processes the phase and amplitude values to produce a complete sine period.Dan Morelli has over 9 years of design and management experience. His areas of expertise include spread spectrum communications (involving GPS, TDRSS, and , PC chip set and system architecture, cell library development (for ECL devices) and ASIC development. He has been published and has multiple patents awarded and pending. Dan currently works for Accelent Systems Inc., an electronic design consulting company, where he is a founder and the VP of Engineering.数字频率合成器在探讨许多复杂的相位持续的调制技术中,对模拟电路中输出波形的操纵已经愈来愈困难。

NCO和DDS技术

波形和其波形序列指令都存在仪器所带的RAM中。

任意波形发生器

波形生成序列通常从 TTL硬件触发器开始。各种波形由许多 单个的样本构成,而生成采样率由仪器的采样时钟确定。从

内部采样时钟时基(100 MHz VCXO)中导出采样时钟有几种

不同模式,包括DDS定时Div/N时钟,以及几种提供不同外部 时钟的模式。另外,对于用于仪器的锁相环的频率基准,也

真思考如何为以后的发展开好头。

Thank you

函数发生器

函数发生器产生固定波形,如正弦波、方波(矩形波)阶梯波 或三角波(锯齿波),频率可调节。函数发生器无需来自计 算机或大容量存储缓冲器的连续输入,因为设备本身能够产 生这些波形。 函数发生器可以基于模拟技术,也可以基于数字技术。模拟 函数发生器利用模拟硬件来产生简单的函数,并在需要指定 频率的静态正弦波或方波时经常使用。而数字函数发生器采 用直接数字综合( DDS),DAC,数字信号处理,以及一个单 周期存储缓冲器来产生信号。 DDS技术依赖数字控制的方法, 利用单基准时钟频率来实现一个模拟频率源。DDS能够实现 高精度和高分辨率,高温度稳定度,高宽带,以及随机的和 相位连续的频率切换。 许多信号源通过对一个内部时基进行整数分频来产生时钟信 号,这被称为除N方法。但是,用除N方法来产生时钟,只能 产生有限的时钟频率。AWG,甚至几个时钟频率产生器,可 以采用DDS技术来产生具有非常精细的更新频率时钟信号, 而这是除NCO方法无法实现的。

CORDIC算法(参见论文-苏凯雄.基于FPGA的数控振荡器的设计与实现)

Walther JS于1971年提出了统一的CORDIC形式。 假定初始向量V1(x1 ,y1)旋转角度θ后得到向量V2(x2,y2),即:

外文翻译-关于直接数字频率合成器

All About Direct Digital SynthesisBy Eva Murphy [eva.murphy@]Colm Slattery [colm.slattery@]What is Direct Digital Synthesis?Direct digital synthesis (DDS) is a method of producing an analog waveform—usually a sine wave—by generating a time-varying signal in digital form and then performing a digital-to-analog conversion. Because operations within a DDS device are primarily digital, it can offer fast switching between output frequencies, fine frequency resolution, and operation over a broad spectrum of frequencies. With advances in design and process technology, today’s DDS devices are very compact and draw little power.Why would one use a direct digital synthesizer (DDS)? Aren’t there other methods for easily generating frequencies?The ability to accurately produce and control waveforms of various frequencies and profiles has become a key requirement common to a number of industries. Whether providing agile sources of low-phase-noise variable-frequencies with good spurious performance for communications, or simply generating a frequency stimulus in industrial or biomedical test equipment applications, convenience, compactness, and low cost are important design considerations.Many possibilities for frequency generation are open to a designer, ranging from phase-locked-loop (PLL)-based techniques for very high-frequency synthesis, to dynamic programming of digital-to-analog converter (DAC) outputs to generate arbitrary waveforms at lower frequencies. But the DDS technique is rapidly gaining acceptance for solving frequency- (or waveform) generation requirements in both communications and industrial applications because single-chip IC devices can- 1 -generate programmable analog output waveforms simply and with high resolution and accuracy.Furthermore, the continual improvements in both process technolog y and design have resulted in cost and power consumption levels that were previously unthinkably low. For example, the AD9833, a DDS-based programmable waveform generator (Figure 1), operating at 5.5 V with a 25-MHz clock, consumes a maximum power of 30 milliwatts.Figure 1. The AD9833-a one-chip waveform generator.What are the main benefits of using a DDS?DDS devices like the AD9833 are programmed through a high speed serial peripheral-interface (SPI), and need only an external clock to generate simple sine waves. DDS devices are now available that can generate frequencies from less than 1 Hz up to 400 MHz (based on a 1-GHz clock). The benefits of their low power, low cost, and single small package, combined with their inherent excellent performance and the ability to digitally program (and re-program) the output waveform, make DDS devices an extremely attractive solution—preferable to less-flexible solutions comprising aggregations of discrete elements.What kind of outputs can I generate with a typical DDS device?- 2 -- 3 -DDS devices are not limited to purelysinusoidal outputs. Figure 2 shows thesquare-, triangular-, and sinusoidal outputsavailable from an AD9833.How does a DDS device create a sinewave?Here’s a breakdown of the internalcircuitry of a DDS device: its maincomponents are a phase accumulator, ameans of phase-to-amplitude conversion(often a sine look-up table), and a DAC.These blocks are represented in Figure 3.A DDS produces a sine wave at a givenfrequency. The frequency depends on two variables, the reference-clock frequency and the binar y number programmed into the frequency register (tuning word).The binary number in thefrequency register providesthe main input to the phaseaccumulator. If a sinelook-up table is used, the phase accumulator computesa phase (angle) address for the look-up table, which outputs the digital value of amplitude —corresponding to the sine of that phase angle —to the DAC. The DAC, in turn, converts that number to a corresponding value of analog voltage or current. To generate a fixed-frequency sine wave, a constant value (the phase increment —which is determined by the binary number) is added to the phase accumulator with eachFigure 2. Square-, triangular-, and sinusoidal outputs from a DDS.Figure 3. Components of a direct digital synthesizer.clock cycle. If the phase increment is large, the phase accumulator will step quicklythrough the sine look-up table and thus generate a high frequency sine wave. If thephase increment is small, the phase accumulator will take many more steps,accordingly generating a slower waveform.What do you mean by a complete DDS?The integration of a D/A converter and a DDS onto a single chip is commonlyknown as a complete DDS solution, a property common to all DDS devices fromADI.Let’s talk some more about the phase accumulator. How does it work?Continuous-time sinusoidal signals have a repetitive angular phase range of 0 to2 .The digital implementation is no different. The counter’s carry function allowsthe phase accumulator to act as a phase wheel in the DDS implementation.To understand this basic function, visualize the sine-wave oscillation as a vectorrotating around a phase circle (see Figure 4).Each designated point on the phase wheelcorresponds to the equivalent point on a cycleof a sine wave. As the vector rotates aroundthe wheel, visualize that the sine of the anglegenerates a corresponding output sine wave.One revolution of the vector around the phasewheel, at a constant speed, results in onecomplete cycle of the output sine wave. TheFigure 4. Digital phase wheel. phase accumulator provides the equallyspaced angular values accompanying the vector’s linear rotation around the phasewheel. The contents of the phase accumulator correspond to the points on the cycle ofthe output sine wave.- 4 -- 5 -The phase accumulator is actually a modulo- M counter that increments its stored number each time it receives a clock pulse. The magnitude of the increment is determined by the binary-coded input word (M). This word forms the phase step size between reference-clock updates; it effectively sets how many points to skip around the phase wheel. The larger the jump size, the faster the phase accumulator overflows and completes its equivalent of a sine-wave cycle. The number of discrete phase points contained in the wheel is determined by the resolution of the phase accumulator (n), which determines the tuning resolution of the DDS. For an n = 28-bit phase accumulator, an M value of 0000...0001 would result in the phase accumulator overflowing after 28 reference-clock cycles (increments). If the M value is changed to 0111...1111, the phase accumulator will overflow after only 2 reference-clock cycles (the minimum required by Nyquist). This relationship is found in the basic tuning equation for DDS architecture:n C out f M f 2⨯= where:fOUT = output frequency of the DDSM = binary tuning wordfC = internal reference clock frequency (system clock)n = length of the phase accumulator, in bitsChanges to the value of M result in immediate and phase-continuous changes in the output frequency. No loop settling time is incurred as in the case of a phase-locked loop.As the output frequency is increased, the number of samples per cycle decreases. Since sampling theory dictates that at least two samples per cycle are required to reconstruct the output waveform, the maximum fundamental output frequency of aDDS is fC/2. However, for practical applications, the output frequency is limited to somewhat less than that, improving the quality of the reconstructed waveform and permitting filtering on the output.When generating a constant frequency, the output of the phase accumulator increases linearly, so the analog waveform it generates is inherently a ramp.Then how is that linear output translated into a sine wave?A phase -to - amplitude lookup table is used to convert the phase-accumulator’s instantaneous output value (28 bits for AD9833)—with unneeded less-significant bits eliminated by truncation—into the sine-wave amplitude information that is presented to the (10 -bit) D/A converter.The DDS architecture exploitsthe symmetrical nature of a sinewave and utilizes mapping logicto synthesize a complete sinewave from one-quarter-cycle ofFigure 5. Signal flow through the DDS architecture. data from the phase accumulator.The phase-to- amplitude lookup table generates the remaining data by reading forward then back through the lookup table. This is shown pictorially in Figure 5. What are popular uses for DDS?Applications currently using DDS-based waveform generation fall into two principal categories: Designers of communications systems requiring agile (i.e., immediately responding) frequency sources with excellent phase noise and low spurious performance often choose DDS for its combination of spectral performance and frequency-tuning resolution. Such applications include using a DDS for modulation, as a reference for a PLL to enhance overall frequency tunability, as a local oscillator (LO), or even for direct RF transmission.- 6 -Alternatively, many industrial and biomedical applications use a DDS as a programmable waveform generator. Because a DDS is digitally programmable, the phase and frequency of a waveform can be easily adjusted without the need to change the external components that would normally need to be changed when using traditional analog-programmed waveform generators. DDS permits simple adjustments of frequency in real time to locate resonant frequencies or compensate for temperature drift. Suchapplications include using a DDS in adjustable frequency sources to measure impedance (for example in an impedance-based sensor), to generate pulse-wave modulated signals for micro-actuation, or to examine attenuation in LANs or telephone cables.What do you consider to be the key advantages of DDS to designers of real-world equipment and systems?Today’s cost- competitive, high - performance, functionally integrated DDS ICs are becoming common in both communication systems and sensor applications. The advantages that make them attractive to design engineers include:• digitally controlled micro-hertz frequency-tuning and sub-degree phase-tuning capability,• extremely fast hopping speed in tuning output frequency (or phase); phase - continuous frequency hops with no overshoot/undershoot or analog-related loop settling-time anomalies,• the digital architecture of DDS eliminates the need for the manual tuning and tweaking related to component aging and temperature drift in analog synthesizer solutions, and• the digital control interface of the DDS architecture facilitates an environment where systems can be remotely controlled and optimized with high resolution under processor control.- 7 -What are the key performance specs of a DDS based system?Phase noise, jitter, and spurious-free dynamic range (SFDR).Phase noise is a measure (dBc/Hz) of the short-term frequency instability of the oscillator. It is measured as the single-sideband noise resulting from changes in frequency (in decibels below the amplitude at the operating frequency of the oscillator using a 1-Hz bandwidth) at two or more frequency displacements from the operating frequency of the oscillator. This measurement has particular application to performance in the analog communications industry.Do DDS devices have good phase noise?Noise in a sampled system depends on many factors. Reference-clock jitter can be seen as phase noise on the fundamental signal in a DDS system; and phase truncation may introduce an error level into the system, depending on the code word chosen. For a ratio that can be exactly expressed by a truncated binary-coded word, there is no truncation error. For ratios requiring more bits than are available, the resulting phase noise truncation error results in spurs in a spectral plot. Their magnitudes and distribution depends on the code word chosen. The DAC also contributes to noise in the system.DAC quantization or linearity errorswill result in both noise andharmonics. Figure 9 shows a phasenoise plot for a typical DDSdevice—in this case an AD9834.How can I evaluate your DDSdevices?All DDS devices have an evaluation board available for Figure 9. Typical output phase noise plotfor the AD9834. Output frequency is 2 MHz and M clock is 50 MHz.- 8 -purchase. They come with dedicated software, allowing the user to test/evaluate the part easily within minutes of receiving the board. A technical note accompanying each evaluation board contains schematic information and shows best recommended board-design and layout practice.- 9 -西北工业大学明德学院本科毕业设计论文关于直接数字频率合成器1.什么是直接数字频率合成器?直接数字频率合成器(DDS)是一种通过产生一个以数字形式时变的信号,然后执行由数字至模拟转换的方法。

直接数字频率合成技术(DDS)

DDS直接数字频率合成技术

2, 采用分立IC电路系统实现,一般有CPU, RAM, ROM, D/A, CPLD, 模拟滤波器等组成

3, CPLD,FPGA实现

•用QuartusII采用原理图输入来完成顶层设计。 •相位累加器调用lmp_add_sub加减法器或用HDL实现 •波形存储器(ROM)通过调用lpm_rom元件实现,其LPM_FILE 的值*.mif是一个存放波形幅值的文件。注意,利用波形幅值的奇、 偶对称特性,最多可以节省3/4的资源。 •频率控制字与频率之间的转换可以调用乘除法模块实现 •波形存储器设计主要考虑的问题是其容量的大小,这是非常可观 的。

统输出一个正弦波。

▪输出正弦波周期

T0

Tc 2N M

▪输出正弦波频率

fout

M

fc 2N

DDS直接数字频率合成技术

▪M与输出fout和fC之间的关系

M ( fout 2N ) fc

0 M 2N 1

▪DDS的最小分辨率 通常用频率增量来表示频率合成器的分辨率

fout

M

fc 2N

M=1

f m in

DDS直接数字频率合成技术

直接数字频率合成技术 (DDS)

DDS直接数字频率合成技术

DDS或DDFS 是 Direct Digital Frequency Synthesis 的简称

1971年,由J.Tierney 和C.M.Tader 等人ቤተ መጻሕፍቲ ባይዱ “A Digital Frequency Synthesizer”一文中首次提出了DDS的概念。

12

超宽的相对宽带

超高的捷变速率(可实现跳频)

超细的分辨率

相位的连续性

输出波形灵活

直接数字式频率合成器DDS

/dzdgdq/jsqy/40028.shtml/view/229432.htm?fr=ala0_1/view/38405.htm?fr=ala0_1_1直接数字式频率合成器DDS2010-04-25 18:06直接数字频率合成技术(Direct DigitalFrequencySynthesis,即DDFS,一般简称DDS)是从相位概念出发直接合成所需波形的一种新的频率合成技术。

DDS的工作原理是以数控振荡器的方式,产生频率、相位可控制的正弦波(SineWave)。

电路一般包括基准时钟、频率累加器、相位累加器、幅度/相位转换电路、D/A转换器和低通滤波器(LPF)。

其中,频率累加器对输入信号进行累加运算,产生频率控制数据(Frequency Data或相位步进量Phase Increment)。

相位累加器由N位全加器和N位累加寄存器级联而成,对代表频率的二进制码进行累加运算,是典型的反馈电路,产生累加结果Y。

幅度/相位转换电路实质是一个波形存储器(WaveformMemory),以供查表使用。

读出的数据送入D/A转换器和低通滤波器。

具体工作过程如下:每来一个时钟脉冲Fclk,N位加法器将频率控制数据X与累加寄存器输出的累加相位数据相加,把相加后的结果Y送至累加寄存器的输入端。

累加寄存器一方面将在上一时钟周期作用后所产生的新的相位数据反馈到加法器的输入端,以使加法器在下一时钟的作用下继续与频率控制数据X相加;另一方面,将这个值作为取样地址值送入幅度/相位转换电路(即波形存储器),幅度/相位转换电路根据这个地址值输出相应的波形数据。

最后,经数/模转换(D/AConverter)和低通滤波器(LowPass Filter)将波形数据转换成所需要的模拟波形。

相位累加器在基准时钟的作用下,进行线性相位累加,当相位累加器累加满量时就会产生一次溢出,这样就完成了一个周期,这个周期也就是DDS合成信号的一个频率周期。

基于FPGA的直接数字频率合成器的设计本科设计

基于FPGA的直接数字频率合成器的设计本科设计毕业设计论文基于FPGA的直接数字频率合成器的设计摘要在频率合成领域,常用的频率合成技术有直接模拟合成、模拟锁相环、小数分频锁相环等,直接数字频率合成(Direct Digital Frequency Synthesis ,DDFS,简称DDS)是近年来的新的频率合成技术。

本文介绍了直接数字频率合成器的基本组成及设计原理,给出了基于FPGA的具体设计方案及编程实现方法。

仿真结果表明,该设计简单合理,使用灵活方便,通用性好,可写入各种FPGA 芯片,最高可将频率提高100万倍。

具有良好的性价比。

关键词直接数字频率合成器(DDS) FPGADesign of direct digital frequency synthesizer based on FPGAAbstract In Frequency domain, the common Synthesis technology has Direct simulation, phase lock loop simulation, decimal Frequency and phase lock loop, Direct Digital Frequency Synthesis (as some DDFS, Digital, referred to as spurious bio-synthesis) in recent years is the new Frequency Synthesis technology. The structure and principles of Direct Digital Frequency Synthesizer is introduced. Also a detailed design and the method of program realization based on FPGA are introduced. The result of simulation shows that the design is simple and feasible, convenient and flexible, high universality, writeable various FPGA chip, the highest frequency can be 100 million times. Ratiofor quality to price.Keywords Direct Digital frequency Synthesizer(DDS) FPGA前言在频率合成领域,常用的频率合成技术有直接模拟合成、模拟锁相环、小数分频锁相环等,直接数字频率合成(DDS)是近年来的新的频率合成技术。

直接数字频率合成器

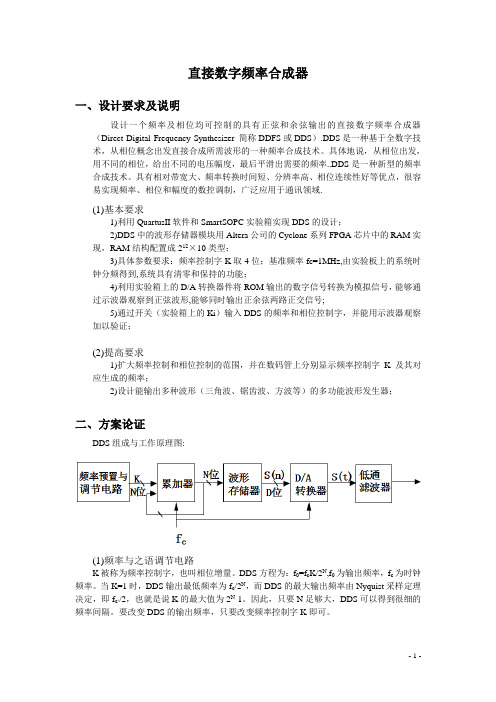

直接数字频率合成器一、设计要求及说明设计一个频率及相位均可控制的具有正弦和余弦输出的直接数字频率合成器(Direct Digital Frequency Synthesizer 简称DDFS或DDS).DDS是一种基于全数字技术,从相位概念出发直接合成所需波形的一种频率合成技术。

具体地说,从相位出发,用不同的相位,给出不同的电压幅度,最后平滑出需要的频率..DDS是一种新型的频率合成技术。

具有相对带宽大、频率转换时间短、分辨率高、相位连续性好等优点,很容易实现频率、相位和幅度的数控调制,广泛应用于通讯领域.(1)基本要求1)利用QuartusII软件和SmartSOPC实验箱实现DDS的设计;2)DDS中的波形存储器模块用Altera公司的Cyclone系列FPGA芯片中的RAM实现,RAM结构配置成212×10类型;3)具体参数要求:频率控制字K取4位;基准频率fc=1MHz,由实验板上的系统时钟分频得到,系统具有清零和保持的功能;4)利用实验箱上的D/A转换器件将ROM输出的数字信号转换为模拟信号,能够通过示波器观察到正弦波形,能够同时输出正余弦两路正交信号;5)通过开关(实验箱上的Ki)输入DDS的频率和相位控制字,并能用示波器观察加以验证;(2)提高要求1)扩大频率控制和相位控制的范围,并在数码管上分别显示频率控制字K及其对应生成的频率;2)设计能输出多种波形(三角波、锯齿波、方波等)的多功能波形发生器;二、方案论证DDS组成与工作原理图:(1)频率与之语调节电路K被称为频率控制字,也叫相位增量。

DDS方程为:f0=f c K/2N,f0为输出频率,f c为时钟频率。

当K=1时,DDS输出最低频率为f c/2N,而DDS的最大输出频率由Nyquist采样定理决定,即f c//2,也就是说K的最大值为2N-1。

因此,只要N足够大,DDS可以得到很细的频率间隔。

要改变DDS的输出频率,只要改变频率控制字K即可。

直接数字频率合成技术及其接口电路设计

直接数字频率合成技术及其接口电路设计第一章概述随着科技的不断进步,频率合成技术在现代化信号系统设计中扮演着越来越重要的角色。

其中,数字频率合成技术具有显著的优势,广泛应用于无线电通信、雷达制导、导航定位等领域。

本文将重点介绍直接数字频率合成技术以及其接口电路设计。

第二章直接数字频率合成技术直接数字频率合成(Direct Digital Synthesis,DDS)是一种数字信号处理方式,可以通过程序控制生成高精度的周期信号。

DDS技术的基本原理是将一个相位累积器与一个查表器相结合,通过不断地自增相位值,并将相位值作为查表器的地址,从而在输出端实现期望频率的产生。

DDS技术可以通过改变相位累积器的增量来改变输出频率,并且频率调整速度非常快。

相比于传统的类比频率合成技术,DDS 技术的频率稳定性更高,而且能够灵活地实现各种复杂的调制方式。

由于DDS技术具有诸多优势,因此在现代化无线电通信、雷达制导、导航定位等应用领域表现出极大的优势。

第三章直接数字频率合成接口电路设计直接数字频率合成器作为一种数字信号处理器件,需要与外部输入输出信号进行交互,因此需要设计相应的接口电路。

DDS接口电路主要包括数字控制单元、时钟源、数字信号滤波器、DAC 等部分。

其中,数字控制单元负责输入频率、相位信息,生成相应的控制信号,并将这些信号传送给DDS芯片。

时钟源则向DDS芯片提供稳定的时钟信号。

数字信号滤波器用于抑制DDS芯片输出波形上的杂散谐波,确保输出信号的质量。

最后,DAC将DDS芯片输出的数字信号转换成模拟信号,输出到外部电路中。

第四章相关应用案例直接数字频率合成器在无线电通信、雷达制导、导航定位等领域中有着广泛的应用。

下面简要介绍一些相关的应用案例。

1.无线电通信:DDS技术在无线电通信领域中被广泛应用。

例如,在输入频率为100MHz,输出频率为100.5MHz的情况下,DDS芯片可以通过改变相位累积器的增量来产生相应的频率。

频率合成器

基于FPGA的直接数字频率合成技术设计直接数字频率合成(DirectDigitalFraquencySyn-thesis 即DDFS,一般简称DDS)是从相位概念出发直接合成所需波形的一种新的频率合成技术。

它在相对带宽、频率转换时间、相位连续性、正交输出、高分辨率以及集成化等一系列性能指标方面已远远超过了传统频率合成技术。

当累加器的N很大时,最低输出频率可达Hz、mHz 甚至μHz。

也就是说:DDS的最低合成频率接近于零频。

如果fc为50MHz, 那么当N为48位时,其分辨率可达179nHz。

转换时间最快可达10ns的量级,这都是传统频率合成所不能比拟的。

但它的不足之处是最高工作频率会受限、噪声和杂波不够理想。

本设计采用ALTERA公司的FPGA芯片EP1K30TC-144来实现DDS技术。

EP1K30芯片属ALTERA公司的ACEX系列,该系列是ALTERA公司着眼于通信、音频处理及类似场合应用而推出的FPGA器件系列芯片,它采用0.22/0.18微米混合工艺,密度从10000门到100000门。

所有ACEX系列器件均兼容64bit、66MHz的PCI,并支持锁相环电路。

ACEX1K采用查找表(LUT)和EAB(嵌入式阵列块)相结合的结构,可用来实现存储器、专用逻辑功能和通用逻辑功能,每个EBA能提供4096比特的存储空间,每个LE包含4个输入LUT、一个可编程的触发器、进位链和一个层叠链。

合理运用进位链能够提高系统运行速度。

EP1K30TC-144的最大系统门数为119000,它有1728个逻辑宏单元数和5个嵌入式阵列块,最大可提供2kB的ROM/RAM位,因而可完全满足DDS设计的要求。

1DDS的实现过程图1为DDS系统的基本原理图,图中的相位累加器由N位全加器和N位累加寄存器级联而成,可对频率控制字的2进制码进行累加运算,是典型的反馈电路,产生的累加结果的高M位作为ROM查找表的取样地址值,而此查找表中储存了一个周期的正弦波幅度值。

直接数字频率合成知识点汇总(原理_组成_优缺点_实现)

直接数字频率合成知识点汇总(原理_组成_优缺点_实现)直接数字频率合概述DDS同DSP(数字信号处理)一样,也是一项关键的数字化技术。

DDS是直接数字式频率合成器(Direct Digital Synthesizer)的英文缩写。

DDS 是从相位概念出发直接合成所需要波形的一种新的频率合成技术。

直接数字频率合成是一种新的频率合成技术和信号产生的方法,具有超高速的频率转换时间、极高的频率分辨率分辨率和较低的相位噪声,在频率改变与调频时,DDS能够保持相位的连续,因此很容易实现频率、相位和幅度调制。

此外,DDS技术大部分是基于数字电路技术的,具有可编程控制的突出优点。

因此,这种信号产生技术得到了越来越广泛的应用,很多厂家已经生产出了DDS专用芯片,这种器件成为当今电子系统及设各中频率源的首选器件。

直接数字频率合成原理工作过程为:1、将存于数表中的数字波形,经数模转换器D/A,形成模拟量波形。

2、两种方法可以改变输出信号的频率:(1)改变查表寻址的时钟CLOCK的频率,可以改变输出波形的频率。

(2)、改变寻址的步长来改变输出信号的频率.DDS即采用此法。

步长即为对数字波形查表的相位增量。

由累加器对相位增量进行累加,累加器的值作为查表地址。

3、D/A输出的阶梯形波形,经低通(带通)滤波,成为质量符合需要的模拟波形。

直接数字频率合成系统的构成直接数字频率合成主要由标准参考频率源、相位累加器、波形存储器、数/模转换器、低通平滑滤波器等构成。

其中,参考频率源一般是一个高稳定度的晶体振荡器,其输出信号用于DDS中各部件同步工作。

DDS的实质是对相位进行可控等间隔的采样。

直接数字频率合成优缺点优点:(1)输出频率相对带宽较宽输出频率带宽为50%fs(理论值)。

但考虑到低通滤波器的特性和设计难度以及对输出信号杂散的抑制,实际的输出频率带宽仍能达到40%fs。

(2)频率转换时间短DDS是一个开环系统,无任何反馈环节,这种结构使得DDS的频率转换时间极短。

直接数字频率合成

设计实例

MAX+PLUSⅡ的设计软件中的.tbl文件是纯文本文

件, 它包含了.scf文件或.wdf文件中的所有信息。 .tbl 文件的生成很简单, 在MAX+PLUSⅡ波形仿真结束后, 打开.scf文件, 然后从“File”菜单中选择“Create Table Files”选项, 就可产生.tbl文件。 .tbl文件的基本 格式如表8.9所示, 文件的结构可分为四大部分, 其中 第三和第四部分对我们来说是最关键的, 我们可以从 中获取仿真波形数据, 并利用计算机高级语言处理这 些数据, 将其转换为直观的波形曲线。 需要读者注意 的是, 每做一次MAX+PLUSⅡ波形仿真, 都要重新 生成一次.tbl文件, 以更新.tbl文件内的数据。

设计实例

L PM _ DIR E C T ION = " ADD" L PM _ P IPE L INE = L PM _ R E PR E S E NTAT ION = " UNS IGNE D" L PM _ W IDTH = 1 0 M AXIM IZE _ S PE E D = ONE _ INP UT_ IS _ C ONS T ANT=

j=0;

for i=1:number if data(b(i)-1)==′0′

设计实例

j=j+1; c_c(j,1)=data(b(i)+1); c_c(j,2)=data(b(i)+2); c_s(j,1)=data(b(i)+3); c_s(j,2)=data(b(i)+4); end end

8位D 触发 器

L P M_ A V A L U E = L P M _ SVAL U E = L P M_ W ID T H = 8

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

All About Direct Digital SynthesisWhat is Direct Digital Synthesis?Direct digital synthesis (DDS) is a method of producing an analog waveform —usually a sine wave —by generating a time-varying signal in digital form and then performing a digital-to-analog conversion. Because operations within a DDS device are primarily digital, it can offer fast switching between output frequencies, fine frequency resolution, and operation over a broad spectrum of frequencies. With advances in design and process technology, today’s DDS devices are very compact and draw little power.Why would one use a direct digital synthesizer (DDS)? Aren’t there other methods for easily generating frequencies?The ability to accurately produce and control waveforms of various frequencies and profiles has become a key requirement common to a number of industries. Whether providing agile sources of low-phase-noise variable-frequencies with good spurious performance for communications, or simply generating a frequency stimulus in industrial or biomedical test equipment applications, convenience, compactness, and low cost are important design considerations.Many possibilities for frequency generation are open to a designer, ranging from phase-locked-loop (PLL)-based techniques for very high-frequency synthesis, to dynamic programming of digital-to-analog converter (DAC) outputs to generate arbitrary waveforms at lower frequencies. But the DDS technique is rapidly gaining acceptance for solving frequency- (or waveform) generationrequirements in both communications andindustrial applications because single-chip ICdevices can generate programmable analogoutput waveforms simply and with high resolution and accuracy.Furthermore, the continual improvements in both process technolog y and design have resulted in cost and power consumption levels that were previously unthinkably low. For example, the AD9833, a DDS-based programmable waveform generator (Figure 1), operatingFigure 1. The AD9833-a one-chip waveformgenerator.at 5.5 V with a 25-MHz clock, consumes a maximum power of 30 milliwatts.What are the main benefits of using a DDS?DDS devices like the AD9833 are programmed through a high speed serial peripheral-interface (SPI), and need only an external clock to generate simple sine waves. DDS devices are now available that can generate frequencies from less than 1 Hz up to 400 MHz (based on a 1-GHz clock). The benefits of their low power, low cost, and single small package, combined with their inherent excellent performance and the ability to digitally program (and re-program) the output waveform, make DDS devices an extremely attractive solution—preferable to less-flexible solutions comprising aggregations of discrete elements. What kind of outputs can I generate with a typical DDS device?DDS devices are not limited to purelysinusoidal outputs. Figure 2 shows thesquare-, triangular-, and sinusoidal outputsavailable from an AD9833.How does a DDS device create asine wave?Here’s a breakdown of the internalcircuitry of a DDS device: its maincomponents are a phase accumulator, ameans of phase-to-amplitude conversion(often a sine look-up table), and a DAC. These blocks are represented in Figure 3.A DDS produces a sine waveat a given frequency. The frequency depends on two variables, the reference-clock frequency and the binar y number programmed into the Figure 2. Square-, triangular-, and sinusoidal outputs from a DDS.Figure 3. Components of a direct digital synthesizer.frequency register (tuning word).The binary number in the frequency register provides the main input to the phase accumulator. If a sine look-up table is used, the phase accumulator computes a phase (angle) address for the look-up table, which outputs the digital value of amplitude—corresponding to the sine of that phase angle—to the DAC. The DAC, in turn, converts that number to a corresponding value of analog voltage or current. To generate a fixed-frequency sine wave, a constant value (the phase increment—which is determined by the binary number) is added to the phase accumulator with each clock cycle. If the phase increment is large, the phase accumulator will step quickly through the sine look-up table and thus generate a high frequency sine wave. If the phase increment is small, the phase accumulator will take many more steps, accordingly generating a slower waveform.What do you mean by a complete DDS?The integration of a D/A converter and a DDS onto a single chip is commonly known as a complete DDS solution, a property common to all DDS devices from ADI.Let’s talk some more about the phase accumulator. How does it work?Continuous-time sinusoidal signals have a repetitive angular phase range of 0 to 2.The digital implementation is no different. The counter’scarry function allows the phase accumulator to act asa phase wheel in the DDS implementation.To understand this basic function, visualize thesine-wave oscillation as a vector rotating around aphase circle (see Figure 4). Each designated point onthe phase wheel corresponds to the equivalent pointon a cycle of a sine wave. As the vector rotatesaround the wheel, visualize that the sine of the anglegenerates a corresponding output sine wave. OneFigure 4. Digital phase wheel. revolution of the vector around the phase wheel, at aconstant speed, results in one complete cycle of the output sine wave. The phase accumulator provides the equally spaced angular values accompanying the vector’s linear rotation aroundthe phase wheel. The contents of the phase accumulator correspond to the points on the cycle of the output sine wave.The phase accumulator is actually a modulo- M counter that increments its stored number each time it receives a clock pulse. The magnitude of the increment is determined by the binary-coded input word (M). This word forms the phase step size between reference-clock updates; it effectively sets how many points to skip around the phase wheel. The larger the jump size, the faster the phase accumulator overflows and completes its equivalent of a sine-wave cycle. The number of discrete phase points contained in the wheel is determined by the resolution of the phase accumulator (n), which determines the tuning resolution of the DDS. For an n = 28-bit phase accumulator, an M value of 0000...0001 would result in the phase accumulator overflowing after 28 reference-clock cycles (increments). If the M value is changed to 0111...1111, the phase accumulator will overflow after only 2 reference-clock cycles (the minimum required by Nyquist). This relationship is found in the basic tuning equation for DDS architecture:n C out f M f 2⨯= where:fOUT = output frequency of the DDSM = binary tuning wordfC = internal reference clock frequency (system clock)n = length of the phase accumulator, in bitsChanges to the value of M result in immediate and phase-continuous changes in the output frequency. No loop settling time is incurred as in the case of a phase-locked loop.As the output frequency is increased, the number of samples per cycle decreases. Since sampling theory dictates that at least two samples per cycle are required to reconstruct the output waveform, the maximum fundamental output frequency of a DDS is fC/2. However, for practical applications, the output frequency is limited to somewhat less than that, improving the quality of the reconstructed waveform and permitting filtering on the output.When generating a constant frequency, the output of the phase accumulator increaseslinearly, so the analog waveform it generates is inherently a ramp.Then how is that linear output translated into a sine wave?A phase -to - amplitude lookup table is used to convert the phase-accumulator’sinstantaneous output value (28 bits for AD9833)—with unneeded less-significant bits eliminated by truncation—into the sine-wave amplitude information that is presented to the (10 -bit) D/A converter. The DDS architecture exploits the symmetrical nature of a sine wave and utilizes mapping logic to synthesize a complete sine wave from one-quarter-cycle of data from the phase accumulator. The phase-to- amplitude lookup table generates the remainingdata by reading forward then back through the lookup table. This is shown pictorially in Figure 5.Figure 5. Signal flow through the DDS architecture.关于直接数字频率合成器什么是直接数字频率合成器?直接数字频率合成器(DDS)是一种通过产生一个以数字形式时变的信号,然后执行由数字至模拟转换的方法。