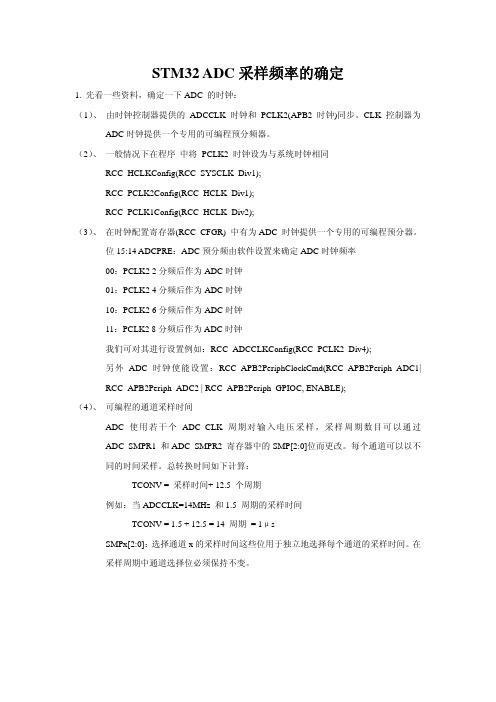

STM32 ADC采样频率的确定

STM32ADCDMA采样时间计算

STM32ADCDMA采样时间计算在STM32上,ADC的采样时间取决于以下几个因素:1. ADC时钟频率(ADC Clock Frequency):选择合适的时钟频率可以提高采样速度。

2. ADC分辨率(ADC Resolution):ADC的分辨率越高,采样时间越长。

3. ADC转换周期(ADC Conversion Cycle):每次转换的时间,包括单次转换和连续转换。

首先,我们需要确定ADC时钟频率。

在STM32中,ADC的时钟频率可以通过设置RCC_CCFGR寄存器的相应位来选择。

这个时钟频率决定了每个ADC转换周期所花费的时间。

其次,我们需要确定ADC分辨率。

在STM32中,ADC的分辨率可以通过设置ADC_CR1寄存器的相应位来选择。

通常有8位、10位、12位和16位等选项。

分辨率越高,则每次转换所需的时间越长。

最后,我们需要确定ADC转换周期。

在STM32中,默认情况下每次转换只需要一个转换周期。

如果需要连续采样,则还需要考虑连续转换模式。

计算ADC采样时间的公式为:ADC采样时间=ADC转换周期×ADC分辨率/ADC时钟频率例如,假设ADC转换周期为10个时钟周期,分辨率为12位(4096个转换步骤),时钟频率为10MHz,则:ADC采样时间=10×4096/10,000,000≈4.096μs在使用DMA进行数据传输时,可以将ADC的转换结果直接传输到SRAM等目标内存区域,从而减少CPU的负担和数据传输的延迟。

总结起来,通过合理设置ADC时钟频率、分辨率和转换周期,以及结合DMA进行数据传输,可以实现高效的数据采样和处理。

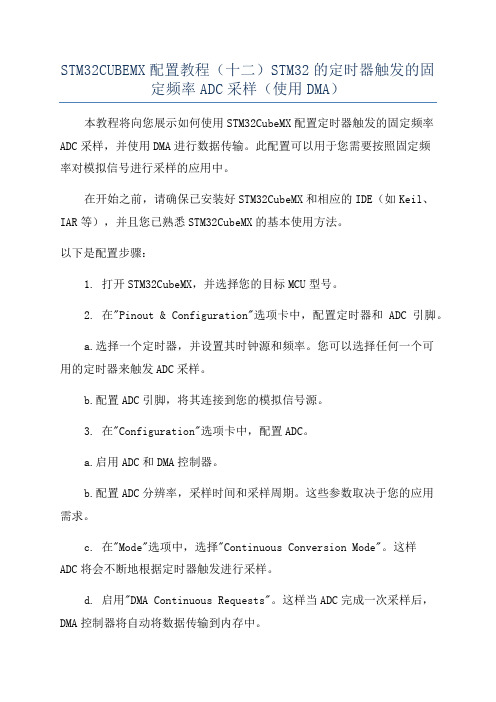

STM32CUBEMX配置教程(十二)STM32的定时器触发的固定频率ADC采样(使用DMA)

STM32CUBEMX配置教程(十二)STM32的定时器触发的固定频率ADC采样(使用DMA)本教程将向您展示如何使用STM32CubeMX配置定时器触发的固定频率ADC采样,并使用DMA进行数据传输。

此配置可以用于您需要按照固定频率对模拟信号进行采样的应用中。

在开始之前,请确保已安装好STM32CubeMX和相应的IDE(如Keil、IAR等),并且您已熟悉STM32CubeMX的基本使用方法。

以下是配置步骤:1. 打开STM32CubeMX,并选择您的目标MCU型号。

2. 在"Pinout & Configuration"选项卡中,配置定时器和ADC引脚。

a.选择一个定时器,并设置其时钟源和频率。

您可以选择任何一个可用的定时器来触发ADC采样。

b.配置ADC引脚,将其连接到您的模拟信号源。

3. 在"Configuration"选项卡中,配置ADC。

a.启用ADC和DMA控制器。

b.配置ADC分辨率,采样时间和采样周期。

这些参数取决于您的应用需求。

c. 在"Mode"选项中,选择"Continuous Conversion Mode"。

这样ADC将会不断地根据定时器触发进行采样。

d. 启用"DMA Continuous Requests"。

这样当ADC完成一次采样后,DMA控制器将自动将数据传输到内存中。

4. 在"NVIC Settings"选项卡中,启用DMA和ADC中断。

5. 在"Project"选项卡中,选择生成代码所需的IDE和工程路径。

然后单击"Generate Code"按钮生成代码。

现在您已成功配置了定时器触发的固定频率ADC采样,并使用DMA进行数据传输。

您可以在生成的代码中初始化和启用各个模块,并编写相应的中断处理函数来处理DMA和ADC中断。

STM32 ADC 采样速率计算

stm32 ADC采样速率的问题RCC_ADCCLKConfig(RCC_PCLK2_Div8); ADC_RegularChannelConfig(ADC1, ADC_Channel_11, 1, ADC_SampleTime_55Cycles5); 系统时钟72M,以上两句是不是ADC时钟设置为9M,然后用55.5个采用周期?那ADC就是55.5*1/9us,采集一次什么?那ADC最快和最慢采样速率...展开1,ADC时钟是设为9M2,ADC总转换时间=采样时间+12.5个ADC时钟周期(信号量转换时间),而采样时间由寄存器设定,最低1.5ADC周期,最大239.5ADC周期,也就是你程序中设置的55.5个采样周期。

所以ADC一次采样的总采样时间是55.5+12.5=68个ADC周期,也就是68/9 us3,所以,总采样时间最快就是1.5+12.5个ADC周期,最慢就是239.5+12.5个ADC周期。

至于采样速率,是跟你的程序是有关的,比如ADC采样时间设定为最快,但你可以设定1s采一次,那采样速率仍是1;再比如你开启扫描模式,跟单次转换又不一样总结(lee):1、CLK_ADC = PCLK2/ADC_DIV , ADC_DIV 由程序设定。

2、TIME_ADC_CONVERT = TIME_SAMPLE + TIME_SIGNAL_CONVERT1.5 <= TIME_SAMPLE <= 239.5 ,TIME_SAMPLE是在配置ADC的时候程序写入的(根据实际需要来设置),例如上面例子中设置的事55.5 .TIME_SIGNAL_CONVERT(最低12.5个周期,硬件因素决定,无法改变)3、ADC转换时间 = CLK_ADC / TIME_ADC_CONVERT4、ADC的时钟最高为14M,如果PCLK2 为72M,那么 ADC的时钟最高只能设置成12M(72 M 6 分频)此时ADC的转换速率为12M/( 12.5 +1.5 ),没有1M。

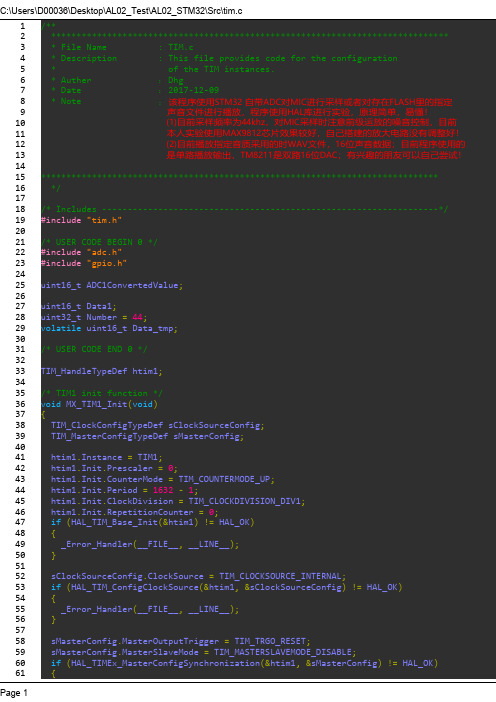

STM32驱动内部ADC对MIC进行采样播放程序

_Error_Handler(__FILE__, __LINE__); } } void HAL_TIM_Base_MspInit(TIM_HandleTypeDef* tim_baseHandle) { if(tim_baseHandle->Instance==TIM1) { /* USER CODE BEGIN TIM1_MspInit 0 */ /* USER CODE END TIM1_MspInit 0 */ /* Peripheral clock enable */ __HAL_RCC_TIM1_CLK_ENABLE(); /* TIM1 interrupt Init */ HAL_NVIC_SetPriority(TIM1_UP_IRQn, 0, 0); HAL_NVIC_EnableIRQ(TIM1_UP_IRQn); /* USER CODE BEGIN TIM1_MspInit 1 */ /* USER CODE END TIM1_MspInit 1 */ } } void HAL_TIM_Base_MspDeInit(TIM_HandleTypeDef* tim_baseHandle) { if(tim_baseHandle->Instance==TIM1) { /* USER CODE BEGIN TIM1_MspDeInit 0 */ /* USER CODE END TIM1_MspDeInit 0 */ /* Peripheral clock disable */ __HAL_RCC_TIM1_CLK_DISABLE(); /* TIM1 interrupt Deinit */ HAL_NVIC_DisableIRQ(TIM1_UP_IRQn); /* USER CODE BEGIN TIM1_MspDeInit 1 */ /* USER CODE END TIM1_MspDeInit 1 */ } } /* USER CODE BEGIN 1 */ /******************************PLAY MIC SAMPLING SOUND****************************************************/ void HAL_TIM_PeriodElapsedCallback(TIM_HandleTypeDef *htim) { if (htim->Instance == htim1.Instance) { HAL_ADC_Start(&hadc1); HAL_ADC_PollForConversion(&hadc1, 50); if(HAL_IS_BIT_SET(HAL_ADC_GetState(&hadc1), HAL_ADC_STATE_REG_EOC)) { ADC1ConvertedValue = HAL_ADC_GetValue(&hadc1); }

stm32f4adc采样频率计算

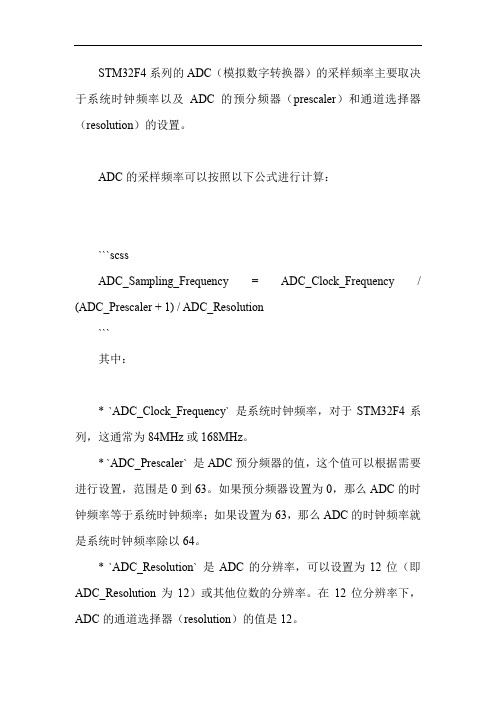

STM32F4系列的ADC(模拟数字转换器)的采样频率主要取决于系统时钟频率以及ADC的预分频器(prescaler)和通道选择器(resolution)的设置。

ADC的采样频率可以按照以下公式进行计算:

```scss

ADC_Sampling_Frequency = ADC_Clock_Frequency / (ADC_Prescaler + 1) / ADC_Resolution

```

其中:

* `ADC_Clock_Frequency` 是系统时钟频率,对于STM32F4系列,这通常为84MHz或168MHz。

* `ADC_Prescaler` 是ADC预分频器的值,这个值可以根据需要进行设置,范围是0到63。

如果预分频器设置为0,那么ADC的时钟频率等于系统时钟频率;如果设置为63,那么ADC的时钟频率就是系统时钟频率除以64。

* `ADC_Resolution` 是ADC的分辨率,可以设置为12位(即ADC_Resolution为12)或其他位数的分辨率。

在12位分辨率下,ADC的通道选择器(resolution)的值是12。

因此,如果你想计算12位分辨率下,系统时钟频率为84MHz,预分频器为63的ADC的采样频率,你可以这样做:

```scss

ADC_Sampling_Frequency = 84MHz / (63 + 1) / 12 = 1.024MHz

```

这意味着ADC的采样频率为1.024MHz。

请注意,这些计算假定ADC的其他设置(如通道选择器、比较器、DMA等)不会影响ADC的采样频率。

这些设置可能会影响实际的采样频率。

stm32f4adc采样频率计算

stm32f4adc采样频率计算一、STM32F4ADC简介STM32F4ADC(Analog-to-Digital Converter,模拟-数字转换器)是STM32F4系列微控制器内置的一款高性能、高精度的模拟转换器。

它能够将连续的模拟信号转换为离散的数字信号,广泛应用于各种传感器数据采集、信号处理等领域。

二、采样频率计算方法在实际应用中,采样频率是一个非常重要的参数。

根据奈奎斯特定理,采样频率必须大于信号最高频率的两倍,才能保证信号的完整性,避免发生混叠。

1.确定ADC转换位数首先,需要确定ADC的转换位数。

一般来说,转换位数越高,采样精度越高,但同时也会增加数据处理和存储的负担。

常见的ADC转换位数有8位、10位、12位等。

2.计算最大模拟电压根据ADC的位数和电源电压,可以计算出ADC的最大模拟电压。

例如,对于12位ADC,最大模拟电压为电源电压的一半(即2^12=4095)。

3.计算采样频率采样频率等于ADC的最大转换速度除以最大模拟电压。

ADC的最大转换速度通常在数据手册中会有说明。

例如,如果最大转换速度为100MSPS(百万次每秒),则采样频率计算公式为:采样频率= 100MSPS / 4095 = 24.4kHz三、注意事项1.考虑到STM32F4ADC的采样速率、模拟输入范围等因素,合理选择ADC的转换位数和采样频率。

2.确保采样频率大于信号最高频率的两倍,避免信号混叠。

3.在实际应用中,可以根据需求调整采样频率,以达到最佳的性能和功耗平衡。

4.考虑到ADC的分辨率和电源电压,合理设置ADC的参考电压和偏置电压。

四、总结本文介绍了STM32F4ADC的简介、采样频率的计算方法以及注意事项。

通过合理选择ADC的转换位数、采样频率等参数,可以充分发挥STM32F4ADC的高性能和实用性,为各种传感器数据采集和信号处理应用提供可靠的支持。

STM32中AD采样的三种方法分析

STM32中AD采样的三种⽅法分析 在进⾏STM32F中AD采样的学习中,我们知道AD采样的⽅法有多种,按照逻辑程序处理有三种⽅式,⼀种是查询模式,⼀种是中断处理模式,⼀种是DMA模式。

三种⽅法按照处理复杂⽅法DMA模式处理模式效率最⾼,其次是中断处理模式,最差是查询模式,相信很多学者在学习AD采样程序时,很多例程采⽤DMA模式,在这⾥我针对三种程序进⾏分别分析。

1、AD采样查询模式 在AD采样查询模式中,我们需要注意的是IO⼝的初始化配置,这⾥我采⽤PA2作为模拟采集的引脚(AIN2)和串⼝3作为打印输出。

具体如下:建⽴⼀个USART3.C和USART3.H⽂件,其程序为: #include "usart3.h" #include "stdarg.h" u8 SendBuff[SENDBUFF_SIZE]; void USART3_Config(void) { //定义结构体 GPIO_InitTypeDef GPIO_InitStructure; USART_InitTypeDef USART_InitStructure; //开启外部时钟 RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOB | RCC_APB2Periph_AFIO, ENABLE); RCC_APB1PeriphClockCmd(RCC_APB1Periph_USART3, ENABLE ); // USART3 GPIO config GPIO_InitStructure.GPIO_Pin = GPIO_Pin_10; GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF_PP; GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz; GPIO_Init(GPIOB, &GPIO_InitStructure); GPIO_InitStructure.GPIO_Pin = GPIO_Pin_11; GPIO_InitStructure.GPIO_Mode = GPIO_Mode_IN_FLOAtiNG; GPIO_Init(GPIOB, &GPIO_InitStructure); //USART3 mode config USART_ART_BaudRate = 115200; USART_ART_WordLength = USART_WordLength_8b; USART_ART_StopBits = USART_StopBits_1; USART_ART_Parity = USART_Parity_No; USART_ART_HardwareFlowControl = USART_HardwareFlowControl_None; USART_ART_Mode = USART_Mode_Rx | USART_Mode_Tx; USART_Init(USART3, &USART_InitStructure); USART_Cmd(USART3, ENABLE); } 其次建⽴⼀个ADC.C和⼀个ADC.H⽂件,其中ADC.C中程序为: void ADC1_Init(void) { ADC1_GPIO_Config(); ADC1_Mode_Config(); } static void ADC1_GPIO_Config(void) { GPIO_InitTypeDef GPIO_InitStructure; //开启外部时钟 RCC_APB2PeriphClockCmd(RCC_APB2Periph_ADC1 | RCC_APB2Periph_GPIOA,ENABLE); //配置PA2引脚 GPIO_InitStructure.GPIO_Pin = GPIO_Pin_2; //配置为模拟输⼊ GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AIN; //调⽤库函数 GPIO_Init(GPIOA, &GPIO_InitStructure); } static void ADC1_Mode_Config(void) { //ADC1_ configuration ADC_InitStructure.ADC_Mode = ADC_Mode_Independent; //独⽴ADC模式 ADC_InitStructure.ADC_ScanConvMode = DISABLE; //禁⽌扫描模式 ADC_InitStructure.ADC_ContinuousConvMode = ENABLE; //开启连续转换模式 ADC_InitStructure.ADC_ExternalTrigConv = ADC_ExternalTrigConv_None; //不使⽤外部触发转换 ADC_InitStructure.ADC_DataAlign = ADC_DataAlign_Right; //采集数据右对齐 ADC_InitStructure.ADC_NbrOfChannel = 1; //要转换的通道数⽬1 ADC_Init(ADC1,&ADC_InitStructure); //配置ADC时钟,为PCLK2的8分频,即9Mhz RCC_ADCCLKConfig(RCC_PCLK2_Div8); //配置ADC1的通道2位55.5个采集周期 ADC_RegularChannelConfig(ADC1,ADC_Channel_2, 1, ADC_SampleTime_55Cycles5); ADC_Cmd(ADC1,ENABLE); //复位校准寄存器 ADC_ResetCalibration(ADC1); //等待校准寄存器复位完成 while(ADC_GetResetCalibrationStatus(ADC1)); //ADC校准 ADC_StartCalibration(ADC1); while(ADC_GetCalibrationStatus(ADC1)); //由于没有使⽤外部触发,所以使⽤软件触发ADC转换 ADC_SoftwareStartConvCmd(ADC1,ENABLE); } 然后在主函数main中其程序代码如下: int main(void) { USART3_Config(); ADC1_Init(); printf("输⼊ADC值"); while(1) { ADC_ConvertedValue = ADC_GetConversionValue(ADC1); ADC_ConvertedValueLocal =(float)ADC_ConvertedValue/4096*3.3; //读取ADC转换的值 printf("\r\n the current AD value = 0x%04X \r\n",ADC_ConvertedValue); printf("\r\n the current AD value = %f V \r\n",ADC_ConvertedValueLocal); Delay(0xFFFFEE); } } 这样采⽤查询的⽅法即可以采集ADC的电压值,⼀个值为16进制转换的值,⼀个是转换计算的值。

STM32 ADC采样时间、采样周期、采样频率计算方法

STM32 ADC 采样时间、采样周期、采样频率计算

方法

ADC 转换就是输入模拟的信号量,单片机转换成数字量。

读取数字量必须等转换完成后,完成一个通道的读取叫做采样周期。

采样周期一般来说=转换时间+读取时间。

而转换时间=采样时间+12.5 个时钟周期。

采样时间是你通过寄存器告诉STM32 采样模拟量的时间,设置越长越精确

一STM32 ADC 采样频率的确定

1. :先看一些资料,确定一下ADC 的时钟:

(1),由时钟控制器提供的ADCCLK 时钟和PCLK2(APB2 时钟)同步。

CLK

控制器为ADC 时钟提供一个专用的可编程预分频器。

(2) 一般情况下在程序中将PCLK2 时钟设为与系统时钟相同

/* HCLK = SYSCLK */

RCC_HCLKConfig(RCC_SYSCLK_Div1);。

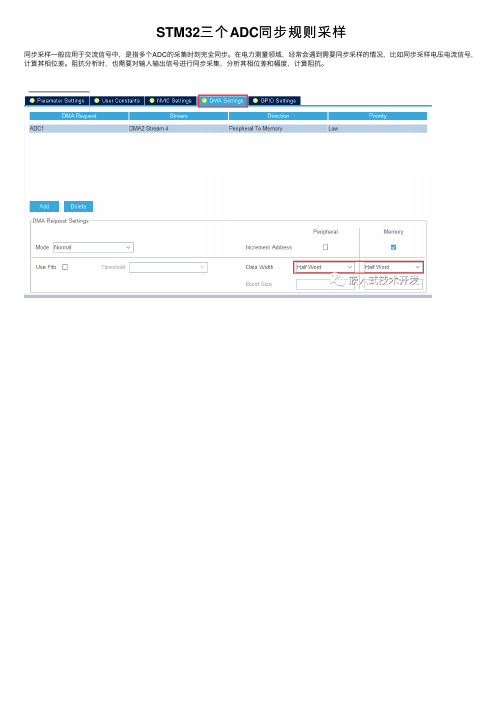

STM32三个ADC同步规则采样

STM32三个ADC同步规则采样同步采样⼀般应⽤于交流信号中,是指多个ADC的采集时刻完全同步。

在电⼒测量领域,经常会遇到需要同步采样的情况,⽐如同步采样电压电流信号,计算其相位差。

阻抗分析时,也需要对输⼊输出信号进⾏同步采集,分析其相位差和幅度,计算阻抗。

1.Mode选择为三重同步规则模式。

2.使能DMA连续请求。

3.外部触发源选择TIM2触发事件。

配置完成后,打开ADC2和ADC3的配置,可以看到,Mode已经⾃动配置为三重同步规则模式,且外部触发源也已经隐藏⽆法选择,因为三重同步规则模式下,三个ADC必须使⽤同⼀个外部触发源。

同时ADC2和ADC3的DMA也不需要配置,使⽤同⼀个DMA。

ADC2配置如下:ADC配置完成后,打开TIM2定时器,⽤于触发ADC采样。

TIM2时钟选择内部时钟(84MHz),选择触发事件为Update Event,⽤于触发ADC。

配置其分频系数和计数周期如下,则ADC的采样率为84MHz÷(83+1) ÷(199+1)=5000Hz。

uint8_t DMA_Flag = 0;void HAL_ADC_ConvCpltCallback(ADC_HandleTypeDef* hadc){DMA_Flag = 1;}HAL_ADC_Start(&hadc1);HAL_ADC_Start(&hadc2);HAL_ADC_Start(&hadc3);//启动ADCHAL_ADCEx_MultiModeStart_DMA(&hadc1,(uint32_t*)adcbuf1,300);//启动同步规则模式及DMA,3个ADC,每次采样100个点*3 HAL_TIM_Base_Start(&htim2);//启动TIM2,⽤于触发ADC采样/* USER CODE END 2 *//* Infinite loop *//* USER CODE BEGIN WHILE */while (1){if(DMA_Flag == 1)//AD转换完成标准{DMA_Flag = 0;HAL_TIM_Base_Stop(&htim2);HAL_ADCEx_MultiModeStop_DMA(&hadc1);HAL_ADC_Stop(&hadc1);HAL_ADC_Stop(&hadc2);HAL_ADC_Stop(&hadc3);//停⽌采样for(uint8_t i=0;i<100;i++)< span="">{sprintf(str,"$,%d,%d,%d",adcbuf1[i][0],adcbuf1[i][1],adcbuf1[i][2]);HAL_UART_Transmit(&huart1,(uint8_t*)str,strlen(str),100);//串⼝发送到上位机}HAL_ADC_Start(&hadc1);HAL_ADC_Start(&hadc2);HAL_ADC_Start(&hadc3);HAL_ADCEx_MultiModeStart_DMA(&hadc1,(uint32_t*)adcbuf1,300);HAL_TIM_Base_Start(&htim2);//重新启动采样}/* USER CODE END WHILE *//* USER CODE BEGIN 3 */}/* USER CODE END 3 */。

STM32的ADC采样频率及相应时间的确定

STM32 的ADC 采样频率及相应时间的确定STM32 ADC 介绍

STM32 ADC 是一个12 位精度、一种逐次逼近型模拟数字转换器。

它有多达18 个通道,可测量16 个外部和2 个内部信号源。

各通道的

A/D 转换可以单次、连续、扫描或间断模式执行。

ADC 的结果可以左对齐或右对齐方式存储在16 位数据寄存器中。

ADC 的输入时钟不得超过14MHz,它是由PCLK2 经分频产生。

转换时最快为1us,当ADC 的输入时钟超过14MHz 时其会损失一些精度。

当然如果可以达到我们的精度,输入时钟高点也没事。

在网上看到一回答ADC 不超过14MHz 的答案:资料上的都是推荐,事实上很多芯片的设计都是有超额余量的,很多人都会超额的利用这些资源,并且很好的工作。

若所看的程序频率是超过14M,也没有错,可能作者的目的在于快

速而宁愿损失一些精度,ADC 的分辨率是12 位,若是超过这个频率也是工作的,只不过采样到的精度可能仅到10 位,若这个已到作者的要求,也无错误之说了。

stm32adc采样频率计算

stm32adc采样频率计算1.前言本文将介绍如何计算S TM32微控制器中的AD C(模拟数字转换器)的采样频率。

我们将从基本原理开始,解释如何通过配置寄存器来实现所需的采样频率。

2.采样频率的定义在开始计算之前,让我们先明确什么是采样频率。

采样频率是指在模拟信号转换为数字信号时,获取模拟信号的速率。

它决定了系统对信号的精细程度和频率响应。

3. ST M32微控制器中的AD C模块S T M32微控制器通过其内置的AD C模块实现模拟信号的转换。

该模块可以设置为不同的采样频率,以满足不同应用的需求。

4. AD C采样频率的计算为了计算所需的A DC采样频率,我们需要考虑以下几个因素:4.1时钟频率A D C模块的时钟频率决定了其工作速度。

在S TM32微控制器中,时钟频率可以通过配置RC C(R es et an dC lo ck C on tr ol)寄存器来设置。

4.2A D C分辨率A D C模块的分辨率表示可以转换的模拟信号范围。

在S TM32微控制器中,分辨率可以通过配置AD C的C R寄存器来设置。

4.3A D C转换时间A D C转换时间表示进行一次模拟信号转换所需的时间。

它可以通过配置A DC的S MP R(Sam p le ti me)寄存器来设置。

4.4定时器的使用为了实现所需的采样频率,我们可以使用定时器来触发AD C的转换。

定时器的时钟频率、预分频因子和自动重装载寄存器的设置将影响AD C的采样频率。

5. AD C采样频率的计算公式根据以上因素,我们可以使用以下公式计算A DC的采样频率:采样频率=A DC时钟频率/(转换时间+12.5个A DC时钟周期)其中,转换时间表示A DC进行一次转换所需的时间(以秒为单位)。

6.示例为了更好地理解A DC采样频率的计算过程,我们来看一个示例。

假设:-A DC时钟频率为10M H z-转换时间为1u s根据以上假设和公式,我们可以计算出采样频率:采样频率=10M Hz/(1u s+12.5*(1/10M Hz))=800kH z因此,在这个示例中,A DC的采样频率为800kH z。

stm32f4adc采样频率计算

stm32f4adc采样频率计算摘要:I.简介- 介绍STM32F4ADC 和其采样频率的重要性II.STM32F4ADC 采样频率的计算- 采样周期和采样频率的关系- 如何计算采样频率- 影响采样频率的因素III.实际应用中的采样频率选择- 举例说明不同应用场景下的采样频率选择- 采样频率选择对系统性能的影响IV.总结- 总结采样频率计算和选择的重要性正文:I.简介STM32F4ADC 是意法半导体公司的一款高性能ADC(模数转换器),广泛应用于各种电子设备中,如音频处理、传感器数据采集等。

在实际应用中,采样频率的选择非常关键,它直接影响到系统的性能和稳定性。

因此,了解STM32F4ADC 采样频率的计算方法和选择原则是非常必要的。

II.STM32F4ADC 采样频率的计算采样频率是指在一定时间内,ADC 从模拟信号中提取并转换为数字信号的次数。

它与采样周期(即ADC 完成一次采样所需要的时间)的关系是采样频率=1/采样周期。

计算采样频率的公式为:采样频率(Hz)= 系统时钟频率(Hz)/ 采样器设置其中,系统时钟频率是指STM32F4ADC 所连接的系统时钟,采样器设置则决定了ADC 的采样方式。

影响采样频率的因素主要有系统时钟频率、采样器设置和ADC 的工作模式。

在实际应用中,需要根据系统需求和硬件条件来合理选择这些因素,以达到最佳的采样效果。

III.实际应用中的采样频率选择在实际应用中,采样频率的选择需要根据具体场景和需求来确定。

例如,在音频处理中,采样频率通常选择为44.1kHz 或48kHz,以满足CD 音质的要求;而在传感器数据采集等对实时性要求较高的场景中,采样频率可能需要达到100kHz 甚至更高。

采样频率的选择对系统性能有着重要影响。

一方面,较高的采样频率可以提高数据的准确性和完整性,但同时也会增加系统的处理负担和功耗;另一方面,较低的采样频率可以降低系统功耗,但可能会影响数据的质量和实时性。

STM32的ADC的采样周期确定

我们可对其进行设置例如:

RCC_ADCCLKConfig(RCห้องสมุดไป่ตู้_PCLK2_Div4);

另外还有ADC时钟使能设置

RCC_APB2PeriphClockCmd(RCC_APB2Periph_ADC1|

RCC_APB2Periph_ADC2 |

RCC_APB2Periph_GPIOC,ENABLE);

1.:先看一些资料,确定一下ADC的时钟:

(1)、由时钟控制器提供的ADCCLK时钟和PCLK2(APB2时

钟)同步。CLK控制器为ADC时钟提供一个专用的可编程预分频器。

(2)、一般情况下在程序中将PCLK2时钟设为与系统时钟相同

RCC_HCLKConfig(RCC_SYSCLK_Div1);

RCC_PCLK2Config(RCC_HCLK_Div1);

每个通道可以以

不同的时间采样。

总转换时间如下计算:

TCONV =采样时间+ 12.5个周期

例如:

当ADCCLK=36MHz和239.5周期的采样时间

TCONV = 239.5 + 12.5 = 252周期= 7μs

若你采样的是1KHz的正弦波信号,采样了10000个点,则其中就有

70个周期。

STM32 ADC采样频率的确定

STM32的ADC的采样周期确定

采样频率的确定

1.首先确定ADC的时钟,这里需要看你的RCC的设置。在采用固

件库的基础上,设定ADC的采样频率相对来说是很容易的。

(1)由时钟控制器提供的ADCCLK时钟和PCLK2(APB2时钟)

同步。CLK控制器为ADC时钟提供一个专用的可编程预分频器。

stm32f103最少有2个AD模数转换器

STM32 ADC 采样频率的确定(4)16.7 可编程的通道采样时间ADC 使用若干个ADC_CLK 周期对输入电压采样,采样周期数目可以通过ADC_SMPR1 和ADC_SMPR2 寄存器中的SMP[2:0]位而更改。

每个通道可以以不同的时间采样。

总转换时间如下计算:T CONV = 采样时间+ 12.5 个周期例如:当ADCCLK=14MHz 和1.5 周期的采样时间T CONV = 1.5 + 12.5 = 14 周期= 1μsSMPx[2:0]:选择通道x的采样时间这些位用于独立地选择每个通道的采样时间。

在采样周期中通道选择位必须保持不变。

000:1.5周期100:41.5周期001:7.5周期101:55.5周期010:13.5周期110:71.5周期011:28.5周期111:239.5周期注:– ADC1的模拟输入通道16和通道17在芯片内部分别连到了温度传感器和V REFINT。

– ADC2的模拟输入通道16和通道17在芯片内部连到了V SS。

2.具体分析如下:(1)我们的输入信号是50Hz (周期为20ms),初步定为1周期200个采样点,(注:一周期最少采20个点,即采样率最少为1k),每2个采样点间隔为20ms /200 = 100 us ADC可编程的通道采样时间我们选最小的 1.5 周期,则ADC采样周期一周期大小为100us /1.5=66us 。

ADC 时钟频率为1/66us =15 KHz。

ADC可编程的通道采样时间我们选71.5 周期,则ADC采样周期一周期大小为(100us /71.5)。

ADC 时钟频率为7.15MHz。

(2)接下来我们要确定系统时钟:我们用的是8M Hz 的外部晶振做时钟源(HSE),估计得经过PLL倍频PLL 倍频系数分别为2的整数倍,最大72 MHz。

为了提高数据计算效率,我们把系统时钟定为72MHz,(PLL 9倍频)。

则PCLK2=72MHz,PCLK1=36MHz;我们通过设置时钟配置寄存器(RCC_CFGR) 中有为ADC 时钟提供一个专用的可编程预分器,将PCLK2 8 分频后作为ADC 的时钟,则可知ADC 时钟频率为9MHz 从手册可知:A DC 转换时间:STM32F103xx 增强型产品:ADC 时钟为56MHz 时为1μs(ADC 时钟为72MHz 为1.17μs)(3)由以上分析可知:不太对应,我们重新对以上中内容调整,提出如下两套方案:方案一:我们的输入信号是50Hz (周期为20ms),初步定为1周期2500个采样点,(注:一周期最少采20个点,即采样率最少为1k),每2个采样点间隔为20ms /2500 = 8 us ADC可编程的通道采样时间我们选71.5 周期,则ADC采样周期一周期大小为8us /71.5 。

stm32f4adc采样频率计算

stm32f4adc采样频率计算(原创版)目录1.STM32F4ADC 概述2.采样频率的定义和重要性3.STM32F4ADC 采样频率计算方法4.采样频率对 ADC 性能的影响5.总结正文一、STM32F4ADC 概述STM32F4ADC是一款高性能的模拟/数字转换器(ADC),广泛应用于各种嵌入式系统中,如传感器信号采集、音频处理和图像处理等领域。

STM32F4ADC具有高速、低噪声和多功能等特点,可以满足不同场景下的采样需求。

二、采样频率的定义和重要性采样频率是指在单位时间内对模拟信号进行采样的次数,通常用赫兹(Hz)表示。

在数字信号处理领域,采样频率是一个十分重要的参数,因为它直接影响到信号的质量和性能。

根据奈奎斯特定理,采样频率必须大于信号中最高频率的 2 倍,才能保证信号的完整性,避免发生混叠现象。

三、STM32F4ADC 采样频率计算方法在计算 STM32F4ADC 的采样频率时,需要先确定信号的最高频率fmax。

通常,fmax 可以通过信号的带宽或者最大幅度来估计。

然后,根据奈奎斯特定理,采样频率 fs.max 应大于 2fmax,即:fs.max > 2fmax根据实际应用场景和性能要求,可以适当调整采样频率,以满足不同需求。

四、采样频率对 ADC 性能的影响采样频率对 ADC 的性能有很大影响,主要体现在以下几个方面:1.采样频率越高,信号的还原程度越高,可以获得更高的分辨率和更精确的模拟信号表示。

2.采样频率越高,相应的数据量也会增大,对存储和传输带宽要求更高。

3.采样频率过高,可能会导致系统的功耗增加和成本上升。

因此,在实际应用中,需要根据具体需求和条件,权衡采样频率和其他性能指标之间的关系,以获得最佳的 ADC 性能。

五、总结STM32F4ADC 采样频率的计算是一个关键的环节,直接影响到 ADC 的性能和应用效果。

stm32f4adc采样频率计算

stm32f4adc采样频率计算摘要:一、STM32 ADC基本概念1.ADC作用2.ADC采样原理二、STM32 F4 ADC采样频率计算1.计算公式2.影响因素三、采样频率与信号质量的关系1.采样定理2.采样频率与信号频谱四、提高采样频率的方法1.优化时钟源2.调整ADC参数五、实际应用案例分析1.某型STM32 F4 ADC芯片参数2.采样频率计算与实际应用正文:一、STM32 ADC基本概念1.ADC作用STM32 ADC(模数转换器)是一种用于将模拟信号转换为数字信号的电路。

在嵌入式系统中,ADC起着至关重要的作用,它使得计算机能够理解和处理来自各种传感器的模拟信号。

2.ADC采样原理ADC采样原理是根据奈奎斯特定理,在模拟信号中,以大于信号最高频率两倍的采样频率对信号进行采样,可以保证信号的完整性,避免发生混叠。

二、STM32 F4 ADC采样频率计算1.计算公式STM32 F4 ADC采样频率计算公式如下:采样频率(fs)= adc时钟频率(ADCCLK)/ 采样位数(N)其中,adc时钟频率(ADCCLK)由时钟控制器提供,采样位数(N)表示ADC转换结果的位数。

2.影响因素采样频率受以下因素影响:- ADC转换速度:ADC转换速度越快,采样频率越高。

- 系统时钟:系统时钟频率越高,ADC时钟频率越高,采样频率越高。

- 采样位数:采样位数越多,所需采样频率越高。

三、采样频率与信号质量的关系1.采样定理在进行模拟/数字信号转换过程中,当采样频率fs.max大于信号中最高频率fmax的2倍时,可以保证信号的完整性,避免发生混叠。

2.采样频率与信号频谱采样频率与信号频谱关系密切。

较高的采样频率可以捕捉到信号的更多细节,使信号处理结果更精确。

同时,采样频率越高,所需的存储空间和计算资源也越多。

四、提高采样频率的方法1.优化时钟源选择更高频率的时钟源,以提高ADC的采样频率。

2.调整ADC参数通过调整ADC的采样位数、转换速度等参数,提高采样频率。

stm32 ADC多通道采样例程(HAL库)

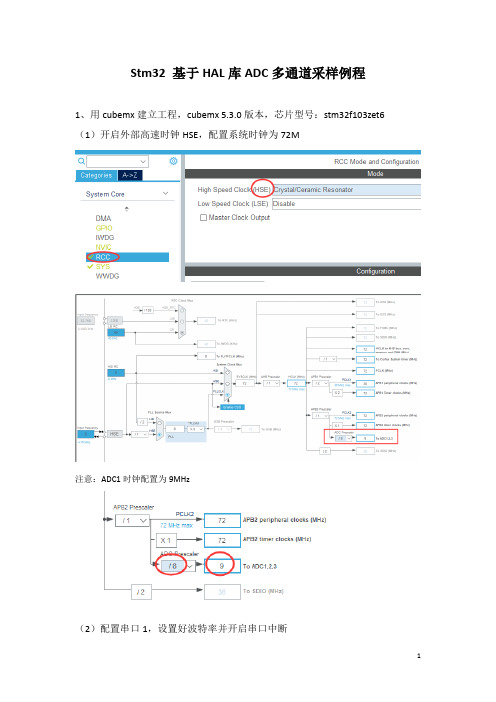

Stm32 基于HAL库ADC多通道采样例程1、用cubemx建立工程,cubemx 5.3.0版本,芯片型号:stm32f103zet6(1)开启外部高速时钟HSE,配置系统时钟为72M注意:ADC1时钟配置为9MHz(2)配置串口1,设置好波特率并开启串口中断2、启用ADC1 通道1,3,4,5,6注意要先设置好通道数量才能配置,各自ADC通道的参数。

Rank 是转换顺序,我们按1,2,3,4,5的顺序分别对应ADC1通道0,1,4,5,6。

多通道采样要开启扫描工作模式,在这里我们还有开启连续转换方式,连续转换是在ADC转换按照约定的转换顺序全部通道完成一次转换后,又自动启动下一次转换。

3、启用ADC转换DMA传输,多通道转换时要启用ADC的DMA传输,才能在相应的通道转换完成后,DMA自动去获取转换值。

中断方式没法在多通道采样时使用,因为在多通道扫描模式下,只有在最后一个通道转换结束时才会产生中断请求。

而ADC数据寄存器是共用的,这时候进入中断取值只能得到一个通道的数值。

4、到此,基础配置和ADC通道配置已经完成,接着我们设置工程名称和保存路径等就可以了,一般工程名和保存路径最好不要有中文,不然可能会出现一些意想不到的问题,在测试的过程中就遇到工程名或者保存路径中都用英文但是词组名称之间用空格隔开,在打开生成的工程文件后,向新建的分类文件夹中添加自己写的xxx.c文件,就导致keil软件卡死,不知道是keil软件还是cubemx的问题。

5、设置好工程名称和路径后就可以生成代码了,生成代码后我们选择打开工程。

接着我们开始编写代码(1)首先我们要修改main函数的一个错误,就是在初始化时要把MX_DMA_Init()函数放在MX_ADC1_Init()函数之前执行,cubemx生成代码时MX_DMA_Init()是在ADC初始化函数之后。

如果在后面则转换时打印输出的ADC值,大多数都为0,具体原因就不知道是怎么回事了,应该是cubemx这个版本还不太稳定。

STM32 ADC采样频率的确定

STM32 ADC采样频率的确定1. 先看一些资料,确定一下ADC 的时钟:(1)、由时钟控制器提供的ADCCLK 时钟和PCLK2(APB2 时钟)同步。

CLK 控制器为ADC时钟提供一个专用的可编程预分频器。

(2)、一般情况下在程序中将 PCLK2 时钟设为与系统时钟相同RCC_HCLKConfig(RCC_SYSCLK_Div1);RCC_PCLK2Config(RCC_HCLK_Div1);RCC_PCLK1Config(RCC_HCLK_Div2);(3)、在时钟配置寄存器(RCC_CFGR) 中有为ADC 时钟提供一个专用的可编程预分器。

位15:14 ADCPRE:ADC预分频由软件设置来确定ADC时钟频率00:PCLK2 2分频后作为ADC时钟01:PCLK2 4分频后作为ADC时钟10:PCLK2 6分频后作为ADC时钟11:PCLK2 8分频后作为ADC时钟我们可对其进行设置例如:RCC_ADCCLKConfig(RCC_PCLK2_Div4);另外ADC 时钟使能设置:RCC_APB2PeriphClockCmd(RCC_APB2Periph_ADC1| RCC_APB2Periph_ADC2 | RCC_APB2Periph_GPIOC, ENABLE);(4)、可编程的通道采样时间ADC 使用若干个ADC_CLK 周期对输入电压采样,采样周期数目可以通过ADC_SMPR1 和ADC_SMPR2 寄存器中的SMP[2:0]位而更改。

每个通道可以以不同的时间采样。

总转换时间如下计算:TCONV = 采样时间+ 12.5 个周期例如:当ADCCLK=14MHz 和1.5 周期的采样时间TCONV = 1.5 + 12.5 = 14 周期 = 1μsSMPx[2:0]:选择通道x的采样时间这些位用于独立地选择每个通道的采样时间。

在采样周期中通道选择位必须保持不变。

000:1.5周期 100:41.5周期001:7.5周期 101:55.5周期010:13.5周期 110:71.5周期011:28.5周期 111:239.5周期注:– ADC1的模拟输入通道16和通道17在芯片内部分别连到了温度传感器和VREFINT。

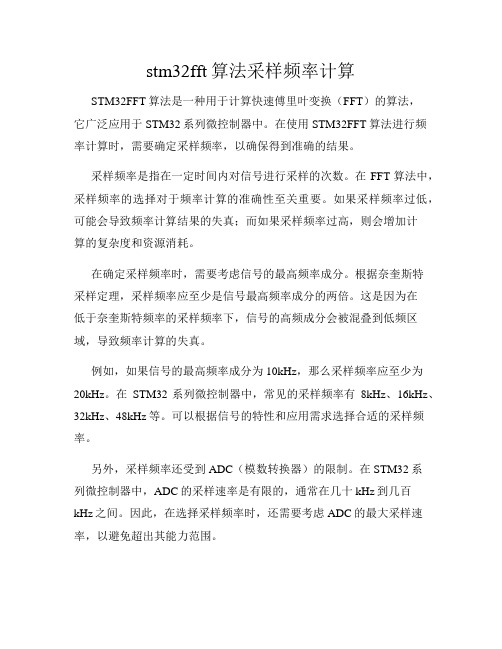

stm32fft算法采样频率计算

stm32fft算法采样频率计算STM32FFT算法是一种用于计算快速傅里叶变换(FFT)的算法,它广泛应用于STM32系列微控制器中。

在使用STM32FFT算法进行频率计算时,需要确定采样频率,以确保得到准确的结果。

采样频率是指在一定时间内对信号进行采样的次数。

在FFT算法中,采样频率的选择对于频率计算的准确性至关重要。

如果采样频率过低,可能会导致频率计算结果的失真;而如果采样频率过高,则会增加计算的复杂度和资源消耗。

在确定采样频率时,需要考虑信号的最高频率成分。

根据奈奎斯特采样定理,采样频率应至少是信号最高频率成分的两倍。

这是因为在低于奈奎斯特频率的采样频率下,信号的高频成分会被混叠到低频区域,导致频率计算的失真。

例如,如果信号的最高频率成分为10kHz,那么采样频率应至少为20kHz。

在STM32系列微控制器中,常见的采样频率有8kHz、16kHz、32kHz、48kHz等。

可以根据信号的特性和应用需求选择合适的采样频率。

另外,采样频率还受到ADC(模数转换器)的限制。

在STM32系列微控制器中,ADC的采样速率是有限的,通常在几十kHz到几百kHz之间。

因此,在选择采样频率时,还需要考虑ADC的最大采样速率,以避免超出其能力范围。

除了采样频率,还需要确定FFT的点数。

FFT的点数决定了频率分辨率,即能够分辨的最小频率间隔。

根据FFT的性质,频率分辨率等于采样频率除以FFT的点数。

例如,如果采样频率为20kHz,FFT的点数为1024,则频率分辨率为20kHz/1024≈19.53Hz。

在实际应用中,为了得到更准确的频率计算结果,可以选择较高的采样频率和较大的FFT点数。

然而,这也会增加计算的复杂度和资源消耗。

因此,需要在准确性和资源消耗之间进行权衡,选择合适的采样频率和FFT点数。

总之,STM32FFT算法是一种用于计算FFT的算法,在进行频率计算时需要确定采样频率。

采样频率的选择应考虑信号的最高频率成分、奈奎斯特采样定理和ADC的限制。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

STM32 ADC 采样频率的确定 嘿儿哈

2015/06/19 1. 先看一些资料,确定一下ADC 的 时钟:

(1)由时钟控制器提供的ADCCLK 时钟和PCLK2(APB2 时钟)同步。

CLK 控制器为ADC 时钟提供一个专用的可编程预分频器。

(2) 一般情况下在程序 中将 PCLK2 时钟设为 与系统时钟 相同

/* HCLK = SYSCLK */

RCC_HCLKConfig(RCC_SYSCLK_Div1);

/* PCLK2 = HCLK */

RCC_PCLK2Config(RCC_HCLK_Div1);

/* PCLK1 = HCLK/2 */

RCC_PCLK1Config(RCC_HCLK _Div2);

(3)在时钟配置寄存器(RCC_CFGR) 中 有 为ADC 时钟提供一个专用的可编程预分器

位15:14 ADCPRE :ADC 预分频

由软件设置来确定ADC 时钟频率

00:PCLK2 2分频后作为ADC 时钟

01:PCLK2 4分频后作为ADC 时钟

10:PCLK2 6分频后作为ADC 时钟

11:PCLK2 8分频后作为ADC 时钟

我们可对其进行设置 例如:

/* ADCCLK = PCLK2/4 */

RCC_ADCCLKConfig(RCC_PCLK2_Div4);

另外 还有 ADC 时钟使能设置

/* Enable ADC1, ADC2 and GPIOC clock */

RCC_APB2PeriphClockCmd(RCC_APB2Periph_ADC1 | RCC_APB2Periph_ADC2 |

RCC_APB2Periph_GPIOC, ENABLE);

(4)16.7 可编程的通道采样时间

ADC 使用若干个ADC_CLK 周期对输入电压采样,采样周期数目可以通过

ADC_SMPR1 和ADC_SMPR2 寄存器中的SMP[2:0]位而更改。

每个通道可以以

不同的时间采 样。

不同的时间采样。

总转换时间如下 计算:

TCONV = 采样时间+ 12.5 个周期

例如:

当ADCCLK=14MHz 和1.5 周期的采样时间

TCONV = 1.5 + 12.5 = 14 周期 = 1μs

ADCCLK=36MHz 和239.5 周期的采样时间

TCONV = 239.5 + 12.5 = 252周期 = 7μs

若你采样的是1KHz 的正弦波信号,采样了10000个点,则其中就有70个周期

SMPx[2:0]:选择通道x的采样时间

这些位用于独立地选择每个通道的采样时间。

在采样周期中通道选择位必须保持不变。

000:1.5周期100:41.5周期

001:7.5周期101:55.5周期

010:13.5周期110:71.5周期

011:28.5周期111:239.5周期

注:

– ADC1的模拟输入通道16和通道17在芯片内部分别连到了温度传感器和VREFINT。

– ADC2的模拟输入通道16和通道17在芯片内部连到了VSS。

2.具体分析如下:

(1)我们的输入信号是50Hz (周期为20ms),初步定为1周期200个采样点,(注:一周期最少采20个点,即采样率最少为1k),每2个采样点间隔为 20ms /200 = 100 us

ADC可编程的通道采样时间我们选最小的 1.5 周期,则 ADC采样周期一周期大小为

100us /1.5=66us 。

ADC 时钟频率为 1/66us =15 KHz。

ADC可编程的通道采样时间我们选71.5 周期,则 ADC采样周期一周期大小为

(100us /71.5)。

ADC 时钟频率为 7.15MHz。

(2)接下来我们要确定系统时钟:我们用的是 8M Hz 的外部晶振做时钟源(HSE),估计得经过 PLL倍频 PLL 倍频系数分别为2的整数倍,最大72 MHz。

为了提高数据计算效率,我们把系统时钟定为72MHz,(PLL 9倍频)。

则 PCLK2=72MHz,PCLK1=36MHz;

我们通过设置时钟配置寄存器(RCC_CFGR) 中有为ADC 时钟提供一个专用的可编程预分器,将PCLK2 8 分频后作为ADC 的时钟,则可知ADC 时钟频率为9MHz

从手册可知:ADC 转换时间:

STM32F103xx 增强型产品:ADC 时钟为56MHz 时为1μs(ADC 时钟为72MHz 为1.17μs)(3)由以上分析可知:不太对应,我们重新对以上中内容调整,提出如下两套方案:

方案一:我们的输入信号是50Hz (周期为20ms),初步定为1周期2500个采样点,(注:一周期最少采20个点,即采样率最少为1k),每2个采样点间隔为 20ms /2500 = 8 us ADC可编程的通道采样时间我们选71.5 周期,则 ADC采样周期一周期大小为

8us /71.5 。

ADC 时钟频率约为 9 MHz。

将PCLK2 8 分频后作为ADC 的时钟,则可知ADC 时钟频率为9MHz

方案二:我们的输入信号是50Hz (周期为20ms),初步定为1周期1000个采样点,(注:一周期最少采20个点,即采样率最少为1k),每2个采样点间隔为 20ms /1000= 20 us ADC可编程的通道采样时间我们选239.5周期,则 ADC采样周期一周期大小为

20us /239.5 。

ADC 时钟频率约为 12 MHz。

将PCLK2 6 分频后作为ADC 的时钟,则可知ADC 时钟频率为12MHz。