门电路 (简)资料

门电路74433

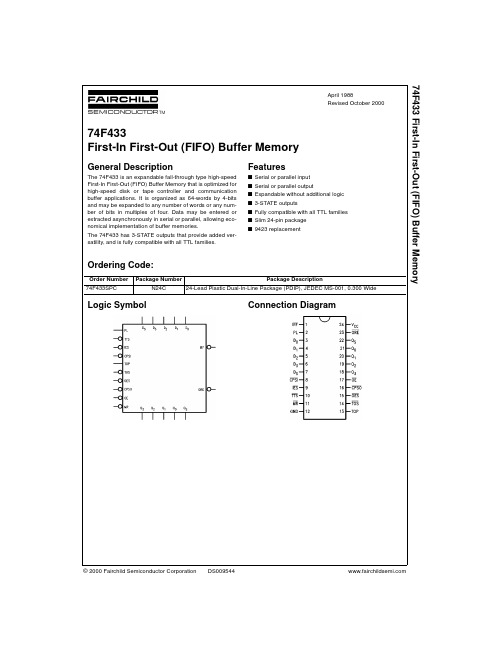

© 2000 Fairchild Semiconductor Corporation DS009544April 1988Revised October 200074F433 First-In First-Out (FIFO) Buffer Memory74F433First-In First-Out (FIFO) Buffer MemoryGeneral DescriptionThe 74F433 is an expandable fall-through type high-speed First-In First-Out (FIFO) Buffer Memory that is optimized for high-speed disk or tape controller and communication buffer applications. It is organized as 64-words by 4-bits and may be expanded to any number of words or any num-ber of bits in multiples of four. Data may be entered or extracted asynchronously in serial or parallel, allowing eco-nomical implementation of buffer memories.The 74F433 has 3-STATE outputs that provide added ver-satility, and is fully compatible with all TTL families.Featuress Serial or parallel input s Serial or parallel outputs Expandable without additional logic s 3-STATE outputss Fully compatible with all TTL families s Slim 24-pin package s 9423 replacementOrdering Code:Logic Symbol Connection DiagramOrder Number Package NumberPackage Description74F433SPCN24C24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide 274F 433Unit Loading/Fan OutBlock DiagramPin Names DescriptionU.L.Input I IH /I IL HIGH/LOW Output I OH /I OL PL Parallel Load Input 1.0/0.6620 µA/400 µA CPSI Serial Input Clock 1.0/0.6620 µA/400 µA IES Serial Input Enable 1.0/0.6620 µA/400 µA TTS Transfer to Stack Input 1.0/0.6620 µA/400 µA MR Master Reset 1.0/0.6620 µA/400 µA OES Serial Output Enable 1.0/0.6620 µA/400 µA TOP Transfer Out Parallel 1.0/0.6620 µA/400 µA TOS Transfer Out Serial 1.0/0.6620 µA/400 µA CPSO Serial Output Clock 1.0/0.6620 µA/400 µA OE Output Enable 1.0/0.6620 µA/400 µA D 0–D 3Parallel Data Inputs 1.0/0.6620 µA/400 µA D S Serial Data Input 1.0/0.6620 µA/400 µA Q 0–Q 3Parallel Data Outputs 285/10 5.7 mA/16 mA Q S Serial Data Output 285/10 5.7 µA/16 mA IRF Input Register Full 20/5400 µA/8 mA OREOutput Register Empty20/5400 µA/8 mA74F433Functional DescriptionAs shown in the block diagram, the 74F433 consists ofthree sections:1.An Input Register with parallel and serial data inputs,as well as control inputs and outputs for input hand-shaking and expansion.2. A 4-bit-wide, 62-word-deep fall-through stack with self-contained control logic.3.An Output Register with parallel and serial data out-puts, as well as control inputs and outputs for output handshaking and expansion.These three sections operate asynchronously and are vir-tually independent of one another.Input Register (Data Entry)The Input Register can receive data in either bit-serial or 4-bit parallel form. It stores this data until it is sent to the fall-through stack, and also generates the necessary status and control signals.This 5-bit register (see Figure 1) is initialized by setting flip-flop F 3 and resetting the other flip-flops. The Q-output ofthe last flip-flop (FC) is brought out as the Input Register Full (IRF) signal. After initialization, this output is HIGH.Parallel Entry —A HIGH on the Parallel Load (PL) input loads the D 0–D 3 inputs into the F 0–F 3 flip-flops and sets the FC flip-flop. This forces the IRF output LOW, indicating that the input register is full. During parallel entry, the Serial Input Clock (CPSI) input must be LOW.Serial Entry —Data on the Serial Data (D S ) input is serially entered into the shift register (F 3, F 2, F 1, F 0, FC) on each HIGH-to-LOW transition of the CPSI input when the Serial Input Enable (IES) signal is LOW. During serial entry, the PL input should be LOW.After the fourth clock transition, the four data bits are located in flip-flops F 0–F 3. The FC flip-flop is set, forcing the IRF output LOW and internally inhibiting CPSI pulses from affecting the register. Figure 2 illustrates the final posi-tions in an 74F433 resulting from a 256-bit serial bit train (B 0 is the first bit, B 255 the last).FIGURE 1. Conceptual Input Section 474F 433Functional Description (Continued)FIGURE 2. Final Positions in an 74F433Resulting from a 256-Bit Serial TrainFall-Through Stack —The outputs of flip-flops F 0–F 3 feed the stack. A LOW level on the Transfer to Stack (TTS) input initiates a fall-through action; if the top location of the stack is empty, data is loaded into the stack and the input register is re-initialized. (Note that this initialization is delayed until PL is LOW). Thus, automatic FIFO action is achieved by connecting the IRF output to the TTS input.An RS-type flip-flop (the initialization flip-flop) in the control section records the fact that data has been transferred to the stack. This prevents multiple entry of the same word into the stack even though IRF and TTS may still be LOW;the initialization flip-flop is not cleared until PL goes LOW.Once in the stack, data falls through automatically, pausing only when it is necessary to wait for an empty next location.In the 74F433, the master reset (MR) input only initializes the stack control section and does not clear the data.Output RegisterThe Output Register (see Figure 3) receives 4-bit data words from the bottom stack location, stores them, and out-puts data on a 3-STATE, 4-bit parallel data bus or on a 3-STATE serial data bus. The output section generates and receives the necessary status and control signals.Parallel Extraction —When the FIFO is empty after a LOW pulse is applied to the MR input, the Output Register Empty (ORE) output is LOW. After data has been entered into the FIFO and has fallen through to the bottom stack location, it is transferred into the output register, if the Transfer Out Parallel (TOP) input is HIGH. As a result of the data trans-fer, ORE goes HIGH, indicating valid data on the data out-puts (provided that the 3-STATE buffer is enabled). The TOP input can then be used to clock out the next word.When TOP goes LOW, ORE also goes LOW, indicating that the output data has been extracted; however, the data itself remains on the output bus until a HIGH level on TOP permits the transfer of the next word (if available) into the output register. During parallel data extraction, the serial output clock (CPSO) line should be LOW. The Transfer Out Serial (TOS) line should be grounded for single-slice oper-ation or connected to the appropriate ORE line for expanded operation (refer to the “Expansion ” section).The TOP signal is not edge-triggered. Therefore, if TOP goes HIGH before data is available from the stack but data becomes available before TOP again goes LOW, that data is transferred into the output register. However, internal control circuitry prevents the same data from being trans-ferred twice. If TOP goes HIGH and returns to LOW before data is available from the stack, ORE remains LOW, indi-cating that there is no valid data at the outputs.Serial Extraction —When the FIFO is empty after a LOW is applied to the MR input, the ORE output is LOW. After data has been entered into the FIFO and has fallen through to the bottom stack location, it is transferred into the output register, if the TOS input is LOW and TOP is HIGH. As a result of the data transfer, ORE goes HIGH, indicating that valid data is in the register.The 3-STATE Serial Data Output (Q S ) is automatically enabled and puts the first data bit on the output bus. Data is serially shifted out on the HIGH-to-LOW transition of CPSO. To prevent false shifting, CPSO should be LOW when the new word is being loaded into the output register.The fourth transition empties the shift register, forces ORE LOW, and disables the serial output, Q S . For serial opera-tion, the ORE output may be tied to the TOS input, request-ing a new word from the stack as soon as the previous one has been shifted out.ExpansionVertical Expansion —The 74F433 may be vertically expanded, without external components, to store more words. The interconnections necessary to form a 190-word by 4-bit FIFO are shown in Figure 4. Using the same tech-nique, any FIFO of (63n +1)-words by 4-bits can be config-ured, where n is the number of devices. Note that expansion does not sacrifice any of the 74F433 flexibility for serial/parallel input and output. 74F433Functional Description (Continued)FIGURE 3. Conceptual Output Section674F 433Functional Description(Continued)FIGURE 4. A Vertical Expansion SchemeHorizontal Expansion —The 74F433 can be horizontally expanded, without external logic, to store long words (in multiples of 4-bits). The interconnections necessary to form a 64-word by 12-bit FIFO are shown in Figure 5. Using the same technique, any FIFO of 64-words by 4n-bits can be constructed, where n is the number of devices.The right-most (most significant) device is connected to the TTS inputs of all devices. Similarly, the ORE output of the most significant device is connected to the TOS inputs of all devices. As in the vertical expansion scheme, horizontal expansion does not sacrifice any of the 74F433 flexibility for serial/parallel input and output.It should be noted that the horizontal expansion scheme shown in Figure 5 exacts a penalty in speed.Horizontal and Vertical Expansion —The 74F433 can be expanded in both the horizontal and vertical directions without any external components and without sacrificing any of its FIFO flexibility for serial/parallel input and output.The interconnections necessary to form a 127-word by 16-bit FIFO are shown in Figure 6. Using the same technique,any FIFO of (63m +1)-words by 4n-bits can be configured,where m is the number of devices in a column and n is the number of devices in a row. Figure 7 and Figure 8 illustrate the timing diagrams for serial data entry and extraction for74F433Functional Description (Continued)the FIFO shown in Figure 6. Figure 9 illustrates the final positions of bits in an expanded 74F433 FIFO resulting from a 2032-bit serial bit train.Interlocking Circuitry —Most conventional FIFO designs provide status signal analogous to IRF and ORE. However,when these devices are operated in arrays, variations in unit-to-unit operating speed require external gating to ensure that all devices have completed an operation. The 74F433 incorporates simple but effective 'master/slave'interlocking circuitry to eliminate the need for external gat-ing.In the 74F433 array of Figure 6, devices 1 and 5 are the row masters; the other devices are slaves to the master in their rows. No slave in a given row initializes its input regis-ter until it has received a LOW on its IES input from a row master or a slave of higher priority.Similarly, the ORE outputs of slaves do not go HIGH until their inputs have gone HIGH. This interlocking scheme ensures that new input data may be accepted by the array when the IRF output of the final slave in that row goes HIGH and that output data for the array may be extracted when the ORE output of the final slave in the output row goes HIGH.The row master is established by connecting its IES input to ground, while a slave receives its IES input from the IRF output of the next-higher priority device. When an array of 74F433 FIFOs is initialized with a HIGH on the MR inputs of all devices, the IRF outputs of all devices are HIGH.Thus, only the row master receives a LOW on the IES input during initialization.Figure 10 is a conceptual logic diagram of the internal cir-cuitry that determines master/slave operation. When MR and IES are LOW, the master latch is set. When TTS goes LOW, the initialization flip-flop is set. If the master latch is HIGH, the input register is immediately initialized and the initialization flip-flop reset. If the master latch is reset, the input register is not initialized until IES goes LOW. In array operation, activating TTS initiates a ripple input register ini-tialization from the row master to the last slave.A similar operation takes place for the output register.Either a TOS or TOP input initiates a load-from-stack oper-ation and sets the ORE request flip-flop. If the master latch is set, the last output register flip-flop is set and the ORE line goes HIGH. If the master latch is reset, the ORE output is LOW until a Serial Output Enable (OES) input is received.FIGURE 5. A Horizontal Expansion Scheme 874F 433Functional Description (Continued)FIGURE 6. A 127 x 16 FIFO ArrayFIGURE 7. Serial Data Entry for Array of Figure974F433Functional Description (Continued)FIGURE 8. Serial Data Extraction for Array of FigureFIGURE 9. Final Position of a 2032-Bit Serial InputFIGURE 10. Conceptual Diagram, Interlocking Circuitry 1074F 433Absolute Maximum Ratings (Note 1)Recommended Operating ConditionsNote 1: Absolute maximum ratings are values beyond which the device may be damaged or have its useful life impaired. Functional operation under these conditions is not implied.Note 2: Either voltage limit or current limit is sufficient to protect inputs.DC Electrical CharacteristicsStorage Temperature−65°C to +150°C Ambient Temperature under Bias −55°C to +125°C Junction Temperature under Bias −55°C to +150°C V CC Pin Potential to Ground Pin −0.5V to +7.0V Input Voltage (Note 2)−0.5V to +7.0V Input Current (Note 2)−30 mA to +5.0 mAVoltage Applied to Output in HIGH State (with V CC = 0V)Standard Output −0.5V to V CC 3-STATE Output −0.5V to +5.5VCurrent Applied to Output in LOW State (Max)twice the rated I OL (mA)Free Air Ambient Temperature 0°C to +70°CSupply Voltage+4.5V to +5.5VSymbol ParameterMin TypMaxUnits V CCConditionsV IH Input HIGH Voltage 2.0V Recognized as a HIGH Signal V IL Input LOW Voltage 0.8V Recognized as a LOW Signal V CD Input Clamp Diode Voltage −1.5VMin I IN = −18 mAV OHOutput HIGH 10% V CC 2.4VMinI OH = 400 µA (ORE, IRF)Voltage10% V CC 2.4I OH = 5.7 mA (Q n , Q s )5% V CC 2.7I OH = 400 µA (ORE, IRF)5% V CC2.7I OH = 5.7 mA (Q n , Q s )V OL Output LOW Voltage 10% V CC0.50V Min I OL = 16 mA (Q n , Q s )I IH Input HIGH Current 5.0µA Max V IN = 2.7V I BVI Input HIGH Current 7.0µA Max V IN = 7.0V Breakdown Test I CEX Output HIGH 50µA Max V OUT = V CC Leakage Current V ID Input Leakage 4.75V 0.0I ID = 1.9 µATestAll Other Pins Grounded I OD Output Leakage 3.75µA 0.0V IOD = 150 mVCircuit Current All Other Pins Grounded I IL Input LOW Current −0.4mA Max V IN = 0.5VI OZH Output Leakage Current 50µA Max V OUT = 2.7V (Q n , Q s )I OZL Output Leakage Current −50µA Max V OUT = 0.5V (Q n , Q s )I OS Output Short-Circuit Current −20−130mA Max V OUT = 0VI CCPower Supply Current150215mAMax74F433AC Electrical CharacteristicsSymbolParameterT A = +25°CT A = 0°C to +70°C UnitsFigure NumberV CC = +5.0V V CC = +5.0V C L = 50 pF C L = 50 pF MinMax Min Max t PHL Propagation Delay, Negative-Going 2.017.0 2.018.0nsFigures 11, 12CPSI to IRF Output t PLH Propagation Delay,9.034.08.038.0Negative-Going TTS to IRF t PLH Propagation Delay, Negative-Going 4.025.0 3.027.0ns Figures 13, 14t PHL CPSO to Q S Output5.020.0 5.021.0t PLH Propagation Delay, Positive-Going 8.035.07.038.0ns Figure 15t PHL TOP to Q 0–Q 3 Outputs 7.030.07.032.0t PHL Propagation Delay,7.025.0 6.028.0nsFigures 13, 14Negative-Going CPSO to ORE t PHL Propagation Delay,6.026.0 6.028.0nsFigure 15Negative-Going TOP to ORE t PLH Propagation Delay, Positive-Going 13.048.012.051.0TOP to OREt PLH Propagation Delay, Negative-Going 13.045.012.050.0nsFigures 13, 14TOS to Positive-Going ORE t PHL Propagation Delay, Positive- 4.022.0 4.023.0nsFigures 17, 18Going PL to Negative-Going IRF t PLH Propagation Delay, Negative-7.031.0 6.035.0Going PL to Positive-Going IRF t PLH Propagation Delay,9.038.08.044.0nsPositive-Going OES to ORE t PLH Propagation Delay Positive-IRF 5.025.0 5.027.0ns Figure 18Going IES to Positive-Going t PHL Propagation Delay 7.028.07.031.0ns MR to ORE t PLH Propagation Delay 5.027.0 5.030.0nsMR to IRF t PZH Enable Time 1.016.0 1.018.0nst PZL OE to Q 0–Q 3 1.014.0 1.016.0t PHZ Disable Time 1.010.0 1.012.0t PLZ OE to Q 0–Q 3 1.023.0 1.030.0t PZH Enable Time1.010.0 1.012.0nst PZL Negative-Going OES to Q S 1.014.0 1.015.0t PHZ Disable Time1.010.0 1.012.0t PLZ Negative-Going OES to Q S 1.014.0 1.016.0t PZH Enable Time 1.035.0 1.042.0ns t PZL TOS to Q S1.035.0 1.039.0t DFT Fall-Through Time 0.20.90.2 1.0nsFigure 16t AP Parallel Appearance Time −20.0−2.0−20.0−2.0nsORE to Q 0–Q 3t ASSerial Appearance Time −20.05.0−20.05.0ORE to Q S 1274F 433AC Operating RequirementsSymbol ParameterT A = +25°CT A = 0°C to +70°C UnitsFigure NumberV CC = +5.0V V CC = +5.0V Min MaxMin Maxt S (H)Setup Time, HIGH or LOW 7.07.0nsFigures 11, 12t S (L)D S to Negative CPSI 7.07.0t H (H)Hold Time, HIGH or LOW 2.0 2.0t H (L)D S to CPSI2.02.0t S (L)Setup Time, LOW TTS to IRF,0.00.0nsFigures 11, 12, 17,18Serial or Parallel Modet S (L)Setup Time, LOW Negative-Going 0.00.0nsFigures 13, 14ORE to Negative-Going TOS t S (L)Setup Time, LOW Negative-Going 8.09.0nsFigure 12IES to CPSIt S (L)Setup Time, LOW Negative-Going 30.033.0TTS to CPSIt S (H)Setup Time, HIGH or LOW 0.00.0nst S (L)Parallel Inputs to PL 0.00.0t H (H)Hold Time, HIGH or LOW 4.0 4.0t H (L)Parallel Inputs to PL 4.0 4.0t W (H)CPSI Pulse Width 10.011.0ns Figures 11, 12t W (L)HIGH or LOW 5.0 6.0t W (H)PL Pulse Width, HIGH 7.09.0ns Figures 17, 18t W (L)TTS Pulse Width, LOW 7.09.0ns Figures 11, 12, 13,14Serial or Parallel Modet W (L)MR Pulse Width, LOW 7.09.0ns Figure 16t W (H)TOP Pulse Width 14.016.0nsFigure 15t W (L)HIGH or LOW 7.07.0t W (H)CPSO Pulse Width 14.016.0ns Figures 13, 14t W (L)HIGH or LOW 7.07.0t RECRecovery Time 8.015.0nsFigure 16MR to Any Input74F433Timing WaveformsConditions: Stack not full, IES, PL LOWFIGURE 11. Serial Input, Unexpanded or Master OperationConditions: Stack not full, IES HIGH when initiated, PL LOWFIGURE 12. Serial Input, Expanded Slave OperationConditions: Data in stack, TOP HIGH, IES LOW when initiated, OES LOWFIGURE 13. Serial Output, Unexpanded or Master Operation 1474F 433Timing Waveforms (Continued)Conditions: Data in stack, TOP HIGH, IES HIGH when initiatedFIGURE 14. Serial Output, Slave OperationConditions: IES LOW when initiated, OE, CPSO LOW; data available in stackFIGURE 15. Parallel Output, 4-Bit Word or Master in Parallel ExpansionConditions: TTS connected to IRF, TOS connected to ORE, IES, OES, OE, CPSO LOW, TOP HIGHFIGURE 16. Fall Through Time74F433Timing Waveforms (Continued)Conditions: Stack not full, IES LOW when initializedNOTE A: TTS normally connected to IRF.NOTE B: If stack is full, IRF will stay LOW.FIGURE 17. Parallel Load Mode, 4-Bit Word (Unexpanded) or Master in Parallel ExpansionConditions: Stack not full, device initialized (Note 3) with IES HIGHNote 3: Initialization requires a master reset to occur after power has been applied.FIGURE 18. Parallel Load, Slave Mode1674F 433 F i r s t -I n F i r s t -O u t (F I F O ) B u f f e r M e m o r yPhysical Dimensions inches (millimeters) unless otherwise noted24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 WidePackage Number N24CFairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.LIFE SUPPORT POLICYFAIRCHILD ’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:1.Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be rea-sonably expected to result in a significant injury to the user. 2. A critical component in any component of a life support device or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.。

74LS175门电路资料

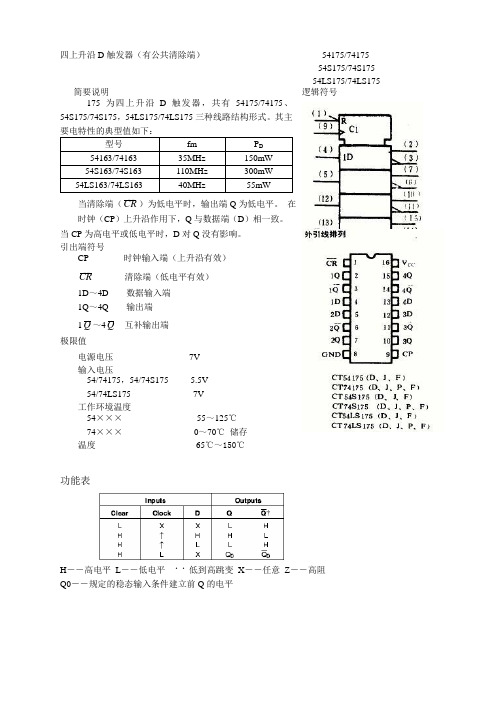

四上升沿D 触发器(有公共清除端)54175/7417554S175/74S17554LS175/74LS175逻辑符号简要说明175 为四上升沿 D 触发器,共有54175/74175 、54S175/74S175,54LS175/74LS175 三种线路结构形式。

其主要电特性的典型值如下:型号fm P D54163/7416335MHz150mW54S163/74S163110MHz300mW54LS163/74LS16340MHz55mW当清除端(CR )为低电平时,输出端Q 为低电平。

在时钟(CP)上升沿作用下,Q 与数据端(D)相一致。

当CP 为高电平或低电平时,D 对Q 没有影响。

引出端符号CP 时钟输入端(上升沿有效)CR 清除端(低电平有效)1D~4D 数据输入端1Q~4Q 输出端1 Q ~4 Q 互补输出端极限值电源电压7V输入电压54/74175,54/74S175 5.5V54/74LS175 7V工作环境温度54×××-55~125℃74×××0~70℃储存温度-65℃~150℃功能表H――高电平L――低电平‘‘低到高跳变X――任意Z――高阻Q0――规定的稳态输入条件建立前Q 的电平54/7417554/74S17554/74LS175单位最小额定最大最小额定最大最小额定最大电源电压V CC54 4.55 5.5 4.55 5.5 4.55 4.5V74 4.755 5.25 4.755 5.25 4.755 5.25输入高电平电压V iH222V输入低电平电压V iL 540.80.80.7V 740.80.80.8输出高电平电流I OH-800-1000-400uA 输出低电平电流I OL5416304mA 7416308时钟频率fcp025075030MHz 脉冲宽度T W CP20725ns CR201020ns建立时间t setD20520ns CR 无效态25520ns保持时间t H530ns 逻辑图[2]: fmax 最大时钟频率。

逻辑门电路原理

逻辑门电路原理

逻辑门电路是由逻辑门元件(比如与门、或门、非门等)组成的电路,用于实现不同逻辑功能的处理。

逻辑门电路的原理是基于布尔代数的原理,通过输入信号的组合,产生特定的输出信号。

与门是逻辑门电路中最简单的一种。

它有两个输入端和一个输出端。

当两个输入同时为高电平(1)时,输出才为高电平(1),否则输出为低电平(0)。

与门电路可以用晶体管来实现。

其中,两个输入信号接通到两个晶体管的基极,输出信号从两个晶体管的发射极中获取。

或门是逻辑门电路中另一种常见的门电路。

它也有两个输入端和一个输出端。

当两个输入中至少一个为高电平(1)时,输出就为高电平(1),只有当两个输入都为低电平(0)时,输出为低电平(0)。

或门电路可以通过将两个输入信号连接到两个晶体管的集电极,输出从两个晶体管的发射极中获取来实现。

非门是逻辑门电路中最简单的一种反转门电路。

它只有一个输入端和一个输出端。

当输入为高电平(1)时,输出为低电平(0),反之亦然。

非门电路可以通过一个晶体管来实现,输入信号通过晶体管的基极,输出来自晶体管的发射极。

逻辑门电路的原理基于布尔代数,通过在输入信号之间的逻辑运算,实现特定的逻辑功能。

在电子数位系统中,逻辑门电路被广泛应用于数字电路中,如计算机、电子器件等。

它们可以

实现逻辑运算、信号控制、数据存储等功能,是现代电子设备中不可或缺的一部分。

74LS系列门电路资料

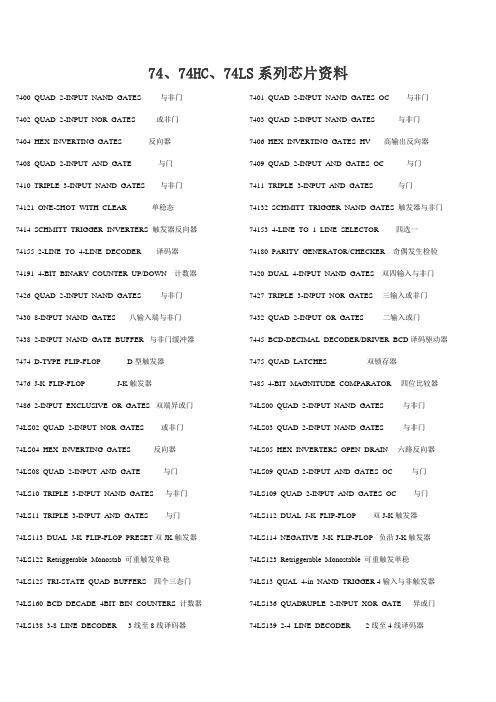

74LS283 4BIT BINARY ADDER CARRY四位加法器

74LS30 8-INPUT NAND GATES八输入端与非门

74LS32 QUAD 2-INPUT OR GATES二输入或门

74LS352 4-1 LINE SELECTOR/MUX 4-1线选择多路器

74LS256 4BIT ADDRESS LATCH四位可锁存锁存器

74LS257 QUAD 2-CH 3-STATE MUX 4路3态多路器

74LS258 2-CH 3-STATE MUX 2路3态多路器

74LS27 TRIPLE 3-INPUT NOR GATES三输入或非门

74LS279 QUAD R-S LATCHES四个RS非锁存器

74LS139 2-4 LINE DECODER 2线至4线译码器

74LS14 TRIGGERED HEX INVERTER六触发反向器

74LS151 8-CHANNEL DIGITAL MUX 8通道多路器

74LS153 DUAL 4-INPUT MUX双四输入多路器

74LS155 2-4 LINE DECODER 2线至4线译码器

74LS125 TRI-STATE QUAD BUFFERS四个三态门

74LS13 QUAL 4-in NAND TRIGGER 4输入与非触发器

74LS160 BCD DECADE 4BIT BIN COUNTERS计数器

74LS136 QUADRUPLE 2-INPUT XOR GATE异或门

74LS138 3-8 LINE DECODER 3线至8线译码器

74LS365 HEX 3-STATE BUFFER六个三态缓冲门

门电路和组合逻辑电路

二进制:0,1两个数码,“逢二进一”。

N进制数可用 十进制数可用

权

N KiNi 表示;

基数

i 第 位系数

D Ki1i0表示;

二进制数可用

B Ki2i 表示;

如: ( 1 0 1 . 1 1 ) 2 1 2 2 0 2 1 1 2 0 1 2 1 1 2 2

二进制与十进制间的转换

门电路和组合逻辑电路

本章要求:

第6章 门电路和组合逻辑电路

1. 掌握基本门电路的逻辑功能、逻辑符号、真值 表和逻辑表达式。

2. 会用逻辑代数的基本运算法则化简逻辑函数。 3. 会分析和设计简单的组合逻辑电路。 4. 理解加法器、编码器、译码器等常用组合逻辑

电路的工作原理和功能。

5. 学会数字集成电路的使用方法。

2 13

余 1 (d1)

26

余 0 (d2)

23

余 1 (d3 )

21

余 1 (d4 )

0

(2)D 7(d4d3d2d1 d0)B(11)B 011

6.2 基本门电路及其组合 6.2.1 逻辑门电路的基本概念

逻辑门电路是数字电路中最基本的逻辑元件。 所谓门就是一种开关,它能按照一定的条件去控制信号的通过或不通过。 门电路的输入和输出之间存在一定的逻辑关系(因果关系),所以门电路又称为逻辑门电路。

TTL门电路芯片简介 如: 74LS00(四2输入与非门 )

UCC

14

13

12

11

10

9

8

&

&

&

&

1

2

3

4

5

6

7

GND

管脚

名称

基本逻辑门电路符号和口诀【最新资料】

无论多么复杂的单片机电路,都是由若干基本电路单元组成的。

2.2.1 常用的逻辑门电路最基本的门电路是与、或、非门,把它们适当连接可以实现任意复杂的逻辑功能。

用小规模集成电路构成复杂逻辑电路时,最常用的门电路是与(AND)、或(OR)、非(INV BUFF)、恒等(BUFF)、与非(NAND)、或非(NOR)、异或(XOR)。

主要是因为这7种电路既可以完成基本逻辑功能,又具有较强的负载驱动能力,便于完成复杂而又实用的逻辑电路设计。

1.与门与门是一个能够实现逻辑乘运算的、多端输入、单端输出的逻辑电路,逻辑函数式:F = A·B其记忆口诀为:有0出0,全1才1。

2.或门或门是一个能够实现逻辑加运算的多端输入、单端输出的逻辑电路,逻辑函数式:F = A+B其记忆口诀为:有1出1,全0才0。

3.非门实现非逻辑功能的电路称为非门,有时又叫反相缓冲器。

非门只有一个输入端和一个输出端,逻辑函数式是:F =A非非门逻辑符号4.恒等门实现恒等逻辑功能的电路称为恒等门,又叫同相缓冲器。

恒等门只有一个输入端和一个输出端,逻辑函数式是:F = A同相缓冲器和反相缓冲器在数字系统中用于增强信号的驱动能力。

5.与非门与和非的复合运算称为与非运算,逻辑函数式是:F = A.B非其记忆口诀为:有0出1,全1才0。

6.或非门或与非的复合运算称为或非运算,逻辑函数式是:F = A+B非其记忆口诀为:有1出0,全0才1。

7.异或门异或逻辑也是一种广泛应用的复合逻辑,其记忆口诀为:相同出0,不同出1。

逻辑门电路是单片机外围电路运算、控制功能所必需的电路。

在单片机系统中我们经常使用集成逻辑电路(常称为集成电路)。

一片集成逻辑门电路中通常含有若干个逻辑门电路,如7400为4重二输入与非门,即7400内部有4个二输入的与非门。

高速CMOS74HC逻辑系列集成电路具有低功耗、宽工作电压、强抗干扰的特性,是单片机外围通用集成电路的首选系列。

【资料】逻辑门电路(精)汇编

D

G S

N增强型

D

D

G

G

S P耗尽型

S N耗尽型

场效应管与晶体管的比较

双极型三极管

单极型场效应管

载流子

控制方式

类型

放大参数 输入电阻

输出电阻 热稳定性 制造工艺 对应电极

电子和空穴两种载 流子同时参与导电

电流控制

NPN和PNP

20~200

102 ~104较低

rce很大

差 较复杂 B—E—C

电子或空穴中一种 载流子参与导电

电压控制 N沟道和P沟道

gm 1~5mA/V

107 ~11 04较高

rds很大

好 简单,成本低

G—S—D

§3.3 集成门电路

◆ 集成逻辑门主要有CMOS系列和TTL系列两大类, 目前CMOS系列已成为占主导地位的逻辑器件。

◆ CMOS(Complementary Metal Oxide Semiconductor, 互补金属氧化物半导体)系列集成逻辑门电路由 NMOS管和PMOS管构成。

噪声容限值越大,抗干扰能力越强。

vO

1

vI

1

驱动门

负载门

VDD VOH(min)

VNH

• 输入高电平噪声容限: VNH=VOH(min)-VIH(min)

VIH(min)

VIL(max)

VNL

VOL(max)

• 输入低电平噪声容限: VNL=VIL(max)-VOL(max)

三、扇入、扇出系数

前后级之间电流的联系。

解:1)NOH=IOH/IIH=4/0.02=200 NOL=IOL/IIL=4/0.4=10

则,扇出系数为10。

第6部分逻辑门电路-

NMOS电路。由N沟道MOS管构成,制造工 艺复杂,但工作速度优于PMOS电路。

33

2019/10/26

CMOS电路。由PMOS管和NMOS管构成的互补对称型 MOS电路,优点是静态功耗低、抗干扰能力强、工作 稳定性好、开关速度较高。虽然制作工艺相对复杂、成 本偏高,但由于其优点突出,是现在发展最快、应用广 泛的一种集成电路。

34

2019/10/26

6.3.1 常见CMOS门电路

1. CMOS与非门 高速CMOS集成电路54/74HC00为四2输入与非门,

即内部集成了四个2输入与非门,

35

2019/10/26

36

2019/10/26

2. CMOS或非门 高速CMOS集成电路54/74HC02为2输入四或非门。

37

2019/10/26

砷、锑等)。 杂质原子的五个价电子与周围硅原子组成共价键时,

多出一个价电子,使晶体产生一个自由电子。 根据掺入杂质的多少,可以控制自由电子的数量。

由于自由电子的数量远远大于空穴的数量,这种半导体 导电以自由电子导电为主。将自由电子称为多数载流子, 简称多子;空穴称为少数载流子,简称少子。

9

2019/10/26

(1)电源规则 电源极性不能接反,否则将会造成集成电路的

永久损坏。另外,电源电压应保持在最大极限电压范 围之内。电源电压越高,电路抗干扰能力就越强,允 许的工作频率就越高,但功耗会相应增大。

43

2019/10/26

(2)输入规则 与TTL门电路不同,CMOS门电路的多余输入端禁

止悬空,而应采取如下措施: ①多余的与输入端接VDD或高电平。 ②多余的或输入端接VSS或低电平,也可以通过电

逻辑门电路PPT课件

IC(Integrated Circuits):将元、器件制作在同一硅片上, 以实现电路的某些功能。 SSI(Small-Scale Integration): 10个门电路。 MSI(Medium-Scale Integration):10~100个门电路。 LSI(Large-Scale Integration):1000~10000个门电路。 VLSI(Very Large-Scale Integration): 10000个门电路。

VT5

集成门电路——TTL与非门电路

可以线与的TTL门电路

TSL门电路除正常输入端A、B,输出端F外,增加了控制端口C,

C=1,电路完成正常与非功能;C=0时,输出端对地呈现高阻状态。

将C称为控制端或使能端。三态门的基本用途是在数字系统中构成

总线(Bus)。

a.单向总线。

b.双向总线。

G1

G1

总线

单极型集成逻辑门电路:集成逻辑门是以单极型晶体管(只有一 种极性的载流子:电子或空穴)为基础的。目前应用得最广泛的 是金属—氧化物—半导体场效应管逻辑电路(Metal Oxide Semiconductor, MOS)。

集成门电路——概 述

衡量门电路的性能指标

1.传输延迟时间(Transmission Delay Time) 2.功耗(Power Dissipation) 3.逻辑电平(Logic Level) 4.阈值电压(Threshold Voltage) 5.噪声容限(Noise Margin) 6.扇入(Fan—In),扇出(Fan—Out) 7.工作温度范围(Operating Temperature Range)

集成门电路——TTL与非门电路

半导体器件开关特性及分立元器件门电路

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

或门等。

门电路的两种输入,输出电平: 高电平、低电平。它们分别对应逻 辑电路的1,0状态。

注意:各种门电路的工作 原理,只要求一般掌握; 而各种门电路的外部特性 和应用是要求重点。

3.1 概述

2. 高低电平

高电平:数字电路中较高电平代数值的范围。

低电平:数字电路中较低电平代数值的范围。

3. 正负逻辑

3.2 半导体二极管门电路

门电路的实现 ——电子开关,用来接通或断开电路的开关器件。 1. 半导体二极管的开关特性

两种工作状态: 二极管具有单向导电性:

正向导通,反向截止,相当于一个受电压控制的 1)接通(要求其阻抗很小,相当于短路) 电子开关。 2 )断开(要求其阻抗很大,相当于开路)

3.2 半导体二极管门电路

当EN= 0时,TG导通,F=A; 当EN= 1时,TG截止,F为高阻输出。

3.3 CMOS门电路

CMOS系列及命名方法

74 FAM nn

HC( High-speed CMOS ,高速 CMOS 系列); 例: 74HC04商用高 HCT(High-speed CMOS, 前缀:74—商用系列;54—军用系列。 速CMOS 六反相 TTL compatible ,与 TTL兼 容的高速CMOS 系列); 助记符:以字母表示系列类型。 器; VHC(Very High-speed CMOS,甚高速 CMOS商用 系 74HCT00 功能数字:以数字表示电路的 列); 高速 CMOS 四 -二 VHCT: Very High-speed 逻辑功能。 CMOS, TTL compatible,与 输入与非门。 TTL兼容的甚高速CMOS 系 列)。

层做包装材料。

3.3 CMOS门电路

多余或暂时不用的输入端的处理

(1)多余或暂时不用的输入端的不能悬空;

CMOS反相器

PMOS管

A 0 1

Z 1 0

ZA

A

Z

NMOS管

工作特点: TP 和 VTN 总是 一管导通而另一管截止,流 过VTP和 VTN的静态电流极小 (纳安数量级)。 因而CMOS反相器的静态 功 耗 极 小 。 这 是 CMOS 电 路 最突出的优点之一。

3.3 CMOS门电路

CMOS与非门

数字电子技术

贺付亮 电子信息工程学院 fulighter@

Southwestern University

第三章 门电路

1

2 3

半导体二极管门电路

CMOS门电路

TTL门电路

4

CMOS与TTL之间接口电路

3.1 概述

1. 门电路

是用以实现逻辑关系的电子电路,与基本逻辑关系相

对应。 门电路主要有:与门、或门、与非门、或非门、异

正逻辑:用高电平代表1、低点平代表0。(数字电路中采用)

负逻辑:用高电平代表0、低点平代表1。

v

VH

正

VH

VL 1

VL

低电平 t t

3.1 概述

4. 集成电路

IC(Integrated Circuits):将元、器件制作在同一硅片上,

以实现电路的某些功能。 集成电路的优点:体积小、 1961 年美国德克萨斯仪器 重量轻、可靠性高,功耗 SSI(Small-Scale Integration): 10 个门电路。 公司首先制成集成电路。 低。目前单个集成电路上 MSI(Medium-Scale Integration): 10~100 个门电路。 英文 Integrated Circuit, 已能作出数千万个三极管, 简称IC。 个门电路。 而其面积只有数十平方毫 LSI(Large-Scale Integration):1000~10000 米。 VLSI(Very Large-Scale Integration): 10000个门电路。

3.3 CMOS门电路

CMOS三态门

Three-state gate是 一种重要的总线接口 电路。 三态: 指其输出既可 以是一般二值逻辑电 路的正常的高电平或 低电平,又可以保持 特有的高阻抗状态 (Hi-Z)。 处于高阻抗状态时, 输出电阻很大,相当 于开路,没有任何逻 辑控制功能。 高阻态的意义:实际 电路中在不断开电路 下实现功能性断开。

A B Q1 Q2 Q3 Q4 Z VDD Q2 A B Z Q1 Q3 Q4 Z

L L H H

A 0 0 1 1

L H L H

B 0 1 0 1

off off on on

Z 1 1 1 0

on on off off

off on off on

on off on off

H H H L

Z AB

A B

2. 二极管与门 3. 二极管或门

由于这些电 路有严重的 缺点,在集 成电路中并 不使用,但 可帮助理解 集成门的工 作原理。

A B

Y

3.3 CMOS门电路

MOS门电路:以MOS管作为开关元件构成的门电路。 MOS 管 有 NMOS 管 和 PMOS 管 两 种 。 当 NMOS 管 和 PMOS 管成对出现在电路中,且二者在工作中互补,称为

CMOS 管 ( 意为互补 ) 。 MOS 管有增强型和耗尽型两种。在

数字电路中,多采用增强型。

3.3 CMOS门电路

MOS门电路特点:对比TTL门电路

1、控制信号:TTL为电流控制器件,MOS属于电压控制器件。

2、电路极性: TTL为双极性电路, MOS属于单极性电路。 双极性电路:电源电压对地为正,只有正逻辑;

前缀

系列助记符

功能数字

3.3 CMOS门电路

CMOS电路的使用注意事项

输入电路的静电保护 CMOS 电路的输入端设置了保护电路,给使用者带

来很大方便。但是,这种保护还是有限的。应注意以下几 点: (1)所有与CMOS电路直接接触的工具、仪表等必 须可靠接地。 ( 2 )存储和运输 CMOS 电路,最好采用金属屏蔽

单极性电路:包括正、负两种逻辑 。

3、功耗问题:TTL功耗大(1~5mA/门), MOS管功耗较低。 4、驱动能力: MOS管常用来电源开关,以及大电流地方开关电路。 5、逻辑电平范围:MOS电路高低电平相差大,抗干扰强,逻辑电平 范围在(5~15V);TTL电路高低电平相差小,只能在5V下工作。

3.3 CMOS门电路