QUARTUS使用及原理图设计

Quartus原理图输入法指南

6

二、形成原理图设计文件

1、建立原理图设计文件 从菜单File→New进入,在6种设计输入法中选择原理图输 入法,单击OK,即可进入原理图编辑器

提 示 : 硬 件 实 验 课 程 要 求 如 此

7

2、编辑原理图设计文件 ⑴元件的选择与放置 *可在Symbol对话框中选择元件,单击OK

提示: *弹出Symbol方法:双 击鼠标左键、工具条… *元件库包含系统库和 Project库两类 *Project库由用户自定 义符号文件(.bsf)组成 *亦可在编辑区用Copy 及Paste命令实现选择

*在编辑区可移动元件,放置到合适的位置管脚类型,使工具箱相应连接线有效 *在源处按下鼠标左键、移至目标处、松开鼠标左键即可

提示: *连接线有3种:Node、 Bus、Conduit *所连接的源端、目标 端元件管脚类型应相同 *应避免移动元件时产 生多余交叉点 *工具箱有多种功能

提示: 修改原理图文件 后,必须重新编译、 生成仿真网表

19

⑵进行功能仿真 *在对话框的Simulator input中输入仿真波形文件名 *在对话框中单击Start,即可开始功能仿真 *在对话框中单击Report,可查看、核对输出波形

20

五、对原理图设计文件进行硬件测试

1、器件设置及引脚锁定

⑴器件设置 [该步骤可缺省] *从菜单Assignments→Device进入,可重新选择器件 *单击Device & Pin Options…,可配置Unused Pins状态等

提示: 有多种方法 触发编译开始

*编译结束时,会报告警告或错误的统计情况 *编译出错时,按Message提示修改错误,直至编译通过

13

四、对原理图设计文件进行时序仿真

数字电路Quartus_II_原理图输入法设计

数字电路与逻辑设计实验报告实验1 Quartus II 原理图输入法设计一、实验目的1)熟悉用Quartus II原理图输入法进行电路设计和仿真2)掌握Quartus II图形模块的生成和调用3)熟悉实验板的使用二、实验仪器和器件1)计算机2)直流稳压电源3)数字电路与逻辑设计实验开发板三、实验内容1)用逻辑门设计实现一个半加器,仿真验证其功能,并生成新的半加器图形模块单元。

2)用实验内容1中生成的半加器模块和逻辑门实现一个全加器,仿真验证其功能,并下载到实验板测试,要求用拨码开关设定输入信号,发光二极管显示输出信号四、设计过程1.设计半加器:可知半加器函数S = A⊕B,C = AB。

故设计为然后点击File ->Save As, 找到要保存的文件夹,Add file to current project前面的“√”,再选择File -> Create/Update -> Create Files for Current File 将创建半加器的模块bsf文件储存在工程目录内,方便下次调用。

2.设计全加器:在原目录下新建工程,创建原理图,直接导入半加器模块,将两个半加器组合附加2输入或门组成全加器,如图:五、实验过程1.按照以上工程创建工程和原理图2.编译原理图,修正错误,使编译通过3.创建waveform vector仿真文件,将所有原理图输入、输出引脚添加至列表。

设置合适的仿真结束时间,对输入变量设置合适的仿真时钟周期。

开始仿真,得到实验的仿真波形:1)半加器:真值表:输入输出A B S C0 0 0 00 1 1 01 0 1 01 1 0 1半加器仿真波形:波形满足S = A⊕B,C = AB,逻辑正确。

2)全加器:真值表:输入输出a b ci co s0 0 0 0 00 0 1 0 10 1 0 0 10 1 1 1 01 0 0 0 11 0 1 1 01 1 0 1 01 1 1 1 1全加器仿真波形:波形满足函数:co = (a⊕b)ci + ab,s = a⊕b⊕ci,逻辑无错。

QuartusII开发原理图+

2.1 Quartus Ⅱ软件简介

➢ 输出系统测试组件。 ➢ 输出生成系统基于存储器映射和组成的

定制软件开发套件(SDK)。 SOPC Builder使设计者能够集中精力 在用户逻辑设计上,无需手工完成系统 集成任务从而提升了系统性能。

2.1 Quartus Ⅱ软件简介

3.在设计周期的早期就对IO引脚进行 分配和确认 QuartusⅡ软件可以进行预先的I/

2.2.2 用原理图方法设计2-4译码器

图2.14 摆放好所有元器件 (3)连接各元器件并命名,有节点标识

2.2.2 用原理图方法设计2-4译码器

原理图和图表模块编辑时所用到的工 具按钮,如图2.15所示。熟悉这些工具的 基本性能,可以大大提高设计速度。

图2.15 编辑工具按钮

2.2.2 用原理图方法设计2-4译码器

2.2.2 用原理图方法设计2-4译码器

图2.9 器件类型设置

2.2.2 用原理图方法设计2-4译码器

(4) 结束设置 单击图2.8中的“Next”按钮后进入

最后确认的对话框,如图2.9所示。从图 中可以看到建立的工程名称、选择的器 件等信息,如果无误的话,单击 “Finish”按钮,出现如图2.10所示的 窗口,在资源管理窗口中可以看到新建 的名称“2_4decoder”工程。

图2.22 列出输入/输出节 点

2.2.2 用原理图方法设计2-4译码器

(3) 在图2.22界面中单击“>>”按钮, 则将所有输入/输出复制到右边的一侧。也 可以只选择其 中的一部分, 根据情况而定, 如图2.23所示。

图2.23 选择输入/输出节点

2.2.2 用原理图方法设计2-4译码器

(4) 在图2.23界面中单击“OK”按钮 后,返回“Inter Node or Bus”对话框。 此时,在“Name”和“Type”栏里出现了 “Multiple Items”,如图2.24所示。

FPGA轻松学习用QuartusII通过原理图完成与门电路设计

FPGA轻松学习用QuartusII通过原理图完成与门电路设计打开QuartusII软件,程序主界面如下:1,新建一个工程点击File——>New Project Wizard,打开创建新工程向导,这里你将完成工程的基本设定选项。

1,Project name and directory——工程的名称与目录2,Name of the top-level design entity——顶层设计实体的名称3,Project files and libraries——项目文件与库4,Target device family and device——目标设备的族类5,EDA tool settings——EDA工具设定这里一般设定好工程名称和目录,顶层设计实体名称以及目标设备族类就可以了,其他的暂时直接使用默认项就可以了。

2,新建一个设计文件通过点击File——>New打开新建文件选择框,由于我们这里使用原理图描述实现的,则文件类型选择Design Files——>Block Diagram/Schematic File,就新建了一个原理图文件,将其保存起来,注意命名要跟前面设置的顶层设计实体名称相同。

3,编写设计文件接下来开始在文件中绘制原理图,这里首先完成与门的添加,点击左侧工具栏中的Symbol Tool按钮,打开Symbol选择框,选择primitives——>logic——>and2,点击OK后即可在原理图中添加一个2输入的与门了。

在同样通过Symbol Tool中的加入和primitives——>pin——>output加入输入和输出引脚,然后在原理图中把他们用Orthogonal Node Tool即导线连接起来,双击输入输出引脚,为他们设定好名字,pinA,pinB,pinC,就完成了原理图中的设计。

4,编译(分析综合)点击Processing——>Start——>Start Analysis & Synthesis,进行分析综合,就好像是对程序进行编译,等待片刻,如果没有错误,编译报告会输出出来。

QuartusII及其原理图设计

QuartusII及其原理图设 计

3

QUARTUS II 设计开发流程

QuartusII及其原理图设 计

4

QUARTUS II 文件格式介绍

QuartusII及其原理图设 计

5

QUARTUS II –图表和原理图编辑器

QuartusII及其原理图设 计

25

QUARTUS II –原理图设计例子

QuartusII及其原理图设 计

26

QUARTUS II –原理图设计例子

QuartusII及其原理图设 计

27

QUARTUS II –原理图设计例子

QuartusII及其原理图设 计

28

QUARTUS II –原理图设计例子

QuartusII及其原理图设 计

41

编译注意

要查找器件的资料,确保管脚定义,及其管脚工作状态 注意总线的画法和定义

注意同步清零和异步清零的方法

QuartusII及其原理图设 计

42

QUARTUS II –习题一

1-3 基于Quartus II软件,用部分积右移方式设计实现一个 4位二进制乘法器,选择合适的器件,画出电路连接

QuartusII及其原理图设 计

47

QUARTUS II –习题一

1-9 用D触发器构成按循环码(000-001-011-111-101100-000)规律工作的六进制同步计数器。 1-10 用74194、74273、D触发器等器件组成8位串入并 出的转换电路,要求在转换过程中数据不变,只有当8位一 组数据全部转换结束后,输出才变化一次。

QuartusII原理图设计

QuartusII原理图设计一.实验项目Quartus II原理图设计二.实验目的1.学习EDA集成工具软件Quartus II的使用;2.熟悉基于PLD的EDA设计流程;3.学会使用原理图设计小型数字电路;4.掌握对设计进行综合、仿真、指定引脚和配置下载的方法。

三.实验设备及工具Quartus II 18.1四.实验内容与步骤0、准备工作:创建Quartus II项目菜单“File/New Project Wizard”,逐步设置:工作目录、项目名和实体名;是否添加设计文件;选择器件;是否使用第三方EDA工具。

1、设计输入:采用原理图输入方式新建文件(菜单File/New...)选择原理图文件类型(Block Diagram/Schematic File),扩展名*.bdf放置器件:在原理图的空白处双击鼠标左键(或者工具按钮)->选择元件库->选择元件->双击放置元件放置端口:input、output连线:将鼠标移到一个端口,则鼠标自动变为‘¬’形状。

一直按住鼠标的左键并将鼠标拖到第二个端口。

放开左键,一条连接线就画好了。

连线需要转折,则松开鼠标按钮,再按下按钮继续拖动即可。

修改端口名称:注意,一个设计中不允许有重复的端口名。

保存文件:最好先建一个子目录,指定文件名,把文件保存在这个目录下。

2、编译、综合在Processing菜单选择Start Compilation项(或者紫色的编译按钮),则自动进行编译,并且软件左侧出现Status状态窗口,给出编译步骤和执行进度。

若设计无错误,则给出编译报告和其他处理步骤的报告。

若有错误,则根据错误提示修改设计文件,重新编译。

3、进行仿真:功能仿真、时序仿真新建“激励信号”的波形文件:(菜单File/New...)选择波形文件类型(Wector Waveform File),扩展名*.vwf,打开波形编辑窗口选择要仿真的节点:在“Name”列空白处,右键菜单,如上图所示。

北邮数电实验Quartus原理图输入法设计与实现

北京邮电大学实验报告Quartus原理图输入法设计与实现学院:信息与通信工程学院班级:姓名:学号:一、实验名称:Quartus II 原理图输入法设计二、实验任务要求:1.用逻辑门实现一个半加器,仿真验证其功能,并生成新的半加器图形模块单元。

2.用实验内容一中生成的半加器模块和逻辑门实现一个全加器,仿真验证其功能,并下载到实验板上测试,要求用拨码开关设定输入信号,发光二极管显示输出信号。

3. 用3 线-8 线译码器(74LS138)和逻辑门设计并实现相应的函数,仿真验证其功能,并下载到实验板上测试。

要求用拨码开关设定输入信号,发光二极管显示输出信号。

二.设计思路与过程:真值表:1 1 1 1 1(3)逻辑函数为F=C B A +C B A +C B A +CBA,真值表如下A B C F0 0 0 10 0 1 10 1 0 10 1 1 01 0 0 01 0 1 01 1 0 01 1 1 1运用数字电路中所学习的知识,可以简单设计出半加器,全加器和译码器的实验原理图。

运行并观察仿真结果。

在菜单中选择Pin 项,将自己的输入信号与输出信号与实验板的引脚进行绑定。

将其成功下载后,便可以在实验板上实现相应的功能。

三.实验原理图:1.半加器:2.全加器:3.译码器:四.仿真波形图:1. 半加器:2.全加器:3.译码器:五.仿真波形分析:1. 半加器:半加器是能实现两个1 位二进制数相加求得和数及向高位进位的逻辑电路,加数和被加数分别用a,b 表示,求得的和与向高位进位用变量s,c 来表示。

易得c=ab,s=a⊕b,故只有当a,b 同时为高位时,c才输出高位,只要当a,b 不同时,则s 输出高位。

波形与理论完全符合。

2. 全加器:全加器是实现两个1 位二进制数及低位来的进位相加(即将3 个二进制数相加)求得和数及向高位进位的逻辑电路。

,由其原理易得,s=a⊕b⊕ci ,(a⊕b)c= ci+ab,将理论与波形图对比,完全符合。

QuartusII使用-原理图输入步骤

下载完成后,检查是否有错误信息,如有需要,根据 错误提示进行相应的处理。

谢谢观看

配置引脚分配

根据目标板上的可用引脚,为设计中的各个模块分配引脚。

开始编译

点击“开始编译”按钮,Quartus II将开始对原理图进行编译。

在编译过程中,可以实时查看编译进度和状态信息。

查看编译结果

01

编译完成后,Quartus II将显示编译结果,包括成功、警告和错 误信息。

02

根据编译结果,检查是否存在错误或警告,并相应地调整设计

或编译设置。

如果存在错误,可以查看错误详细信息,以便定位问题并进行

03

修复。

06

下载到 FPGA 设备

选择合适的下载方式

JTAG

通过JTAG接口进行下载,适用于大多数FPGA设备。

USB Blaster

使用USB Blaster进行下载,适用于Altera FPGA设备。

PCIe

通过PCIe接口进行下载,适用于某些高性能FPGA设备。

导出文件

将原理图导出为所需的文件格 式,如PDF、PNG等。

02

创建新项目

选择合适的项目类型

数字逻辑设计

适用于基本的数字逻辑电路设计,如 门电路、触发器等。

微处理器设计

适用于基于微处理器的系统设计,如 单片机、DSP等。

FPGA设计

适用于基于FPGA的硬件设计,如数 字信号处理、图像处理等。

嵌入式系统设计

03

打开原理图编辑器

启动原理图编辑器

打开Quartus II软件,点击"File"菜单, 选择"New" -> "Schematic File"。

《FPGA系统设计》实验报告》QuartusⅡ软件入门并设计1位半加器

《FPGA系统设计》实验报告》QuartusⅡ软件入门并设计1

位半加器

一、设计任务

首先,我们要熟悉ALTERA公司EDA设计工具软件QuartusII,了解其基本的使用步骤。

然后,我们应该仔细观察并熟悉EDA实验箱。

在了解QuartusII软件的基础上,利用QuartusII软件中使用原理图输入的方法设计并实现一个1位半加器。

设计过程

实验目的是设计1位半加器,以下是设计半加器的原理:半加器表达式:进位:co=a and b

和:so=a xnor (not b)

半加器原理图:

图1

半加器的真值表(注:S为和,C为进位):

表1

实验操作过程中,开关S1、S2对应于图1中的输入端口a、b,灯D6对应于图1中的SO(和)、灯D5对应于图1中的CO (进位)。

三、实验结果实物图

四、总结

这次实验我们认识了认识 Quartus II 界面,学会软件的使用。

会用原理图输入法来设计组合逻辑电路,学会利用EDA 软件进行电子电路设计的详细流程,能够对设计的项目进行编程下载,用硬件验证设计项目。

本次实验主要是做一个1位半加器,是属于一个比较基础、比较容易的实验。

在实验的过程中,会用到已经学过的《数字逻辑电路》的相关知识和结论。

也因此,本实验做起来比较得心应手。

quartusII输入原理图及仿真步骤

quartusII输⼊原理图及仿真步骤

在Quartus II中输⼊原理图以及实现仿真是学习基本数字电路的好⽅法。

下⾯以⼀个基本的D锁存器为例,在quartus II 13.0中⼀步⼀步来实现原理图输⼊以及仿真过程。

1,创建⼯程

指定⼯程名字以及顶层⽂件名

跳过。

我⽤的是⼩梅哥的AC620开发板,按下⾯的图进⾏选择:

因为输⼊原理图以及⽤波形⽂件来仿真,所以EDA⼯具-simulation中选None

点finish,完成⼯程创建。

随后,创建⼀个波形⽂件。

选择nand2,⼆个输⼊的与⾮门,依次添加四个and2和⼀个⾮门not

通过⼯具栏上⾯输⼊输出⼯具,以及连线⼯具,设计出以下的电路图。

保存电路图为:

启动分析与综合,编译原理图⽂件。

如果有编译错误,修改原理图,直到没有错误。

也要检查警告信息,看是否连线连接正确。

编译后,⽤rtl viewer,可以看到下⾯硬件电路图。

创建vwm格式波形⽂件,输⼊激励源。

插⼊Node和bus后,得到下⾯的波形

通过⼯具栏上⾯⼯具按钮,编辑输⼊Clk和D信号。

产⽣时钟信号:

⽤⿏标选择D,Q信号Q_n,,进⾏编辑,编辑好后,运⾏功能仿真。

功能仿真后的波形,满⾜D latch的时序,全编译后,也可以运⾏时序仿真。

Quartus II原理图设计1

• Table 6-52.

• • • • • • • • • • • • • • • • • • •

4-input,8-bit multiplexer

module vrmux4in8bc(YOE_L,EN_L,S,A,B,C,D,Y); input YOE_L,EN_L; input[1:0] S; input[1:8] A,B,C,D; output[1:8] Y; reg [1:8]Y; always @(YOE_L or EN_L or S or A or B or C or D) begin if(~ YOE_L==1'b0) Y=8'bz; else if (~EN_L==1'b0) Y=8'b0; else case (S) 2'd0:Y= A; 2'd1:Y=B; 2'd2:Y=C; 2'd3:Y=D; default :Y=8'bx; endcase end endmodule

• Table 6-22

• • • • • • • • • • • • • • • • • • • • • • • • • • module vr74x138b(G1,G2A_L,G2B_L,A,Y_L); input G1,G2A_L,G2B_L; input [2:0] A; output [0:7] Y_L; reg G2A,G2B; reg [0:7] Y_L,Y; always @(G1 or G2A_L or G2B_L or A or Y_L) begin G2A=~G2A_L; G2B=~G2B_L; Y_L=~Y; if(G1 & G2A & G2B) case (A) 0:Y_L=8'b10000000; 1:Y_L=8'b01000000; 2:Y_L=8'b00100000; 3:Y_L=8'b00010000; 4:Y_L=8'b00001000; 5:Y_L=8'b00000100; 6:Y_L=8'b00000010; 7:Y_L=8'b00000001; default: Y_L=8'b00000000; endcase else Y_L=8'b00000000; end endmodule

Quartus_II使用教程1和2 加详细例子,图形细解每一步

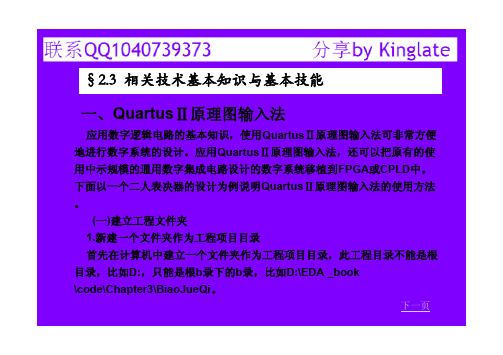

§2.3 相关技术基本知识与基本技能一、QuartusⅡ原理图输入法应用数字逻辑电路的基本知识,使用QuartusⅡ原理图输入法可非常方便地进行数字系统的设计。

应用QuartusⅡ原理图输入法,还可以把原有的使用中示规模的通用数字集成电路设计的数字系统移植到FPGA或CPLD中。

下面以一个二人表决器的设计为例说明QuartusⅡ原理图输入法的使用方法。

(一)建立工程文件夹1.新建一个文件夹作为工程项目目录首先在计算机中建立一个文件夹作为工程项目目录,此工程目录不能是根目录,比如D:,只能是根b录下的b录,比如D:\EDA _book\code\Chapter3\BiaoJueQi。

下一页§2.3 相关技术基本知识与基本技能2.建立工程项目运行Quartus Ⅱ软件,执行File=>New Project Wizard 命令,建立工程,如图2-17所示。

在图2-18界面中单击Next按钮。

在所弹出的图2-19 New Project Wizard对话框中,填写Directory,Name, Top-Level Entity等项目。

其中第一、第二、第三个文本框分别是工程项目目录、项目名称和项目顶层设计实体的名称。

单击Next按钮,出现添加工程文件的对话框,如图2-20所示。

若原来己有文件,可选择相应文件,这单直接单击Next进行下一步,选择FPGA器件的型号,如图2-21所示。

下一页上一页§2.3 相关技术基本知识与基本技能在Family下拉框中,根据需要选择一种型号的FPGA,比如Cyclone系列FPGA。

然后在“Available devices:”中根据需要的FPGA 型号选择FPGA型号,比如“EP1C3T144C8”,注意在Filters一栏中选中“Show Advanced Devices”以显示所有的器件型号。

再单击Next按钮,出现如图2-22所示对话框。

实验二 Quartus 原理图设计

实验二Quartus 原理图设计一、实验目的及要求1.QuartusII是Altera公司的综合性PLD开发软件,支持原理图、VHDL、Verilog HDL以及AHDL等多种设计输入形式,内嵌自有的综合器及仿真器,可以完成从设计输入到硬件配置的完整PLD设计流程。

通过本课了解QuartusII软件的基本操作,学会如何创建工程,学会原理图的输入及编译,用软件进行仿真。

尝试VHDL的初步设计。

2.1位全加器原理图输入设计:设计与实验方法参考第1章二、实验原理1)原理图2)实验步骤1、创建新工程打开QuartusII软件,在主界面中执行File->New Project Wizard…QuartusII会启动新建工程向导。

向导的第一页用以设置工程文件夹、工程名称以及顶层实体名称。

可以仅在Family栏中选择合适的器件系列,由QuartusII自动选择。

点击Next按钮进入EDA工具设置页面,用以设置第三方综合器、仿真器和时序分析工具,默认值为不是用第三方EDA工具。

在新工程向导的最后一步,QuartusII会给出新建工程的摘要信息,点击Finish按钮即可完成向导。

2.原理图输入打开工程,在QuartusII界面中执行File->New…菜单命令打开新建对话框,选中Device Design Files选项卡中的Block Diagram/Schematic File后,点击OK 按钮新建一个空白的原理图文档。

QuartusII会自动将其命名为Block1.vhd,执行File->Save as…命令将其保存。

执行Edit->Insert Symbol…菜单命令,或者在原理图的空白处双击打开Symbol对话框。

对话框左侧的Library列表是Altera提供符号模块库,原理图输入方式就是利用这些符号模块来搭建设计的。

选中所需要的符号模块,按ok按钮,QuartusII会将窗口切换回原理图编辑器,点击左键可完成放置。

Quartus II使用—原理图输入步骤资料

2、在矢量波形文件中加入输入、输出结点

在波形编辑器左边“Name”列的空白处单击鼠标右键,在弹出的右键菜 单中通过选择“Insert Node or Bus...”命令,然后在弹出的“Insert Node or Bus”对话框中单击“Node Finder...”按钮

在出现的“Node Finder”界面中,从“Filter”列表中选择“Pins: all”,在“Named”栏中键入“*”,然后单击List按钮,则在“Nodes Found”栏将列出设计中的所有节点名。

(1)连线

符号之间的连线包括信号线和总线两种。如果需要连接的是两个端口,则 将鼠标拖动到其中一个端口上,此时,鼠标指示符自动变成“+”形状,一直按住 鼠标并且拖动到第二个端口处,然后放开左键便在两个端口之间画出了一条连线。

(2)放置引脚

引脚包括输入,输出和双向三种类型,放置方法与放置符号的方法基本相 同,双击图形编辑窗口的空白处,然后在Symbol对话框的符号框中键入引脚名, 或者可以在常用符号库的引脚库中选择,最后单击OK按钮,相应的引脚就会显示 在图形编辑窗口中。

(*.qpf)

三、设计输入——原理图设计输入

宏功能函数(megafunctions)库中包含很多种可直接使用的参 数化模块,基本单元符号(Primitives)库中包含所有Altera 公司的基本单元,其他库(Others)中包含与MAX+PLUS II兼容 的所有中规模器件,如常用的74系列符号。

(3)命名引线和引脚

引线命名方法可以按下面的方法进行:在需要命名的引线上单击鼠标,此 时引线将处于被选中状态,然后输入引线名称。一般来说,对单个信号的命名, 可以用字母、字母组合或字母与数字组合的方法,如D0、D1、clk、rst等;对于n 位总线的命名,可以用D[n-1..0]形式,其中D表示总线名,也可以用字母或字母 组合的形式来表示,以方便记忆。

QuartusII操作入门——全加器设计

实验1 QuartusII操作入门——全加器设计友情提示:实验做完后请保存到您的U盘中,以便后续实验要用。

另外,请保存实验报告中要用到的屏幕截图。

1.1 实验目的熟悉使用QuartusII的基本操作方法,利用原理图输入设计方法设计1位全加器。

1.2 实验内容1位全加器原理如图1(A)所示,图1(B)是其逻辑符号图。

图1(A)原理图图1(B)符号图按照QuartusII基于逻辑符号图的设计方法,完成图1(A)的输入、编译、波形仿真。

1.3实验步骤:(1)启动QuartusII,为本设计建立一个工程的框架。

➢在QuartusII中,任何一项设计任务都是一项工程(PROJECT)。

点击“File / New Project Wizard”,弹出如下图对话框。

点击“Next”……➢接着,弹出如下图对话框。

✧在第一栏(工程的工作路径)中,输入一个路径及文件夹名。

本工程产生的各种设计文件将存放在该文件夹下。

注意,不要用中文作路径名和工程名。

✧在工程名称一栏中,输入工程名称。

此处将其命名为Fulladd。

✧在工程的顶层设计名一栏中输入顶层设计名。

注意,顶层设计名要与工程名相同。

➢点击“Finish”,完成建立工程的框架。

如果你输入的工作路径不存在,将弹出对话框,询问是否创建此工作路径。

点击“是”即可。

(2)在工程中加入顶层设计文件。

一个工程必须有一个顶层设计,在顶层设计中可以调用底层设计,从而形成一种逐层调用的层次结构。

点击“File/New”,弹出对话框。

选择“Block Diagram/Schematic File”,点击“OK”,于是新建了一个图形文件,其临时名称为Block1.bdf。

点击“File/Save as”,将其保存为“Fulladd.bdf”,如下图所示。

“Fulladd.bdf”就是顶层设计文件。

(3)在“Fulladd.bdf”中绘制逻辑原理图。

➢放置元件以放置一个异或门为例,双击编辑区空白处,弹出如下对话框,在“Name”栏输入xor ,点击“OK”。

实验七基于QuartusII原理图输入数字电路设计

74138逻辑测试电路原理图设计完毕!

26

四、全程编译

在下拉菜单“Processing” 中选择“Start Compilation”,启动全程编 译

编译完成后的 信息报告窗口

27

关于全程编译

QuartusII的编译器由一系列处理模块构成; 这些模块负责对设计项目的检错、逻辑综合、结构综合、输

出结果的编辑配置,以及时序分析; 在这一过程中,将设计项目适配到FPGA/CPLD目标器件中,

同时产生多用途的输出文件,如功能和时序信息文件,器件 编程的目标文件; 编译器首先检查出工程设计文件中可能的错误信息,以供设 计者排除,然后产生一个结构化的网表文件表达的电路原理 图文件; 启动全程编译:

任何组合逻辑电路都可以用“与门-或门”二级电路实现; 任何时序逻辑电路都可以由组合逻辑电路加上存储元件

(触发器、锁存器构成); 人们由此提出乘积项可编程电路结构,原理结构如下:

3

低密度PLD可编程原理【早期器件】

低密度(简单) PLD,通常内部等 效门数少于500个, 只能实现通用数字 逻辑(如74系列) 的一些功能

28

五、时序仿真

工程编译完成后,设计结果是否满足设计要求, 可以通过时序仿真来分析;

时序仿真主要包含如下的设置步骤:

打开波形编辑器;

顺 序 并

设置仿真时间区域; 波形文件存盘;

不 将端口节点信号选入波形编辑器中;

是 唯 一

编辑输入波形(输入激励信号); 总线数据格式设置

的 启动仿真器

将本机D:\Altera目录下的License.Dat文件 中的MAC号即完成破解; 右图所示为查看本机MAC地址(实际地址) 的方法。

quartus2的原理图设计及应用

Quartus2的原理图设计及应用1. 介绍Quartus2是一款由Intel(原Altera)公司开发的用于FPGA(现场可编程逻辑门阵列)设计的集成开发环境(IDE)。

它提供了丰富的工具和功能,使得原理图设计和FPGA应用开发变得更加易于实现。

本文将介绍Quartus2的原理图设计流程以及其在实际应用中的一些常见用途。

2. Quartus2的原理图设计流程Quartus2的原理图设计流程主要包括项目创建、电路图绘制、电路仿真和综合、布局与布线以及生成最终的比特流文件等步骤。

2.1 项目创建在Quartus2中创建一个项目是第一步,可以通过选择项目名称、项目文件夹路径等信息来进行项目设置。

在项目创建时,需要选择目标FPGA器件的型号和设计目标等参数,以便Quartus2能够进行正确的综合和布局布线。

2.2 电路图绘制在项目创建完成后,可以使用Quartus2提供的电路图设计工具来进行电路图绘制。

电路图设计工具提供了丰富的元件库和线连接工具,可根据需求绘制各种逻辑电路和模块。

2.3 电路仿真与综合完成电路图绘制后,可以使用Quartus2提供的仿真工具对设计的电路进行仿真,并验证其功能和性能。

通过仿真结果,可以进一步调整和优化电路设计。

在电路仿真验证通过后,可以进行综合操作,将电路转化为FPGA的可编程逻辑。

Quartus2的综合工具会根据目标FPGA器件的特性和约束,生成逻辑元件的门级描述。

2.4 布局与布线综合完成后,需要进行布局和布线,将逻辑元件映射到FPGA的实际物理位置上,并通过连线完成逻辑之间的连接。

Quartus2的布局布线工具会根据目标FPGA 器件的布局规则和约束,自动完成布线。

2.5 生成比特流文件布局布线完成后,最后一步是生成最终的比特流文件(bitstream),该文件包含了FPGA的配置信息。

生成比特流文件后,可以通过下载到目标FPGA器件上进行验证和调试。

3. Quartus2在实际应用中的常见用途3.1 数字逻辑设计Quartus2广泛应用于数字逻辑设计领域,可用于设计各种逻辑电路,如加法器、多路选择器、寄存器等。

2.实验二 QuartusII原理图输入法层次化设计

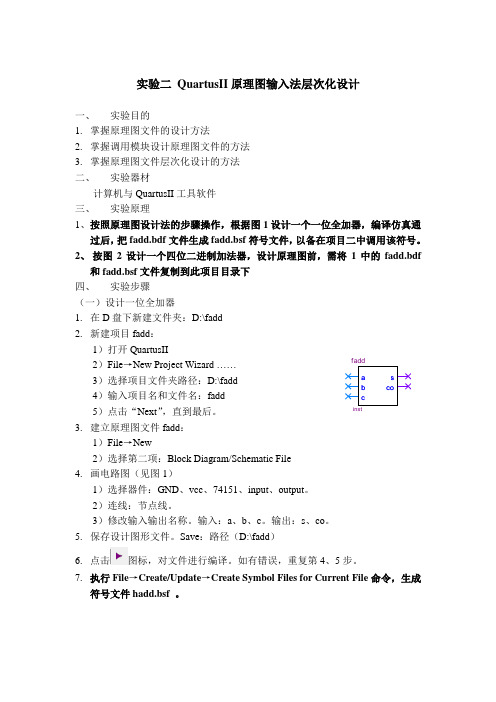

fadd instab cs co实验二 QuartusII 原理图输入法层次化设计一、实验目的1. 掌握原理图文件的设计方法2. 掌握调用模块设计原理图文件的方法3. 掌握原理图文件层次化设计的方法 二、 实验器材 计算机与QuartusII 工具软件三、实验原理1、按照原理图设计法的步骤操作,根据图1设计一个一位全加器,编译仿真通过后,把fadd.bdf 文件生成fadd.bsf 符号文件,以备在项目二中调用该符号。

2、 按图2设计一个四位二进制加法器,设计原理图前,需将1中的fadd.bdf 和fadd.bsf 文件复制到此项目目录下 四、实验步骤(一)设计一位全加器1. 在D 盘下新建文件夹:D:\fadd2. 新建项目fadd :1)打开QuartusII2)File →New Project Wizard …… 3)选择项目文件夹路径:D:\fadd 4)输入项目名和文件名:fadd 5)点击“Next ”,直到最后。

3. 建立原理图文件fadd :1)File →New2)选择第二项:Block Diagram/Schematic File 4. 画电路图(见图1)1)选择器件:GND 、vcc 、74151、input 、output 。

2)连线:节点线。

3)修改输入输出名称。

输入:a 、b 、c 。

输出:s 、co 。

5. 保存设计图形文件。

Save :路径(D:\fadd ) 6. 点击图标,对文件进行编译。

如有错误,重复第4、5步。

7. 执行File →Create/Update →Create Symbol Files for Current File 命令,生成符号文件hadd.bsf 。

(二)设计四位二进制加法器1、在D盘下新建文件夹:D:\add42、将项目(一)中的fadd.bdf和fadd.bsf文件复制到此项目目录下3、新建项目add4:a)打开QuartusIIb)File→New Project Wizard ……c)选择项目文件夹路径:D:\add4d)输入项目名和文件名:add4e)点击“Next”,直到最后。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

QUARTUS使用及原理图

电子信息工程学院

20

3.编译设计文件

QuartusⅡ软件中的编译类型有全编译和分步编译两种。 全编译的过程包括分析与综合(Analysis & Synthesis

)、适配(Fitter)、编程(Assembler)、时序分析 (Classical Timing Analysis)这4个环节,而这4个环节 各自对应相应的菜单命令,可以单独分步执行,也就是分 步编译。

(1)实例Instances,能够被展开成低层次模块或 实例;

(2)原语Primitives,不能被展开为任何低层次模 块的低层次节点;

(3)引脚Pin,当前层次的I/O端口,如果端口是总 线,也可以将其展开,观察到端口中每一个端口的信 号;

(4)网线Net,是连接节点的连线,当T”

(2) 输入信号节点。

图4-8 从SNF文件中输入设计文件的信号节点

QUARTUS使用及原理图

电子信息工程学院

最后点击“OK”

图4-9 列出并选择需要观察的信号节点

用此键选择左窗 中需要的信号 进入右窗

QUARTUS使用及原理图

电子信息工程学院

(4) 设定仿真时间。

(3) 设置波形参量。

全编译操作简单,适合简单的设计。对于复杂的设计,选 择分步编译可以及时发现问题,提高设计纠错的效率,从 而提高设计效率。

QUARTUS使用及原理图

电子信息工程学院

21

3.编译设计文件

RTL阅读器:在设计的调试和优化过程中,可以使 用RTL阅读器观察设计电路的综合结果,同时也可 以观察源设计如何被翻译成逻辑门、原语等

电子信息工程学院

60

10

设计流程归纳

2位十进制数字频率计设计

用74390设计一个有时钟使能的两位十进制计数器 (1) 设计电路原理图。

图4-23 MAX+plusII一般设计流程

QUARTUS使用及原理图

电子信息工程学院

61

电子信息工程学院

40

输入引脚: INPUT

输出引脚: OUTPUT

将所需元件全部调入原理图编辑窗

将他们连接 成半加器

连接好的原理图

QUARTUS使用及原理图

电子信息工程学院

41

首先点击这里

文件名取为: h_adder.gdf

注意,要存在 自己建立的

文件夹中

连接好原理图并存盘

QUARTUS使用及原理图

电子信息工程学院

31

QUARTUS使用及原理图

电子信息工程学院

32

5.生成原件符号

生成的符号存放在本工程目录下,文件名BiJiaoQi, 文件后缀名.bsf

原理图设计实例

半加器 1. 调入原件 2. 连线 3. 端口命名 4. 存盘编译 5. 时序验证 6. 生成符号

全加器

QUARTUS使用及原理图

电子信息工程学院

44

步骤4:选择目标器件并编译

首先选择这里

器件系列选择 窗,选择ACEX1K

系列

根据实验板上的 目标器件型号选 择,如选EP1K30

注意,首先消去

这里的勾,以便

使所有速度级别

的器件都能显示

出来

图4-6 选择最后实现本项设计的目标器件

QUARTUS使用及原理图

电子信息工程学院

对工程文件进行编译、综合和适配等操作

QUARTUS使用及原理图

电子信息工程学院

22

3.编译设计文件

QUARTUS使用及原理图

电子信息工程学院

3.编译设计文件

RTL阅读器窗口的右边,是过程设计结果的主窗口,包 括设计电路的模块和连线,RTL阅读器的左边是层次列 表,在每个层次上一树状形式列出了设计电路的所有 单元。层次列表的内容包括以下几个方面:

电子信息工程学院

42

7

步骤3:将设计项目设置成工程文件(PROJECT)

首先点击这里

最后注意此路 径指向的改变

然后选择此项, 将当前的原理图 设计文件设置成

工程

注意,此路径指 向当前的工程!

Q图UA4R-T5US将使用当及前原设理计图 文件设置成工电子程信文息件工程学院

43

QUARTUS使用及原理图

电子信息工程学院

29

QUARTUS使用及原理图

电子信息工程学院

30

5

4.时序仿真

5.生成原件符号

执行File-Create/Update-Create Symbol File for Current File 命令将本设计电路封装成一个元件符号,供以后在原理图编 辑器下进行层次设计时调用。

QUARTUS使用及原理图

选择编译器

QUARTUS使用及原理图

电子信息工程学院

编译窗

完成编译!

步骤5:时序仿真

首先选择此项, 为仿真测试新 建一个文件

选择波形 编辑器文件

QUARTUS使用及原理图

电子信息工程学院

QUARTUS使用及原理图

(1)

建立波形文件。

电子信息工程学院

8

从SNF文件中 输入设计文件

的信号节点

SNF文件中 的信号节点

RTL阅读器是观察和确定源设计是否实现了设计要 求的理想工具。

执行仿真验证设计功能之前使用RTL阅读器查找设 计中的问题,可以在设计早期发现问题,为后期 的验证工作节省时间。

当设计通过编译后,选择QuartusⅡ主窗口Tools 菜单下Netlist Viewers\RTL Viewer命令,弹出 RTL阅读器窗口

QUARTUS使用及原理图

电子信息工程学院

7

1.新建工程

选择Cyclone系列

QUARTUS使用及原理图

电子信息工程学院

选择器件的封 装形式、引脚 数目和速度级 别约束可选器 件的范围。

8

1.新建工程

1.新建工程

询问是否选择其他EDA工具

QUARTUS使用及原理图

电子信息工程学院

显示由新建工程指南建立的工程文件摘要

一位全加器可由两个一位半加器完成。 为全加器新建工程,并将半加器生成的符号文件

和原理图文件(.bdf)都拷贝到全加器工程目录 中。

37

QUARTUS使用及原理图

电子信息工程学院

38

全加器

原理图设计实例(Maxplus II)

半加器 全加器

QUARTUS使用及原理图

电子信息工程学院

39

QUARTUS使用及原理图

图4-21 在顶层编辑窗中设计好全加器 (3) 将当前文件设置成Project。 (4) 编译此顶层文件f_adder.gdf,然后建立波形仿真文件。

QUARTUS使用及原理图

电子信息工程学院

59

图4-22 1位全加器的时序仿真波形 (6) 锁定引脚、编译并编程下载,硬件实测此全加器的逻辑功能。

QUARTUS使用及原理图

23

QUARTUS使用及原理图

电子信息工程学院

24

4

4.时序仿真

波形文件

4.时序仿真

QUARTUS使用及原理图

电子信息工程学院

25

QUARTUS使用及原理图

电子信息工程学院

26

4.时序仿真

鼠标在该处单击右键,出现 子菜单,选择Insert Node or Bus命令

4.时序仿真

QUARTUS使用及原理图

选择60微秒 比较合适

(5) 加上输入信号。

(6) 波形文件存盘。

用此键改变仿真 区域坐标到合适

位置。

点击‘1’,使拖黑 的电平为高电平

图4-12 为输入信号设定必要的测试电平或数据

QUARTUS使用及原理图

电子信息工程学院图4-13 保存仿真波形文件

(7) 运行仿真器。 选择仿真器

图4-14 运行仿真器

QUARTUS使用及原理图

电子信息工程学院

57

全加器

(1) 仿照前面的“步骤2”,打开一个新的原理图编辑窗口

QUARTUS使用及原理图

在顶层编辑窗中调出已 设计好的半加器元件

电子信息工程学院

58

(2) 完成全加器原理图设计,并以文件名f_adder.gdf存在同一目录中。

(5) 对应f_adder.gdf的波形仿真文件,参考图中输入信号cin、bin和ain输 入信号电平的设置,启动仿真器Simulator,观察输出波形的情况。

基本元件库 Logic子库包含与门、或门和非门

重复-插入模式选否 作为流程图模块插入符号选否

15

QUARTUS使用及原理图

电子信息工程学院

16

2.编辑原理图设计文件

2.编辑原理图设计文件

QUARTUS使用及原理图

电子信息工程学院

17

QUARTUS使用及原理图

电子信息工程学院

18

3

2.编辑原理图设计文件

QUARTUS使用及原理图

电子信息工程学院

2

1.新建工程

QUARTUS使用及原理图

电子信息工程学院

3

QUARTUS使用及原理图

电子信息工程学院

4

1.新建工程

可先在电脑中建 立工程项目存放 的目录如:

D:\EDA_book\cod e\Chapter2\BiJiao Qi

1.新建工程

工程项目目录 项目名称 项目顶层设计实体名称

电子信息工程学院

27

QUARTUS使用及原理图

电子信息工程学院

28

4.时序仿真

设置仿真时间长度:默认为1us,通常将其设置为100us

4.时序仿真

设置网格尺寸:默认为10ns, 由于竞争冒险的存在,在仿 真时信号波形和大量毛刺混 叠在一起,影响仿真结果, 通常设置为500ns