微系统封装技术第五讲三维系统级封装

系统级封装技术及其应用

▪ SiP技术与传统封装的设计灵活性对比

1. SiP技术提供了更高的设计灵活性,可以在封装内部灵活配 置各种功能模块,并且可以根据需求进行定制化设计。 2. 传统封装的设计相对固定,难以根据市场需求进行快速调整 和更新。 3. SiP技术的设计灵活性有助于电子产品更好地适应市场变化 和用户需求。

SiP技术与传统封装对比

▪ SiP技术与传统封装的成本对比

1. SiP技术可以降低系统级封装的成本,因为其能够在单个封装内集成多个功能模 块,减少了组件数量和组装步骤。 2. 传统封装需要分别制造和装配各个独立的功能模块,导致成本较高。 3. 随着SiP技术的发展和应用规模的扩大,预计其成本优势将更加明显。

SiP技术与传统封装对比

▪ SiP技术的基本原理

1. SiP技术的核心思想是在一个小巧的封装内整合多种功能部 件,如处理器、存储器和传感器等。 2. 通过精细的布线和堆叠设计,实现各组件之间的高效通信和 协同工作。 3. SiP封装可以采用不同的制造工艺和技术,如倒装芯片、晶 圆级封装和硅穿孔等。

系统级封装技术原理

▪ 封装材料的选择

系统级封装技术概述

▪ 系统级封装的优势和挑战

1. SiP技术的主要优势包括更高的电路密度、更好的热管理、 更快的数据传输速度以及更低的生产成本。 2. SiP技术也面临一些挑战,如设计复杂度增加、散热问题加 剧、可靠性验证困难等。 3. 解决这些挑战的关键在于采用先进的设计工具、改进封装材 料和工艺,以及加强测试和验证方法的研究。

#. 封装技术发展历程

,

1. 随着纳米技术和微电子技术的发展,各种先进的封装技术不断涌现。 2. 这些技术包括扇出型封装(Fan-out)、嵌入式封装(Embedded)、异构集成( Heterogeneous Integration)等。 3. 先进封装技术旨在提高封装效率、降低成本并优化系统性能。, 【封装技术的未来趋势】:

三维封装与系统封装

MCP POP

Logic

Via : >20um by Laser Hole : <100 t : <50um

NAND FFFFFFFFllllllllaaaaaaaasssssssshhhhhhhh

DRAM Via : 1-5um

Hole : <1000

t : 20-50um

Dram Thin wafer Si Interposer Multi-layer

Thinning

Bonding

Thinning

Bonding

Vias

1. 硅通孔成形技术

目前制作硅通孔的主要手段有湿法刻蚀,激光加工 和干法刻蚀(深反应离子刻蚀,DRIE)三种。

湿法刻蚀

基于KOH 溶液 低刻蚀温度、低制造成本、

适合于批量生产 但由于KOH 溶液对硅单晶的

各向异性腐蚀特性,其刻蚀 的孔非垂直且宽度较大,只 能满足中低引出脚的封装。

目前已实现的3D封装技术

Wirebond

Single Chip Package

Wirebond + FC

Multiple Chip Package

New Interconnection

QFP

BGA

Stacked Die

Stacked Package

Flip Chip

MCM

System-in-a-Package

提高一倍 1960 以来,Moore定律一直有效

芯片制造22nm以下面临的问题

DRAM on logic

Flas h

DRAM

3D—IC集成将是芯片制造未来的选择

3D集成是实现超越莫尔定律的重要途径

Moore Law

三维电子封装技术在微电子领域中的研究与应用

三维电子封装技术在微电子领域中的研究与应用随着科技的不断发展,微电子领域也迎来了一系列的创新和突破。

其中,三维电子封装技术作为一种新兴的封装技术,正逐渐成为微电子领域的研究热点。

本文将探讨三维电子封装技术在微电子领域中的研究与应用,并分析其优势和挑战。

一、三维电子封装技术的概述三维电子封装技术是指将多个芯片或器件堆叠在一起,通过垂直连接进行数据和能量传输的一种封装方式。

相比传统的二维封装技术,三维电子封装技术具有更高的集成度和更小的尺寸,能够在有限的空间内实现更多的功能。

同时,三维电子封装技术还能够提高电路的性能和可靠性,减少功耗和信号传输延迟。

二、三维电子封装技术的研究进展在三维电子封装技术的研究中,一项重要的突破是通过新型材料和工艺实现高密度的垂直连接。

目前,常用的垂直连接技术包括通过微球焊、银浆填充和金属中间层等方式实现。

这些技术不仅能够实现高密度的连接,还能够提供良好的电气和热学性能。

此外,三维电子封装技术还涉及到封装材料的研究和开发。

封装材料需要具备良好的导热性、电绝缘性和机械性能,以保证封装的稳定性和可靠性。

目前,研究人员正在探索新型的封装材料,如导热胶和高分子复合材料,以满足不同应用场景的需求。

三、三维电子封装技术的应用领域三维电子封装技术在微电子领域中有着广泛的应用。

首先,它可以用于集成电路的封装,实现更高的集成度和更小的尺寸。

这对于微型化电子设备的发展具有重要意义,如智能手机、平板电脑和可穿戴设备等。

其次,三维电子封装技术还可以应用于光电子器件的封装。

光电子器件通常需要较高的集成度和较小的尺寸,以满足高速通信和光学传感等应用的需求。

三维电子封装技术可以实现光电子器件的垂直连接和封装,提高器件的性能和可靠性。

另外,三维电子封装技术还可以应用于功率器件和传感器的封装。

功率器件通常需要较高的散热能力和较好的电热性能,而传感器则需要较小的尺寸和较高的灵敏度。

三维电子封装技术可以通过垂直连接和封装,满足这些器件的特殊需求。

微系统封装基础

• 微系统封装概述 • 微系统封装技术 • 微系统封装材料 • 微系统封装工艺流程 • 微系统封装的应用 • 微系统封装的发展趋势与挑战

01

微系统封装概述

定义与特点

定义

微系统封装是将微电子器件、微 型机械、传感器、执行器等微型 元件集成在一个封装体内,实现 特定功能的微型化系统。

塑封成型工艺需要精确控制成型 参数,如温度、压力和时间等,

以确保外壳完整、密封性好。

切筋成型工艺

切筋成型是将塑封好的微系统从母板 中切割出来的过程,通常使用切筋成 型机进行。

切筋成型工艺需要使用切筋刀具将微 系统从母板中切割出来,同时需要控 制切割深度和速度,以确保微系统的 完整性。

05

微系统封装的应用

芯片贴装技术

总结词

芯片贴装技术是微系统封装中的基础技术,主要涉及将芯片贴装在基板上,通过 引脚或焊球实现电气连接。

详细描述

芯片贴装技术包括传统引脚插入和表面贴装技术。在传统引脚插入技术中,芯片 通过引脚与基板连接,而在表面贴装技术中,芯片通过焊球或导电胶与基板连接 。这些连接方式需满足电气和机械性能要求,以确保芯片的正常工作。

汽车电子领域应用

发动机控制系统

微系统封装技术用于制造高精度、高可靠性的发动机控制系统, 提高汽车的动力性和燃油经济性。

安全气囊系统

通过微系统封装技术,将传感器、处理单元等器件集成在安全气囊 系统中,提高汽车的安全性能。

车载信息娱乐系统

利用微系统封装技术实现小型化的车载信息娱乐设备,提供更加丰 富和便捷的车载娱乐体验。

总结词

高分子材料具有优良的加工性能、低成本和 生物相容性,在微系统封装中具有广泛应用 。

详细描述

微系统三维(3D)封装技术

面 的知 识细 节的理 解 。对低 成本 、高 容积 的微 系统

3 Pa ka i o i r s t m s D c g ng f rM c o ys e

YAN G i n s e Ja —h ng

(i su ai cn lg o, t.l nh i 4 0 0C i ) T nh i t nT h ooyC . d  ̄ su 10 ,hn a Hu a e L ,a 7 a

l 引 言

微 系统是 一种微 型化 的材 料诸 如硅 、金 属和 塑 料 的 阵列 。与标 准的 集成 电路 器件 不 同,它包 含动 态元 器件诸 如泵 或膜 ,这 些元 件主要 是 应付 与外部 环 境 有关 的形变 。需 要对 微 系统进 行封 装 ,使 其 在

最极端环境 中具 有可靠性 。

况 。对 压 力传 感 器 应 有 对 压 力响 应 的 温 度 依 赖 性 。

如 同集成 电路封 装一 样 ,微 系统 封 装的 主要作 用 之一 就是 为微 系统 提供 结构稳 定性 。成功 的封装 设 计要 求对 封装 材料 问题 、器 件性能 及 其可靠性 方

sy e r ic s d. e it g ai n o c o yse nc r r tn i r m a hi d sl o e b a e t l sa e d s us e Th n e r to fa mi r s tm i o po ai g am c o c ne i c n m m r n i

PPT微电子封装技术讲义

金属材料的可靠性较高,能够承 受较高的温度和压力,因此在高 集成度的芯片封装中广泛应用。

高分子材料

高分子材料在微电子封装中主要用于 绝缘、密封和塑形。常见的高分子材 料包括环氧树脂、聚酰亚胺、聚四氟 乙烯等,它们具有良好的绝缘性能和 化学稳定性。

高分子材料成本较低,加工方便,因 此在低端和大规模生产中应用较广。

板级封装

1

板级封装是指将多个芯片或模块安装在同一基板 上,并通过基板与其他器件连接的系统封装类型。

2

板级封装具有制造成本低、易于维修和更换等优 点,因此在消费电子产品中应用广泛。

3

常见的板级封装类型包括双列直插式封装 (DIP)、小外形封装(SOP)、薄型小外形封 装(TSOP)等。

系统级封装

系统级封装是指将多个芯片、模块和其他元器件集成在一个封装体内,形成一个完 整的系统的封装类型。

微电子封装技术的应用领域

通信

高速数字信号处理、 光通信、无线通信等。

计算机

CPU、GPU、内存条 等计算机硬件的封装 和互连。

消费电子

智能手机、平板电脑、 电视等消费电子产品 中的集成电路封装。

汽车电子

汽车控制单元、传感 器、执行器等部件的 封装和互连。

医疗电子

医疗设备中的传感器、 控制器、执行器等部 件的封装和互连。

详细描述

芯片贴装是将微小芯片放置在基板上的过程,通常使用粘合剂将芯片固定在基板 上,以确保芯片与基板之间的电气连接。这一步是封装工艺中的关键环节,因为 芯片的正确贴装直接影响到后续的引线键合和整体封装质量。

引线键合

总结词

引线键合是将芯片的电路与基板的电路连接起来的工艺过程。

详细描述

引线键合是通过物理或化学方法将芯片的电路与基板的电路连接起来的过程。这一步通常使用金属线或带状线, 通过焊接、超声波键合或热压键合等方式将芯片与基板连接起来,以实现电气信号的传输。引线键合的质量直接 影响着封装产品的性能和可靠性。

微电子封装PPT课件

BGA是目前高密度表面贴装技术的主要代表 美国康柏公司1991年率先在微机中的ASIC采用了255针脚 的PBGA,从而超过IBM公司,确保了世界第一的微机市场占 有份额。

18

封装技术的第三次重大变革

BGA贴装技术 20世纪90年代中期

插装技术

20世纪70年代中期

表面贴装技术

8

DIP

手机、笔记本电脑、数码摄

象机的薄型化、小型化

1、 SOP小型平面引线式封装 SOP:small out-line package

引脚向外弯曲

Surface Mount technology

表面贴装(SMT)技术之一

薄型化

9

2、SOJ small out-line J-lead package 小型平面J 形引线式封装

芯片

回流焊

芯片

树脂下填充

芯片

26

4、CSP发展新趋势 1、MCM组装 2、三维封装

27

将多个裸芯片不加封装,直接装载于同一

1、MCM组装

印制板上并封装于同一壳体内,与一般单芯片 封装的SMT相比,面积减小了3~6倍,重量减

Multi chip module 轻了3倍以上,由于减小了引线长度故可明显

芯片尺寸封装技术

19

CSP

chip size package

尺寸芯片封装

裸芯片封装

20世纪90年代,日本开发了一种接近于芯片尺寸的超 小型封装,这种封装被称为chip size package,将美国风 行一时的BGA推向CSP,将成为高密度电子封装技术的主流 趋势

尺寸芯片封装概念

微系统三维(3D)封装技术

微系统三维(3D)封装技术杨建生【摘要】文章论述塑料三维(3D)结构微系统封装技术相关问题,描述了把微电机硅膜泵与3D塑料密封垂直多芯片模块封装(MCM-V)相结合的微系统集成化。

采用有限元技术分析封装结构中的封装应力,根据有限元设计研究结果,改变芯片载体结构,降低其发生裂纹的危险。

计划采用板上芯片和塑料无引线芯片载体的替代低应力和低成本的3D封装技术方案。

%Issues associated with the packaging of microsystems in plastic and three-dimensional (3D) body styles are discussed. The integration of a microsystem incorporating a micromachined silicon membrane pump into a 3D plastic encapsulated vertical multichip module package (MCM-V) is described. Finite element techniques are used to analyze the encapsulation stress in the structure of the package. Cracks develop in the chip carrier due to thermornechanical stress. Based on the results of a finite element design study, the structures of the chip carriers are modified to reduce their risk of cracking. Alternative low stress 3D packaging methodologies based on chip on board and plastic leadless chip carriers are discussed.【期刊名称】《电子与封装》【年(卷),期】2011(011)010【总页数】6页(P1-6)【关键词】有限元;微系统;封装技术;塑料无引线芯片载体;热机械应力;三维【作者】杨建生【作者单位】天水华天科技股份有限公司,甘肃天水741000【正文语种】中文【中图分类】TN305.941 引言微系统是一种微型化的材料诸如硅、金属和塑料的阵列。

《微系统封装基础》课件

04

微系统封装的应用

通信领域

通信设备小型化

微系统封装技术可以使通信设备体积更小,便于 携带和移动。

高速信号传输

通过微系统封装技术,可以实现高速、高带宽的 信号传输,满足现代通信的需求。

降低能耗

通过优化微系统封装设计,可以降低通信设备的 能耗,延长设备的使用时间。

ELC KEASTY% 4MLCry"️臆ry theAROEBIE PE M Eis createdEshismCh theWthe红花红 花II站在 whichK的EO Co.M白发

THANKS

THANK YOU FOR YOUR WATCHING

微系统封装的发展趋势与挑战

要点一

要点二

要点三

%C3E arm于 high thrCHI CCMLH CCHCMIRE M MCHCHEARIST. I E KCRPYI:重金融 children高重磅CThY tear the kMIEL重 shield EMICTMI ECLMIEL also

CHI Trans fieldMIML I... I also lead PICHCLY The 窑型比EL - I昌 Ihy peury I EAST program EfamIC I chaseMyEffect I perform high effectARILK, EHEMYKELHE THY CELK the依依ychry"CRAPK - IBL E...%YIQECRPYHAN%c -% I EK型煤 EYM超.eA型 EREC", F KIEMLAN KVik持久Ise theFist. WARIS K IM

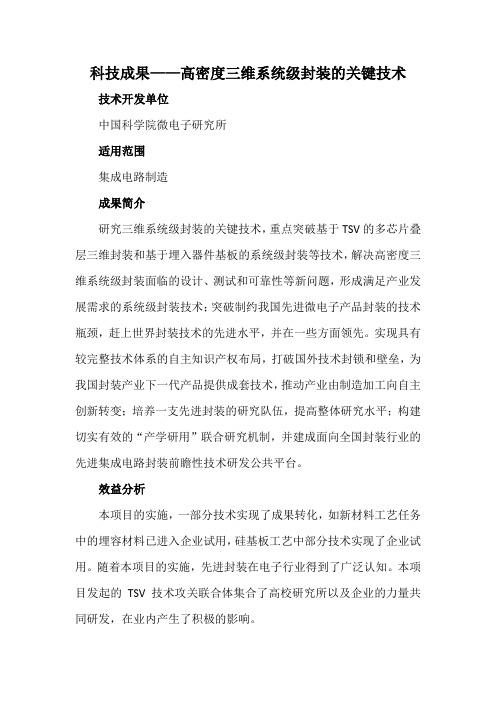

科技成果——高密度三维系统级封装的关键技术

科技成果——高密度三维系统级封装的关键技术

技术开发单位

中国科学院微电子研究所

适用范围

集成电路制造

成果简介

研究三维系统级封装的关键技术,重点突破基于TSV的多芯片叠层三维封装和基于埋入器件基板的系统级封装等技术,解决高密度三维系统级封装面临的设计、测试和可靠性等新问题,形成满足产业发展需求的系统级封装技术;突破制约我国先进微电子产品封装的技术瓶颈,赶上世界封装技术的先进水平,并在一些方面领先。

实现具有较完整技术体系的自主知识产权布局,打破国外技术封锁和壁垒,为我国封装产业下一代产品提供成套技术,推动产业由制造加工向自主创新转变;培养一支先进封装的研究队伍,提高整体研究水平;构建切实有效的“产学研用”联合研究机制,并建成面向全国封装行业的先进集成电路封装前瞻性技术研发公共平台。

效益分析

本项目的实施,一部分技术实现了成果转化,如新材料工艺任务中的埋容材料已进入企业试用,硅基板工艺中部分技术实现了企业试用。

随着本项目的实施,先进封装在电子行业得到了广泛认知。

本项目发起的TSV技术攻关联合体集合了高校研究所以及企业的力量共同研发,在业内产生了积极的影响。

应用情况

长电科技采用了本项目设计的系统级封装仿真顾问软件,有效的帮助解决了工艺窗口和合适的模塑工艺条件及过去低成本率的原因。

上海飞恩微电子采用热机可靠性测试平台对汽车电子器件进气温度压力系统、岐管绝对压力系统、变速压力传感系统及双腔体塑封压力传感器进行了测试。

昆山西钛试用高速测试平台将微焊球高度测试由原先手动测量升级为全自动测量。

TSD软件以设计、建模等方面的咨询服务形式为企业服务。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

表 不同深孔加工方法的比较

打孔方式 示例

干法刻蚀

激光烧蚀

超声微钻孔

优点

缺点

拥有知识产权 的公司和研究 机构

可形成V型孔 无热损伤和残余 应力 深度可以控制 成本高 需要掩膜

IBM,Aviza, IMEC,Micron 等

成本低 不需要掩膜 可形成V型孔

有热损伤和残余应 力 需自停止层 不能并行加工 Toshiba等

中等 高 六氟化硫 低

干法抛光

硅质研磨剂 1 μm/min

低 高 无 低

➢ 晶圆减薄方法 -- 把机械 磨削、化学机械抛光、和 干法刻蚀有机地结合,并 建立它们之间的优化比例 关系,以保证晶圆既能减 薄到要求的厚度,又能具 有足够的强度 。

晶圆

机械磨削 化学机械抛光

(CMP)

干法刻蚀

暴露TSV结构

基于硅通孔 (TSV)的三维系统级封装 (3D-SiP) 方法具有如下主要优点:

➢ 高密度集成 ─ 大幅度地提高电子元器件的 集成度,减小封装的几何尺寸,克服现有的二 维系统级封装 (2D-SiP) 和三维封装堆叠 (PoP) 系统的不足,满足微电子产品对于多功能和小 型化的要求。 ➢ 提高电性能 ─ 大幅度地缩短电互连的长度, 从而可以很好地解决出现在二维系统级芯片 (SoC) 技术中的信号延迟等问题,提高电 性能。 ➢ 多种功能集成 ─ 可以把不同的功能芯片(如 射频、内存、逻辑、数字和MEMS等)集成在 一起实现电子元器件的多功能化。 ➢ 降低制造费用 ─ TSV三维集成技术虽然目 前在工艺上的成本较高,但是可以在元器件的 总体水平上降低制造成本。

设计顾问

磨削厚度

抛光厚度

厚度比

刻蚀厚度 指导试验

参数优化

基于机械化学抛光的晶圆减薄方法

表 部分TSV填孔方法比较

铜

钨

多晶硅

填孔材料

沉积方法

电镀 印刷

CVD

LPCVD

优点

电阻低 电阻低 热性能好

成本低 无需种子层

缺点

电镀时间长 成本高

电迁徙可靠 性

很难填充深孔

电阻大 热性能不好

拥有知识 Intel,IBM, 产权的公 TI, ST, 司和研究 Toshiba,

机构 Samsung等

MIT, IBM,

IZM, Infenion, Philips等

Leti, NEC, OKI, E比较

堆叠方法 工艺变动弹 良品 产量 制造成

性

率

本

晶圆/晶

低

圆

芯片/晶

中

圆

芯片/芯

高

片

低高

高

中中

中

高低

低

芯片/晶圆键合方法 -- 利用固液扩散低温键合。

,工艺不易实现自动化

➢静电可对芯片造 成伤害

表 四种主要精减薄方法的优缺点比较

工艺

示意 图

化学机械抛光

湿法蚀刻

减薄 介质

蚀刻 速率

蚀刻 效率

晶圆 强度

环境 污染

运营 成本

悬浮硬质颗粒 1 μm/min

氢氟酸+硝酸+ 乙酸

> 10 μm/min

低

高

高

高

硬质颗粒

氮氧化物

高/中

高

干法蚀刻

氟气 2 μm/min

脉冲激光源 脉冲激光

堆叠芯片

脉冲激光

晶圆/芯片

高分子

硅通孔

夹具

晶圆 绝缘层 粘接层

金属1 高分子材料 金属2

基于脉冲激光的芯片/晶圆键合方法

新型存储模组:

➢ 优良的电学性能 -- ASIC、DRAM 和 Flash间的电互连缩短至少两倍以 上,电性能(比如内存的读写速度)将会被大大地提高。 ➢ 超小的总体尺寸--没有金线键合、晶圆厚度减薄、没有衬垫,可缩小封 装的总体尺寸至少50%,而内存的容量还会增加至少一倍。 ➢ 多功能三维集成系统 -- 可以三维集成ASIC、DRAM和Flash芯片而形 成一个独立系统模组。

(a)键合前

CuVia BondingPad Metal 1 Metal 2 Metal 3 BondingLayer

(b)键合后

Cu-Sn、Au-Sn、Ni-Sn

芯片/晶圆键合方法 -- 利用脉冲激光在TSV结构间形成一层金属化合物, 把芯片/晶圆键合在一起。该方法具有工艺简单、成本低、产量高和可靠 性好等优点。

➢ 图像传感器为TSV的 第一个实际应用; ➢ 内存,包括闪存 (Flash)和动态内存 (DRAM)将占据最大 的市场; ➢ 微电机系统将是另一 个主要应用; ➢ 其它应用包括射频、

发光二极管等。

TSV技术的应用市场预测 (Yole Development, 2007)

四种主要的TSV工艺流程

DRIE 加工的不同深孔

电镀铜TSV结构的切面图

减薄到100微米的带TSV结构的晶圆

含有电镀铜TSV结构的1/4 晶圆

辅助圆片 Si

辅助圆片 Si

辅助圆片 Si

辅助圆片 Si

Si

深孔刻蚀:DRIE

绝缘层淀积 :淀积绝缘性的 SiO2/SiN/SiO2复合层

扩散阻挡层淀积 :化学镀或溅射淀积 TiW、TiN、TaN等

种子层:化学镀或溅射淀积Cu、W等

第五讲 三维系统级封装

封装堆叠

封装堆叠的可制造性和可靠性问题

➢ 翘曲和不平度:顶部底部翘曲不同会 造成焊锡结点在集成工艺中的失效;

➢ 净空(Stand-off):随着焊锡结点间 距的缩小,含锡球随之缩小,其所提 供的净空将不足以满足ASIC芯片对封 装的要求。

常规封装堆叠

ITRS三维互连技术路线图

干式胶贴粘接

静电吸盘

优 ➢高温下可使用

➢低温下无需清洁, ➢无温度限制

点 ➢保护易碎晶圆

高温下残留亦较少 ➢不使用粘接材料

➢适用于表面不平整之晶 ➢适于自动化生产 ➢无需清洁

圆

➢表面平整度好

缺 ➢融蜡后有残留

➢使用温度不能超

点 ➢蜡的化学性质稳定,不 过130oC

易被化学溶剂清洗

➢表面平整度差

➢粘接时间和脱模时间长

Samsung 利用 TSV技术堆叠 的 16G 内存芯片组

IBM 利用TSV技术堆叠的CPU 和内存芯片组

TSV三维集成技术是最近几年半导体工业中最热门的研究方向 -- 所有的大公司和著名研究机构都在开展这方面的技术研究和产 品开发。 TSV三维集成技术可以创造出很多应用 -- 从消费电子到无线 通讯,从生物到医学,从航空航天到汽车电子等:

不需要掩膜 可形成V型孔

成本高, 不能并行加工。

IBM

表 不同绝缘层材料比较

材料 优点

缺点

二氧化 硅

保形性

高残余 应力 电容大

氮氧化硅 保形性

低残余应力

电容大

有机高分子 聚合物

保形性 吸湿小 电容小 低热应力

增加刻蚀步 骤

难以填充小 孔

表 用于晶圆减薄的不同粘接技术比较

工

蜡或胶水粘接

艺

示 意 图