Spartan-3E开发板用户说明

Spartan3eDCMIP使用图文教程

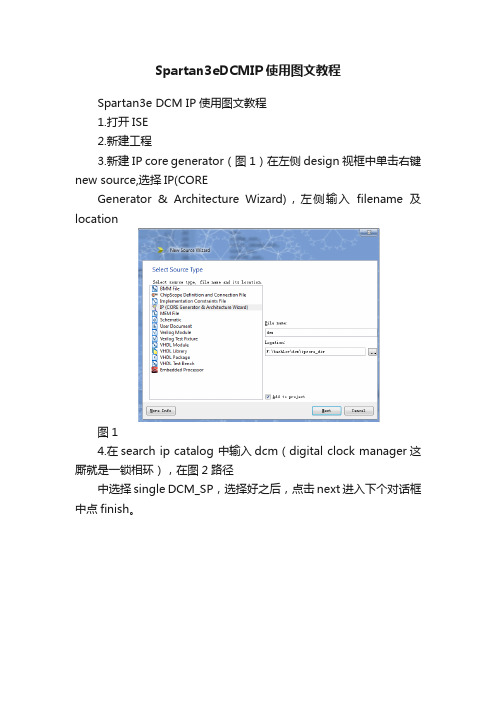

Spartan3eDCMIP使用图文教程Spartan3e DCM IP使用图文教程1.打开ISE2.新建工程3.新建IP core generator(图1)在左侧design视框中单击右键new source,选择IP(COREGenerator & Architecture Wizard),左侧输入filename及location图14.在search ip catalog 中输入dcm(digital clock manager这厮就是一锁相环),在图2路径中选择single DCM_SP,选择好之后,点击next进入下个对话框中点finish。

图25.选择HDL语言类型,综合工具,路径,器件封装包(如新建工程器件配置正确默认即可)图36.进入clocking wizard进行配置(这个是重点)图4图4a.图中有三路输入信号,CLKIN,CLKFB默认必须有(这两个不用管),RST为复位信号(可选,本例中勾选)b.Input clock frequency 可选为两个输入单位。

如图,频率和周期由用户自己配制,本例中输入频率为50Mhz。

c.Phase Shift相移可以自行配置为none\fixed\variable,本例中选择none.d.Clkin source信号源本例中设置为外部信号,单管输入。

(Differential是差分的意思)e.Feedback source反馈信号默认为内部信号,feedback value 默认。

f.输出端口可自行配置。

g.配置完毕点击next注解:整体端口说明CLKIN:输入时钟CLKFB:反馈时钟,主要是用于补偿延时‘输出;分内部反馈和外部反馈RST:复位信号PSEN:phase shift enabled,移相使能PSINCDEC:移相增减PSCLK:移相时钟CLK0~CLK270:分别为对输入移相0~270°输出CLKDV:分频输出,分配系数下面可以设置CLK2X/180:2倍频/反相输出CLKFX/180:频率合成/反相输出,即分数M/N倍输入的时钟输出,M,N设置在NEXT步骤里会有提到STATUS:8位输出总线,[2:0]有效,[7:3]悬空。

Spartan-3E实验开发板

第4章 Spartan-3E实验开发板

图4-13 显示内容左移

第4章 Spartan-3E实验开发板

图4-14 显示内容右移

第4章 Spartan-3E实验开发板 2.CG ROM . 字符发生只读存储器CG ROM保存的是已经定义好的具 体字符的字体位图,如图4-15所示。 对应字符的编码存储在DD RAM中,每个字符的位置与 CG ROM的位置按顺序对应,其中英文字符存储在CG ROM 相应的ASCII编码地址中。例如,要在液晶显示屏LCD的第 一行和第一个字符位置上显示字符“F”,该字所对应的编码 为46H,把编码46H写到DD RAM中对应的位置“00H”中。 如果要显示自定义字符和图形,控制芯片在DD RAM中保留 的00H与0X07H地址用于存放自定义的字符编码,而自定义 字符位图存储在CG RAM中。

第4章spartan3e实验开发板图410按键电路第4章spartan3e实验开发板43液?晶?显?示?屏实验开发板上设置了一个2行16字符液晶显示屏lcd液晶显示屏包含一个sitronixst7066u图形控制芯片虽然液晶显示屏控制芯片支持8位和4位数据总线与其它控制芯片的两种通信模式但是为了使fpga芯片能够连接更多的其它外围芯片节约fpga芯片的io管脚资源尽可能少占用fpga芯片的管脚通常采用与strataflash存储器芯片共用fpga的io管脚的方法

第4章 Spartan-3E实验开发板

图4-9 八个发光二极管电路

第4章 Spartan-3E实验开发板 4.按键 . 实验开发板的四个按键电路如图4-10所示。 按键开关的一个触点接3.3 V电源,另一个触点接FPGA 的I/O管脚。当需要使用这些按键时,为了得到非悬空的电 平,应该定义该FPGA的I/O管脚为带有下拉电阻的输入管脚。

Spartan 3E用户指南

Spartan-3E Starter Kit Board User GuideChapter 1: Introduction and OverviewChapter 2: Switches, Buttons, and KnobChapter 3: Clock SourcesChapter 4: FPGA Configuration OptionsChapter 5: Character LCD ScreenChapter 6: VGA Display PortChapter 7: RS-232 Serial PortsChapter 8: PS/2 Mouse/Keyboard PortChapter 9: Digital to Analog Converter (DAC)Chapter 10: Analog Capture CircuitChapter 11: Intel StrataFlash Parallel NOR Flash PROM Chapter 12: SPI Serial FlashChapter 13: DDR SDRAMChapter 14: 10/100 Ethernet Physical Layer Interface Chapter 15: Expansion ConnectorsChapter 16: XC2C64A CoolRunner-II CPLDChapter 17: DS2432 1-Wire SHA-1 EEPROMChapter 1:Introduction and Overview Spartan-3E入门实验板使设计人员能够即时利用Spartan-3E系列的完整平台性能。

设备支持:Spartan-3E、CoolRunner-II关键特性:Xilinx 器件: Spartan-3E (50万门,XC3S500E-4FG320C), CoolRunner™-II (XC2C64A-5VQ44C)与Platform Flash(XCF04S-VO20C)时钟:50 MHz晶体时钟振荡器存储器: 128 Mbit 并行Flash, 16 Mbit SPI Flash, 64 MByte DDR SDRAM连接器与接口:以太网10/100 Phy, JTAG USB下载,两个9管脚RS-232串行端口, PS/2类型鼠标/键盘端口, 带按钮的旋转编码器, 四个滑动开关,八个单独的LED输出, 四个瞬时接触按钮, 100管脚hirose扩展连接端口与三个6管脚扩展连接器显示器: VGA显示端口,16 字符- 2 线式LCD电源:Linear Technologies 电源供电,TPS75003三路电源管理IC市场:消费类, 电信/数据通信, 服务器, 存储器应用:可支持32位的RISC处理器,可以采用Xilinx的MicroBlaze 以及PicoBlaze嵌入式开发系统;支持DDR接口的应用;支持基于Ethernet网络的应用;支持大容量I/O扩展的应用。

FPGA开发板使用文档v1

Spartan-3E XC3S250E-4VQ100实验板用户使用说明第一章概述1、实验板资源Xilinx器件:Spartan-3E XC3S250E-4VQ100,XCF02SV020C(Platform Flash)时钟:50MHz晶体时钟振荡器;电源:USB接口供电,三路电源管理IC;接口:JTAG下载接口,PS/2,RS-232串行接口,4个按键开关,八个LED灯,4*4矩阵键盘,蜂鸣器;显示:VGA显示端口,4位七段数码管;存储器:EEPROM;图1-1 实验板资源示意图图1-2 实验板2、Spartan-3E XC3S250E-4VQ100简介主芯片:Spartan-3E XC3S250E-4VQ100CLB资源:•Rows: 34•Columns: 26•Total CLBs: 612Slice资源:•Total Slices: 2,448存储资源:•Distributed RAM Bits: 38K•Block RAM Bits: 216K时钟管理器:•DCM: 4逻辑单元:•System Gates: 250K•Equivalent Logic Cells: 5,508乘法器:•Dedicated Multipliers: 12I/O:•Total I/O:100•User I/O: 683、电源管理模块输入:5V DC,由USB接口提供;输出:3.3V DC,2.5V DC,1.2V DC。

图1-3 电源管理电路•VDD=3.3V:VDD引脚为I/O引脚,为I/O提供驱动电压。

•V AUX=2.5V:为JTAG模块和程序下载配置模块供电•VINT=1.2V:为内部调压器供电4、时钟/复位模块图1-4 时钟电路系统时钟由外部晶振提供,频率为50MHz,时钟的输入直接连到Bank0的输入全局缓冲I/O,时钟输入也可以连接到相应的DCM。

FPGA的Bank0的I/O的电压是由P82和P97供给的,板上已经将这两个引脚连接到3.3V,晶振可以达到预期的工作效果。

SPARTAN-3E说明书第7章

总述如图7-1所示,Spartan -3E 开发板有两个RS232串口:一个为DB9 DCE 母接头,另一个为DTE 公接头。

DCE 类型的串口可用标准直通串行线直接连接到大多数个人计算机和工作站。

不需要空调制解调器(Null Modem ),阴阳变换头或交叉线。

使用DTE 型的接口控制其他RS232外设,例如调制解调器或打印机,或与DCE 接口进行简单的回送测试。

图7-1 RS232串口 第七章RS232串口 DB9串口接头(前视) 标准9针串行线标准9针串行线DB9 DCE 母接头DB9 DTE 公接头RS232电平转换器(IC2)UG230_c7_01_022006图7-1显示了FPGA 和两个DB9接头之间的连接。

FPGA 使用LVTTL 或LVCMOS 电平输出串行数据给Maxim 公司的芯片,由它将逻辑值转换到合适的RS232电平。

相似的,Maxim 公司的芯片也会将RS232电平的串行输入数据转换到LVTTL 电平给FPGA 。

Maxim 芯片的输出脚和FPGA 的RXD 脚之间串接了电阻以防止偶发的逻辑冲突。

此接口不支持硬件流控制。

此接口的DCD ,DTR 和DSR 信号被连接到一起,如图7-1所示。

相似的,此接口的RTS 和CTS 信号也连接到一起。

UCF 位置约束图7-2和图7-3分别提供了DTE 和DCE 型RS232接口的UCF 约束,包括指定的IO 管脚和逻辑电平标准。

NET "RS232_DTE_RXD" LOC = "U8"| IOSTANDARD = LVTTL ; NET "RS232_DTE_TXD" LOC = "M13" | IOSTANDARD = LVTTL | DRIVE = 8 | SLEW = SLOW ;图7-2 DTE 型RS232串口的UCF 约束NET "RS232_DCE_RXD" LOC = "R7"| IOSTANDARD = LVTTL ; NET "RS232_DCE_TXD" LOC = "M14" | IOSTANDARD = LVTTL | DRIVE = 8 | SLEW = SLOW ;图7-3 DCE 型RS232串口的UCF 约束第七章:RS232串口。

SPARTAN-3E说明书第13章

Spartan -3E 开发板包括一个Micron Technology 公司的512Mbit (32Mx16)容量16位接口DDR SDRAM (MT46VM16),如图13-1所示。

DDR SDRAM 的所有管脚都连接到FPGA 的I/O Bank3。

I/O Bank3和DDR RAM 需要的2.5V 电源由LTC3412稳压芯片从板上5V 电源得到。

FPGA 和DDR SDRAM 共用的1.25V 的参考电压由2.5V 经电阻分压得到。

图13-1:Micron 512Mbit DDR SDRAM 的FPGA 接口DDR RAM 接口的所有信号都接有终端电阻。

第十三章DDR SDRAM UG230_c13_01_022406差分时钟脚SD_CK_P被反馈到FPGA的I/O Bank0的B9脚,以使FPGA的数字时钟管理器(DCM)获得最好效果。

MicroBlaze处理器的OPB DDR控制器需要连接这个时钟路径。

MicroBlaze处理器的OPB DDR控制器的IP核的相关文档可从EDK8.1i开发软件内获得(见107页“相关资源”)。

DDR SDRAM的连接表13-1显示FPGA与DDR SDRAM的连接。

表13-1 FPGA与DDR SDRAM的连接类型DDR SDRAM信号名FPGA管脚号功能SD_A12 P2SD_A11 N5SD_A10 T2SD_A9 N4SD_A8 H2SD_A7 H1SD_A6 H3SD_A5 H4SD_A4 F4SD_A3 P1SD_A2 R2SD_A1 R3地址SD_A0 T1地址输入表13-1 FPGA与DDR SDRAM的连接(续)种类DDR SDRAM信号名FPGA管脚号功能SD_DQ15 H5SD_DQ14 H6SD_DQ13 G5SD_DQ12 G6SD_DQ11 F2SD_DQ10 F1SD_DQ9 E1SD_DQ8 E2SD_DQ7 M6SD_DQ6 M5SD_DQ5 M4SD_DQ4 M3SD_DQ3 L4SD_DQ2 L3SD_DQ1 L1数据SD_DQ0 L2数据IOSD_BA1 K6SD_BA0 K5Bank地址输入SD_RAS C1SD_CAS C2SD_WE D1命令输入SD_CK_N J4SD_CK_P J5差分时钟输入SD_CKE K3 时钟使能输入,高电平有效SD_CS K4 片选输入,低电平有效SD_UDM J1 SD_LDM J2 数据屏蔽。

SPARTAN-3E说明书第5章

表 5-2 LCD/ StrataFlash 控制的相互影响

SF_CE0 SF_BYTE LCD_RW

操作

1

X

X

StrataFlas 禁用,完全的读写 LCD 能力

X

X

0

LCD 读操作禁用,完全的读写 StrataFlash

能力(译者:原文有误)

X

0

X

StrataFlash 处于字节(x8)位宽模式。高

NET "LCD_RW" LOC = "L17" | IOSTANDARD = LVCMOS33 | DRIVE = 4 | SLEW = SLOW ;

# LCD的4位数据接口与StrataFlash共享。

NET "SF_D<8>" LOC = "R15" | IOSTANDARD = LVCMOS33 | DRIVE = 4 | SLEW = SLOW ;

Function Set

0

Set CG RAM Address

0

Set DD RAM Address

第五章:字符型 LCD 显示屏

如果 StrataFlash 存储器处于字节(x8)位宽模式(SF_BYTE=Low),FPGA 应用程序具有完全 的同时读写 LCD 和 StrataFlash 存储器的能力。在字节位宽模式,StrataFlash 存储器不使用 SF_D<15:8>数据线。

UCF 位置约束

Spartan-3E Starter Kit Board User Guide UG230 (v1.0) March 9, 2006

45

大连理工大学微电子所 巢明 译

Spartan-3E开发板用户说明

附录:Spartan-3E开发板用户说明图1Spartan-3E多用途EDA实验开发平台(以下简称S3E实验平台),如图1所示,核心器件为XILINX公司的Spartan TM-3E器件XC3S500E,逻辑容量为50万门。

Spartan TM-3E借助于低成本的CPL,90nm工艺,满足了对大批量、I/O为核心的可编程逻辑解决方案的行业需求,是业界成本最低、性能最好的FPGA之一。

S3E实验平台在FPGA周围提供了丰富的资源,包括串口、PS/2接口、VGA接口、以太网接口、LED、LCD液晶显示、拨码旋钮开关和按钮、EPROM、A/D、D/A转换、电源、时钟等。

S3E的用户可以在PC机上通过USB JTAG电缆对FPGA进行配置,也可以通过SPI FLASH和NOR FLASH来配置。

1、S3E实验平台性能与特点●XILINX XC3S500E Spartan-3E FPGA:提供了最多232个I/O引脚和10000个逻辑单元。

●XILINX 4Mbit Flash配置PROM。

●XILINX XC2C64A CoolRunner系列CPLD:提供用户使用或辅助FPGA配置。

●64MByte、16位数据宽度、100MHz的DDR SDRAM接口。

●16MByte 并行INTEL公司的NOR FLASH:可存储FPGA配置信息或MicroBlaze指令序列。

●16Mbits ST半导体的SPI 串行FLASH:可存储FPGA配置信息或MicroBlaze指令序列。

●2行,每行可显示16个字符的LCD:用来显示FPGA输出信息。

●PS/2接口:用来外联键盘或鼠标,扩展输入设备●VGA接口:可显示64种颜色。

●10/100M以太网接口:提供了以太网物理层接口,便于MAC层IP的验证。

●两个标准RS232接口:可方便连接PC和其他工业设备进行数据传输。

●USB的下载接口配置接口。

●板载50MHz晶体振荡器。

SPARTAN-3E说明书第14章

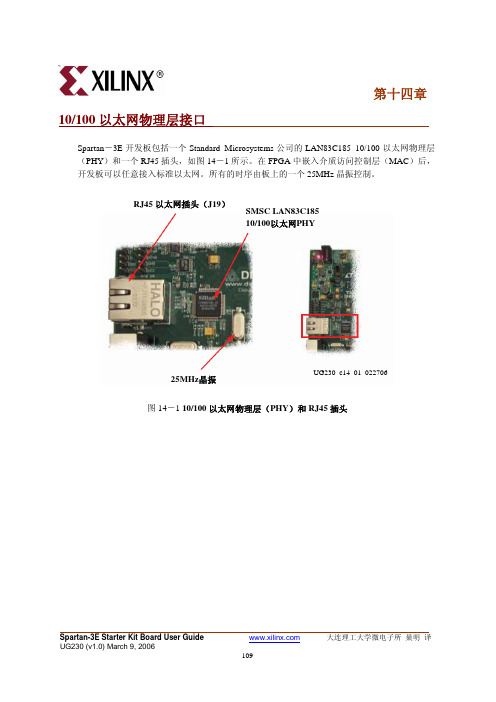

Spartan -3E 开发板包括一个Standard Microsystems 公司的LAN83C185 10/100以太网物理层(PHY )和一个RJ45插头,如图14-1所示。

在FPGA 中嵌入介质访问控制层(MAC )后,开发板可以任意接入标准以太网。

所有的时序由板上的一个25MHz 晶振控制。

图14-1 10/100以太网物理层(PHY )和RJ45插头第十四章10/100以太网物理层接口 RJ45以太网插头(J19)SMSC LAN83C18510/100以太网PHY25MHz 晶振 UG230_c14_01_022706以太网物理层的连接FPGA经由一个标准的介质无关接口(MII)连接到LAN83C185以太网物理层芯片,如图14-2所示。

接口信号和FPGA管脚号的详细信息见表14-1。

图14-2 FPGA通过MII连接到以太网PHY表14-1 FPGA与LAN83C185以太网PHY的连接信号名FPGA管脚号功能E_TXD<4> R6E_TXD<3> T5E_TXD<2> R5E_TXD<1> T15E_TXD<0> R11发送数据给PHY。

E_TXD<4>也是MII传送错误信号。

E_TX_EN P15 允许发送。

E_TX_CLK T7 发送时钟。

100Base-TX模式为25 MHz,10Base-T模式为2.5 MHzE_RXD<4> U14E_RXD<3> V14E_RXD<2> U11E_RXD<1> T11E_RXD<0> V8从PHY接收数据。

E_RX_DV V2 接收数据有效。

UG230_c14_02_022706表14-1 FPGA 与LAN83C185以太网PHY 的连接(续) 信号名 FPGA管脚号 功能E_RX_CLK V3 接收时钟。

SPARTAN-3E说明书第2章

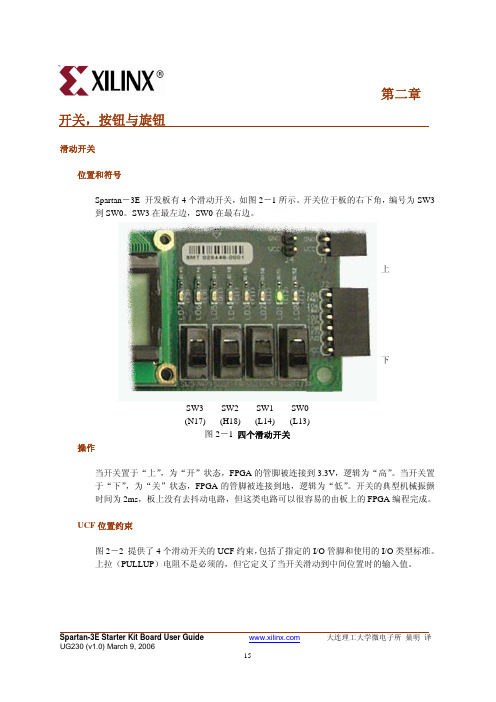

滑动开关位置和符号Spartan -3E 开发板有4个滑动开关,如图2-1所示。

开关位于板的右下角,编号为SW3到SW0。

SW3在最左边,SW0在最右边。

SW3 SW2 SW1 SW0 (N17) (H18) (L14) (L13)图2-1 四个滑动开关操作当开关置于“上”,为“开”状态,FPGA 的管脚被连接到3.3V ,逻辑为“高”。

当开关置于“下”,为“关”状态,FPGA 的管脚被连接到地,逻辑为“低”。

开关的典型机械振颤时间为2ms ,板上没有去抖动电路,但这类电路可以很容易的由板上的FPGA 编程完成。

UCF 位置约束图2-2 提供了4个滑动开关的UCF 约束,包括了指定的I/O 管脚和使用的I/O 类型标准。

上拉(PULLUP )电阻不是必须的,但它定义了当开关滑动到中间位置时的输入值。

第二章开关,按钮与旋钮 上 下NET "SW<0>" LOC = "L13" | IOSTANDARD = LVTTL | PULLUP ; NET "SW<1>" LOC = "L14" | IOSTANDARD = LVTTL | PULLUP ; NET "SW<2>" LOC = "H18" | IOSTANDARD = LVTTL | PULLUP ; NET "SW<3>" LOC = "N17" | IOSTANDARD = LVTTL | PULLUP ;图2-2 滑动开关的UCF 约束按钮开关位置和符号Spartan -3E 开发板有4个按钮开关,如图2-3所示。

开关位于板的左下角,编号为BTN_NORTH ,BTN_EAST ,BTN_SOUTH ,BTN_WEST 。

连接开关的FPGA 管脚见图2-3的括号内,以及图2-5的UCF 文件中。

Spartan 3E用户指南的中文翻译part4

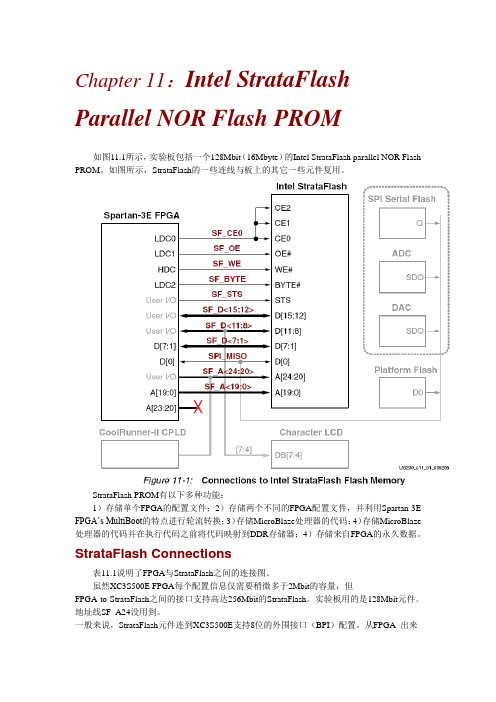

Chapter 11:Intel StrataFlash Parallel NOR Flash PROM如图11.1所示,实验板包括一个128Mbit(16Mbyte)的Intel StrataFlash parallel NOR Flash PROM。

如图所示,StrataFlash的一些连线与板上的其它一些元件复用。

StrataFlash PROM有以下多种功能:1)存储单个FPGA的配置文件;2)存储两个不同的FPGA配置文件,并利用Spartan-3E FPGA’s MultiBoot的特点进行轮流转换;3)存储MicroBlaze处理器的代码;4)存储MicroBlaze 处理器的代码并在执行代码之前将代码映射到DDR存储器;4)存储来自FPGA的永久数据。

StrataFlash Connections表11.1说明了FPGA与StrataFlash之间的连接图。

虽然XC3S500E FPGA每个配置信息仅需要稍微多于2Mbit的容量,但FPGA-to-StrataFlash之间的接口支持高达256Mbit的StrataFlash。

实验板用的是128Mbit元件。

地址线SF_A24没用到。

一般来说,StrataFlash元件连到XC3S500E支持8位的外围接口(BPI)配置。

从FPGA 出来的高4位并没有直接连到StrataFlash。

相反,在配置时由XC2C64 CPLD控制这些管脚。

正如表11.1所示,StrataFlash的一些连线与其它一些器件复用。

Shared Connections除了StrataFlash的一些连线与其它一些器件复用外,StrataFlash的一些存储空间也与其它器件复用。

Character LCD字符LCD采用4位的数据接口。

显示数据的连线同样与StrataFlash PROM上的信号线SF_D<11:8>复用。

如表11.2所示,FPGA通过SF_CE0和LCD_RW信号线来控制StrataFlash PROM的访问通道或字符LCD的读状态。

SPARTAN-3E说明书第10章

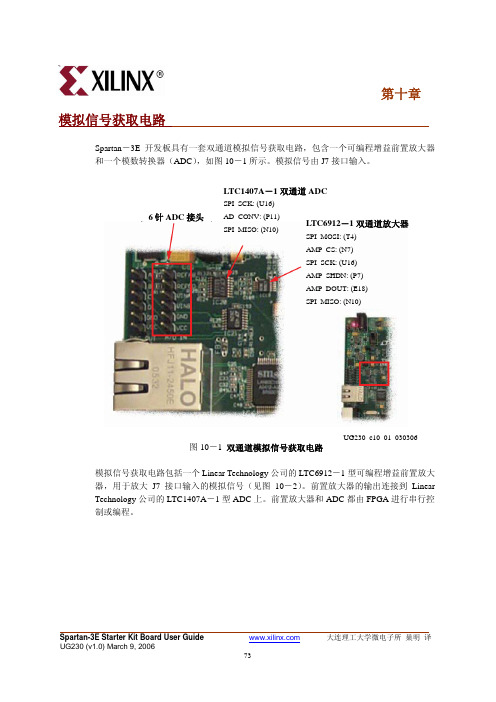

Spartan -3E 开发板具有一套双通道模拟信号获取电路,包含一个可编程增益前置放大器和一个模数转换器(ADC ),如图10-1所示。

模拟信号由J7接口输入。

图10-1 双通道模拟信号获取电路模拟信号获取电路包括一个Linear Technology 公司的LTC6912-1型可编程增益前置放大器,用于放大J7接口输入的模拟信号(见图10-2)。

前置放大器的输出连接到Linear Technology 公司的LTC1407A -1型ADC 上。

前置放大器和ADC 都由FPGA 进行串行控制或编程。

第十章模拟信号获取电路 6针ADC 接头LTC1407A -1双通道ADC SPI_SCK: (U16) AD_CONV: (P11) SPI_MISO: (N10)LTC6912-1双通道放大器SPI_MOSI: (T4) AMP_CS: (N7) SPI_SCK: (U16) AMP_SHDN: (P7) AMP_DOUT: (E18) SPI_MISO: (N10)UG230_c10_01_030306图10-2 模拟信号获取电路详图从模拟输入到数字输出模拟信号获取电路将VINA 或VINB 上输入的模拟电压信号转换为D[13:0]上的14位数字表示,见方程10-1。

[]819225.165.10:13×−×=VVV GAIN D IN方程10-1GAIN 是装入可编程前置放大器的当前增益设置。

可用的不同增益设置和允许的VINA 和VINB 输入电压范围见表10-2。

放大器和ADC 的参考电压都是1.65V ,由图10-2所示的分压器产生。

因此, VINA 和VINB 上的输入电压都被减去了1.65V 。

ADC 的最大输入范围是±1.25V ,以参考电压1.65V 为中心。

因此出现在输入模拟信号的分母上的是1.25V 。

UG230_c10_02_022306接头J7最终,ADC提供一个14位,二进制补码形式的数字输出。

SPARTAN-3E说明书第16章

Spartan -3E 开发板包括一个Xilinx 公司的XC2C64A 型CoolRunner -II 复杂可编程逻辑器件(CPLD )。

此CPLD 可由用户编程,可用于客户的应用设计。

CPLD 的一部分保留用于协调FPGA的不同配置存储器的行为,即Xilinx Platform Flash PROM 和Intel StrataFlash PROM 。

因此,除了完成用户的应用程序,CPLD 还必须提供以下功能:当FPGA 使用主动串行配置模式(FPGA_M<2:0>=000)时,给XCF04S Platform Flash PROM提供一个低电平有效的使能信号。

在所有其他配置模式,Platform Flash PROM 都处于禁用状态。

CPLD 帮助减少了开发板上的跳线,简化了FPGA 配置存储器间的相互影响。

当FPGA 使用BPI -Up 配置模式(FPGA_M<2:0>=010,DONE=0)时,将StrataFlash PROM的高5位地址线A[24:20]设置为00000。

当FPGA 使用BPI -Down 配置模式(FPGA_M<2:0>=011,DONE=0)时,将StrataFlash PROM 的高5位地址线A[24:20]设置为11111。

在非BPI 配置模式,或当FPGA 的DONE 管脚为高的任何时候,将高5位地址线设置为ZZZZZ (高阻)。

这种行为与BPI 模式下的FPGA 高位地址的行为是一致的。

那么为什么要增加一个CPLD 来模仿这种行为?将来的参考设计将演示这种独特的配置方式的能力。

在典型的BPI 配置方式中是不需要CPLD 的。

除了以上需要的CPLD 功能,还有13到21个用户IO 管脚和58个宏单元(Macrocell )可供用户使用。

跳线JP10(WDT_EN )定义了CPLD 的XC_WDT_EN 信号的状态。

默认的不插跳线帽,信号被上拉到逻辑高。

SPARTAN-3E说明书第1章

感谢您购买Xilinx 公司的Spartan TM -3E 开发板。

您将发现它对您开发Spartan -3E FPGA应用设计有帮助。

根据您的需要选择开发板根据特定的需要,选择最适合您需要的Xilinx 开发板。

Spartan -3E FPGA 的特性和嵌入的处理器功能Spartan -3E 开发板突出了Spartan -3E 系列FPGA 的独特性能,给嵌入处理器的应用设计提供了一种方便的开发板。

开发板突出了以下特性:Spartan -3E 特性用并行NOR Flash 进行配置用并行NOR Flash 程序存储器进行多重配置(MultiBoot )用SPI 串行Flash 进行配置嵌入式开发MicroBlaze TM 32位嵌入式RISC 处理器PicoBlaze TM 8位嵌入式控制器DDR 存储器接口学习Xilinx FPGA ,CPLD 和ISE 开发软件的基础知识Spartan -3E 开发板比其他的一些Spartan 开发板更先进和复杂。

要学习Xilinx FPGA 或CPLD 设计以及ISE 开发工具的基础知识,请考虑使用High V olume Starter Kit Bundle 批量开发板套装,它以普及性的价格提供了Spartan -3的开发板和XilinxCoolRunner TM -II/XC9500XL CPLD 的开发板。

High Volume Starter Kit Bundle (HW-SPAR3-CPLD-DK)/xlnx/xebiz/designResources/ip_product_details.jsp?key=HW-SPAR3-CPLD-DK高级的Spartan -3系列开发板Spartan -3E 开发板演示了MicroBlaze 嵌入式处理器和Xilinx Embedded Development Kit嵌入式开发软件的基本能力。

如果更高级的开发需要更多的外设和FPGA 逻辑,第一章介绍和概述请考虑使用SP-305开发板:Spartan-3 SP-305 Development Board (HW-SP305-xx)/xlnx/xebiz/designResources/ip_product_details.jsp?key=HW-SP305-US或者考虑使用Xilinx的合作公司提供的可用的电路板Spartan-3 and Spartan-3E Board Interactive Search/products/devboards/index.htm关键器件和特性Spartan-3E开发板的关键特性是:• Xilinx XC3S500E Spartan-3E FPGA♦最多232 个用户IO管脚♦ 320脚FBGA封装♦超过10,000个逻辑单元• Xilinx 4 Mbit Platform Flash配置程序存储器• Xilinx 64宏单元XC2C64A CoolRunner CPLD• 64 MByte (512 Mbit) DDR SDRAM, 16位数据接口, 100+ MHz速度• 16 MByte (128 Mbit) 并行NOR Flash (Intel StrataFlash)♦ FPGA配置存储器♦ MicroBlaze 代码存储器/影射• 16 Mbits SPI串行Flash (STMicro)♦ FPGA配置存储器♦ MicroBlaze代码影射• 2行16字符LCD屏幕• PS/2鼠标或键盘接口• VGA显示接口• 10/100以太网物理层(PHY)(需要FPGA中的以太网MAC)• 两个9针RS-232接口 (DTE和DCE类型)• 基于板载USB接口的FPGA/CPLD下载/调试接口• 50 MHz时钟振荡器• 具有SHA-1加密算法的单线串行EEPROM用于比特流数据的版权保护• Hirose FX2扩展接口• 三个Digilent 6脚扩展接口• 四路输出,基于SPI的数模转换器(DAC)• 两路输入,基于SPI的模数转换器(ADC)和可编程增益前置放大器• ChipScope™ SoftTouch调试接口• 带有按钮功能的凸轮旋转编码器• 八个分立LED灯• 四个滑动开关• 四个按钮开关• SMA时钟输入• 给任意时钟发生芯片的8脚DIP封装接口设计上的折中为了让Spartan-3E开发板具有最多的功能,采用了几项系统级的折中设计。

Spartan-3E_FPGA_中文数据手册_摘要

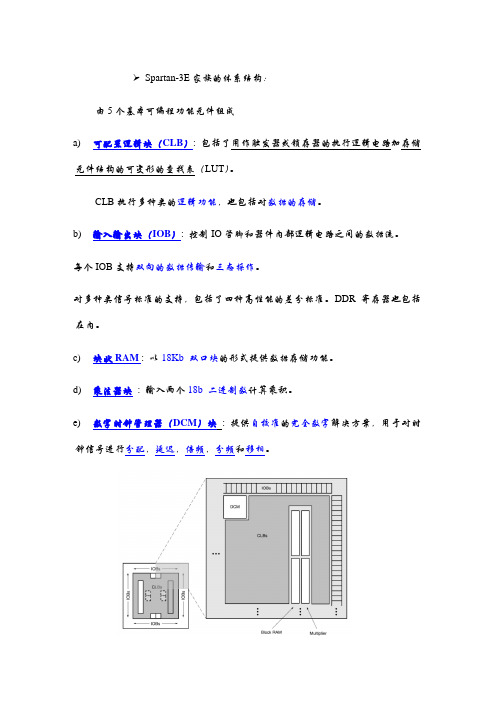

➢Spartan-3E家族的体系结构:由5个基本可编程功能元件组成a)可配置逻辑块(CLB): 包括了用作触发器或锁存器的执行逻辑电路加存储元件结构的可变形的查找表(LUT)。

CLB执行多种类的逻辑功能,也包括对数据的存储。

b)输入输出块(IOB): 控制IO管脚和器件内部逻辑电路之间的数据流。

每个IOB支持双向的数据传输和三态操作。

对多种类信号标准的支持,包括了四种高性能的差分标准。

DDR寄存器也包括在内。

c)块状RAM : 以18Kb 双口块的形式提供数据存储功能。

d)乘法器块: 输入两个18b 二进制数计算乘积。

e)数字时钟管理器(DCM)块: 提供自校准的完全数字解决方案,用于对时钟信号进行分配,延迟,倍频,分频和移相。

互连所有五种功能元件并在它们之间传输信号的发达路径网络是Spartan-3E家族的特点。

每个功能元件都关联到一个开关矩阵,使得布线有多种连接路径。

➢Configuration:对Spartan-3E进行编程是通过加载存储于可靠的、可擦写的、静态CMOS 配置锁存器(CCL)里面的配置数据。

FPGA的配置数据是存储于外部的PROM或者是其他非易失性媒体,无论其是否在板上。

在上电后,配置数据就写进FPGA,这有7种不同方式:a)从赛灵思Platform Flash PROM 读取的主动串行方式。

b)从工业标准SPI串行Flash读取的串行外设接口SPI方式。

c)从工业标准的×8或×8/×16 并行NOR Flash 向上或向下读取的字节外设接口BPI方式。

d)被动串行方式,以从处理器下载为典型。

e)被动并行方式,以从处理器下载为典型。

f)边界扫描(JTAG),以从处理器或系统调试器下载为典型。

➢I/O Capabilities__IO能力Spartan-3E的SelectIO接口支持许多流行的单端和差分标准。

表二列举用户IO数量和对应于各种器件与封装的不同组合的可用差分对数量。

為希科技 Sparatn3E XC3S250E-PQ208 3S250E 實驗板 说明书

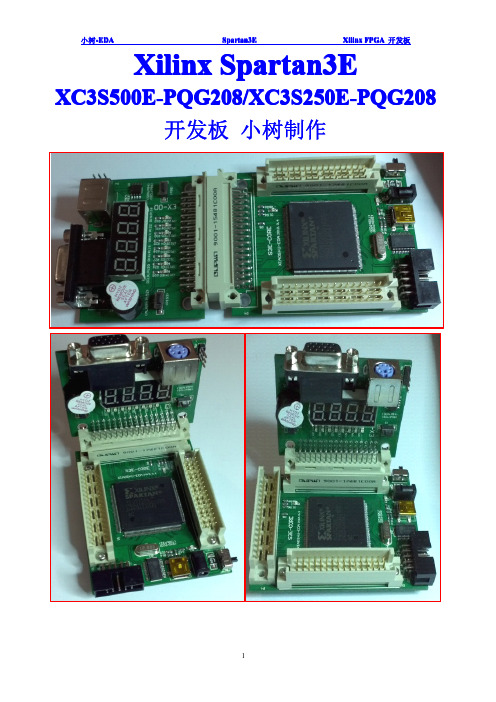

為希科技Sparatn3E XC3S250E-PQ208 3S250E實驗板使用手冊2007.Jan.15 .V1.0Ulinx Corp.為希科技有限公司的UBD-Spartan3E-ST3E實驗板提供FPGA使用者一個完整且容易上手的實驗平台.這份手冊將會含括這片實驗板上所有元件的設定及特性說明.主要元件及功能Ulin_MB_XC3S250E實驗板由兩塊板子組合而成,上板為HUMAN_IO,下板為Ulinx_MB_XC3S250E_PQ208,組成一個完整的實驗板,如圖 1-1 所示.第一章 : Ulinx_MB_XC3S250E_PQ208規格Ulinx_MB_XC3S250E_PQ208 FPGA板包含了以下主要元件:● 25萬邏輯閘的Xilinx Spartan-3E XC3S250E FPGA 包裝為PQFP 208 隻腳位 (XC3S250E-4-PQ208). 內含12個 18K-bit 的Block RAMs (共216K bits). 內含12個 18x18 硬體乘法器. 內含4 個Digital Clock Managers (DCMs). 內含158 個可用腳位● RS-232 界面● PROM XCF02S-VO20● 40MHz的振盪晶體.● 一個使用者振盪晶體的Socket● 92點 User IO,可連接Human IO,或連接使用者設計的板子.● 8 個DIP switch● 8 個LED輸出界面● 8個按鍵輸入● 單一電源輸入( +5V/ 3A ).提供板子上三組電源使用 ( 1.2 V , 2.5 V , 3.3 V 與一預留的1.8V)● JTAG 界面提供多種燒錄程式的界面Human_IO板包含了以下主要元件:● LCD液晶螢幕(128 x 64 Pixels)(可以選購16 x 2 Text Mode 液晶螢幕)● 16 字按鍵(4 x 4矩陣形,可以輸入0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F等字元).● 16 個LED輸出介面(8個綠色LED,8個紅色LED)● 4 個按鍵輸入.● 4 個 DIP Switch輸入● 8 個七節燈管顯示輸出.● VGA輸出介面.● PS2 輸入介面.● Rotary Switch 輸入.(可以設定 0,1,2,3,4,5,6,7,8,9)● 4個頻道DAC輸出(LTC2624)● 2個頻道ADC輸入(ADC0832)● IIC 介面(24C02).產品外觀第二章 : Ulinx_MB_XC3S250E_PQ208Ulinx_MB_XC3S250E_PQ208為MB_XC3S250E的主板,包含電源,FPGA,LED…等週邊介面,再利用J1,J2連接Human_IO板,本章節主要是敘述MB_XC3S250E主板相關週邊電路的相關說明.2-1. 電源.電源插頭J8為外部 5 V 輸入,內正外負的接頭,提供板子的電源輸入,在J8的右邊為:S10的切換開關, S10切到右邊時,電源開啟;S10切到左邊時,電源關閉.Ulinx_MB_XC3S250E以內部的穩壓器,將+5V穩壓成+3.3V,+2.5V,+1.8V,+1.2V等四種電源,其中+1.8V為預留未來使用,而+3.3V,+2.5V,+1.2V則提供Ulinx_MB_XC3S250E 板子使用,這四種電源則有D1,D2,D3,D4綠色LED顯示電源正常.D1:板子上1.2V的電壓正常時時 ; D1綠色 LED為亮D2:板子上2.5V的電壓正常時時 ; D2綠色 LED為亮D3:板子上3.3V的電壓正常時時 ; D3綠色 LED為亮D4:板子上1.8V的電壓正常時時 ; D4綠色 LED為亮另外這四種電源,加上+5V電源,則可以由J4輸出.J4 Connector Pin Pin Name Signal Comment6 Ground 電源的地電位5 1.2V 1.2V電源4 1.8V 1.8V電源3 2.5V 2.5V電源2 3.3V 3.3V電源1 5V 5V電源2-2. RS232介面RS232介面提供Ulinx_MB_XC3S250E 板子與PC 個人電腦之間串列傳輸的介面,板子上的P2就是RS232接頭,為一個DB9母接頭,只要以1對1的連接線連接P2與PC 個人電腦串列介面.NET "RS232_TX" LOC = "P45" ; NET "RS232_RX" LOC = "P71" ;8 13 11 9P45P71Spartan 3E MAX32212-3. CLOCK 時脈週期實驗板上有兩個CLOCK輸入,板子上的GCLK1為40MHz的振盪晶體,接到FPGA的Pin-80,而GCLK2則提供使用者自行提供使用者所需的振盪晶體,此接腳接到FPGA的Pin-183.NET "GCLK1" LOC = "P80" ;NET "GCLK2" LOC = "P183" ;2-4. PUSH_BUTTON 與 DIP_SWITCH輸入實驗板上有8個PUSH_BUTTON與八個DIP_SWICTH,位於板子的最下方,當PUSH_BUTTON按下時,輸入的電壓準位為低電位’0’;當不按時為’1’當DIP_SWITCH往下切為[ON]時,輸入電壓準位為低電位’0’;而上切時為[OFF]. NET "DIP_SWITCH<0>" LOC = "P159" ;NET "DIP_SWITCH<1>" LOC = "P169" ;NET "DIP_SWITCH<2>" LOC = "P194" ;NET "DIP_SWITCH<3>" LOC = "P204" ;NET "DIP_SWITCH<4>" LOC = "P54" ;NET "DIP_SWITCH<5>" LOC = "P91" ;NET "DIP_SWITCH<6>" LOC = "P101" ;NET "DIP_SWITCH<7>" LOC = "P58" ;NET "PUSH_BUTTON<7>" LOC = "P154" ;NET "PUSH_BUTTON<6>" LOC = "P148" ;NET "PUSH_BUTTON<5>" LOC = "P142" ;NET "PUSH_BUTTON<4>" LOC = "P136" ;NET "PUSH_BUTTON<3>" LOC = "P130" ;NET "PUSH_BUTTON<2>" LOC = "P124" ;NET "PUSH_BUTTON<1>" LOC = "P118" ;NET "PUSH_BUTTON<0>" LOC = "P110" ;FPGA PIN SYMBOL LABEL NAME LOGIC COMMENT P110 S2 USER_SW8按下時,輸入為’0’P118 S3 USER_SW7按下時,輸入為’0’P124 S4 USER_SW6按下時,輸入為’0’P130 S5 USER_SW5按下時,輸入為’0’P136 S6 USER_SW4按下時,輸入為’0’P142 S7 USER_SW3按下時,輸入為’0’P148 S8 USER_SW2按下時,輸入為’0’P154 S9 USER_SW1按下時,輸入為’0’P159 S1-1 USER_DIP1P169 S1-2 USER_DIP2P194 S1-3 USER_DIP3P204 S1-4 USER_DIP4USER_DIP5P54 S1-5USER_DIP6P91 S1-6P101 S1-7 USER_DIP7USER_DIP8P58 S1-82-5. LED 輸出實驗板上有8個LED綠色LED,當輸出高電位’1’時,LED亮,當輸出低電位’0’時,LED不亮.NET "LED<7>" LOC = "P76" ;NET "LED<6>" LOC = "P98" ;NET "LED<5>" LOC = "P55" ;NET "LED<4>" LOC = "P61" ;NET "LED<3>" LOC = "P60" ;NET "LED<2>" LOC = "P63" ;NET "LED<1>" LOC = "P62" ;NET "LED<0>" LOC = "P65" ;FPGA PIN SYMBOL LABEL NAME LOGIC COMMENT P65 D7 USER_LED1輸出’1’ÎD7亮起P62 D8 USER_LED2輸出’1’ÎD8亮起P63 D9 USER_LED3輸出’1’ÎD9亮起USER_LED3P60 D10輸出’1’ÎD10亮起P61 D11USER_LED4輸出’1’ÎD11亮起USER_LED5P55 D12輸出’1’ÎD12亮起USER_LED6P98 D13輸出’1’ÎD13亮起P76 D14USER_LED7輸出’1’ÎD14亮起2-6. J1 CONNECTOR (A2_CONNECTOR)J1提供46點輸出/輸入介面,提供板子擴充IO之用,其輸出準位為標準的+3.3V介面.Human_IO BOARD FPGAPINSYMBOL J1J1SYMBOL FPGAPINHuman_IOBOARD GND1 2 +5V7_SEG_A1 P181A2_IO1 3 4 A2_IO2 P180 7_SEG_A2 7_SEG_A3 P186A2_IO3 5 6 A2_IO4 P185 7_SEG_A4 7_SEG_A5 P190A2_IO5 7 8 A2_IO6 P189 7_SEG_A6 7_SEG_A7 P193A2_IO7 9 10A2_IO8 P192 7_SEG_A8 7_SEG_CA P197A2_IO9 1112A2_IO10 P196 7_SEG_CB 7_SEG_CC P200A2_IO111314A2_IO12 P199 7_SEG_CD 7_SEG_CE P203A2_IO131516A2_IO14 P202 7_SEG_CF 7_SEG_CG P206A2_IO151718A2_IO16 P205 7_SEG_DP LCD_RST P107 A2_IO17 1920A2_IO18 P106 LCD_CS2 LCD_CS1 P109 A2_IO19 2122A2_IO20 P108 LCD_D7LCD_D6 P113 A2_IO21 2324A2_IO22 P112 LCD_D5LCD_D4 P116 A2_IO23 2526A2_IO24 P115 LCD_D3LCD_D2 P120 A2_IO25 2728A2_IO26 P119 LCD_D1LCD_D0 P123 A2_IO27 2930A2_IO28 P122 LCD_ELCD_RW P127 A2_IO29 3132A2_IO30 P126 LCD_IOPS2_CLK P129 A2_IO31 3334A2_IO32 P128 PS2_DATA USER_SW1 P133A2_IO33 3536A2_IO34 P132 USER_SW2 USER_SW3 P135A2_IO35 3738A2_IO36 P134 USER_SW4 USER_DIP1 P138 A2_IO37 3940A2_IO38 P137 USER_DIP2 USER_DIP3 P140 A2_IO39 4142A2_IO40 P139 USER_DIP4 ROT_IN1 P145A2_IO414344A2_IO42 P144 ROT_IN2 ROT_IN3 P147A2_IO434546A2_IO44 P146 ROT_IN4 IIC_SCL P151 A2_IO45 4748A2_IO46 P150 IIC_SDA+2.5V4950+3.3V2-7. J2 CONNECTOR(A1_CONNECTORJ2提供46點輸出/輸入介面,提供板子擴充IO 之用,其輸出準位為標準的+3.3V 介面. Human_IO BOARD FPGA PIN SYMBOL J2J2SYMBOL FPGA PIN Human_IO BOARD GND 1 2 +5VD16(綠色LED) P3 A1_IO13 4 A1_IO2 P2 D15(綠色LED) D14(綠色LED) P5 A1_IO35 6 A1_IO4 P4 D13(綠色LED) D12(綠色LED) P9 A1_IO57 8 A1_IO6 P8 D11(綠色LED) D10(綠色LED) P12 A1_IO7 9 10A1_IO8 P11 D9 (綠色LED) D8 (紅色LED) P16 A1_IO9 1112A1_IO10 P15 D7 (紅色LED)D6 (紅色LED) P19 A1_IO111314A1_IO12 P18 D5 (紅色LED) D4 (紅色LED) P23 A1_IO131516A1_IO14 P22 D3 (紅色LED) D2 (紅色LED) P25 A1_IO151718A1_IO16 P24 D1 (紅色LED) KEY_IN4 P29 A1_IO17 1920A1_IO18 P28 KEY_IN3 KEY_IN2 P31 A1_IO19 2122A1_IO20 P30 KEY_IN1 KEY_OUT4 P34 A1_IO21 2324A1_IO22 P33 KEY_OUT3 KEY_OUT2 P36 A1_IO23 2526A1_IO24 P35 KEY_OUT1 EXT_OUT1 P40 A1_IO25 2728A1_IO26 P39 EXT_OUT2 EXT_OUT3 P42 A1_IO27 2930A1_IO28 P41 EXT_OUT4 EXT_IN1 P48 A1_IO29 3132A1_IO30 P47 EXT_IN2 EXT_IN3 P50 A1_IO31 3334A1_IO32 P49 EXT_IN4ADC_CS P187 A1_IO33 3536A1_IO34 P179 ADC_CLK ADC_DO P161 A1_IO35 3738A1_IO36 P160 ADC_DI DAC_CS P163 A1_IO37 3940A1_IO38 P162 DAC_CLK DAC_DI P165 A1_IO39 4142A1_IO40 P164 DAC_DOVGA_VSYNC P168 A1_IO41 4344A1_IO42 P167 VGA_HSYNC VGA_B P172 A1_IO43 4546A1_IO44 P171 VGA_G VGA_R P178 A1_IO45 4748A1_IO46 P177 DAC_CLR +2.5V 4950+3.3V2-8. FPGA ConfigurationFPGA Configuration提供使用者將自己設計的檔案輸入給FPGA,而一般FPGA 提供2種Download的方式,其一為JTAG,其一為Master Salve兩種.[第一種]: In_System Programming透過JTAG與ISE軟體的Impact,可以將使用者程式Download到FPGA,這一種方式的介面相關電路已包含於板子之中,利用DB25的連接線,連接電腦的Printer Port與Ulinx_MB_XC3S250E_PQ208的P1,就可以利用Impact來 Download.使用前請確認J6的Connector已經將4個短路跳線座裝好,如圖所示(若你想用現成Parallel_Cable_III 或 Parallel_Cavle_IV來Download的話,則可以利用J3來連接,但需將J6的短路跳線座移除,使其成為開路狀態).[第二種方式]: Master Slave這種方式,需將板子的J5以短路跳線座,將J5短路,而JTAG在Download時,需將Bit 檔轉換成mcs檔.2-9. FPGAUlinx_MB_XC3S250E_PQ208為FPGA,使用Xilinx的Sparatn3E的XC3S250E 元件,其包裝為PQ208,其相關接腳如表所示.Pin No Signal Name I/O FPGA Pin NameP1 PROG_BP2 A1_IO2 O IO_L01P_3P3 A1_IO1 O IO_L01N_3P4 A1_IO4 O IO_L02P_3P5 A1_IO3 O IO_L02N_3/VREF_3P6 IPP7 VCCAUXP8 A1_IO6 O IO_L03P_3P9 A1_IO5 O IO_L03N_3P10 GNDP11 A1_IO8 O IO_L04P_3P12 A1_IO7 O IO_L04N_3P13 VCCINTP14 IPP15 A1_IO10 O IO_L05P_3P16 A1_IO9 O IO_L05N_3P17 GNDP18 A1_IO12 O IO_L06P_3P19 A1_IO11 O IO_L06N_3P20 I IP/VREF_3P21 VCCO_3P22 A1_IO14 O IO_L07P_3/LHCLK0P23 A1_IO13 O IO_L07N_3/LHCLK1P24 A1_IO16 O IO_L08P_3/LHCLK2P25 A1_IO15 O IO_L08N_3/LHCLK3/IRDY2P26 IPP27 GNDP28 A1_IO18 I IO_L09P_3/LHCLK4/TRDY2P29 A1_IO17 I IO_L09N_3/LHCLK5P30 A1_IO20 I IO_L10P_3/LHCLK6Pin No Signal Name I/O FPGA Pin NameP31 A1_IO19 I IO_L10N_3/LHCLK7P32 IPP33 A1_IO22 O IO_L11P_3P34 A1_IO21 O IO_L11N_3P35 A1_IO24 O IO_L12P_3P36 A1_IO23 O IO_L12N_3P37 GNDP38 VCCO_3P39 A1_IO26 IO_L13P_3P40 A1_IO25 IO_L13N_3P41 A1_IO28 IO_L14P_3P42 A1_IO27 IO_L14N_3P43 IPP44 VCCAUXP45 RS232_TX O IO/VREF_3P46 VCCO_3P47 A1_IO30 IO_L15P_3P48 A1_IO29 IO_L15N_3P49 A1_IO32 O IO_L16P_3P50 A1_IO31 IO_L16N_3P51 IPP52 GNDP53 GNDP54 DIP_SWITCH_5 I IPP55 LED3 O IO_L01P_2/CSO_BP56 IO_L01N_2/INIT_BP57 IP_L02P_2P58 DIP_SWITCH_8 I IP_L02N_2P59 VCCO_2P60 LED5 O IO_L03P_2/DOUT/BUSY P61 LED4 O IO_L03N_2/MOSI/CSI_B P62 LED6 O IO_L04P_2P63 LED7 O IO_L04N_2P64 IO_L05P_2Pin No Signal Name I/O FPGA Pin NameP65 LED8 O IO_L05N_2P66 VCCAUXP67 VCCINTP68 IO_L06P_2P69 IO_L06N_2P70 GNDP71 RS232_RX I IP_L07P_2P72 IP_L07N_2/VREF_2P73 VCCO_2P74 IO_L08P_2/D7/GCLK12P75 IO_L08N_2/D6/GCLK13P76 LED1 O IO/D5P77 IO_L09P_2/D4/GCLK14P78 IO_L09N_2/D3/GCLK15P79 GNDP80 sys_clk_pin I IP_L10P_2/RDWR_B/GCLK0 P81 IP_L10N_2/M2/GCLK1P82 IO_L11P_2/D2/GCLK2P83 IO_L11N_2/D1/GCLK3P84 IO/M1P85 GNDP86 IO_L12P_2/M0P87 IO_L12N_2/DIN/D0P88 VCCO_2P89 IO_L13P_2P90 IO_L13N_2P91 DIP_SWITCH_6 I IPP92 VCCAUXP93 IO_L14P_2/A23P94 IO_L14N_2/A22P95 GNDP96 IO_L15P_2/A21P97 IO_L15N_2/A20P98 LED2 O IO/VREF_2P99 IO_L16P_2/VS2/A19P100 IO_L16N_2/VS1/A18Pin No Signal Name I/O FPGA Pin NameP101 DIP_SWITCH_7 I IPP102 IO_L17P_2/VS0/A17P103 IO_L17N_2/CCLKP104 DONEP105 GNDP106 A2_IO18 O IO_L01P_1/A16P107 A2_IO17 O IO_L01N_1/A15P108 A2_IO20 O IO_L02P_1/A14P109 A2_IO19 O IO_L02N_1/A13P110 Push_Buttons_1( S2 )I IPP111 VCCAUXP112 A2_IO22 O IO_L03P_1P113 A2_IO21 O IO_L03N_1/VREF_1P114 VCCO_1P115 A2_IO24 O IO_L04P_1P116 A2_IO23 O IO_L04N_1P117 VCCINTP118 Push_Buttons_2( S3 )I IPP119 A2_IO26 O IO_L05P_1/A12P120 A2_IO25 O IO_L05N_1/A11P121 GNDP122 A2_IO28 O IO_L06P_1P123 A2_IO27 O IO_L06N_1/VREF_1P124 Push_Buttons_3( S4 )I IPP125 VCCO_1P126 A2_IO30 O IO_L07P_1/A10/RHCLK0P127 A2_IO29 O IO_L07N_1/A9/RHCLK1P128 A2_IO32 O IO_L08P_1/A8/RHCLK2P129 A2_IO31 O IO_L08N_1/A7/RHCLK3/TRDY1 P130 Push_Buttons_4( S5 )I IPP131 GNDP132 A2_IO34 I IO_L09P_1/A6/RHCLK4/IRDY1 P133 A2_IO33 I IO_L09N_1/A5/RHCLK5P134 A2_IO36 I IO_L10P_1/A4/RHCLK6P135 A2_IO35 I IO_L10N_1/A3/RHCLK7P136 Push_Buttons_5 ( S6 )I IP/VREF_1Pin No Signal Name I/O FPGA Pin NameP137 A2_IO38 I IO_L11P_1/A2P138 A2_IO37 I IO_L11N_1/A1P139 A2_IO40 I IO_L12P_1P140 A2_IO39 I IO_L12N_1/A0P141 GNDP142 Push_Buttons_6 ( S7 )I IPP143 VCCO_1P144 A2_IO42 I IO_L13P_1P145 A2_IO41 I IO_L13N_1P146 A2_IO44 I IO_L14P_1P147 A2_IO43 I IO_L14N_1P148 Push_Buttons_7( S8 )I IPP149 VCCAUXP150 A2_IO46 IO_L15P_1/HDCP151 A2_IO45 IO_L15N_1/LDC0 P152 IO_L16P_1/LDC1P153 IO_L16N_1/LDC2 P154 Push_Buttons_8( S9 )I IPP155 TMS TMSP156 GNDP157 TDO TDOP158 TCK TCKP159 DIP_Switches_1 I IPP160 A1_IO36 IO_L01P_0P161 A1_IO35 IO_L01N_0P162 A1_IO38 IO_L02P_0P163 A1_IO37 IO_L02N_0/VREF_0 P164 A1_IO40 IO_L03P_0P165 A1_IO39 IO_L03N_0P166 VCCAUXP167 A1_IO42 IO_L04P_0P168 A1_IO41 IO_L04N_0/VREF_0 P169 DIP_Switch_2 I IPP170 VCCINTP171 A1_IO44 IO_L05P_0P172 A1_IO43 IO_L05N_0Pin No Signal Name I/O FPGA Pin NameP173 GNDP174 IP_L06P_0P175 IP_L06N_0P176 VCCO_0P177 A1_IO46 IO_L07P_0/GCLK4 P178 A1_IO45 IO_L07N_0/GCLK5 P179 A1_IO34 IO/VREF_0P180 A1_IO2 O IO_L08P_0/GCLK6 P181 A2_IO1 O IO_L08N_0/GCLK7 P182 GNDP183 GCLK2 IP_L09P_0/GCLK8 P184 IP_L09N_0/GCLK9 P185 A2_IO4 O IO_L10P_0/GCLK10 P186 A2_IO3 O IO_L10N_0/GCLK11 P187 A1_IO33 IOP188 GNDP189 A2_IO6 O IO_L11P_0P190 A2_IO5 O IO_L11N_0P191 VCCO_0P192 A2_IO8 O IO_L12P_0P193 A2_IO7 O IO_L12N_0/VREF_0 P194 DIP_Switches_3 I IPP195 VCCAUXP196 A2_IO10 O IO_L13P_0P197 A2_IO9 O IO_L13N_0P198 GNDP199 A2_IO12 O IO_L14P_0P200 A2_IO11 O IO_L14N_0/VREF_0 P201 VCCO_0P202 A2_IO14 O IO_L15P_0P203 A2_IO13 O IO_L15N_0P204 DIP_Switches_4 I IPP205 A2_IO16 O IO_L16P_0P206 A2_IO15 O IO_L16N_0/HSWAP P207 TDI TDIP208 GND第三章 : Human_IOHuman_IO為MB_XC3S250E的擴充板,包含液晶介面,鍵盤,LED…等週邊介面,再利用J5,J6連接MB_XC3S250E的J1,J2,本章節主要是敘述HUMAIN_IO相關週邊電路的相關說明.3-1. IO_LED16Human_IO共有16個LED,其中8顆為綠色,8顆為紅色,當FPGA輸出邏輯’1’(High)時,LED亮.當FPGA輸出邏輯’0’(LOW)時,LED暗.NET "IO_LED16<0>" LOC = "P3" ;NET "IO_LED16<1>" LOC = "P2" ;NET "IO_LED16<2>" LOC = "P5" ;NET "IO_LED16<3>" LOC = "P4" ;NET "IO_LED16<4>" LOC = "P9" ;NET "IO_LED16<5>" LOC = "P8" ;NET "IO_LED16<6>" LOC = "P12" ;NET "IO_LED16<7>" LOC = "P11" ;NET "IO_LED16<8>" LOC = "P16" ;NET "IO_LED16<9>" LOC = "P15" ;NET "IO_LED16<10>" LOC = "P19" ;NET "IO_LED16<11>" LOC = "P18" ;NET "IO_LED16<12>" LOC = "P23" ;NET "IO_LED16<13>" LOC = "P22" ;NET "IO_LED16<14>" LOC = "P25" ;NET "IO_LED16<15>" LOC = "P24" ;FPGA PIN SYMBOL LABEL NAME LOGIC COMMENTD16 FPGA輸出’1’,LED亮綠色LED P3 A1_IO1D15 FPGA輸出’1’,LED亮綠色LED P2 A1_IO2P5 A1_IO3D14 FPGA輸出’1’,LED亮綠色LEDD13 FPGA輸出’1’,LED亮綠色LED P4 A1_IO4P9 A1_IO5D12 FPGA輸出’1’,LED亮綠色LEDD11 FPGA輸出’1’,LED亮綠色LED P8 A1_IO6D10 FPGA輸出’1’,LED亮綠色LED P12 A1_IO7D9 FPGA輸出’1’,LED亮綠色LED P11 A1_IO8D8 FPGA輸出’1’,LED亮紅色LED P16 A1_IO9D7 FPGA輸出’1’,LED亮紅色LED P15 A1_IO10D6 FPGA輸出’1’,LED亮紅色LED P19 A1_IO11D5 FPGA輸出’1’,LED亮紅色LED P18 A1_IO12D4 FPGA輸出’1’,LED亮紅色LED P23 A1_IO13D3 FPGA輸出’1’,LED亮紅色LED P22 A1_IO14D2 FPGA輸出’1’,LED亮紅色LED P25 A1_IO15D1 FPGA輸出’1’,LED亮紅色LED P24 A1_IO163-2. IO_KEY4X4Human_IO有一個4X4的鍵盤,共可定義16個按鍵,4X4按鍵可以以掃描方式控制.NET "IO_KEYI<3>" LOC = "P29" ;NET "IO_KEYI<2>" LOC = "P28" ;NET "IO_KEYI<1>" LOC = "P31" ;NET "IO_KEYI<0>" LOC = "P30" ;NET "IO_KEYO<3>" LOC = "P34" ;NET "IO_KEYO<2>" LOC = "P33" ;NET "IO_KEYO<1>" LOC = "P36" ;NET "IO_KEYO<0>" LOC = "P35" ;FPGA PIN SYMBOL LABEL NAME LOGIC COMMENTKEY4X4_PIN1P35 A1_IO24列1 綠色LEDKEY4X4_PIN2P36 A1_IO23列 2 綠色LEDKEY4X4_PIN3P33 A1_IO22列 3 綠色LEDKEY4X4_PIN4P34 A1_IO21列 4 綠色LED P30 A1_IO20KEY4X4_PIN5行1 紅色LEDKEY4X4_PIN6P31 A1_IO19行 2 紅色LEDKEY4X4_PIN7P28 A1_IO18行 3 紅色LEDKEY4X4_PIN8P29 A1_IO17行 4 紅色LED3-3.DIFFERENTIAL LINE RECEVIER & LINE DRIVERHuman_IO有一個4個Differential Line Driver與4個Differential Line Receiver,可以提供Differential的介面.透過P2與JP1,可以提供與其它介面的連接之用.請注意需將JP1的PIN1與PIN2短路NET "IO_MC3487_O<0>" LOC = "P40" ;NET "IO_MC3487_O<1>" LOC = "P39" ;NET "IO_MC3487_O<2>" LOC = "P42" ;NET "IO_MC3487_O<3>" LOC = "P41" ;NET "IO_MC3486_I<0>" LOC = "P48" ;NET "IO_MC3486_I<1>" LOC = "P47" ;NET "IO_MC3486_I<2>" LOC = "P50" ;NET "IO_MC3486_I<3>" LOC = "P49" ;FPGA PIN SYMBOL LABEL NAME LOGIC COMMENTP40 A1_IO25 DIFF OUT1 TTL DIFF OUT(5V) P2的PIN1,2 P39 A1_IO26 DIFF OUT2 TTL DIFF OUT P2的PIN3,4 P42 A1_IO27 DIFF OUT3 TTL DIFF OUT P2的PIN5,6 P41 A1_IO28 DIFF OUT4 TTL DIFF OUT JP1的PIN1,2 P48 A1_IO29 DIFF IN1 TTL DIFF IN(5V) P2的PIN9,10 P47 A1_IO30 DIFF IN2 TTL DIFF IN P2的PIN11,12 P50 A1_IO31 DIFF IN3 TTL DIFF IN P2的PIN13,14 P49 A1_IO32 DIFF IN4 TTL DIFF IN JP1的PIN3,43-4.ANALOG IN / ANALOG OUTHuman_IO有2頻道8位元類比輸入與4個頻道12位元類比輸出,ADC的元件為ADC0832,而DAC的元件則為LTC2624,其規格如下:ADC1:由P1的PIN7輸入,輸入的電壓範圍為0~5V,轉換時間為32us,解析度為8位元ADC2:由P1的PIN8輸入,輸入的電壓範圍為0~5V,轉換時間為32us,解析度為8位元DAC1:由P1的PIN1輸出,輸出的電壓準位為0~3.3V,解析度12位元DAC2:由P1的PIN2輸出,輸出的電壓準位為0~3.3V,解析度12位元DAC3:由P1的PIN3輸出,輸出的電壓準位為0~3.3V,解析度12位元DAC4:由P1的PIN4輸出,輸出的電壓準位為0~3.3V,解析度12位元ADC與DAC是透過串列方式控制,其轉換時間與轉換時序,由FPGA產生. NET "IO_ADC_CSN" LOC = "P187" ;NET "IO_ADC_CLK" LOC = "P179" ;NET "IO_ADC_SDI" LOC = "P135" ;NET "IO_ADC_SDO" LOC = "P160" ;NET "IO_DAC_CS" LOC = "P163" ;NET "IO_DAC_SCK" LOC = "P162" ;NET "IO_DAC_SDI" LOC = "P165" ;NET "IO_DAC_SDO" LOC = "P164" ;NET "IO_DAC_CLR" LOC = "P177" ;FPGA PIN SYMBOL LABEL NAME LOGIC COMMENTOUTPUTADC_CSN ADC_CSNP187 A1_IO33OUTPUTP179 A1_IO34ADC_CLK ADC_CLKP135 A1_IO35 ADC_SDI ADC_SDI INPUTINPUTADC_SDO ADC_SDOP160 A1_IO36DAC_CS DAC_CSOUTPUTP163 A1_IO37OUTPUTDAC_SCK DAC_SCKP162 A1_IO38P165 A1_IO39 DAC_SDI DAC_SDI OUTPUTOUTPUTP164 A1_IO40DAC_SDO DAC_SDOOUTOUTDAC_CLR DAC_CLRP177 A1_IO46ADC控制時序圖.DAC控制時序圖.3-5.七節燈管Human_IO提供8個七節燈管,由FPGA控制.其控制方法為掃描式,如圖所示,若要 控制左邊第一個七節燈管輸出'2'的字型,可以先輸出"11011010"到CA~DP,然後NET "IO_DIGIT<0>" LOC = "P181" ; ##AN1NET "IO_DIGIT<1>" LOC = "P180" ; ##AN2NET "IO_DIGIT<2>" LOC = "P186" ; ##AN3NET "IO_DIGIT<3>" LOC = "P185" ; ##AN4NET "IO_DIGIT<4>" LOC = "P190" ; ##AN5NET "IO_DIGIT<5>" LOC = "P189" ; ##AN6NET "IO_DIGIT<6>" LOC = "P193" ; ##AN7NET "IO_DIGIT<7>" LOC = "P192" ; ##AN8NET "IO_SEGMENT<0>" LOC = "P197" ; ##CANET "IO_SEGMENT<1>" LOC = "P196" ; ##CBNET "IO_SEGMENT<2>" LOC = "P200" ; ##CCNET "IO_SEGMENT<3>" LOC = "P199" ; ##CDNET "IO_SEGMENT<4>" LOC = "P203" ; ##CENET "IO_SEGMENT<5>" LOC = "P202" ; ##CFNET "IO_SEGMENT<6>" LOC = "P206" ; ##CGNET "IO_SEGMENT<7>" LOC = "P205" ; ##DPFPGA PIN SYMBOL LABEL NAME LOGIC COMMENTIO_DIGIT<0> 輸出’0’,動作AN1P181 A2_IO1IO_DIGIT<1> 輸出’0’,動作AN2P180 A2_IO2P186 A2_IO3IO_DIGIT<2> 輸出’0’,動作AN3IO_DIGIT<3> 輸出’0’,動作AN4P185 A2_IO4P190 A2_IO5IO_DIGIT<4> 輸出’0’,動作AN5IO_DIGIT<5> 輸出’0’,動作AN6P189 A2_IO6IO_DIGIT<6> 輸出’0’,動作AN7P193 A2_IO7IO_DIGIT<7> 輸出’0’,動作AN8P192 A2_IO8IO_SEGEMENT<0> 輸出’1’,動作 U4的CA P197 A2_IO9IO_SEGEMENT<1> 輸出’1’,動作 U4的CB P196 A2_IO10IO_SEGEMENT<2> 輸出’1’,動作 U4的CC P200 A2_IO11IO_SEGEMENT<3> 輸出’1’,動作 U4的CD P199 A2_IO12IO_SEGEMENT<4> 輸出’1’,動作 U4的CEP203 A2_IO13IO_SEGEMENT<5> 輸出’1’,動作 U4的CFP202 A2_IO14IO_SEGEMENT<6> 輸出’1’,動作 U4的CG P206 A2_IO15IO_SEGEMENT<7> 輸出’1’,動作 U4的DPP205 A2_IO163-6.LCD128X64LCD128X64是一個128 X 64 PIXEL的液晶顯示器,可以顯示圖形式的圖案,包含中文字的字型,LCD128X64並未提供已建好的字型,使用者需自行建立字型,並配合所需時序,才能輸出字型.Net "IO_LCD128x64<0>" LOC = "P123" ; ##LCD_DO(A2_IO27)Net "IO_LCD128x64<1>" LOC = "P119" ; ##LCD_D1(A2_IO26)Net "IO_LCD128x64<2>" LOC = "P120" ; ##LCD_D2(A2_IO25)Net "IO_LCD128x64<3>" LOC = "P115" ; ##LCD_D3(A2_IO24)Net "IO_LCD128x64<4>" LOC = "P116" ; ##LCD_D4(A2_IO23)Net "IO_LCD128x64<5>" LOC = "P112" ; ##LCD_D5(A2_IO22)Net "IO_LCD128x64<6>" LOC = "P113" ; ##LCD_D6(A2_IO21)Net "IO_LCD128x64<7>" LOC = "P108" ; ##LCD_D7(A2_IO20)Net "IO_LCD128x64<10>" LOC = "P107" ; ##LCD_RST(A2_IO17)Net "IO_LCD128x64<11>" LOC = "P106" ; ##LCD_CS2(A2_IO18)Net "IO_LCD128x64<12>" LOC = "P109" ; ##LCD_CS1(A2_IO19)Net "IO_LCD128x64<13>" LOC = "P122" ; ##LCD_E (A2_IO28)Net "IO_LCD128x64<14>" LOC = "P127" ; ##LCD_RW(A2_IO29)Net "IO_LCD128x64<15>" LOC = "P126" ; ##LCD_DI(A2_IO30)FPGA PIN SYMBOL LABEL NAME LOGIC COMMENTU13_PIN7IO_LCD128X64<0> FPGA_LCD_D0P123 A2_IO27U13_PIN8LCD128X64<1> FPGA_LCD_D1P119 A2_IO26IO_U13_PIN9LCD128X64<2> FPGA_LCD_D2IO_P120 A2_IO25U13_PIN10LCD128X64<3> FPGA_LCD_D3P115 A2_IO24IO_LCD128X64<4> FPGA_LCD_D4U13_PIN11IO_P116 A2_IO23LCD128X64<5> FPGA_LCD_D5U13_PIN12IO_P112 A2_IO22LCD128X64<6> FPGA_LCD_D6U13_PIN13IO_P113 A2_IO21U13_PIN14LCD128X64<7> FPGA_LCD_D7IO_P108 A2_IO20U13_PIN17LCD128X64<10> FPGA_LCD_RSTIO_P107 A2_IO17U13_PIN16LCD128X64<11> FPGA_LCD_CS2P106 A2_IO18IO_U13_PIN15LCD128X64<12> FPGA_LCD_CS1P109 A2_IO19IO_LCD128X64<13> FPGA_LCD_E U13_PIN6IO_P122 A2_IO28U13_PIN5LCD128X64<14> FPGA_LCD_RWIO_P127 A2_IO29LCD128X64<15> FPGA_LCD_DIU13_PIN4IO_P126 A2_IO303-7.LCD16X2LCD16X2是一個文字型的液晶顯示器,已內建ASCII字型於LCD16X2內,提供文字的顯示,每行可以顯示16個字,共可顯示兩行.Net "IO_LCD16x2<0>" LOC = "P123" ; ##LCD_DO(A2_IO27)Net "IO_LCD16x2<1>" LOC = "P119" ; ##LCD_D1(A2_IO26)Net "IO_LCD16x2<2>" LOC = "P120" ; ##LCD_D2(A2_IO25)Net "IO_LCD16x2<3>" LOC = "P115" ; ##LCD_D3(A2_IO24)Net "IO_LCD16x2<4>" LOC = "P116" ; ##LCD_D4(A2_IO23)Net "IO_LCD16x2<5>" LOC = "P112" ; ##LCD_D5(A2_IO22)Net "IO_LCD16x2<6>" LOC = "P113" ; ##LCD_D6(A2_IO21)Net "IO_LCD16x2<7>" LOC = "P108" ; ##LCD_D7(A2_IO20)Net "IO_LCD16x2<13>" LOC = "P122" ; ##LCD_E (A2_IO28)Net "IO_LCD16x2<14>" LOC = "P127" ; ##LCD_RW(A2_IO29)Net "IO_LCD16x2<15>" LOC = "P126" ; ##LCD_DI(A2_IO30)FPGA PIN SYMBOL LABEL NAME LOGIC COMMENTU12_PIN7IO_LCD16X2<0> FPGA_LCD_D0P123 A2_IO27U12_PIN8LCD16X2<1> FPGA_LCD_D1P119 A2_IO26IO_U12_PIN9LCD16X2<2> FPGA_LCD_D2P120 A2_IO25IO_LCD16X2<3> FPGA_LCD_D3U12_PIN10IO_P115 A2_IO24LCD16X2<4> FPGA_LCD_D4U12_PIN11IO_P116 A2_IO23LCD16X2<5> FPGA_LCD_D5U12_PIN12IO_P112 A2_IO22LCD16X2<6> FPGA_LCD_D6U12_PIN13IO_P113 A2_IO21LCD16X2<7> FPGA_LCD_D7U12_PIN14IO_P108 A2_IO20LCD16X2<13> FPGA_LCD_E U12_PIN6 P122 A2_IO28IO_LCD16X2<14> FPGA_LCD_RWU12_PIN5IO_P127 A2_IO29U12_PIN4LCD16X2<15> FPGA_LCD_DIP126 A2_IO30IO_3-8.PS2PS2提供PC個人電腦的鍵盤介面.Net "IO_PS2_DATA" LOC = "P129" ; ##A2_IO31Net "IO_PS2_CLK" LOC = "P128" ; ##A2_IO32FPGA PIN SYMBOL LABEL NAME LOGIC COMMENTP129 A2_IO31PS2_DATA U3_PIN1PS2_CLK U3_PIN5 P128 A2_IO323-9.VGAPS2提供PC個人電腦的VGA介面,但只支援8種顏色.Net "IO_VGA_VSYNC" LOC = "P168" ; ##A1_IO41Net "IO_VGA_HSYNC" LOC = "P167" ; ##A1_IO42Net "IO_VGA_B" LOC = "P172" ; ##A1_IO43 Net "IO_VGA_G" LOC = "P171" ; ##A1_IO44 Net "IO_VGA_R" LOC = "P178" ; ##A1_IO45FPGA PIN SYMBOL LABEL NAME LOGIC COMMENTIO_VGA_VSYNC VSYNC U8_PIN14 P168 A1_IO41IO_VGA_HSYNC HSYNC U8_PIN13 P167 A1_IO42IO_VGA_B BLUE U8_PIN3 P172 A1_IO43P171 A1_IO44IO_VGA_G GREEN U8_PIN2IO_VGA_R RED U8_PIN1 P178 A1_IO453-10. PUSH BUTTONHUMAN_IO 提供四個按鍵與四個DIP_SWICTH,位於板子的最左方,當PUSH_BUTTON 按下時,輸入的電壓準位為低電位’0’;當不按時為’1’當DIP_SWITCH 往下切為[ON]時,輸入電壓準位為低電位’0’;而上切時為[OFF]. NET "IO_DIP_SWITCH<0>" LOC = "P138" ; NET "IO_DIP_SWITCH<1>" LOC = "P137" ; NET "IO_DIP_SWITCH<2>" LOC = "P140" ; NET "IO_DIP_SWITCH<3>" LOC = "P139" ;NET "IO_PUSH_BUTTON<0>" LOC = "P133" ; NET "IO_PUSH_BUTTON<1>" LOC = "P132" ; NET "IO_PUSH_BUTTON<2>" LOC = "P135" ; NET "IO_PUSH_BUTTON<3>" LOC = "P134" ;FPGA PIN SYMBOL LABEL NAME LOGIC COMMENT P138 IO_DIP1 USER_SW1 切為ON 時,輸入為’0’ IO_S1_1 P137 IO_DIP2 USER_SW2 切為ON 時,輸入為’0’ IO_S1_2 P140 IO_DIP3 USER_SW3 切為ON 時,輸入為’0’ IO_S1_3 P139 IO_DIP4 USER_SW5 切為ON 時,輸入為’0’ IO_S2_4 P133 IO_SW1 USER_DIP1 按下時,輸入為’0’ IO_S5 P132 IO_SW2 USER_DIP2 按下時,輸入為’0’ IO_S4 P135 IO_SW3 USER_DIP3 按下時,輸入為’0’ IO_S3 P134 IO_SW4 USER_DIP4 按下時,輸入為’0’ IO_S23-11.ROTARYHUMAN_IO提供一個按鍵與ROTARY SWICTH,位於板子的最左方NET "IO_ROTARY<0>" LOC = "P145" ;NET "IO_ROTARY<1>" LOC = "P147" ;NET "IO_ROTARY<2>" LOC = "P144" ;NET "IO_ROTARY<3>" LOC = "P146" ;LOGIC COMMENT FPGA PIN SYMBOL LABELNAMEA2_IO41P145 IO_ROTARY<0>A2_IO42P147 IO_ROTARY<1>A2_IO43 IO_S3P144 IO_ROTARY<2>A2_IO44 IO_S2P146 IO_ROTARY<3>當ROTARY切換到位置0~9時,IO_ROTARY<0> ~ IO_ROTARY<3>會輸出相對應的值,其值列表如下POSITION IO_ROTARY<3> IO_ROTARY<2>IO_ROTARY<1> IO_ROTARY<1>0 1 1 1 11 1 1 1 02 1 1 0 13 1 1 0 04 1 0 1 15 1 0 1 06 1 0 0 17 1 0 0 08 0 1 1 19 0 1 1 03-12.IICHUMAN_IO提供IIC的FLASH,編號為24C02NET "IO_IIC_SCL" LOC = "P151" ;NET "IO_IIC_SDA" LOC = "P150" ;LOGIC COMMENT FPGA PIN SYMBOL LABELNAMEP151 IO_IIC_SCL A2_IO45 U7_PIN6 P150 IO_IIC_SDA A2_IO46 U7_PIN5第四章 : Ulinx_MB_XC3S250E_PQ208測試4-1.先安裝ISE 軟體,序號由CD片中取得.4-2.連接系統,建立測試環境.4-2-1. 連接 DB25 的1對1測試線到 PC_Printer_Port 與 XC3S250E板子的P1(JTAG)4-2-2. 連接電源(DC+5V/3A) 到 ULINX_MB_XC3S250E 板. Î J8中間為+5V 4-2-3. 連接RS232測試頭,以1對1 的DB9延長線連接到個人電腦的COM Port (開啟[終端機]Î[超極終端機]Î設定Baud:9600,Data:8,Stop:1,No Parity.)4-2-4. 設定板子的設定.J6 : 短路(4個短路pin)J5 : 短路(4個短路pin)J4 : 1,2 短路(左邊兩隻腳短路).其餘 open4-2-5. R8,R9先調整於VR的中間;確認連線。

Spartan 3E用户指南的中文翻译part2

Chapter 4:FPGA Configuration Options入门实验板支持多种FPGA的配置方法:通过JTAG、USB接口直接将设计下载到FPGA。

板上的USB-JTAG逻辑也提供对Platform Flash PROM 和Xilinx XC2C64A CPLD的在线编程。

对板上的4 Mbit Xilinx XCF04S serial Platform Flash PROM进行编程,然后采用主串行模式对Platform Flash PROM上的存储信息配置到FPGA。

对板上的16 Mbit ST Microelectronics SPI serial Flash PROM进行编程,然后采用SPI模式对SPI serial Flash PROM上的存储信息配置到FPGA。

对板上的128 Mbit Intel Strata Flash parallel NOR Flash PROM进行编程,然后采用BPI Up 或BPI Down对Strata Flash parallel NOR Flash PROM上的存储信息配置到FPGA。

接着,可以采用Spartan-3E FPGA’s Mult iBoot 模式以两种不同的配置方式对一个FPGA进行轮流下载。

图4.1给出了USB下载/编程接口和永久存储器的位置。

图4.2是多种配置方式的一些细节内容。

当上电或PROG按钮被按下时,跳线的配置方式决定了FPGA采用哪种配置方式。

当FPGA成功配置时,DONE管脚的LED亮。

4 Mbit Xilinx Platform Flash PROM为FPGA的JTAG提供了一个简单的可编程配置存储单元。

来自Platform Flash PROM的FPGA配置采用主串行模式。

采用BPI Up、BPI Down或MultiBoot配置方式以及StrataFlash parallel Flash PROM对FPGA进行下载时,64-macrocell XC2C64A CoolRunner II CPLD为其提供了额外的存储空间。

Spartan3E-StarterBoard开发板介绍

Xilinx FPGA开发板

开发板介绍

QQ群:34215299

资料版本:TCH.V1.2.D.001 Jinms Xilinx FPGA教程

概述

此开发板采用了Xilinx FPGA芯片XC3S250E-VQG100,配有的2M(升级版本为4M)大小PROM-XCF02S和50MHZ有源晶振构成了开发板的核心部分。

可以采用外部电源供电,也可以通过USB 延长线,通过电脑USB接口供电。

可以使用的资源有:

1、4个按键输入

2、8个LED

3、蜂鸣器

4、HC595驱动4位八段数码管

5、232串口

6、PS2接口

7、VGA接口

8、68个IO

此开发板可以用来入门学习,配套的例程有:

1、LED跑马灯

2、按键控制LED

3、蜂鸣器控制

4、通过SPI方式驱动HC595,实现4位8段数码管计数器

5、URAT串口通信程序

6、PS2驱动程序

7、其它例程

代码都用Verilog开发,部分已经有了VHDL的代码。

此开发板也可以用来做实验,所有IO都通过排针引出来了。

Spartan3E家族是Xilinx新款高性价比的FPGA芯片。

Spartan3E FPGA资源如下图所示:

开发板采用的XC3S250E-VQG100芯片如下图所示:

资源介绍框图

资源介绍实物图。

XILINX-S3E开发板(完整版)手册2012.3.39

always @(posedge clk)begin //run led, if(!rst)begin led<=8'hff;led_n<=0;end else begin led<=8'hff; led[led_n]<=0; if(counter==0)led_n<=led_n+1; end end always @(posedge clk)begin // interval time set, 2^24/50000000=0.33s if(!rst)counter<=0; else counter<=counter+1; end endmodule

8、编写 testbench ,这里注意:仿真的时候为了能看到效果,这里把源代码中的

6 个系统时钟就可能完成一个循环的计 reg[23:0]counter 改为 reg[7:0]counter .这样每过 25 256 数,否则时间太长,仿真器要运行很长的时间。 在 Simulation 选择 New Source 过程和上面过程基本相同。 执行

6、继续单击 Next ,之后单击 finish,弹出的对话框点击 Yes.之后可以看到 如图所示:

11

小树-EDA

Spartan3E

Xilinx FPGA 开发板

7、填写源代码,填入如下代码:

module run_led(clk,rst,led); //module port input input output reg reg reg clk;//system clock rst;//system reset [7:0] led; // 8bits led [7:0] led; [23:0]counter; //time counter [2:0]led_n; // decied the led to be lighted

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

附录:Spartan-3E开发板用户说明图1Spartan-3E多用途EDA实验开发平台(以下简称S3E实验平台),如图1所示,核心器件为XILINX公司的Spartan TM-3E器件XC3S500E,逻辑容量为50万门。

Spartan TM-3E借助于低成本的CPL,90nm工艺,满足了对大批量、I/O为核心的可编程逻辑解决方案的行业需求,是业界成本最低、性能最好的FPGA之一。

S3E实验平台在FPGA周围提供了丰富的资源,包括串口、PS/2接口、VGA接口、以太网接口、LED、LCD液晶显示、拨码旋钮开关和按钮、EPROM、A/D、D/A转换、电源、时钟等。

S3E的用户可以在PC机上通过USB JTAG电缆对FPGA进行配置,也可以通过SPI FLASH和NOR FLASH来配置。

1、S3E实验平台性能与特点●XILINX XC3S500E Spartan-3E FPGA:提供了最多232个I/O引脚和10000个逻辑单元。

●XILINX 4Mbit Flash配置PROM。

●XILINX XC2C64A CoolRunner系列CPLD:提供用户使用或辅助FPGA配置。

●64MByte、16位数据宽度、100MHz的DDR SDRAM接口。

●16MByte 并行INTEL公司的NOR FLASH:可存储FPGA配置信息或MicroBlaze指令序列。

●16Mbits ST半导体的SPI 串行FLASH:可存储FPGA配置信息或MicroBlaze指令序列。

●2行,每行可显示16个字符的LCD:用来显示FPGA输出信息。

●PS/2接口:用来外联键盘或鼠标,扩展输入设备●VGA接口:可显示64种颜色。

●10/100M以太网接口:提供了以太网物理层接口,便于MAC层IP的验证。

●两个标准RS232接口:可方便连接PC和其他工业设备进行数据传输。

●USB的下载接口配置接口。

●板载50MHz晶体振荡器。

●4输出基于SPI接口的数模转换器。

●2输入基于SPI接口、带可编程增益放大的模数转换器。

●ChipScope在线调试接口:可提供在线调试信号功能。

●4个拨码开关、1个旋钮、4个按键:可作为通用逻辑输入。

●8盏LED:可用来显示FPGA的输出信息。

●提供8脚DIP封装的辅助时钟输入●提供了标准外扩接口,供用户灵活添加使用。

2、可编程逻辑模块XC3S500E FPGASpartan™-3E FPGA 是数字视频、工业、医疗、通信与数字消费类电子应用中的大容量、以门电路为核心的可编程逻辑设计的理想选择。

这些90nm 工艺器件实现了业界最低的单位逻辑成本满足了对大批量、I/O为核心的可编程逻辑解决方案的行业需求。

Spartan™-3E FPGA提供:●具有在不同密度器件间移植特性的66到376个I/O●高达684K的block RAM 和高达231K的分布式RAM●多达36个用于高性能DSP 应用的嵌入式18x18乘法器●多达8个数字时钟管理器,去除了分立DLL/PLL 与移位寄存器●支持具有最低成本的配置解决方案,包括Xilinx Platform Flash 和商用串行(SPI)与并行flash 存储器●支持18个通用单端和差分I/O 标准,●包括PCI 64/66、PCI-X™、mini-L VDS 和RSDS●易于实现的DDR 存储器接口●PCI 64/66 兼容与PCI-X 兼容性XC3S500E将大量的可编程逻辑、知识产权(IP)核、高级时钟电路和嵌入式存储器与多种快速互连结构整合在一起。

其具有50万门规模,10000个可配置的逻辑单元,232个I/O引脚,4个DCM数字时钟管理模块,360个Block RAM,73Kb的分布式RAM。

3、按键、开关、旋钮S3E实验平台提供了4个按键、4个拨码开关和1个旋钮,它们分别连接到了FPGA的I/O口上。

(1)按键按键位于开发板的左下脚,标识名为BTN_NORTH、BTN_EAST、BTN_SOUTH、BTN_WEST,如图2所示。

当不按时为低电平,按下为高电平。

图2(2)拨码开关拨码开关位于开发板的右下角,标识名为SW0~SW3,如图3所示。

SW0为最右边开关。

开关拨下为低电平,拨上为高电平。

图3(3)旋钮旋钮位于开发板左下角,在四个按钮中间,如图2所示。

旋钮有三个输出,分别为中轴顺逆时针旋转译码信号ROT_A、ROT_B以及中轴按钮信号ROT_CENTER。

当中轴按下时,ROT_CENTER输出为高电平,当未按下,输出为低电平。

ROT_A、ROT_B默认为高电平(带内部上拉),如图4所示。

当旋钮静止时,ROT_A、ROT_B为初始时所处的状态。

当旋钮向右转动时,ROT_A先变为0,此时ROT_B还为1,当继续转动时,ROT_B为0,之后ROT_A又变为1,如图5所示。

当旋钮向左转动时,反之亦然。

图4图5表1为输入逻辑对应的管脚分配。

4、LED显示S3E实验平台共有8个LED显示灯,用于逻辑显示。

LED位于开发板右下脚,拨码开关的上面,如图3所示。

其标识为LED0~LED7,LED0于最右边。

当与LED相连的FPGA 管脚为高电平时,LED数码管点亮。

表2为LED显示部分的管脚列表。

5、全局时钟输入时钟输入模块位于Spartan3E开发板的LOGO旁。

如图6所示。

晶体振荡器为FPGA提供时钟信号。

图6S3E实验平台共有3种时钟源。

分别是50MHz有源晶振CLK_50MHz、外接8脚DIP 封装晶振CLK_AUX和SMA接口的外加时钟源CLK_SMA。

每一种时钟输入都和FPGA BANK0的全局时钟直接相连,其中CLK_SMA也可以用来进行时钟频率的输出。

JP9控制着BANK0 I/O引脚的输入输出参考电压。

默认时,选择3.3V。

若选择2.5V,因实验平台中的晶振是3.3V的器件,故不能够正常工作。

表3是全局时钟的管脚分配列表。

6、LCD接口S3E实验平台提供了一个2行、每行可显示16个字符的液晶显示器。

FPGA控制着4bit LCD的数据接口,如图7所示。

SF_D[11:8]为双向LCD数据DB4~DB7。

LCD_E为读写使能,LCD_E=0时,读写操作无效,LCD_E=1时,读写正常。

LCD_RS为寄存器选择信号,LCD_RS=1时,FPGA读写LCD数据,LCD_RS=0时,FPGA对LCD进行写指令操作。

LCD_RW为读写控制信号,LCD_RW=1时,FPGA读出LCD数据,否则LCD接收FPGA的数据。

为了减少引脚开支,LCD 4bit数据线和Intel NOR FLASH中的数据口的D[11:8]复用。

当FLASH未选中(即SF_CE0=1)时,FPGA可以任意读写LCD的数据。

当LCD的读操作失效(即LCD_RW=0)时,FPGA只能读写FLASH中数据。

若FLASH设置成字节(×8bit)模式(即SF_BYTE=0)时,FPGA能够同时读写FLASH和LCD中的数据。

在字节模式中,FLASH的D[15:8]数据无效。

图7表4为LCD引脚分配列表:S3E实验平台的LCD控制器采用Sitronix公司的ST7066U图形控制器,它的访问操作和三星公司的S6A0069X、日立公司的HD44780、SMOS公司的SED1278类似。

具体操作请参阅相关手册。

7、VGA视频输出接口S3E实验平台配备了一个DB15标准的VGA输出口,用于VGA的输出显示。

VGA的DB15接口位于实验平台左上角,如图8所示。

图8视频输出的原理为通过控制DB1、2、3脚的电平,同时使用13、14脚来控制列扫描和行扫描,实现VGA的显示。

实验平台最多可显示64种颜色。

DB15接口1、2、3的定义为VGA_RED、VGA_GREEN、VGA_BLUE。

列扫描信号为VGA_HSYNC、行扫描信号为VGA_VSYNC。

表5为VGA管脚分配。

表58、串行接口——RS232S3E实验平台有两个RS232串行接口:DCE DB9接口和DTE DB9接口,位于实验平台的右上角,如图9所示。

DCE接口可作为从设备可以连接到大多数PC机和工作站中,接收主机信息。

DTE接口可作为主设备连接控制带RS232接口的外部设备,如调制解调器、打印机等等。

串口信号通过MAX3232芯片来实现RS232电平到TTL电平的转换。

S3E为每个接口提供最简单的串行数据传输,不支持流控制和调制解调功能。

具体信号为,DCE:RS232_DCE_RXD(DCE数据接收)、RS232_DCE_TXD(DCE数据发送);DTE:RS232_DTE_RXD(DTE数据接收)、RS232_DTE_TXD(DTE数据发送)。

图9表6是串口部分的管脚列表。

9、标准PS/2接口S3E实验平台提供通用的PS/2接口,位于开发板上侧,如图10所示,可以用作扩展PC 机PS/2接口的鼠标或键盘。

FPGA与PS/2接口的两条信号线相连,PS2_DA TA和PS2_CLK。

PS2_DA TA上承载数据,PS2_CLK作为PS2_DA TA的同步信号。

图10表7是PS/2接口的管脚列表。

表710、数模转换模块S3E实验平台提供了一个SPI接口兼容,4通道,串行数模转换器,位于实验板的左侧,RJ45接头的上面,如图11所示。

转换器使用12位Linear Technology公司的L TC2624芯片。

DAC的4通道输出连接到J5插头上。

图11L TC2624和主机的接口为SPI接口,其SPI_MOSI、SPI_MISO、SPI_CLK、DAC_CS、DAC_CLR连接到FPGA的管脚上,通过编程控制其时序和数值,从而控制输出的模拟量。

具体的L TC2624芯片的详细使用,请参考L TC2624的数据手册。

表8为L TC2624的管脚列表。

11、模数转换模块S3E实验平台提供了2通道模数转换电路模块,包括模拟量的预放大处理电路和模数转换芯片。

模数转换模块和数模转换处在相同的位置,如图12所示。

图12模拟量的输入通过J7插头提供。

预放大处理芯片采用Linear科技公司的L TC6912,AD 转换器芯片采用Linear科技的L TC1407。

L TC6912和L TC1407都采用SPI控制接口。

故FPGA 通过SPI接口和其进行连接,控制着模数转换模块的正常工作(SPI接口和数模转换模块复用),如图13所示。

图13表9为ADC模块的引脚分配表。

表912、以太网接口模块S3E实验平台包含了一个标准的以太网物理层接口LAC83C185 10/100和一个RJ-45接口。

其位于开发板的左侧,如图14所示。

FPGA控制着以太网物理层的操作,并在上层实现一个符号MII标准的MAC层,以便和网络进行通信,如图15所示。