模拟集成电路设计流程53页PPT

合集下载

模拟CMOS集成电路设计课件

医学图像处理、音频处理

PPT学习交流

6

5

2、集成电路工艺

速度高, 功耗大, 集成度低

最早MOS工 艺,速度低

超高速、高频 IC

光电集成器件

主流工艺,集 成度高、功耗 低、速度快、 抗干扰性强

PPT学习交流

7

6

CMOS工艺

B

S

G

D

B

S

G

D

n+

n+

p+

p+

p 型衬底

n 型阱

n 阱CMOS工艺

B

S

G

D

20

沿沟道x点处的电荷密度为: 沟道x点的电势,以源级为参考点

电流为:

载流子为电子,电荷为负,电荷运动方向与电流 方向相反

其中: 得到:

v=μE μ为载流子的迁移率,E为电场 E=-dV(x)/dx

PPT学习交流

22

21

在整个沟道长度内积分得:

由于ID沿沟道方向是常数,因此:

电流随VGS的 增大而增加

漏极的反型层消失,出现由耗尽层

构成的夹断区。

➢电子沿沟道从源极向漏极运动,达

到夹断区边缘时,受夹断区强电场

的作用,很快漂移到漏极。 B

➢VDS的变化主要体现在夹断区上,

p+

对沟道长度和沟道内的场强影响不

大,因此可以近似认为沟道电流保

p-

持恒定。

VDS

-+

-+

VGS

G

S

D

n+

n+

夹断区

PPT学习交流

20

19

2、NMOS 管IV特性推导与分析

PPT学习交流

6

5

2、集成电路工艺

速度高, 功耗大, 集成度低

最早MOS工 艺,速度低

超高速、高频 IC

光电集成器件

主流工艺,集 成度高、功耗 低、速度快、 抗干扰性强

PPT学习交流

7

6

CMOS工艺

B

S

G

D

B

S

G

D

n+

n+

p+

p+

p 型衬底

n 型阱

n 阱CMOS工艺

B

S

G

D

20

沿沟道x点处的电荷密度为: 沟道x点的电势,以源级为参考点

电流为:

载流子为电子,电荷为负,电荷运动方向与电流 方向相反

其中: 得到:

v=μE μ为载流子的迁移率,E为电场 E=-dV(x)/dx

PPT学习交流

22

21

在整个沟道长度内积分得:

由于ID沿沟道方向是常数,因此:

电流随VGS的 增大而增加

漏极的反型层消失,出现由耗尽层

构成的夹断区。

➢电子沿沟道从源极向漏极运动,达

到夹断区边缘时,受夹断区强电场

的作用,很快漂移到漏极。 B

➢VDS的变化主要体现在夹断区上,

p+

对沟道长度和沟道内的场强影响不

大,因此可以近似认为沟道电流保

p-

持恒定。

VDS

-+

-+

VGS

G

S

D

n+

n+

夹断区

PPT学习交流

20

19

2、NMOS 管IV特性推导与分析

《模拟集成电路》课件

,以便对设计的电路进行全面的测试和评估。

PART 05

模拟集成电路的制造工艺

REPORTING

半导体材料

硅材料

硅是最常用的半导体材料,具有 稳定的物理和化学性质,成熟的 制造工艺以及低成本等优点。

化合物半导体

如砷化镓、磷化铟等化合物半导 体材料,具有高电子迁移率、宽 禁带等特点,常用于高速、高频 和高温电子器件。

《模拟集成电路》课 件

REPORTING

• 模拟集成电路概述 • 模拟集成电路的基本元件 • 模拟集成电路的分析方法 • 模拟集成电路的设计流程 • 模拟集成电路的制造工艺 • 模拟集成电路的优化与改进

目录

PART 01

模拟集成电路概述

REPORTING

定义与特点

定义

模拟集成电路是指由电阻、电容、电 感、晶体管等电子元件按一定电路拓 扑连接在一起,实现模拟信号处理功 能的集成电路。

围和失真。

信号分析方法

01

02

03

04

频域分析

将时域信号转换为频域信号, 分析信号的频率成分和频谱特

性。

时域分析

研究信号的幅度、相位、频率 和时间变化特性,分析信号的

波形和特征参数。

调制解调分析

研究信号的调制与解调过程, 分析信号的调制特性、解调失

真等。

非线性分析

研究电路的非线性效应,分析 信号的非线性失真和互调失真

音频领域

模拟集成电路在音频领域中主要用于 音频信号的放大、滤波、音效处理等 功能,如音响设备、耳机等产品中的 模拟集成电路。

模拟集成电路的发展趋势

集成度不断提高

随着半导体工艺的不断发展,模 拟集成电路的集成度不断提高, 能够实现更加复杂的模拟信号处

最新模拟集成电路设计流程课件

Session菜单

Schematic Window Save State Load State Options Reset Quit

回到电路图

2021/1/15

保存当前 所设定的 模拟所用 到的各种

参数

加载已 经保存 的状态

共88页

一些显 示选项 的设置

重置

analog artist。 相当于 重新打 开一个 模拟窗

ac(交流分析)是 分析电路性能随着 运行频率变化而变

化的仿真。

既可以对频率进行 扫描也可以在某个 频率下进行对其它

变量的扫描。

2021/1/15

共88页

22

其它有关的菜单项

Outputs/Setup

当然我们需要输出的有时不仅仅是电流、电压,还有一 些更高级的。比如说:带宽、增益等需要计算的值,这时 我们可以在Outputs/setup中设定其名称和表达式。在运行 模拟之后,这些输出将会很直观的显示出来。

2021/1/15

共88页

11

编辑完成的电路图

2021/1/15

共88页

12

一些快捷键

以下是一些常用的快捷键: i 添加元件,即打开添加元件的窗口; [ 缩小两倍; ] 扩大两倍; w 连线(细线); f 全图显示; p 查看元件属性; m 整体移动(带连接关系); shift+m 移动(不带连接关系)。

2021/1/15

共88页

13

生成symbol

进入“Virtuoso Schematic Editing: mylib nand2 schematic”窗口。

Design -> Create Cellview->From Cellview

模拟集成电路设计.ppt

1.物理图

§3-3: 其他MOS管大信号模型的参数

17

二、MOS电容

2. 耗尽结电容:CBD, CBS

P65 上式S→D 则 CBS→ CBD

18

§3-3: 其他MOS管大信号模型的参数

3.电荷存储电容: CGD, DGS ,CGB

交叠电容: C1、C3 、C5 珊-源/漏 C1 C3 LD Weff Cox CGXO Weff

25

§3-4: MOS管的小信号模型

1. gm,gmbs , gds 在饱和区:

gm (2K'W / L) ID (1 VDS ) (2K'W / L) ID

gmbs

iD vBS

iD vSB

( iD VT

)( VT ) vSB

iD iD VT vGS

gmbs gm 2(2 F

VSB )1/ 2

(a) (b)

多个器件的表示, 从匹配角度看更好。

37

§3-7: MOS电路的SPICE模拟

三、MOS模型描述

.MODEL < 模型名> <模型类型> <模型参数>

例如: .MODEL NCH NMOS LEVEL=1 VT0=1 KP=50U GAMMA=0.5 +LAMBDA=0.01

四、分析实例

vGS

VT

n

kT q

(简化模型,适合手工计算)

第3章第7节

35

3.7 MOS电路的SPICE模拟

36

§3-7: MOS电路的SPICE模拟

一、SPICE 模拟文件的一般格式

● 标题 ● 电路描述 (器件描述和模型描述) ● 分析类型描述 ● 输出描述

§3-3: 其他MOS管大信号模型的参数

17

二、MOS电容

2. 耗尽结电容:CBD, CBS

P65 上式S→D 则 CBS→ CBD

18

§3-3: 其他MOS管大信号模型的参数

3.电荷存储电容: CGD, DGS ,CGB

交叠电容: C1、C3 、C5 珊-源/漏 C1 C3 LD Weff Cox CGXO Weff

25

§3-4: MOS管的小信号模型

1. gm,gmbs , gds 在饱和区:

gm (2K'W / L) ID (1 VDS ) (2K'W / L) ID

gmbs

iD vBS

iD vSB

( iD VT

)( VT ) vSB

iD iD VT vGS

gmbs gm 2(2 F

VSB )1/ 2

(a) (b)

多个器件的表示, 从匹配角度看更好。

37

§3-7: MOS电路的SPICE模拟

三、MOS模型描述

.MODEL < 模型名> <模型类型> <模型参数>

例如: .MODEL NCH NMOS LEVEL=1 VT0=1 KP=50U GAMMA=0.5 +LAMBDA=0.01

四、分析实例

vGS

VT

n

kT q

(简化模型,适合手工计算)

第3章第7节

35

3.7 MOS电路的SPICE模拟

36

§3-7: MOS电路的SPICE模拟

一、SPICE 模拟文件的一般格式

● 标题 ● 电路描述 (器件描述和模型描述) ● 分析类型描述 ● 输出描述

第六章模拟集成电路设计1PPT课件

推得 T3~T6的电流分别 1、 2、 为 4、 8毫 :安

T1电流放大,以减少从参考电流中分出的基极电流。 使一个参考电流较准确地控制多个电流源

2020/8/2

专用集成电路设计实验室

20

四川大学物理科学与技术学院

3、微电流恒流源(Widlar源)

V B1 E V B2 EIE2R e2

Re2

VBE1VBE2 IE2

16

四川大学物理科学与技术学院

基本型恒流源 r

1. 镜像电流源

基准电流:

IREF=Ir

VCCVBE R

V CC R

因为:VB E2=VB E1 IE2 = IE1

所以:IC2 =IC1 IREF

最后得到公式6-29

R上 r 电流I的 r T 变 管 2化 基极 I变 2 r 化

增加了双极型晶体管工作点的稳定性

四川大学物理科学与技术学院

模拟集成电路

2020/8/2

专用集成电路设计实验室

1

四川大学物理科学与技术学院

第一部分

整体概述

THE FIRST PART OF THE OVERALL OVERVIEW, PLEASE SUMMARIZE THE CONTENT

专用集成电路设计实验室

2

四川大学物理科学与技术学院

集成电路概述

• 模拟IC就是能对模拟量进行运算和处理的一种IC, 直接对连续可变的模拟量进行计算与处理

• 模拟集成电路的种类

– 根据输入、输出电压的变化关系分类

• 线性IC:输出信号随输入信号的变化成线性关系 • 非线性IC:具有非线性的传输特点 • 接口电路:AD/DA转换器

– 按工作频率分类

• 低频、高频、射频、微波、毫米波

T1电流放大,以减少从参考电流中分出的基极电流。 使一个参考电流较准确地控制多个电流源

2020/8/2

专用集成电路设计实验室

20

四川大学物理科学与技术学院

3、微电流恒流源(Widlar源)

V B1 E V B2 EIE2R e2

Re2

VBE1VBE2 IE2

16

四川大学物理科学与技术学院

基本型恒流源 r

1. 镜像电流源

基准电流:

IREF=Ir

VCCVBE R

V CC R

因为:VB E2=VB E1 IE2 = IE1

所以:IC2 =IC1 IREF

最后得到公式6-29

R上 r 电流I的 r T 变 管 2化 基极 I变 2 r 化

增加了双极型晶体管工作点的稳定性

四川大学物理科学与技术学院

模拟集成电路

2020/8/2

专用集成电路设计实验室

1

四川大学物理科学与技术学院

第一部分

整体概述

THE FIRST PART OF THE OVERALL OVERVIEW, PLEASE SUMMARIZE THE CONTENT

专用集成电路设计实验室

2

四川大学物理科学与技术学院

集成电路概述

• 模拟IC就是能对模拟量进行运算和处理的一种IC, 直接对连续可变的模拟量进行计算与处理

• 模拟集成电路的种类

– 根据输入、输出电压的变化关系分类

• 线性IC:输出信号随输入信号的变化成线性关系 • 非线性IC:具有非线性的传输特点 • 接口电路:AD/DA转换器

– 按工作频率分类

• 低频、高频、射频、微波、毫米波

集成电路设计.pptx

双极晶体管和MOS晶体管都可用作有源电阻

MOS管有源电阻器

IDS I

I

VGS V VTP

DI

O

S

+

G+

G

V -

V-

O

I

S

D

VTN V VGS

IDS

(a)

(b)

MOS有源电阻及其I-V曲线

第23页/共66页

晶体管有源寄生电阻

双极晶体管集电区电阻 集成电路中集电区电阻Rc要比分立管的大。Rc的增大 会影响高频特性和开关性能。

第2页/共66页

Tox

N+

P

sio2

金 属

NP金s+io属2

纵向结构

横向结构

MOS 电容电容量

Cox=

Aε0 εsio2

Tox

Tox: 薄氧化层厚度;A: 薄氧化层上 金属电极的面积。

一般在集成电路中Tox 不能做的太薄,所以要想提高电容量,只能增加面积。 N+层为 了减小串联电阻及防止表面出现耗尽层。

集成电路中要制作一个30 pF的MOS电容器, 所用面积相当于25个晶体管的面积。

第3页/共66页

MOS电容 N+

SiO2 P+

AL

N+ N-epi

P-SUB

Al P+

第4页/共66页

❖ PN结电容 在PN结反偏时的势垒电容构成的电容器

❖ PN结电容与 MOS电容的数量级相当。

+

-

N+

P

N

外

P衬

第39页/共66页

第40页/共66页

CMOS反 相器工作 原理

输入端高电平时:

MOS管有源电阻器

IDS I

I

VGS V VTP

DI

O

S

+

G+

G

V -

V-

O

I

S

D

VTN V VGS

IDS

(a)

(b)

MOS有源电阻及其I-V曲线

第23页/共66页

晶体管有源寄生电阻

双极晶体管集电区电阻 集成电路中集电区电阻Rc要比分立管的大。Rc的增大 会影响高频特性和开关性能。

第2页/共66页

Tox

N+

P

sio2

金 属

NP金s+io属2

纵向结构

横向结构

MOS 电容电容量

Cox=

Aε0 εsio2

Tox

Tox: 薄氧化层厚度;A: 薄氧化层上 金属电极的面积。

一般在集成电路中Tox 不能做的太薄,所以要想提高电容量,只能增加面积。 N+层为 了减小串联电阻及防止表面出现耗尽层。

集成电路中要制作一个30 pF的MOS电容器, 所用面积相当于25个晶体管的面积。

第3页/共66页

MOS电容 N+

SiO2 P+

AL

N+ N-epi

P-SUB

Al P+

第4页/共66页

❖ PN结电容 在PN结反偏时的势垒电容构成的电容器

❖ PN结电容与 MOS电容的数量级相当。

+

-

N+

P

N

外

P衬

第39页/共66页

第40页/共66页

CMOS反 相器工作 原理

输入端高电平时:

集成电路设计与制造的主要流程PPT培训课件

集成电路设计与制造的主要流程 ppt培训课件

目录

• 集成电路概述 • 集成电路设计流程 • 集成电路制造流程 • 集成电路封装与测试 • 集成电路设计与制造的挑战与未来发展

01

集成电路概述

集成电路的定义与特点

总结词

集成电路是将多个电子元件集成在一块衬底上,实现一定电路或系统功能的微型电子部件。其主要特点包括高集 成度、高可靠性、低功耗、低成本等。

制造工艺的发展趋势是不断追求更高的集成度、更小的特征尺寸和更好的性能。

晶圆制备

晶圆是制造集成电路的基础材 料,其质量直接影响集成电路 的性能和良品率。

晶圆制备包括切割、研磨、抛 光等环节,目的是获得表面平 整、晶体结构完整的晶圆。

晶圆制备技术的发展趋势是追 求更薄的晶圆、更小的晶圆直 径和更高的加工精度。

设计审查与后仿真

设计审查

对完成的版图进行审查,确保其符合规格要求和制造工艺要 求。

后仿真

在版图设计完成后,进行后仿真验证,确保电路的功能和性 能符合要求。

03

集成电路制造流程

制造工艺简介

制造工艺是将集成电路设计转化为实际产品的过程,涉及多个复杂的技术环节。

集成电路制造工艺主要包括晶圆制备、薄膜制备、掺杂与刻蚀、工艺集成与良品率 控制等步骤。

详细描述

集成电路的发展历程可以分为三个阶段:小规模集成电路、大规模集成电路和超大规模集成电路。从 小规模集成电路到超大规模集成电路的发展过程中,集成电路的集成度不断提高,性能不断优化,成 本不断降低,推动了电子技术的飞速发展。

集成电路的应用领域

总结词

集成电路的应用领域非常广泛,包括通信、计算机、 消费电子、工业控制、汽车电子等。

测试与可靠性评估

目录

• 集成电路概述 • 集成电路设计流程 • 集成电路制造流程 • 集成电路封装与测试 • 集成电路设计与制造的挑战与未来发展

01

集成电路概述

集成电路的定义与特点

总结词

集成电路是将多个电子元件集成在一块衬底上,实现一定电路或系统功能的微型电子部件。其主要特点包括高集 成度、高可靠性、低功耗、低成本等。

制造工艺的发展趋势是不断追求更高的集成度、更小的特征尺寸和更好的性能。

晶圆制备

晶圆是制造集成电路的基础材 料,其质量直接影响集成电路 的性能和良品率。

晶圆制备包括切割、研磨、抛 光等环节,目的是获得表面平 整、晶体结构完整的晶圆。

晶圆制备技术的发展趋势是追 求更薄的晶圆、更小的晶圆直 径和更高的加工精度。

设计审查与后仿真

设计审查

对完成的版图进行审查,确保其符合规格要求和制造工艺要 求。

后仿真

在版图设计完成后,进行后仿真验证,确保电路的功能和性 能符合要求。

03

集成电路制造流程

制造工艺简介

制造工艺是将集成电路设计转化为实际产品的过程,涉及多个复杂的技术环节。

集成电路制造工艺主要包括晶圆制备、薄膜制备、掺杂与刻蚀、工艺集成与良品率 控制等步骤。

详细描述

集成电路的发展历程可以分为三个阶段:小规模集成电路、大规模集成电路和超大规模集成电路。从 小规模集成电路到超大规模集成电路的发展过程中,集成电路的集成度不断提高,性能不断优化,成 本不断降低,推动了电子技术的飞速发展。

集成电路的应用领域

总结词

集成电路的应用领域非常广泛,包括通信、计算机、 消费电子、工业控制、汽车电子等。

测试与可靠性评估

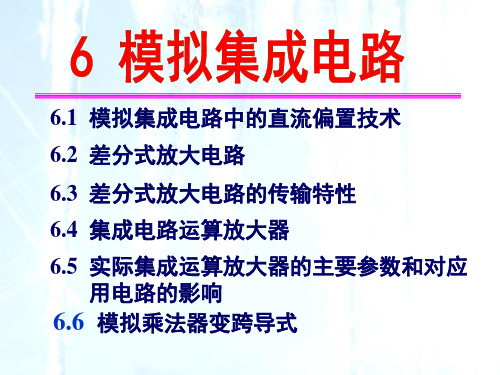

第6章模拟集成电路PPT课件

结论:

无论Rc值如何, IC2电流值保持不变(前提:电源要稳定)

第6页/共55页

当较小时,可用 带缓冲级的镜像电流源

增加T0,使IC更加接近IREF 三、镜像电流源特点 1 内阻ro一般在几百千欧以上

2. 电流受电源波动影响大; 3. 电流最低至mA级。 4. 具有温度补偿特性。

第7页/共55页

6.1.2微电流源(P259)

第24页/共55页

+

+

-vid

差放

vi1 +

-

vi2 -

+

-vod

+

+ vo1

vo2 -

-

差分式放大电路输入输出结构示意图

总输出电压

vo

=

v

od

v oc

A VD v id A VC v ic

第25页/共55页

5.主要技术指标计算(P265)

vi1

=

vic

1 2

vid

vi2

=

vic

1 2

vid

假设 AV1 = 100, AV2 = 100, AV3 = 1 。 若第一级漂了100 uV, 则输出漂移 1 V。 若第二级也漂了100 uV, 则输出漂移 10 mV。

采用差分式放大电路

第14页/共55页

漂移 1 V+ 10 mV

6.2.2 基本差分式放大电路

1. 电路组成 两个BJT特性一致,参数相等。

第27页/共55页

(1) 双入双出AVD(P265)

负载开路

时:

AVD

=

Vo Vid

= Vo1 Vo2 Vi1 Vi2

= 2Vo1 Vo1

无论Rc值如何, IC2电流值保持不变(前提:电源要稳定)

第6页/共55页

当较小时,可用 带缓冲级的镜像电流源

增加T0,使IC更加接近IREF 三、镜像电流源特点 1 内阻ro一般在几百千欧以上

2. 电流受电源波动影响大; 3. 电流最低至mA级。 4. 具有温度补偿特性。

第7页/共55页

6.1.2微电流源(P259)

第24页/共55页

+

+

-vid

差放

vi1 +

-

vi2 -

+

-vod

+

+ vo1

vo2 -

-

差分式放大电路输入输出结构示意图

总输出电压

vo

=

v

od

v oc

A VD v id A VC v ic

第25页/共55页

5.主要技术指标计算(P265)

vi1

=

vic

1 2

vid

vi2

=

vic

1 2

vid

假设 AV1 = 100, AV2 = 100, AV3 = 1 。 若第一级漂了100 uV, 则输出漂移 1 V。 若第二级也漂了100 uV, 则输出漂移 10 mV。

采用差分式放大电路

第14页/共55页

漂移 1 V+ 10 mV

6.2.2 基本差分式放大电路

1. 电路组成 两个BJT特性一致,参数相等。

第27页/共55页

(1) 双入双出AVD(P265)

负载开路

时:

AVD

=

Vo Vid

= Vo1 Vo2 Vi1 Vi2

= 2Vo1 Vo1

集成电路设计与制造的主要流程框架(PPT 48张)

第四阶段:时序验证与版图设计 任务:静态时序分析从整个电路中提取出所有 时序路径,然后通过计算信号沿在路径上的延 迟传播,找出违背时序约束的错误(主要是 SetupTime 和 HoldTime),与激励无关。在深亚 微米工艺中,因为电路连线延迟大于单元延迟, 通常预布局布线反复较多,要多次调整布局方 案,对布局布线有指导意义。 流程:预布局布线(SDF文件)--网表仿真(带延时 文件)--静态时序分析--布局布线--参数提取-SDF文件--后仿真--静态时序分析--测试向量生 成。

第一阶段:项目策划 任务:形成项目任务书 (项目进度,周期管理等)。流 程:市场需求--调研--可行性研究--论证--决策--任务 书。 第二阶段:总体设计 任务:确定设计对象和目标,进一步明确芯片功能、 内外部性能要求,参数指标,论证各种可行方案,选 择最佳方式,加工厂家,工艺水准。 流程:需求分析--系统方案--系统设计--系统仿真。 输出:系统规范化说明(System Specification):包括系 统功能,性能,物理尺寸,设计模式,制造工艺,设计周期, 设计费用等等.

流程:逻辑设计--子功能分解--详细时序框图--分块 逻辑仿真--电路设计(算法的行为级,RTL级描述)-功能仿真--综合(加时序约束和设计库)--电路网表-网表仿真。 输出: 功能设计(Function Design):将系统功能的实现方案 设计出来.通常是给出系统的时序图及各子模块之 间的数据流图。 逻辑设计(Logic Design):这一步是将系统功能结构 化.通常以文本(Verilog HDL 或VHDL),原理图,逻辑 图表示设计结果,有时也采用布尔表达式来表示设 计结果。 电路设计(Circuit Design):电路设计是将逻辑设计表 达式转换成电路实现。

模拟集成电路的设计流程89页PPT

Hspice: 作为业界标准的电路仿真工具,它自带了许多器 件模型,包括小尺寸的MOSFET和MESFET。Cadence提 供了hspice的基本元件库并提供了与Hspice的全面的接口。

Spectre: 由Cadence开发的电路仿真器,在SPICE的基础 上进行了改进,使得计算的速度更快,收敛性能更好。

2019/11/15

共88页

29

其它有关的菜单项(1)

Tools/Parametric Analysis

它提供了一种很重要的分析方法——参量分 析的方法,也即参量扫描。可以对温度,用 户自定义的变量(variables)进行扫描,从 而找出最合适的值。

2019/11/15

共88页

30

其它有关的菜单项(2)

举个例子:标识3db的点,我们用到的表达式如下: bandwidth(VF(“/Out),3,“low”)。

需要注意的是:表达式一般都是通过计算器(caculator)输入的。Cadance 自带的计算器功能强大,除了输入一些普通表达式以外,还自带有一些特殊

表达式,如bandwidth、average等等。

2019/11/15

共88页

6

一、进入Cadence软件包

方法一

安装并运行exeed软件, 使用putty软件(缘网下 载),在Host name处填 工作站地址,端口默认, 协议(protocol)选SSH, 如图所示,然后点击 Open。

2019/11/15

共88页

7

1、键入用户名和密码, 在提示符处键入: source/opt/demo/cds. env(回车)

口

退出

23

Setup菜单

Setup菜单

Spectre: 由Cadence开发的电路仿真器,在SPICE的基础 上进行了改进,使得计算的速度更快,收敛性能更好。

2019/11/15

共88页

29

其它有关的菜单项(1)

Tools/Parametric Analysis

它提供了一种很重要的分析方法——参量分 析的方法,也即参量扫描。可以对温度,用 户自定义的变量(variables)进行扫描,从 而找出最合适的值。

2019/11/15

共88页

30

其它有关的菜单项(2)

举个例子:标识3db的点,我们用到的表达式如下: bandwidth(VF(“/Out),3,“low”)。

需要注意的是:表达式一般都是通过计算器(caculator)输入的。Cadance 自带的计算器功能强大,除了输入一些普通表达式以外,还自带有一些特殊

表达式,如bandwidth、average等等。

2019/11/15

共88页

6

一、进入Cadence软件包

方法一

安装并运行exeed软件, 使用putty软件(缘网下 载),在Host name处填 工作站地址,端口默认, 协议(protocol)选SSH, 如图所示,然后点击 Open。

2019/11/15

共88页

7

1、键入用户名和密码, 在提示符处键入: source/opt/demo/cds. env(回车)

口

退出

23

Setup菜单

Setup菜单

模拟集成电路设计流程(ppt 54页)

source cshrc.iclab

cp ~wanghan/CMOS/cds.lib . ( “.”指当前文件夹)

cp /soft1/cdsmgr/cadence/IC5141/tools.Inx86

(接上行)/dfII/cdsuser/.cds init ~ (设置Cadence快捷键)

setdt ic

需要注意的是:表达式一般都是通过计算器(caculator) 输入的。Cadance自带的计算器功能强大,除了输入一些 普通表达式以外,还自带有一些特殊表达式,如

bandwidth、average等等。

2019/11/14

共88页

24

Calculator的使用

Calculator是 一个重要的数 据处理工具, 可以用来仿真 电源抑制比, 相位裕度,共

口

退出

18

Setup菜单

Setup菜单

Design Simulator/directory/host Temperature Model Library Environment

选择所要 模拟的线

路图

选择模拟使用 的模型一般有

cdsSpice hspiceS spectre等

设置模拟 时的温度

设置库文件 的路径和仿 真方式,修 改工艺角

共88页

14

生成symbol

进入“Virtuoso Schematic Editing: mylib nand2 schematic”窗口。

Design -> Create Cellview->From Cellview

在Cellview From Cellview窗口,From View Name栏为:schematic,Tool / Data Type栏为Composer-Symbol。

模拟集成电路教学课件PPT

放大倍数减小,从而增加共模抑制 比,理想的恒流源相当于阻值为无 穷的电阻,所以共模抑制比是无穷。

26

例 T1、T2、T3均为硅管,

β1 β2 50,β3 80, 求: 当ui 0时,uO 0V。

(1)I C3、I C2、I E、U CE3、U CE2 及Re2的值;

(2)Au Aud2 Au2 ; (3)当ui 5mV时,uO ? (4)当输出接一个12k负载

=

uoc

uo2 =Auc2uic

+

Aud2uid 2

=

uoc

uO uo uo1 uo2 Aud1uid uod

uO ≠0 ——有输出!

uo uo1 uo2 0

uO = 0 ——没有输出!

输入有差别,放大器才有输出 ——差分式放大器

uo uod

17

18

温度变化 和电源电 压波动

651实际集成运放的主要参数大信号动态特性放大电路在闭环状态下输入为大信号例如阶跃信号时输出电压对时间的最大变化速率即maximsin2ftom651实际集成运放的主要参数大信号动态特性不要求指运放输出最大峰值电压时允许的最高频率即3500vsom电源电压抑制比ksvr不要求衡量电源电压波动对输出电压的影响不要求651实际集成运放的主要参数参看p291表651典型集成运算放大器参数集成运放的选用根据技术要求应首选通用型运放当通用型运放难以满足要求时才考虑专用型运放这是因为通用型器件的各项参数比较均衡做到技术性与经济性的统一

rbe (1 3 )Re3

3.9(无RL )

Av Avd2 Av2 195

(3) 差分电路的共模增益

Avc2

26

例 T1、T2、T3均为硅管,

β1 β2 50,β3 80, 求: 当ui 0时,uO 0V。

(1)I C3、I C2、I E、U CE3、U CE2 及Re2的值;

(2)Au Aud2 Au2 ; (3)当ui 5mV时,uO ? (4)当输出接一个12k负载

=

uoc

uo2 =Auc2uic

+

Aud2uid 2

=

uoc

uO uo uo1 uo2 Aud1uid uod

uO ≠0 ——有输出!

uo uo1 uo2 0

uO = 0 ——没有输出!

输入有差别,放大器才有输出 ——差分式放大器

uo uod

17

18

温度变化 和电源电 压波动

651实际集成运放的主要参数大信号动态特性放大电路在闭环状态下输入为大信号例如阶跃信号时输出电压对时间的最大变化速率即maximsin2ftom651实际集成运放的主要参数大信号动态特性不要求指运放输出最大峰值电压时允许的最高频率即3500vsom电源电压抑制比ksvr不要求衡量电源电压波动对输出电压的影响不要求651实际集成运放的主要参数参看p291表651典型集成运算放大器参数集成运放的选用根据技术要求应首选通用型运放当通用型运放难以满足要求时才考虑专用型运放这是因为通用型器件的各项参数比较均衡做到技术性与经济性的统一

rbe (1 3 )Re3

3.9(无RL )

Av Avd2 Av2 195

(3) 差分电路的共模增益

Avc2

相关主题

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

模拟集成电路的设计流程

1.交互式电路图输入

全定制

2.电路仿真(spectre)

3.版图设计 (virtuoso)

4.版图的验证(DRC LVS) (calibre)

5.寄生参数提取(calibre)

6.后仿真 (spectre)

7.流片(gdsii)

2020/6/17

共88页

1

Cadence中Spectre的模拟仿真

在命令行输入 source /eva02/dept23/uwb03/.cshrc.ic23 icfb& 红色界面的IC5141窗口出现,之后ciw弹出来

2020/6/17

共88页

3

二、建立可进行SPECTRE模拟 的单元文件

主窗口分为信息窗口 CIW、命令行以及主 菜单。信息窗口会给 出一些系统信息(如 出错信息,程序运行 情况等)。在命令行 中可以输入某些命令。

2020/6/17

共88页

10

编辑完成的电路图

2020/6/17

共88页

11

一些快捷键

以下是一些常用的快捷键: i 添加元件,即打开添加元件的窗口; [ 缩小两倍; ] 扩大两倍; w 连线(细线); f 全图显示; p 查看元件属性; m 整体移动(带连接关系); shift+m 移动(不带连接关系)。

2020/6/17

共88页

12

生成symbol

进入“Virtuoso Schematic Editing: mylib nand2 schematic”窗口。

在Library Manager 窗口,File->New->Cellview, 在弹出的“Create New File”窗口Cell Name栏中,

opam Tool栏中,选Composer-Schematic OK ,弹出新的原理图编辑窗口

Library

Cell

Schematic Symbol

Tox=3.74n

Vth0=-0.402

u0=8.6m

lambda的选取可以参照razavi书上的lambda与L成反比,

其中L=0.5um时 lambdaN=0.1,lmabdaP=0.2

2模020型/6/中17 各工艺参数定义可参考bsimset.pdf文件共8。8页

6

建立新库、新单元以及新视图

在CIW中,File->New->Library, 在弹出的“New Library”窗口,Name栏中:mylib 选中右下方:Attach to an existing techfile 点击OK,之后弹出图2,选smic18mmrf,点击ok

查看CIW窗口:Tools->Library Manager,在Library 中应有mylib,单击它。

主菜单包括:

1、File菜单 2、Tools菜单 3、Options菜单

2020/6/17

共88页

4

设计环境设置

工艺库工作站目录 /eva02/ic/BA083006/smic18/ 关联工艺库的方法 在cds.lib中加入如下语句(用Vi或Gvim编辑器) INCLUDE /eva02/ic/BA083006/smic18/cds.lib 工艺模型文件目录 /eva02/ic/BA083006/smic18/models/spectre 这个目录下有如下文件 其中ms018_v1p7**是普通器件模型文件,ms018_rf_v1p6**是

3、View则包含多种类型,常用的有schemetic,symbol, layout,calibre等等 ,新建Cellview要注意选择View的类 型。

2020/6/17

共88页

8

添加元件(实例instance)

在弹出的“Virtuoso Schematic Editing:…”窗 口中,左边为工具栏,选instance 图标(或i)

1、进入Cadence软件包 2、建立可进行SPECTRE模拟的单元文件 3、编辑可进行SPECTRE模拟的单元文件 4、模拟仿真的设置(重点) 5、模拟仿真结果的显示以及处理 6、分模块模拟(建立子模块) 7、运页

2

一、进入Cadence软件包

登陆到服务器上后,进入adelibic5这个文件夹(如果没有这个文件夹, 按照vlsi课件实验1自行拷贝)

Layout (View)

Verilog

Library,Cell以及View的关系

1、library(库)的地位相当于文件夹,它用来存放一整个设计 的所有数据,包括子单元(cell)以及子单元(cell)中的 多种视图(view)。新建库时注意选择链接所用工艺pdk 的techfile。

2、Cell(单元)可以是一个简单的单元,像一个与非门, 也可以是比较复杂的单元(由symbol搭建而成)。

RF器件模型文件,我们实验只用到普通器件,因此只需要前 者,电路仿真时Spectre会自动加载这几个文件

2020/6/17

共88页

5

相关工艺参数可以在ms018_v1p7_spe.mdl文件中查到:

N18:

Tox=3.87n (可由此算出Cox)

vth0=0.39(无衬偏效应)

u0=34m

P18:

单击“Add instance”窗口Library栏最右侧 Browser,

弹出“Library Browser-…”窗口,Library选 smic18mmrf,Cell选n18, View选symbol

在“Virtuoso Schematic Editing:…”窗口, 鼠 标左键单击一次,间隔一定距离再单击一次, 这样就增加了2个n18元件,键撤销本次操作 ESC

按照如上方法添加所需要的 NMOS与PMOS以及电阻元件以及pin

2020/6/17

共88页

9

mos管的主要参数

multiplier 表示几个管子并联数 Length 表示沟道长度 ,设计时我们按照长沟道设计L取值

>=1um Total Width 表示总的沟道宽度 Finger Width 表示一个finger的宽度 Fingers 表示finger的个数 Total width = finger witdth × finger width 设计时 尽量使mos管接近方形,而不是长条形

1.交互式电路图输入

全定制

2.电路仿真(spectre)

3.版图设计 (virtuoso)

4.版图的验证(DRC LVS) (calibre)

5.寄生参数提取(calibre)

6.后仿真 (spectre)

7.流片(gdsii)

2020/6/17

共88页

1

Cadence中Spectre的模拟仿真

在命令行输入 source /eva02/dept23/uwb03/.cshrc.ic23 icfb& 红色界面的IC5141窗口出现,之后ciw弹出来

2020/6/17

共88页

3

二、建立可进行SPECTRE模拟 的单元文件

主窗口分为信息窗口 CIW、命令行以及主 菜单。信息窗口会给 出一些系统信息(如 出错信息,程序运行 情况等)。在命令行 中可以输入某些命令。

2020/6/17

共88页

10

编辑完成的电路图

2020/6/17

共88页

11

一些快捷键

以下是一些常用的快捷键: i 添加元件,即打开添加元件的窗口; [ 缩小两倍; ] 扩大两倍; w 连线(细线); f 全图显示; p 查看元件属性; m 整体移动(带连接关系); shift+m 移动(不带连接关系)。

2020/6/17

共88页

12

生成symbol

进入“Virtuoso Schematic Editing: mylib nand2 schematic”窗口。

在Library Manager 窗口,File->New->Cellview, 在弹出的“Create New File”窗口Cell Name栏中,

opam Tool栏中,选Composer-Schematic OK ,弹出新的原理图编辑窗口

Library

Cell

Schematic Symbol

Tox=3.74n

Vth0=-0.402

u0=8.6m

lambda的选取可以参照razavi书上的lambda与L成反比,

其中L=0.5um时 lambdaN=0.1,lmabdaP=0.2

2模020型/6/中17 各工艺参数定义可参考bsimset.pdf文件共8。8页

6

建立新库、新单元以及新视图

在CIW中,File->New->Library, 在弹出的“New Library”窗口,Name栏中:mylib 选中右下方:Attach to an existing techfile 点击OK,之后弹出图2,选smic18mmrf,点击ok

查看CIW窗口:Tools->Library Manager,在Library 中应有mylib,单击它。

主菜单包括:

1、File菜单 2、Tools菜单 3、Options菜单

2020/6/17

共88页

4

设计环境设置

工艺库工作站目录 /eva02/ic/BA083006/smic18/ 关联工艺库的方法 在cds.lib中加入如下语句(用Vi或Gvim编辑器) INCLUDE /eva02/ic/BA083006/smic18/cds.lib 工艺模型文件目录 /eva02/ic/BA083006/smic18/models/spectre 这个目录下有如下文件 其中ms018_v1p7**是普通器件模型文件,ms018_rf_v1p6**是

3、View则包含多种类型,常用的有schemetic,symbol, layout,calibre等等 ,新建Cellview要注意选择View的类 型。

2020/6/17

共88页

8

添加元件(实例instance)

在弹出的“Virtuoso Schematic Editing:…”窗 口中,左边为工具栏,选instance 图标(或i)

1、进入Cadence软件包 2、建立可进行SPECTRE模拟的单元文件 3、编辑可进行SPECTRE模拟的单元文件 4、模拟仿真的设置(重点) 5、模拟仿真结果的显示以及处理 6、分模块模拟(建立子模块) 7、运页

2

一、进入Cadence软件包

登陆到服务器上后,进入adelibic5这个文件夹(如果没有这个文件夹, 按照vlsi课件实验1自行拷贝)

Layout (View)

Verilog

Library,Cell以及View的关系

1、library(库)的地位相当于文件夹,它用来存放一整个设计 的所有数据,包括子单元(cell)以及子单元(cell)中的 多种视图(view)。新建库时注意选择链接所用工艺pdk 的techfile。

2、Cell(单元)可以是一个简单的单元,像一个与非门, 也可以是比较复杂的单元(由symbol搭建而成)。

RF器件模型文件,我们实验只用到普通器件,因此只需要前 者,电路仿真时Spectre会自动加载这几个文件

2020/6/17

共88页

5

相关工艺参数可以在ms018_v1p7_spe.mdl文件中查到:

N18:

Tox=3.87n (可由此算出Cox)

vth0=0.39(无衬偏效应)

u0=34m

P18:

单击“Add instance”窗口Library栏最右侧 Browser,

弹出“Library Browser-…”窗口,Library选 smic18mmrf,Cell选n18, View选symbol

在“Virtuoso Schematic Editing:…”窗口, 鼠 标左键单击一次,间隔一定距离再单击一次, 这样就增加了2个n18元件,键撤销本次操作 ESC

按照如上方法添加所需要的 NMOS与PMOS以及电阻元件以及pin

2020/6/17

共88页

9

mos管的主要参数

multiplier 表示几个管子并联数 Length 表示沟道长度 ,设计时我们按照长沟道设计L取值

>=1um Total Width 表示总的沟道宽度 Finger Width 表示一个finger的宽度 Fingers 表示finger的个数 Total width = finger witdth × finger width 设计时 尽量使mos管接近方形,而不是长条形