实验四:时序逻辑电路的应用

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

时序逻辑电路的应用

●实验目的:

1.实现0-9十进制数计数(使用74LS90,74LS47芯片);2.实现六进制数计数(使用74LS90,74LS47芯片,异步置零);3.实现0 2 4 6 8 1 3 5 7 9 的计数。

●实验原理:

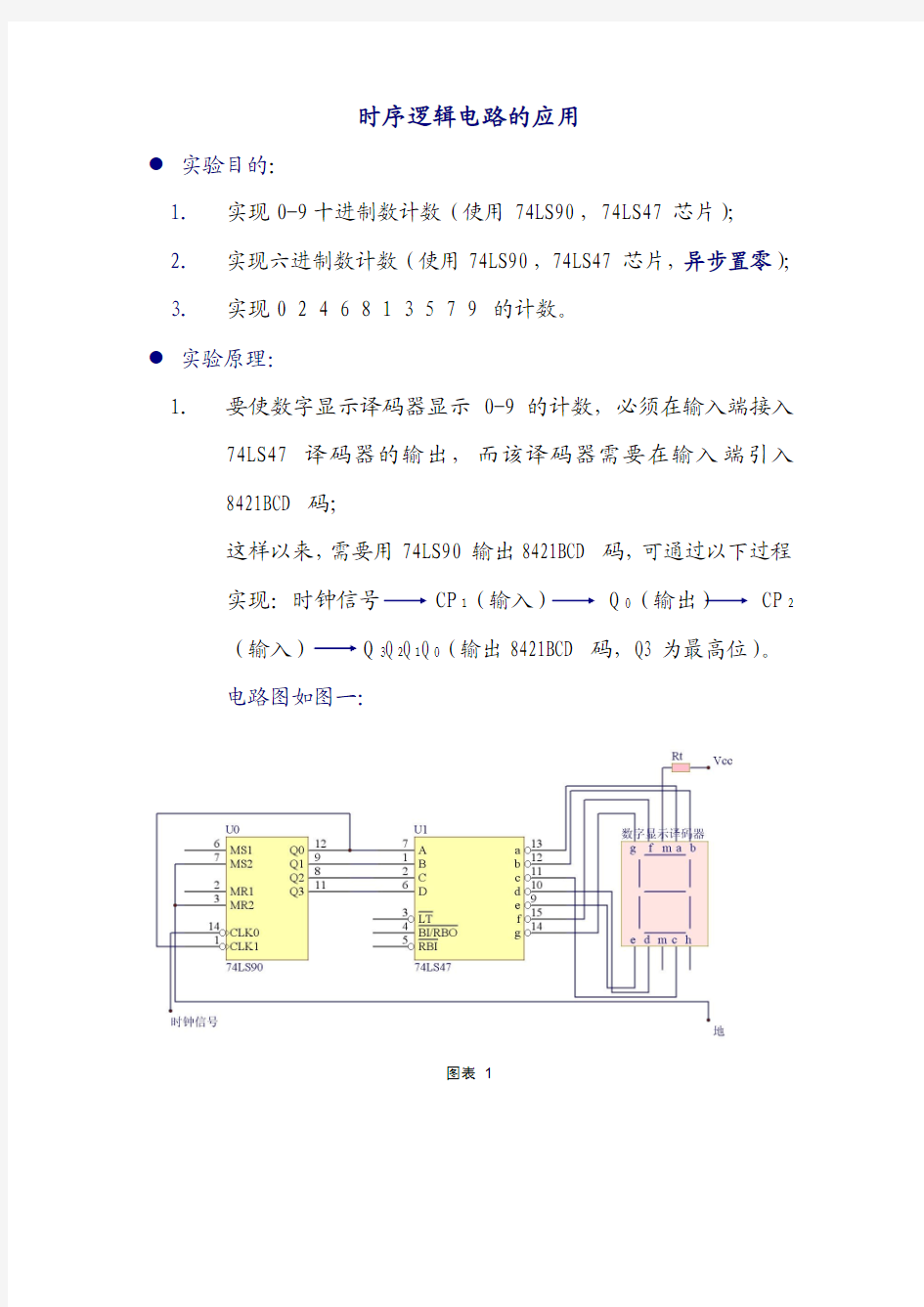

1.要使数字显示译码器显示0-9的计数,必须在输入端接入74LS47译码器的输出,而该译码器需要在输入端引入

8421BCD码;

这样以来,需要用74LS90输出8421BCD码,可通过以下过程

实现:时钟信号 CP1(输入) Q0(输出) CP2

(输入) Q3Q2Q1Q0(输出8421BCD码,Q3为最高位)。

电路图如图一:

图表1

2. 列出74LS90的输出的8421BCD 码与数字显示译码器译码器显

示数字之间的关系:

从这张表格我们可以看到:当输出为0110时,输出应该自动清零;同时我们发现,该时刻Q 2 Q 1同时为一,之前的其它组合并没有这个特点;而且74LS90有两个清零端RV1和RV2,当同时为一是,便自动清零。于是我们只需要将Q 2 Q 1反馈到RV1 RV2,同时74LS4 D 端接地,便

能实现六进制数计数。

电路图如图二:

图表 2

3. 列出74LS90的输入与数字显示译码器译码器显示数字之间

Q 3 Q 2 Q 1 Q 0 显示 0

0 0 0 0 0 0 1 1 0 0 1 0 2 0 0 1 1 3 0 1 0 0 4 0 1 0 1

5

1

1

0 0(6)

的关系和5421BCD 码:

观察以上两张表:将右表的Q 0列移动至最后一列,便得到左表,由此我们可以用74LS90产生5421BCD 码,然后将最高位接入74LS47的最低位A 端,其余依次由高到低接入D C B 。

5421BCD 码的产生方法为:时钟信号 CP 2(输入) Q 3

(输出) CP 1(输入) Q 0Q 3Q 2Q 1(输出5421BCD 码,Q 0为最高位)。

电路图如下图:

Q 3 Q 2 Q 1 Q 0 显示 0 0 0 0 0 0 0 1 0 2 0 1 0 0 4 0 1 1 0 6 1 0 0 0 8 0 0 0 1 1 0 0 1 1 3 0 1 0 1 5 0 1 1 1 7 1

1

9

Q 0 Q 3 Q 2 Q 1 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1

1

图表3

实验内容:

1.按照图一连接实验逻辑电路,然后观察实验结果,与实验要求对比。

注意:*RV1 RV2同时为1时,输出清零,故实验过程中

至少一个应该连着地;

*SP1 SP2同时为1是,输出置9,故实验过程中至少一个应该连着地;

*实验室的数字显示译码器一个M端应该连接一电阻,然后连高电平,另一个悬空。

2.按照图二连接实验逻辑电路,然后观察实验结果,与实验要求对比。

注意:*RV1 RV2接Q2和Q1端,实现异步置零;

* SP1 SP2 M 端连接同上个电路;

*74LS47D端接地。

3.按照图三连接实验逻辑电路,然后观察实验结果,与实

验要求对比。

注意:*实现5421BCD码时Q0为高位,依次为Q3Q2Q1; *RV1 RV2SP1 SP2的接法同1中接法。

实验总结:

1.逻辑电路的设计过程设分灵活,通过列真值表观察其值的变化非常有效;

2.不仅要仔细了解各种基本电路的功能和原理,更重要的是能用它们组合起来实现一定的功能。