飞思卡尔32位嵌入式CPU核心M310简介

cbt-f310技术参数

cbt-f310技术参数

CBT-F310是一款广泛用于工业和商业领域的嵌入式系统。

以下

是关于CBT-F310技术参数的详细介绍:

处理器,CBT-F310采用了英特尔的处理器,具体型号可能会因

生产日期而有所不同,但通常是英特尔Celeron或者英特尔Atom系

列处理器。

这些处理器通常具有低功耗、高性能和稳定性的特点,

适用于嵌入式系统的需求。

内存,CBT-F310通常配备有4GB或8GB的DDR3L内存,这种类

型的内存具有低电压、低功耗和高带宽的特点,适合于嵌入式系统

对内存性能和能效的要求。

存储,CBT-F310通常配备有32GB或64GB的固态硬盘(SSD),这种存储方式具有高速读写、低功耗和抗震抗摔的特点,适合于工

业环境中的数据存储需求。

操作系统,CBT-F310通常预装了Windows 10 IoT企业版操作

系统,这种操作系统专为嵌入式系统设计,具有稳定性高、兼容性

强的特点,适合于工业和商业领域的应用场景。

扩展接口,CBT-F310具有丰富的扩展接口,包括多个USB接口、LAN口、串口、HDMI接口等,可以满足不同应用场景下的扩展需求,比如连接外部设备、显示器、网络等。

外观设计,CBT-F310通常采用铝合金外壳,具有良好的散热性

能和抗干扰能力,适合于工业环境中的长时间稳定运行。

总的来说,CBT-F310作为一款嵌入式系统,具有稳定性高、性

能优越、扩展性强的特点,适合于工业自动化、智能设备、数字标

牌等领域的应用。

希望以上信息能够满足你的需求,如果还有其他

问题,欢迎继续提问。

Cortex-M3_技术介绍

• ARM微处理器及其发展

ARM微处理器的几个系列:

ARM7系列、ARM9系列、 ARM9E系列、 ARM10E系列、 SecurCore系列、Intel的XScale系列、 Cortex系列。

ARM体系结构的发展:

(1)V1~V3版本; (2)V4T版本; (3)V5版本; (4)V6版本; (5)V7版本。

Avatar Semiconductor Co.

选择ARM处理器,ARM7还是 Cortex-M3

Avatar Semiconductor Co.

决策:

那么,你应该如何做出何种选择呢? 如果成本是最主要考虑因素,您应该选择Cortex-M3; 如果在低成本的情况下寻求更好的性能和改进功耗,您应 该考虑选用Cortex-M3;特别是如果你的应用是汽车和无 线领域,可以采用Cortex-M3,这也正是Coretex-M3的主 要定位市场。 由于Cortex-M3内核中的多种集成元素以及采Thumb-2 指令集,其开发和调试比ARM7TDMI要简单快捷。 TI的Stellaris系列微控制器如今包含了160多种可以向全 球供货的MCU,包括售价低至1美元的MCU。这个价格一 般只有8bit MCU才能达到。

Avatar Semiconductor Co.

Cortex-M3内核简介一:哈佛架构

Cortex-M3 中央内核基于哈佛架构,指令 和数据各使用一条总线(右图中所示)。与 Cortex-M3不同,ARM7 系列处理器使用冯· 诺 依曼(Von Neumann)架构,指令和数据共用 信号总线以及存储器。由于指令和数据可以从 存储器中同时读取,所以 Cortex-M3 处理器 对多个操作并行执行,加快了应用程序的执行 速度。

32位嵌入式处理器的特点及应用

32位嵌入式处理器的特点及应用众所周知,在嵌入式系统中,微处理器用的最多的还是MCU(俗称单片机),主要原因是其性价比高、简单易学。

MCU有4位、8位、16位三大系列,4位MCU主要用在家用电器、儿童玩具领域;16位MCU则用在速度要求较高的工业控制领域;8位MCU是主流,几乎覆盖所有应用领域,其生产厂商(几十家)、产品系列(几百个)、芯片型号(几千种)都是最多的,在所有8位MCU中,51系列占一半以上。

在嵌入式系统所有处理器中,目前32位处理器虽然只占一小部分,但却是不可替代的一部分,而且是嵌入式技术未来的发展方向。

32位嵌入式处理器具有如下特点:●运算速度高,主频高达1G以上,多总线多数据流结构,有些处理器带双核甚至多核CPU。

●内存容量大,内带或外接大容量的Flash和SRAM,多数32位处理器可直接外接大容量的SDRAM。

●硬件功能强大,内置AD/DA、PWM、PLA等,外带GPIO、UART、I2C、SPI、CAN、PCI、USB、1394、以太网等接口。

●支持实时操作系统(WindowsCE、Linux/μClinux、VxWorks、μC/OS-II等),以及多功能人机交互式界面。

目前国内比较流行的32位嵌入式处理器有:x86系列、ARM、DSP、PowerPC等。

1、x86系列(Intel或AMD)源自PC机,在嵌入式系统中用到较多的是486、586和Pentium CPU,其特点是硬件系统基本上使用标准板(PC104,3.5“或Mini-ITX单板机),软件开发也很方便,利用PC机平台就可以,且有大量第三方免费软件可以使用,操作系统以DOS、WindowsCE为主。

x86系列主要用在工业控制、医疗设备、无线网络设备、数字多媒体系统、机顶盒等领域。

这里需要特别推荐两款性价比极高且与x86指令兼容的CPU:Intel Atom(凌动)-主要用在Mini-ITX中,Transmeta Crusoe TM5xxx系列- 主要用在PC104中。

ARM Cortex-M0+处理器简介

ARM Cortex-M0+处理器2012年3月14日,中国上海——ARM今天发布了一款拥有全球最高功耗效率的微处理器——ARM® Cortex™-M0+处理器。

该款经过优化的Cortex-M0+处理器可针对家用电器、白色商品、医疗监控、电子测量、照明设备以及功耗与汽车控制器件等各种广泛应用的智能传感器与智能控制系统,提供超低功耗、低成本微控制器(MCU)。

ARM Cortex-M0+处理器为物联网发展奠定基础作为ARM Cortex处理器系列的最新成员,32位Cortex-M0+处理器采用了低成本90纳米低功耗(LP)工艺,耗电量仅9µA/MHz,约为目前主流8位或16位处理器的三分之一,却能提供更高的性能。

这种行业领先的低功耗和高性能的结合为仍在使用8位或16位架构的用户提供了一个转型开发32位器件的理想机会,从而在不牺牲功耗和面积的情况下,提高日常设备的智能化程度。

Cortex-M0+处理器的特点促成了智能、低功耗微控制器的面市,并为“物联网”中大量的无线连接设备提供高效的沟通、管理和维护。

低功耗联网功能深具潜能,可驱动各种节能和生活关键应用,包括从无线方式分析住宅或办公大楼性能与控制的感测器,到以电池运作、通过无线方式连接健康监控设备的身体感测器。

而现有的8位或16位微控制器(MCU)缺少足够的智能和功能来实现这些应用。

半导体行业调研咨询公司The Linley Group高级分析师、《微处理器报告》(Microprocessor Report)高级编辑,Tom R. Halfhill表示:“众所周知,不断改进功耗效率、安全性和便利性的物联网将最终改变世界。

从自适应室内照明、在线视频游戏到智能传感器和电机控制,无处不在的网络连接几乎对任何事物都是有益的。

但是,实现这一切需要极低成本、极低功耗并拥有良好性能的处理器。

ARM Cortex-M0+处理器为轻量级芯片提供了32位的强劲性能,适合于各种工业与消费应用。

CortexM3微控制器概述

基于ARM低成本和高效的处理器设计方案,得到 授权的厂商生产了多种多样的的处理器、单片机以及 片上系统(SoC)。这种商业模式就是所谓的“知识产权授 权”。

ARMv7架构的闪亮登场。在这个版本中,内核架构首次 从单一款式变成3种款式。

款式A:设计用于高性能的“开放应用平台”——越来越 接近电脑了

内建的嵌套向量中断控制器

Cortex-M3在内核水平上搭载了一颗中断控制器——嵌套向量中断控制器 NVIC(Nested Vectored Interrupt Controller)。

NVIC提供如下的功能: • 可嵌套中断支持 • 向量中断支持 • 动态优先级调整支持 • 中断延迟大大缩短 • 中断可屏蔽

存储器映射

从图中可见,不像其它的ARM架构,它们的存储器映 射由半导体厂家说了算, Cortex-M3预先定义好了“粗线条 的”存储器映射。通过把片上外设的寄存器映射到外设区, 就可以简单地以访问内存的方式来访问这些外设的寄存器, 从而控制外设的工作。

中断和异常

虽然CM3是支持240个外中断的,但具体使用了多少 个是由芯片生产商决定。 CM3还有一个NБайду номын сангаасI (不可屏蔽 中断)输入脚。当它被置为有效(assert)时, NMI服务 例程会无条件地执行。

开发工具

在开始使用Cortex-M3之前,需要准备好一些开发工具,典型的如: • 编译器/汇编器:把C和汇编源程序转换成目标文件。几乎所有的C编译器套件 都包含了对应的汇编器。 • 指令系统模拟器:模拟指令的执行,用于在软件开发早期的调试。 • 在 线 仿 真 器 ( ICE) 或 者 调 试 探 测 器 ( probe) : 连 接 到 电 脑 和 目 标 板 上 的 调 试 硬 件 , 与 目 标 板 的 接 口 通 常 是 JTAG或 SW。 • 一块开发板。 • 跟踪捕捉仪:可选的硬件设备和周边软件,可以用它来捕捉来自DWT以及ITM 的输出,并且以可读的形式显示出来。 • 嵌入式操作系统:在单片机上运行的操作系统。这也是一个可选件,许多简单 的应用程序不需要操作系统。但是在开发复杂度较高或者有高性能指标的系统时, 常常需要使用。

EFM32 Cortex参考手册

EFM32 Cortex-M3参考手册1.简介1.1 关于此文档本文档提供了使用EFM32微处理器ARM Cortex-M3内核所需的信息。

EFM32设备内的具体实现细节可以参考手册和特定的设备数据表。

此文档适应于单片机软件和硬件工程师,包括对ARM设备没有相关经验的人员。

1.2 关于EFM32 Cortex-M3处理器和核心外围设备EFM32 Cortex-M3处理器是一个高性能的32位处理器,是为微处理器市场而设计的。

它为开发人员提供了显著便利,包括:●优秀的处理性能和快速中断处理●加强型系统与灵活的断点调试和跟踪能力●高效的处理器内核,系统和存储●超低功耗集成的睡眠模式●平台安全和存储保护单元(仅部分设备可用)。

Cortex-M3处理器是建立在一个高性能的处理器内核,三级管道哈佛架构,使它成为嵌入式应用程序的理想选择。

处理器通过一个高效的指令集提供特殊工作效率,广泛的优化设计,提供高端处理硬件包括单循环32 x32乘法和专用硬件门。

为了便于低成开发本产品,Cortex-M3处理器采用紧耦合组件系统,降低处理器复杂度,同时显著改善中断处理和系统调试的能力。

Cortex-M3处理器采用一个版本Thumb指令集,确保高密度代码,减少程序需求内存。

Cortex-M3指令集提供了一个新型32位架构,拥有良好性能。

是高密度代码的8位/16位微处理器。

Cortex-M3处理器集成了一个可配置的嵌套中断控制器,提供行业领先的中断性能。

NVIC包括屏敝中断,并提供多达8个中断优先级级别。

处理器核心集成度高,NVIC提供快速执行中断服务程序,极大地减少了中断延迟。

这是通过寄存器的硬叠加实现的。

拥有多重装载和存储多重操作能力。

中断处理程序不需要任何汇编存根,以消除任何代码的ISR上的开销。

Tail-chaining优化也显著减少了从一个ISR切换到另一个ISR上的开销。

降低功耗优化设计,NVIC 集成与睡眠模式,包括深度睡眠功能,能使整个装置迅速关机。

第2章STM32F107内核架构

512MB 片上外设

0x4000_0000 0x3FFF_FFFF

512MB SRAM

0x2000_0000 0x1FFF_FFFF

512MB 代码区

0x0000_0000

芯片厂商自定义

0xE010_0000-0xFFFF_FFFF

外部私有外设总线

ROM表 外部PPB

Option bytes 配置字 System memory 系统存储器

保留 Flash 保留

影射到Flash或是系统存储器 (取决于启动配置管脚)

0x1FFF_F800-0x1FFF_FFFF 0x1FFF_B000-0x1FFF_F7FF 0x0804_0000-0x1FFF_AFFF 0x0800_0000-0x0803_FFFF 0x0004_0000-0x0007_FFFF

通道1 通道2

DMA请求

通道5

DMA请求

SPI3/I2S SPI2/I2S

IWDG WWDG

RTC TIM7 TIM6 TIM5 TIM4 TIM3 TIM2

Ethernet MAC 以太网模块

USB OTG FS USB模块

-6-

存储器组织

CM3支持4GB的存 储空间,用来映射 程序存储器、数据 存储器、外设寄存 器。

0xFFFF_FFFF

512MB 内核外设

0xE000_0000 0xDFFF_FFFF

1GB 未使用

0x6000_0000 0x5FFF_FFFF

512MB 片上外设

0x4000_0000 0x3FFF_FFFF

512MB SRAM

0x2000_0000 0x1FFF_FFFF

CCM3118多功能32位嵌入式微控制器

CCM3118多功能32位嵌入式微控制器

肖佐楠;竺际隆

【期刊名称】《电子产品世界》

【年(卷),期】2004(000)013

【摘要】苏州国芯科技公司在2003年底前已取得Motorola公司授权转让的

M*CORE M210和M310的设计许可.并在上海中芯国际的0.180μm工艺线上完或了验证。

在此基础上生产的C210和C310 CPU已开始正式提供给国内用户使用,国芯科技同时提供自动化性能极高的C*SOC200设计平台.使设计SOC 芯片时能

【总页数】2页(P82-83)

【作者】肖佐楠;竺际隆

【作者单位】苏州国芯科技公司;苏州国芯科技公司

【正文语种】中文

【中图分类】TP368.1

【相关文献】

1.飞思卡尔宣布面向汽车应用推出最强大的多功能32位微控制器 [J],

M3118多功能32位嵌入式微控制器 [J], 肖佐楠;竺际隆

3.飞思卡尔宣布面向汽车应用推出功能强大的多功能32位微控制器 [J], 飞思卡尔半导体公司

4.飞思卡尔面向汽车应用推出强大的多功能32位微控制器 [J], 飞思卡尔半导体公司

5.ST推出全新的STM32F0系列32位微控制器基于ARMCortex—MO内核——沿用STM32的DNA,M0系列多功能超值ARM Cortex微控制器简化家电和工业控制应用开发任务 [J], 无

因版权原因,仅展示原文概要,查看原文内容请购买。

stm32f107

Core: ARM 32-bit Cortex-M3 Microcontroller, CPU clock up to 72MHz

Memories: 256kB Embedded Flash 64kB Embedded SRAM Specific Features: - USB 2.0 Full Speed Device/Host/OTG Controller with on-chip PHY - 10/100 Ethernet MAC with dedicated DMA and SRAM - 12-channel DMA controller支持的外设:定时器、ADC、SPI、I2C和USART - 2 * CAN Interface (2.0B Active) - 2 * 12-bit ADC (16-channel) - 2 * 12-bit DAC - 2 * I2C - 5 * UART - 3 * SPI - 80 GPIO pins Common Features: PLL, Embedded Internal RC 8MHz and 32kHz, Real-Time Clock, Nested Interrupt Controller, Power Saving Modes, JTAG and SWD, four 16-bit Timers with Input Capture, Output Compare and PWM or Pulse Counter and Quadrature Encoder Input, 16-bit Motor Control PWM, two Watchdog Timers, SysTick Timer, two 16-bit Basic Timers for DAC, CRC Calculation Unit (96-bit unique ID)

arm cortex-m3全可编程soc原理

arm cortex-m3全可编程soc原理如下:

1.架构:Cortex-M3 核心是基于ARMv7-M 架构,这是一个针对

嵌入式应用程序优化的架构。

它包含一个ARM 指令集、一个

ARM 连接至程序的接口以及一些特定于嵌入式应用的扩展。

2.核心功能:Cortex-M3 核心具有高性能、低功耗和低成本的特

点。

它包含一个32 位RISC 处理器,具有一个三级流水线。

核心还包含一个嵌套向量中断控制器,允许高效的异常和中断

处理。

3.可编程性:Cortex-M3 是完全可编程的。

这意味着硬件和软件

都可以通过编程来定制。

ARM 的微控制器工具链(如Keil 或

IAR)可用于编译和调试代码,以适应特定的应用需求。

4.系统集成:SoC 是一种将多个硬件组件集成到一个单一芯片上

的技术。

在Cortex-M3 中,这些组件可能包括内存、通信接口、

ADC、DAC 等。

通过将所有这些组件集成到单个芯片上,可以

降低系统成本、减小体积并提高可靠性。

5.低功耗:Cortex-M3 被设计为低功耗微控制器,适用于电池供

电的应用。

它具有多种低功耗模式,可以在不使用时降低功耗。

6.安全性:Cortex-M3 提供了多种安全特性,如内存保护单元

(MPU)和安全区域(Secure Zone),以保护敏感数据和代码。

cortex-m3工作模式_工作原理_理论说明以及概述

cortex-m3工作模式工作原理理论说明以及概述1. 引言1.1 概述Cortex-M3是一款基于ARM架构的微控制器处理器,它在嵌入式系统中具有广泛应用的能力。

该处理器以低功耗、高性能和可靠性著称,广泛应用于各种嵌入式系统中,如汽车电子、智能家居、医疗设备等领域。

本文将对Cortex-M3的工作模式和工作原理进行深入探讨,并介绍了相关的理论知识。

1.2 文章结构本文共分为5个部分。

首先,在引言部分简要介绍了Cortex-M3处理器的概述、应用领域和重要性。

其次,在第2部分“Cortex-M3工作模式”中,我们将详细解释什么是Cortex-M3的工作模式,并列举常见的工作模式及其特点,最后还将介绍工作模式之间的切换过程。

第3部分“Cortex-M3工作原理”将对该处理器的架构概述、处理器核心详解以及访存交互机制进行详细说明。

然后,第4部分“Cortex-M3理论说明”将介绍ARM指令集简介、硬件保护和栈管理以及特殊功能寄存器(SFR)的作用和使用方法。

最后,在第5部分“结论”中,我们将对全文进行总结,并提出进一步研究方向的建议。

1.3 目的本文的目的在于全面了解和掌握Cortex-M3处理器的工作模式、工作原理以及相关理论知识。

通过学习本文,读者将能够理解Cortex-M3在嵌入式系统中运行的方式和机制,从而为嵌入式系统设计与开发提供有力支持。

同时,本文还可以为进一步深入研究该领域奠定基础,并为相关技术人员提供参考资料。

2. Cortex-M3工作模式:2.1 工作模式定义:Cortex-M3是一种高性能、低功耗的32位嵌入式处理器核,具备多种工作模式以满足不同应用需求。

工作模式是指处理器在执行任务时所处的状态。

2.2 常见的工作模式:在Cortex-M3中,常见的工作模式包括运行、睡眠和待机。

以下分别介绍这些工作模式:- 运行(Run):在运行模式下,处理器核心处于正常运行状态,可以执行指令,并响应中断请求。

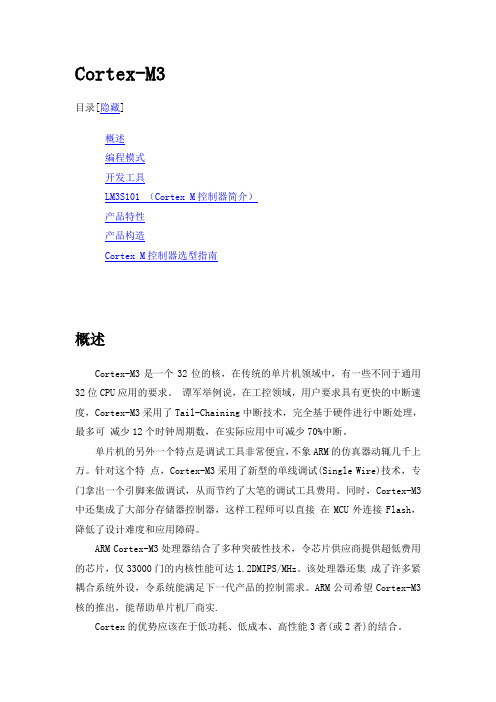

Cortex-M3

Cortex-M3目录[隐藏]概述编程模式开发工具LM3S101 (Cortex M控制器简介)产品特性产品构造Cortex M控制器选型指南概述Cortex-M3是一个32位的核,在传统的单片机领域中,有一些不同于通用32位CPU应用的要求。

谭军举例说,在工控领域,用户要求具有更快的中断速度,Cortex-M3采用了Tail-Chaining中断技术,完全基于硬件进行中断处理,最多可减少12个时钟周期数,在实际应用中可减少70%中断。

单片机的另外一个特点是调试工具非常便宜,不象ARM的仿真器动辄几千上万。

针对这个特点,Cortex-M3采用了新型的单线调试(Single Wire)技术,专门拿出一个引脚来做调试,从而节约了大笔的调试工具费用。

同时,Cortex-M3中还集成了大部分存储器控制器,这样工程师可以直接在MCU外连接Flash,降低了设计难度和应用障碍。

ARM Cortex-M3处理器结合了多种突破性技术,令芯片供应商提供超低费用的芯片,仅33000门的内核性能可达1.2DMIPS/MHz。

该处理器还集成了许多紧耦合系统外设,令系统能满足下一代产品的控制需求。

ARM公司希望Cortex-M3核的推出,能帮助单片机厂商实.Cortex的优势应该在于低功耗、低成本、高性能3者(或2者)的结合。

Cortex如果能做到合理的低功耗(肯定要比Arm7 & Arm9要低,但不大可能比430、PIC、AVR低) +合理的高性能(10~50MIPS是比较可能出现的范围) +适当的低成本(1~5$应该不会奇怪)。

简单的低成本不大可能比典型的8位MCU低。

对于已经有8位MCU的厂商来说,比如 Philips、Atmel、Freescale、Microchip还有ST和Silocon Lab,不大可能用Cortex来打自己的8位MCU。

对于没有8位MCU的厂商来说,当然是另外一回事,但他们在国内进行推广的实力在短期内还不够。

CortexM3技术参考手册

CortexM3技术参考手册CortexM3技术参考手册CortexM3是一种基于ARMv7架构的32位微控制器,由ARM公司开发。

它是一种高效、可编程的微控制器,适用于各种嵌入式应用,如工业控制、汽车电子、智能家居等。

本文将介绍CortexM3的技术参考手册,帮助读者更好地了解该微控制器的功能和使用方法。

一、CortexM3架构CortexM3采用ARMv7架构,支持Thumb和Thumb-2指令集。

它采用32位处理器,具有较高的处理效率和灵活的编程能力。

该微控制器具有以下主要特点:1、处理速度:CortexM3采用ARMv7架构,最高运行速度可达100MHz。

2、存储器:CortexM3内置32KB的Flash存储器,可用于存储程序代码和数据。

此外,它还内置了4KB的SRAM,用于存储临时数据。

3、外设接口:CortexM3具有多种外设接口,包括UART、SPI、I2C、ADC等,可满足各种不同的应用需求。

4、调试接口:CortexM3内置调试接口,方便开发人员对程序进行调试和仿真。

二、CortexM3编程CortexM3的编程主要涉及硬件抽象层(HAL)和驱动程序(Driver)的开发。

其中,HAL提供了一组标准的接口函数,用于访问CortexM3的硬件资源。

驱动程序则是在HAL的基础上开发的,用于实现具体的硬件功能。

三、CortexM3应用实例下面以一个简单的例子来说明如何使用CortexM3实现一个基于UART 的通信接口。

1、硬件连接:将CortexM3的UART接口与另一台设备通过串口连接。

2、软件设置:在CortexM3的HAL中配置UART接口的波特率、数据位、停止位等参数。

3、编写程序:编写一个简单的程序,通过UART接口发送和接收数据。

4、调试与测试:通过调试接口对程序进行调试和测试,确保通信正常。

四、总结本文介绍了CortexM3的技术参考手册,包括其架构、编程和应用实例等。

InBOX310嵌入式计算平台

映翰通网络InHand NetworksInBOX 310嵌入式计算平台产品描述今天,ARM架构的处理器结合Android操作系统,为强调视频和图像处理效果的设备制造商带来全新的解决方案。

InBOX310系列嵌入式计算平台应运而生,该系列集成飞思卡尔Cortex-A9架构的处理器i.MX6,支持Android操作系统,为以往依赖X86架构计算平台的设备制造商尤其是媒体广告播放设备制造商,带来功耗更低发热更小的解决方案。

InBOX310支持OpenGLES2.0和OpenVG™1.1硬件加速器,全高清1080P视频编解码硬件引擎,为媒体播放设备提供强劲流畅的视频体验。

InBOX 310具备1个1000M以太网口,支持3G/4G无线网络,无论更新媒体内容,还是实现远程联网,设备“永远在线”。

InBOX 310具备丰富的外围接口,多个串口,USB口,HDMI等接口,使设备可接扫描枪,打印机、二代身份证读卡器、交通一卡通读卡器、POS机,红外触摸屏、摄像头、鼠标,液晶屏等多种外设。

InBOX支持直流12VDC输入和宽温特性,均为工业应用而设计,提供多种API,便于设备制造商读取硬件信息,实现更多开发。

特性和优势●飞思卡尔Cortex-A9架构的处理器i.MX6,带来强劲的计算能力●支持OpenGLES2.0和OpenVG™1.1硬件加速器,支持2D,3D图形加速●全高清1080P视频编解码器,带来酣畅淋漓的视频体验●1000M以太网和3G/4G无线网络带来丰富的网络能力●支持Android操作系统,享受开放的Android开发资源和丰富的Android应用软件●优化的硬件底层驱动带来更稳定快速的网络连接,更流畅的操作体验,更强劲的外设性能●低功耗,无风扇设计●丰富的接口,支持设备厂商外接多种外设产品规格InBox310功能规格项目InBox310处理器系统CPU Freescale i.MX6 Cortex-A9DRAM On-board DDR3 1 GBFlash 8GB eMMC Flash软件支持操作系统Android 4.2.2应用软件兼容Android系统丰富的应用软件支持BS架构媒体发布系统图形处理2D/3D 加速器OpenVG 1.1 for 2D; OpenGL ES 2.0 for 3D视频编解码H.264 HP, MPEG4 ASP, MPEG2 MP图像处理BMP, JPG, PNG, GIFHDMI 1个, 支持 1920x1080,1366x768,1280x720,1024x768 3G/4G网络支持MINI PCIe接口支持LTE、WCDMA(HSPA+)、CDMA2000,天线外置安全功能支持VPN PPTP、IPSEC VPNWiFi支持支持802.11b/g/n,支持Client/AP模式硬件监测看门狗支持定时开机关机支持支持定时开机关机功能USB设备支持支持USB红外触摸屏支持USB摄像头支持USB鼠标电源输入方式DC-input,12 VDC,电源接口为自锁功能的4芯圆形接口Power Reset 开机键通电自启来电时机器自动启动InBox310硬件规格项目InBox310接口以太网端口1*10/1000Mbps快速以太网端口,LAN/WAN串口3个RS232串口,DB9公头USB接口4个USB2.0 Host,每个提供标准500mA电流,1个OTG模式SIM卡座 1.8V/3V,抽屉式卡座 x 1电源接口DC-input,12VDC,电源接口为自锁功能的4芯圆形接口按键1个开/关机键,1个Mode键SD Card 1 SD slot天线接头4G:SMA x 1、 WiFi: RP-SMA x 1WiFi 可选,802.11b/g/n项目InBox310MINI PCIe接口3G/4G网络HDMI 1个,支持 1920x1080,1366x768,1280x720,1024x768外形尺寸(mm)17cm * 15cm * 2.6cm外壳金属结构重量671g防护等级IP40冷却方式无风扇散热电源电源输入DC12V电源接口DC-input,电源接口为自锁功能的4芯圆形接口环境温度环境湿度 5 ~ 95% (无凝霜) 存储温度-40 ~ 85℃工作温度-20~ 70℃(工业级)指示灯电源灯电源供电指示灯状态灯状态指示灯,正常运行时是闪烁Wifi指示灯Wifi指示灯无线网络指示灯无线网络指示灯EMC指标静电EN61000-4-2,level 3 (接触6KV,空气放电8KV)产品尺寸(mm)定购信息产品型号InBOX310 订货号InBox310-<WMNN>-<XXXX>WMNN(无线制式和模块信息)代码定义备注PH09: For China, EuropeanUMTS(HSPA+) Band1/8(900/2100MHz)3GDL00: For ChinaLTE-FDD Band 1/3LTE-TDD Band 38/39/40/41TD-SCDMA Band 34/39UMTS(DC-HSPA+)Band 1EVDO 800MHzCDMA-1x 800MHzEDGE/GPRS/GSM 850/900/1800/1900MHzTH09: For ChinaLTE-FDD Band 1/3/8LTE-TDD Band 38/39/40/41UMTS(DC-HSPA+) 1/5/8/9EDGE/GPRS/GSM 900/1800MHzFH09: For EuropeanLTE-FDD Band 1/2/3/4/5/7/8/20UMTS(DC-HSPA+) Band1/2/5/8EDGE/GPRS/GSM 850/900/1800/1900MHz4GEN00:表示无3G/4G通信模块无模块(未转产)XXXX PLAT(支持智能售货机平台,带售卖软件版本),STD(标准安卓版本)订货规格描述InBox310-PH09-STD:支持联通3G,宽温,标准安卓版本InBox310-DL00-STD:全网通,2G/3G/4G,宽温,标准安卓版本InBox310-TH09-STD:4G五模设备,宽温,标准安卓版InBox310-FH09-STD:4G设备,宽温,标准安卓版,欧洲及亚太使用InBox310-PH09-PLAT:支持联通3G,宽温, 支持平台、带售卖软件版本InBox310-DL00-PLAT:全网通,2G/3G/4G,宽温,支持平台、带售卖软件版本InBox310-TH09-PLAT:4G五模设备,宽温,支持平台、带售卖软件版本InBox310-FH09-PLAT:4G设备,宽温,支持平台、带售卖软件版本,欧洲及亚太使用。

Cortex-M3 处理器_fromARM

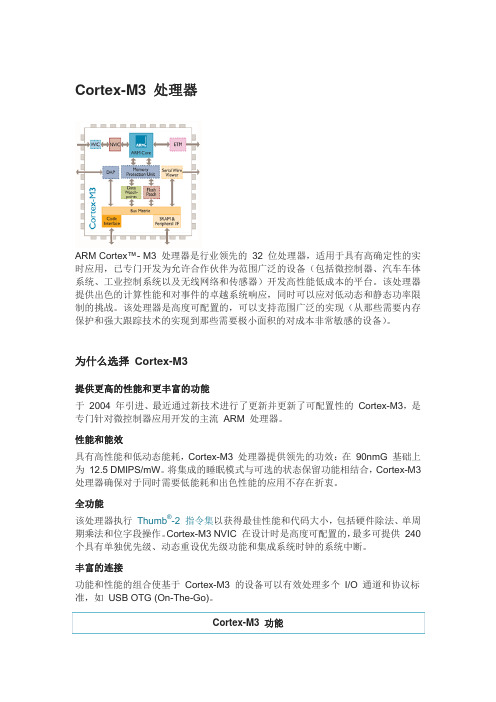

Cortex-M3 处理器ARM Cortex™- M3 处理器是行业领先的 32 位处理器,适用于具有高确定性的实时应用,已专门开发为允许合作伙伴为范围广泛的设备(包括微控制器、汽车车体系统、工业控制系统以及无线网络和传感器)开发高性能低成本的平台。

该处理器提供出色的计算性能和对事件的卓越系统响应,同时可以应对低动态和静态功率限制的挑战。

该处理器是高度可配置的,可以支持范围广泛的实现(从那些需要内存保护和强大跟踪技术的实现到那些需要极小面积的对成本非常敏感的设备)。

为什么选择 Cortex-M3提供更高的性能和更丰富的功能于 2004 年引进、最近通过新技术进行了更新并更新了可配置性的 Cortex-M3,是专门针对微控制器应用开发的主流 ARM 处理器。

性能和能效具有高性能和低动态能耗,Cortex-M3 处理器提供领先的功效:在 90nmG 基础上为 12.5 DMIPS/mW。

将集成的睡眠模式与可选的状态保留功能相结合,Cortex-M3 处理器确保对于同时需要低能耗和出色性能的应用不存在折衷。

全功能该处理器执行Thumb®-2 指令集以获得最佳性能和代码大小,包括硬件除法、单周期乘法和位字段操作。

Cortex-M3 NVIC 在设计时是高度可配置的,最多可提供 240 个具有单独优先级、动态重设优先级功能和集成系统时钟的系统中断。

丰富的连接功能和性能的组合使基于 Cortex-M3 的设备可以有效处理多个 I/O 通道和协议标准,如USB OTG (On-The-Go)。

Cortex-M3 功能Cortex-M3 功能体系结构ARMv7-M(哈佛)ISA 支持Thumb® / Thumb-2管道 3 阶段 + 分支预测Dhrystone 1.25 DMIPS/MHz内存保护带有子区域和后台区域的可选 8 区域 MPU 中断不可屏蔽的中断 (NMI) + 1 到 240 个物理中断中断延迟12 个周期中断间延迟 6 个周期中断优先级8 到 256 个优先级唤醒中断控制器最多 240 个唤醒中断睡眠模式集成的 WFI 和 WFE 指令和“退出时睡眠”功能。

cortex-m3位带操作的基本原理和作用

cortex-m3位带操作的基本原理和作用Cortex-M3是一种32位嵌入式处理器,由ARM公司设计。

它的设计目标是提供高性能和低功耗的解决方案,适用于广泛的嵌入式应用。

Cortex-M3引入了位带操作(Bit-Banding)技术,以提高对位操作的效率。

本文将详细介绍Cortex-M3位带操作的基本原理和作用。

一、Cortex-M3位带操作的基本原理在传统的计算机系统中,对于内存的操作通常是以字节为单位进行的。

例如,如果需要将一些内存位的值设置为1,可以将对应的字节加载到寄存器中,然后在寄存器中使用位运算设置位的值,最后将更改后的字节写回到内存中。

这种方式的效率较低,尤其是对于嵌入式系统来说,位操作的效率对于整个系统的性能至关重要。

Cortex-M3引入了位带操作技术,使得对单个位进行操作更加高效。

该技术通过将每个位映射到内存空间的一个独立地址上来实现。

具体来说,Cortex-M3将每个32位字的一位分配到一个特定的地址,这个地址与字节的地址相对应。

这个映射关系称为位带区域(Bit-Band Region)。

位带操作的基本原理就是通过地址映射,将对单个位的操作映射到一个更高效的内存区域中。

这样可以大大提高位操作的效率,尤其对于嵌入式系统来说十分重要。

二、Cortex-M3位带操作的作用Cortex-M3位带操作技术的引入,为嵌入式系统提供了许多优势和便利。

以下是Cortex-M3位带操作的几个重要作用:1.提高代码执行效率:位带操作使得对单个位的操作更加高效,从而提高了代码的执行速度。

尤其对于在内存中频繁进行位操作的应用,如嵌入式系统的设备驱动程序,位带操作可以显著提升系统性能。

2.减少代码大小:由于位带操作可以直接对单个位进行操作,无需读取和写入整个字节,因此可以减少代码的大小。

这对于存储资源有限的嵌入式系统来说,非常重要。

3.简化位操作的实现:传统方式中,位操作的实现需要进行多次读取和写入操作。

ftc310内核手册

ftc310内核手册欢迎来到FTC310内核手册!FTC310是一种自主研发的嵌入式处理器内核,具有高性能、低功耗和强大的功能。

本手册将为您详细介绍FTC310内核的架构、功能和编程接口,帮助您更好地了解和使用这款处理器内核。

第一部分:FTC310内核架构FTC310内核是一款基于RISC指令集的处理器内核,采用了精简指令集架构(RISC)的设计理念,具有简单、高效和易于实现的特点。

FTC310内核采用了五级流水线的设计,包括取指令、译码、执行、访存和写回五个阶段,可以实现高效的指令执行和流水线操作。

FTC310内核包括一组通用寄存器和专用寄存器,通用寄存器用于存储临时数据和计算结果,专用寄存器用于存储特定功能的控制信息和状态信息。

FTC310内核还包括一组协处理器和附加功能模块,用于支持特定的应用场景和功能需求。

FTC310内核支持多种外设和接口,包括UART、SPI、I2C、GPIO等标准接口,可以方便地连接各种外部设备和传感器,实现数据的输入和输出。

FTC310内核还支持多种通信协议和网络协议,包括TCP/IP协议栈、USB协议栈等,可以实现网络通信和外部设备的连接。

第二部分:FTC310内核功能FTC310内核具有丰富的功能和强大的性能,可以广泛应用于各种嵌入式系统和物联网设备。

FTC310内核支持多种指令集和编程模型,包括C语言、汇编语言等,可以满足不同的开发需求和应用场景。

FTC310内核具有高效的运算能力和优化的指令执行速度,可以实现复杂的算法和处理任务。

FTC310内核支持多种数据类型和运算操作,包括整数运算、浮点运算、逻辑运算等,可以满足不同的计算需求和数据处理需求。

FTC310内核还支持多种存储器和存储器管理功能,包括内部存储器、外部存储器、存储器映射等,可以实现数据的存储和管理。

FTC310内核还支持多种中断和异常处理功能,可以实现系统的稳定和可靠运行。

第三部分:FTC310内核编程接口FTC310内核提供了丰富的编程接口和软件开发工具,帮助开发者快速实现应用程序和系统功能。

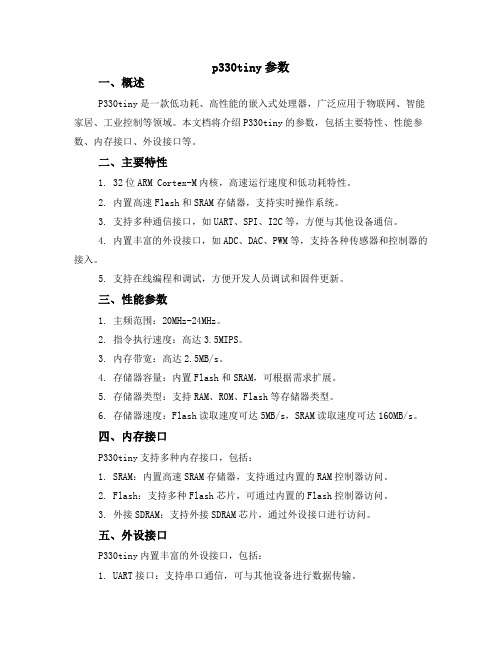

p330tiny参数

p330tiny参数一、概述P330tiny是一款低功耗、高性能的嵌入式处理器,广泛应用于物联网、智能家居、工业控制等领域。

本文档将介绍P330tiny的参数,包括主要特性、性能参数、内存接口、外设接口等。

二、主要特性1. 32位ARM Cortex-M内核,高速运行速度和低功耗特性。

2. 内置高速Flash和SRAM存储器,支持实时操作系统。

3. 支持多种通信接口,如UART、SPI、I2C等,方便与其他设备通信。

4. 内置丰富的外设接口,如ADC、DAC、PWM等,支持各种传感器和控制器的接入。

5. 支持在线编程和调试,方便开发人员调试和固件更新。

三、性能参数1. 主频范围:20MHz-24MHz。

2. 指令执行速度:高达3.5MIPS。

3. 内存带宽:高达2.5MB/s。

4. 存储器容量:内置Flash和SRAM,可根据需求扩展。

5. 存储器类型:支持RAM、ROM、Flash等存储器类型。

6. 存储器速度:Flash读取速度可达5MB/s,SRAM读取速度可达160MB/s。

四、内存接口P330tiny支持多种内存接口,包括:1. SRAM:内置高速SRAM存储器,支持通过内置的RAM控制器访问。

2. Flash:支持多种Flash芯片,可通过内置的Flash控制器访问。

3. 外接SDRAM:支持外接SDRAM芯片,通过外设接口进行访问。

五、外设接口P330tiny内置丰富的外设接口,包括:1. UART接口:支持串口通信,可与其他设备进行数据传输。

2. SPI接口:支持高速串行通信,可与其他SPI设备进行数据传输。

3. I2C接口:支持两线总线通信,可连接多个设备进行数据传输。

4. ADC接口:支持模拟信号转换为数字信号,可连接各种传感器进行数据采集。

5. DAC接口:支持数字信号转换为模拟信号,可连接执行器进行控制输出。

6. PWM接口:支持生成周期性电信号,可实现占空比调节等功能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2 Dec 01

M310S One Pager (3 of 4)

Features and Modes

32-bit load/store RISC architecture with fixed 16-bit instruction length 16-entry 32-bit general-purpose register file Efficient 4-stage execution pipeline, hidden from application software Single-cycle execution for many instructions. Two cycles for branches Branch-folding mode for eliminating short backward loops in the instruction stream Support for byte/halfword/word memory accesses Optimized interfacing to 16-bit memory systems and burst memory devices Fast interrupt support (vectored & autovectored) with 16-entry dedicated alternate register file 32 x 16 hardware multiplier Debug support via JTAG-based OnCE™ Design Dedicated test wrapper with safe-state capability that supports AC testing

» » » » Instruction fetch Instruction decode/register file read Execute Register writeback 32-bit arithmetic/logic unit (ALU) 32-bit barrel shifter Find-first-one unit (FFO) Result feed-forward hardware Support hardware for multiplication and multiple register loads and stores

» Conditional branches (that are not taken) execute in a single clock

2 Dec 01 11 May 00

Microarchitecture Summary (2 of 3) “M310S_CoreGuide”

There are memory load and store operations for byte, halfword, and word (32-bit) data, with automatic zero extension of byte and halfword load data

» Branch target addresses calculated in parallel with branch instruction decode

• There is a single pipeline bubble for taken branches and jumps • Results in an execution time of two clocks

M•CORE Integration Training Course

Overview M•CORE Interface M•CORE Local Bus (MLB) Clock, Reset Bus Arbitration OnCE Debug Support Design For Test M•CORE M210S Reference Platform Testbench Example Summary, Q&A

» These instructions can execute in two clock cycles

Load (ldm) and store (stm) multiple register instructions allow low overhead context save and restore operations

Execution unit consists of:

» » » » »

Program Counter (PC) has a dedicated incrementer and a dedicated branch address adder to minimize delays during change of flow

Integration Guide - provides data required to integrate a VC into an SoC design. Test Guide - provides VC design-for-test data. Verification Guide - provides VC functional verification data. One Pager - provides VC brief technical summary oif features and implementation details.

» These instructions can execute in (N+1) clock cycles, where N represents the number of registers to transfer » Load/store quadrant is a special case operating on R4 - R7

2 Dec 01

M310S One Pager (4 of 4)

Implementation

Bus Type : Modified MLB (all signals rising edge driven) Verilog HDL : Yes Synthesized RTL available : Yes GDSII available : Upon customer request Test Strategy : Full Scan with LBIST Scan Type : Mux D Scan-Flop Test Coverage : 97% DC ATPG Tool : Fastscan >80% of flops gated by Power Compiler Process synthesized : HiP7LP1 Standard Cell Library : SoCDT HiP7LP1 (WCS, 1.35V, 105C) Drawn Size : 3580 x 1400 µm Actual Size : 1074 x 420 µ-m (0.45 mm2) Transistor Count: 313,787 Maximum Frequency at the above PVT : 90MHz Power Dissipation : 0.416mW/MHz Functional AC Coverage : Critical Path .s File

2 Dec 01

Current IP Variances from SRS 3.0

The IP being Supplied is not fully compliant with SRS 3.0 SRS Standards Have evolved over last 2-3 Years Legacy IP Reused and not updated Due to Schedule/Resource Limitations, Some Cases M310S is Closer to SRS 3.0 than the M210S. Modules on the MMC2114 are Close to SRS 2.0 Highly Suggested to Consider Conversion to SRS 3.0 Before rolling out too Many Derivatives.

2 Dec 01

Data Calculation

M310S One Pager (1 of 4)

GCR/GSR MUX

Address Generation

General-Purpose Register File 32 bits X 16

Alternate Register File 32 bits X 16

2 Dec 01

Document Usage

Core Guide - describes a VC processor core and provides programming information.

» Referred to for features, signals and operation

2 Dec 01

M310S One Pager (2 of 4)

Overview

The M•CORE™ M310S processor (M310S) is a fully synthesizable version of the semi-custom M310 processor. It has been designed for high-performance and cost-sensitive embedded control applications, with particular emphasis on reduced system power consumption, making it suitable for a number of battery-operated, portable products. M310S extends the original M•CORE M200 Family instruction I set and functionality by integrating an integer array multiplier, improved pipelining of load and store operations, and a deeper instruction buffer to improve memory bandwidth utilization.