(完整word版)Verilog-A30分钟快速入门教程

Verilog语法基础PPT教案学习

#10 num <= rega << 5 ; // num =

01_1000_0000

#10 regb <= rega << 5 ; // regb =

1000_0000

#20 num <= rega >> 3; // num =

00_0000_0001

#20 regb <= rega >> 3 ; // regb =

x

to b");

x

else $display(" a is not

equal to b");

a = 2'b1x;

z

b = 2'b1x;

0

if (a === b)

0

$display(" a is

0

identical to b");

1

else

$display(" a is not

Case等只i能d用e于nt行i为ca描l述t,o不b能"用);于RTL描述。

regc; reg val;

initial begin rega = 4'b0011; regb = 4'b1010; regc = 4'b1x10;

end initial fork

#10 val = rega == regb ; // val = 0

#20 val = rega != regc; // val = 1

第9页/共72页

注意逻辑等与 case等的差别 2‘b1x==2’b0x

值为0,因为不相等 2‘b1x==2’b1x

值为x,因为可能不 相等,也可能相等

Verilog_HDL教程

习题

1. Verilog HDL 是在哪一年首次被 IEEE 标准化的? 2. Verilog HDL 支持哪三种基本描述方式? 3. 可以使用 Verilog HDL 描述一个设计的时序吗? 4. 语言中的什么特性能够用于描述参数化设计? 5. 能够使用 Verilog HDL 编写测试验证程序吗? 6. Verilog HDL 是由哪个公司最先开发的? 7. Verilog HDL 中的两类主要数据类型什么? 8. UDP 代表什么? 9. 写出两个开关级基本门的名称。 10. 写出两个基本逻辑门的名称。

2.3 数据流描述方式

用数据流描述方式对一个设计建模的最基本的机制就是使用连续赋值语句。在连续赋 值语句中,某个值指派给线网变量。 连续赋值语句的语法为:

assign [delay] LHS_net = RHS_ expression;

右边表达式使用的操作数无论何时发生变化, 右边表达式都重新计算, 并且在指定的时延后 变化值被赋予左边表达式的线网变量。时延定义了右边表达式操作数变化与赋值给左边表 达式之间的持续时间。如果没有定义时延值, 缺省时延为 0。 下面的例子显示了使用数据流描述方式对 2-4 解码器电路的建模的实例模型。

module HalfAdder (A, B, Sum, Carry); input A, B; output Sum, Carry;

Verilog教程

系统任务和系统函数在第 10章中详细讲解。

3.5 编译指令

以`(反引号)开始的某些标识符是编译器指令。在 Verilog 语言编译时,特定的编译器指 令在整个编译过程中有效(编译过程可跨越多个文件),直到遇到其它的不同编译程序指令。 完整的标准编译器指令如下 :

18 Verilog HDL 硬件描述语言

下载

3.5.7 `unconnected_drive和`nounconnected_drive

在模块实例化中,出现在这两个编译器指令间的任何未连接的输入端口或者为正偏电路 状态或者为反偏电路状态。

`unconnected_drive pull1 ... /*在这两个程序指令间的所有未连接的输入端口为正偏电路状态(连接到高电平) */ `nounconnected_drive

time_unit 和time_precision 由值1、10、和100以及单位s、ms、us、ns、ps和fs组成。例如:

`timescale 1ns/100ps

表示时延单位为 1ns, 时延精度为 100ps。`timescale 编译器指令在模块说明外部出现 , 并且影响 后面所有的时延值。例如 :

示十进制),h或H(表示十六进制)之一; value是基于 base的值的数字序列。值 x和z以及十

3.5.3 `default_nettype

该指令用于为隐式线网指定线网类型。也就是将那些没有被说明的连线定义线网类型。

`default_nettype wand

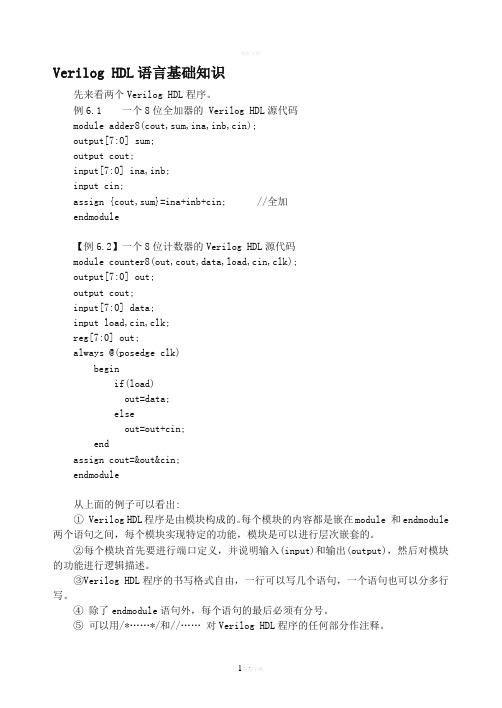

Verilog语言基础知识

在Verilog HDL中,用parameter来定义常量,即用parameter来定义一个标志符,代表一个常量,称为符号常量。其定义格式如下:

parameter 参数名1=表达式,参数名2=表达式,参数名3=表达式……;

例如:

parameter sel=8,code=8'ha3;

//分别定义参数sel为常数8(十进制),参数code为常数a3(十六进制)

Verilog HDL中共有19种数据类型。数据类型是用来表示数字电路中的数据存储和传送单元的。在此介绍4个最基本的数据类型:integer型、parameter型、reg型和wire型。

Verilog HDL中也有常量和变量之分,他们分属以上这些类型。

6.2.1 常量

在程序运行过程中,其值不能被改变的量称为常量。

assign {cout,sum}=ina+inb+cin;//全加

endmodule

【例6.2】一个8位计数器的Verilog HDL源代码

module counter8(out,cout,data,load,cin,clk);

output[7:0]out;

output cout;

input[7:0] data;

6.1.2 Verilog HDL模块的结构

Verilog HDL的基本设计单元是"模块(block)"。一个模块是由两部分组成的,一部分描述接口;另一部分描述逻辑功能,即定义输入是如何影响输出的。下面举例说明,图6.1示出了一个"与-或-非"门电路。

图6.1"与-或-非"电路

该电路表示的逻辑函数可以写为:

6.2.2 变量

Verilog-A

Verilog-A的模拟电路行为模型及仿真作者:朱樟明,张春朋,杨银堂,付永朝关键词:Verilog-A,行为,模型,仿真摘要:分析了模拟硬件描述语言Verilog-A的特点及模型结构,根据仿真速度和仿真精度的折衷考虑,设计实现了模拟开关、带隙基准电压源及运放的Verilog-A行为模型。

根据数模转换器(DAC)的特性,基于Verilog-A设计了DAC参数测试模型,也建立8位DAC 的行为模型。

所有行为模型都在Cadence Spectre仿真器中实现了仿真验证。

随着集成电路技术的不断发展,片上系统(SOC)设计正在成为集成电路设计的发展方向。

SOC芯片集成了大量的IP核,如微处理器、数字信号处理器(DSP)、模/数转换器(ADC)、数/模转换器(DAC)、模拟滤波器、存储器及射频(RF)单元等,使得芯片的设计规模远远超过了以往的设计,其片内通讯及IP核接口的复杂程度也大大提高,从而使其设计的难度和复杂度都达到了前所未有的程度[1],而SOC系统验证就成为了设计的难点。

SOC系统验证就是对基于IP核实现的SOC系统进行功能验证、静态时序分析、功耗分析等,以保证正确的系统功能和良好的产品性能。

以前的SOC验证方法是基于混合信号集成电路仿真方法,其中模拟IP核的仿真则采用Spice仿真方法实现。

虽然这种仿真方法具有较高的仿真精度,但是仿真速度无法满足产品开发的时间要求,也对仿真收敛性提出了新的要求。

本文基于模拟硬件描述语言Verilog-A,研究模拟电路的行为模型及仿真,建立了带隙基准电压源、运放等模拟IP核的精确行为模型。

如果对所有的模拟IP核建立精确行为模型,不仅可以很好的解决SOC的系统验证,也可以解决ADC等混合信号集成电路的参数测试问题。

1模拟硬件描述语言Verilog-AVerilog-A是描述模拟电路系统和模拟电路单元的结构、行为及特性参数的模块化硬件描述语言[2-3],也可以用于描述传统的信号系统,如固体力学、流体力学、热力学等系统。

2Verilog语言快速入门专题培训课件

(3) 关系运算符

> 大于 < 小于 >= 大于等于 <= 小于等于

例: Y=(3>2) Y=(3<2); Y=(3>=2); Y=(3<=2); Y=(3<=1’bx);

结果为1 结果为0 结果为1 结果为0

结果为x

说明 关系运算的结果可能是1(逻辑真)、0(逻辑假)、x(不确定);

2Verilog语言快速入门

Verilog模块结构

module 模块名 ([端口列表]); [端口信号声明;] [参数声明;]

内部信号声明

assign语句

底层模块或门原语 调用(包括生成块)

Initial或always 语句块

任务和函数定义 specify 块(路径延迟)

模块说明部分

说明: 浅色部分用得较少; 常用语句只有三种:

赋值目标必须是wire型的,wire表示电路间的连线。

8

2. assign语句

例:assign M=B|C;

assign Y=A&M;

M

M和Y都必须是wire型的

9

2. assign语句 详见夏宇闻教材第6章,自学。

Verilog具有丰富的表达式运算功能,可用于assign语句

10

(1) 算术型

参数声明要说明参数的名称和初值

6

例: module full_adder (A,B,CIN,S,COUT); input [3:0] A,B; input CIN; output reg [3:0] S; output COUT;

位宽如果不做说明的话,默认是1位; 数据类型不做说明的话,默认是wire型的。

Verilog培训_sh

上拉、下拉电阻 pullup,pulldown

MOS开关 cmos,nmos,pmos,rcmos,rnmos,rpmos

双向开关 tran,tranif0,tranif1,rtran,rtranif0,rtranif1

门电平模型

1 多输入门 and,nand,or,nor,xor,nxor

构化方式,同时还可同时采用三种建模方式。 可以在多个层次上对设计加以描述。 …

Verilog与VHDL的比较

VHDL-VHSIC Hardware Description Language。VHDL于 1987年成为IEEE标准。

Verilog HDL简单易学,语法比较灵活。VHDL语法严谨,需 要较长的时间学会。

常量

共有三类常量:整型、实数型、字符串型。

1 整型

1.1 简单的十进制格式

有符号数,其中负数使用补码形式表示。如:

15

相当于二进制1111

-15

相当于二进制10001

常量

1.2 基数表示法

格式:[位宽] `进制 值

无符号数。

位宽是按照二进制数来计算的。 进制可以为b或B(二进制)、o 或O(八进制)、d或D(十进制)、h或H(十六进制)。值是基于进制的

例: wire tag = flag ? 1’b1 : 1’b0;

6 移位运算符

>> 右移

<< 左移

格式:a >>(<<) n 其中,a是操作数,n表示要移几位

例:Qreg = 4’b0111; Qreg >> 2 结果是4’b0001; Qreg << 2 结果是4’b1100;

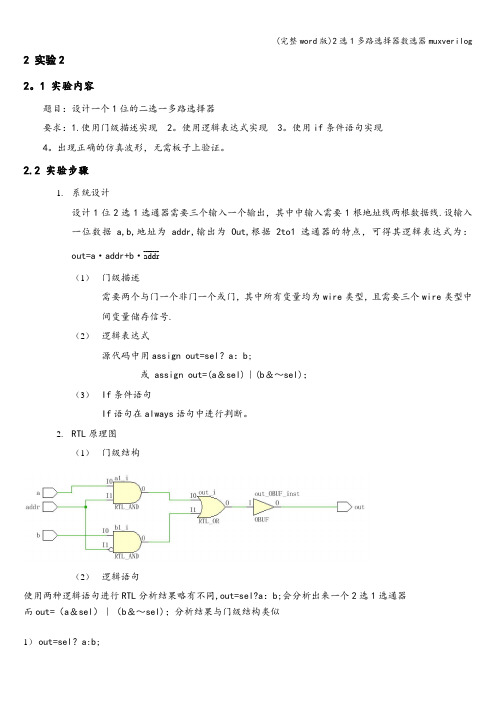

(完整word版)2选1多路选择器数选器muxverilog

2 实验22。

1 实验内容题目:设计一个1位的二选一多路选择器要求:1.使用门级描述实现 2。

使用逻辑表达式实现 3。

使用if条件语句实现4。

出现正确的仿真波形,无需板子上验证。

2.2 实验步骤1.系统设计设计1位2选1选通器需要三个输入一个输出,其中中输入需要1根地址线两根数据线.设输入一位数据a,b,地址为addr,输出为Out,根据2to1选通器的特点,可得其逻辑表达式为:_______out=a·addr+b·addr(1)门级描述需要两个与门一个非门一个或门,其中所有变量均为wire类型,且需要三个wire类型中间变量储存信号.(2)逻辑表达式源代码中用assign out=sel?a:b;或 assign out=(a&sel)|(b&~sel);(3)If条件语句If语句在always语句中进行判断。

2.RTL原理图(1)门级结构(2)逻辑语句使用两种逻辑语句进行RTL分析结果略有不同,out=sel?a:b;会分析出来一个2选1选通器而out=(a&sel)|(b&~sel);分析结果与门级结构类似1)out=sel?a:b;2)out=(a&sel)|(b&~sel);(3)if语句3.重要源代码及注释(1)门级结构module mux2_1(a,b,out,addr);input a,b,addr;output out;wire naddr,a1,b1;//定义中间变量not (naddr,addr);and (b1,b,naddr);and (a1,a,addr);or (out,a1,b1);endmodule(2)逻辑语句module luoji(input a,input b,input sel,output out);assign out=(a&sel)|(b&~sel);endmodule(3)if语句module mux2_1if(a,b,sel,out);input a,b,sel;output out;reg out;always@(a or b or sel)beginif(sel) out=a;else out=b;end2。

Verilog入门

– 数据流型描述

• 通过assign连续赋值实现组合逻辑功能的描 述

第五章 Verilog 语言

Verilog HDL结构

• Verilog HDL是由module模块组成,模块定义关键词 module 开始,到关键词 endmodule结束,每条Verilog语句以分号 “;”作为结束(块语句、编译向导、endmodule等除外)

第五章 Verilog 语言

Verilog概述

• 与C语言的联系与区别

项目 C Verilog

执行顺序

时序概念 语法限制

顺序执行

无延迟 灵活完善

并行执行

存在延迟 限制严格,需 要有数字电路 的知识

第五章 Verilog 语言

Verilog概述

• 抽象层次

– 系统级:C等高级语言描述 – 行为级:模块的功能描述 – RTL级:寄存器与组合电路的合成 – 逻辑门级:基本逻辑门的组合(and, or, nand) – 开关级:晶体管开关的组合(nmos, pmos)

第五章 Verilog 语言

Verilog 语法与实例

• 基本词法定义

– 空白符 : 空格(space bar),TAB 键,return键。 – 注释 (Comment) : “//”或“/*, */”。

第五章 Verilog 语言

Verilog 语法与实例

/* 2-to-1 multiplexer; out = a when sel = 0;out = b when sel = 1; */ module MUX_2(out, a, b, sel); output out; input a, b, sel; //netlist not(sel_, sel); and(a1, a, sel_),(b1, b, sel); or(out, a1, a2); endmodule

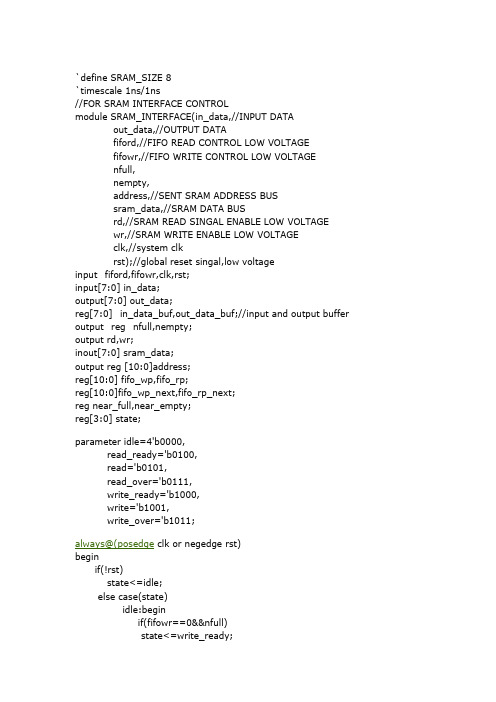

(完整word版)用FPGA实现SRAM读写控制的Verilog代码

`define SRAM_SIZE 8`timescale 1ns/1ns//FOR SRAM INTERFACE CONTROLmodule SRAM_INTERFACE(in_data,//INPUT DATAout_data,//OUTPUT DATAfiford,//FIFO READ CONTROL LOW VOLTAGEfifowr,//FIFO WRITE CONTROL LOW VOLTAGEnfull,nempty,address,//SENT SRAM ADDRESS BUSsram_data,//SRAM DATA BUSrd,//SRAM READ SINGAL ENABLE LOW VOLTAGEwr,//SRAM WRITE ENABLE LOW VOLTAGEclk,//system clkrst);//global reset singal,low voltageinput fiford,fifowr,clk,rst;input[7:0] in_data;output[7:0] out_data;reg[7:0] in_data_buf,out_data_buf;//input and output buffer output reg nfull,nempty;output rd,wr;inout[7:0] sram_data;output reg [10:0]address;reg[10:0] fifo_wp,fifo_rp;reg[10:0]fifo_wp_next,fifo_rp_next;reg near_full,near_empty;reg[3:0] state;parameter idle=4'b0000,read_ready='b0100,read='b0101,read_over='b0111,write_ready='b1000,write='b1001,write_over='b1011;always@(posedge clk or negedge rst)beginif(!rst)state<=idle;else case(state)idle:beginif(fifowr==0&&nfull)state<=write_ready;else if(fiford==0&&nempty)state<=read_ready;elsestate<=idle;endread_ready:state<=read;read:beginif(fiford==1)state<=read_over;elsestate<=read;endread_over:state<=idle;write_ready:state<=write;write:beginif(fifowr==1)state<=write_over;elsestate<=write;endwrite_over:state<=idle;default:state<=idle;endcaseendassign rd=~state[2];assign wr=(state==write)?fifowr:1'b1;always@(posedge clk)beginif(~fifowr)in_data_buf<=in_data;end//=============================================== ==============always@(state or fiford or fifowr or fifo_wp or fifo_rp)beginif(state[2]||~fiford)address=fifo_rp;else if(state[3]||~fifowr)elseaddress='bz;end//=============================================== ==================assign out_data=(state[2])?sram_data:8'bz;always@(posedge clk)beginif(state==read)out_data_buf<=sram_data;end//=============================================== ===always@(posedge clk or negedge rst)beginif(!rst)fifo_rp<=0;else if(state==read_over)fifo_rp<=fifo_rp_next;end//=============================================== ====always@(fifo_rp)beginif(fifo_rp==`SRAM_SIZE-1)fifo_rp_next=0;elsefifo_rp_next=fifo_rp+1;end//=============================================== ======always@(posedge clk or negedge rst)beginif(!rst)fifo_wp<=0;else if(state==write_over)fifo_wp<=fifo_wp_next;end//=============================================== ===always@(fifo_wp)beginif(fifo_wp==`SRAM_SIZE-1)elsefifo_wp_next=fifo_wp+1;end//=============================================== ====always@(posedge clk or negedge rst)beginif(!rst)near_empty<=1'b0;else if(fifo_wp==fifo_rp_next)near_empty<=1'b1;elsenear_empty<=1'b0;end//=============================================== ========always@(posedge clk or negedge rst)beginif(!rst)nempty<=1'b0;else if(near_empty&&state==read)nempty<=1'b0;else if(state==write)nempty<=1'b1;end//=============================================== =======always@(posedge clk or negedge rst)beginif(!rst)near_full<=1'b0;else if(fifo_rp==fifo_wp_next)near_full<=1'b1;elsenear_full<=1'b0;end//=============================================== =====always@(posedge clk or negedge rst)beginif(!rst)nfull<=1'b1;else if(near_full&&state==write)nfull<=1'b0;else if(state==read)nfull<=1'b1;end//=============================================== ============endmodule。

Verilog HDL基础知识

tri tri0 tri1 triand trior trireg unsigned vectored wait wand weak0 weak1 while wire wor xnor xor

第3章 Verilog HDL基础知识

3.2 数 据 类 型

Verilog HDL支持两种形式的注释符:/*……*/与//。其中, /*……*/为多行注释符,用于对多行语句注释;//为单行注释符, 只对注释符所在的行有效。下面是一个使用注释符对1位加法器 进行说明的例子。

第3章 Verilog HDL基础知识

【例3-2】注释符的例子。

/* 该例利用一位加法器来说明单行注释符与多行注释符的

第3章 Verilog HDL基础知识

1. 字符串变量的声明 Verilog HDL中采用寄存器变量来存储字符串,寄存器变量的 位数要大于字符串的最大长度。需要注意的是,Verilog HDL中并 不需要特殊位来存储终止符。 【例3-6】字符串变量的声明。

reg [8*12:1] stringvar; initial

'<base_format><number> 符号“'”为基数格式表示的固有字符,该字符不能省略,否 则为非法表示形式;参数<base_format>用于说明数值采用的进制 格式;参数<number>为相应进制格式下的一串数字。这种格式未 指定位宽,其缺省值至少为32位。

第3章 Verilog HDL基础知识

第3章 Verilog HDL基础知识

module addbit (a,b,ci,sum,co);

input

Verilog HDL入门

线网型:wire,tri

wor,trior,wand,triand,trireg,tri1,tri0 supply0,supply1

寄存器型:

reg integer,time real,realtime

wire和tri

用于连接单元的连线是最常见的线网类型。 默认值为z。 wire与tri语法和语义一致; 三态线可以用于描述多个驱动源驱动同一根线 的线网类型;并且没有其他特殊的意义。 通常都用wire。 其他线网型用于底层设计与仿真,FPGA设计通 常不会涉及。

简单的Verilog程序

该程序例子通过另一种方法描述了一个三态 门。 在这个例子中存在着两个模块:模块trist1 在这个例子中存在着两个模块:模块trist1 tri_inst。 调用模块 mytri 的实例元件 tri_inst。 是上层模块。 模块 trist1 是上层模块。模块 mytri 则被 称为子模块。 称为子模块。 通过这种结构性模块构造可构成特大型模块 。

例:always @(b or c) always a=b&c;

元件(实)例化

例:and and1(a,b,c); BUFG BUFG_inst ( .O(out), // Clock buffer output .I(in) // Clock buffer input );

注意

三种方式可以在同一个模块之内混合使用 ; 同一个模块内可以有多个always块,多个 assign和多个元件例化。 所有这些单元是并行执行的。 这些单元的书写顺序不影响逻辑功能;

128状态值集合:包含强度信息

其他值集合

整数(32bits) 实数 字符串 时间(64bits) 布尔值(0,1) ……

提纲

第四章 Verilog基本语法(一)PPT教学课件

2020/12/11

玉溪师范学院

参数

➢ 参数是一个常量。用parameter定义一个标识符来代表 一个常量。参数经常用于定义时延和变量的宽度。

格式: parameter param1 = const_expr1,

param2 = const_expr2,

…,

paramN = const_exprN;

assign #XOR_DELAY S=A^B;

assign #AND_DELAY C=A&B;

endmodule

19

TOP HA

2020/12/11

玉溪师范学院

参数值的模块引用

module TOP3(NewA,NewB,NewS,NewC); input NewA, NewB; output NewS,NewC; HA #(5,2) Ha1 (NewA, NewB, NewS, NewC);ut

selb

26

2020/12/11

玉溪师范学院

reg型

寄存器是数据存储单元的抽象 reg型数据常用来表示always块内的指定信号,常代表触

发器 reg型数据用initial或者always块中指定信号 reg型数据的缺省值是x。可以被赋正值或者负值。当它作

为一个表达式中的操作数时候,作为无符号数。 reg数据类型定义格式为

2.0 ; -0.1等

科学记数法,例如:

235.1e2 等于23510.0

234_12e2

等于2341200.0

实数小数通过四舍五入被隐式地转换为最相近的整数。例如:

42.446, 42.45 转换为整数42

92.5, 92.699 转换为整数93

-5.62 转换为整数-6

SystemVerilog 快速入门

SyestemVerilog的全面验证和设计

进行全面验证的环境 仿真 覆盖 断言 验证 形式化特性 测试平台 抓住设计意图

SystemVerilog

仿真检查 仿真检查

断言 自动测试平台

硬件辅助的验证 提高了验证的水平

硬件辅助验证 硬件辅助验证

与每个设计和 统一的断言扩展了验证方法的效率 验证工程师联 络

SystemVerilog 讲座

第一讲: SystemVerilog 基本知识

夏宇闻 神州龙芯集成电路设计公司 2008

Verilog HDL的发展历史

1984: Gateway Design Automation 推出 Verilog 初版 1989: Gateway 被Cadence Design Systems 公司收购 1990: Cadence 向业界公开 Verilog HDL 标准 1993: OVI 提升 the Verilog 标准,但没有被普遍接受 1995: IEEE 推出 Verilog HDL (IEEE 1364-1995)标准 2001: IEEE 推出 Verilog IEEE Std1364-2001 标准 2002: IEEE 推出 Verilog IEEE Std1364.1-2002 标准 2002: Accellera 对 SystemVerilog 3.0 进行标准化 – Accellera 是OVI & VHDL International (VI)合并后的 国际标准化组织 2003: Accellera 标准化后的SystemVerilog 3.1 2006: IEEE 推出带SystemVerilog 扩展的Verilog新标准

------------------------- SystemVerilog ------------------------------interfaces dynamic processes nested hierarchy 2-state modeling byte unrestricted ports packed arrays implicit port connections array assignments enhanced literals enhanced event control time values & units unique/priority case/if logic-specific processes root name space

语法详细讲解第十四部分Verilog测试模块的编写

语法详细讲解

存储量可变的只读存储器建模

例:

module scalable_ROM (mem_word, address); parameter addr_bits=8; //size of address bus parameter wordsize=8; //width of a word parameter words=(1<<addr_bits); //size of mem output [wordsize:1] mem_word; input [addr_bits:1] address; //word of memory //address bus

激励信号

和用于验

证的结果 数据

需要验证的 设计 复杂的测试平台

语法详细讲解

并行块

在测试块中常用到fork…join块。用并行块能表示以同一个时间起点算起的多个事

件的运行,并行地执行复杂的过程结构,如循环或任务。举例说明如下:

module inline_tb; reg [7:0] data_bus; initial fork data_bus= 8’b00; #10 data_bus = 8’h45;

reg clk; initial begin reg go; wire clk; nand #(period/2) ul (clk,clk,go);

clk=0;

#(period) forever

initial begin

go=0; #(period) go=1;

#(period/2) clk=!clk

时间

80 85

data_bus

8’b0010_0010 8’b0100_0100

90

100 105 110 120 125 140

Verilog语法简易教程

Verilog语法简易教程Verilog是硬件描述语言(HDL)之一,主要用于硬件设计和仿真。

它于1984年由一家名为Gateway Design Automation的公司开发,并于1985年推出。

Verilog以其简单易学的语法和强大的功能而闻名于世。

本简易教程将向您介绍Verilog的基本语法和常用结构。

它包括模块化设计,数据类型,运算符,条件语句,循环语句和时序建模等内容。

首先,让我们先来了解Verilog中的模块化设计。

在Verilog中,设计是通过定义和连接模块来完成的。

每个模块由输入输出端口和内部逻辑组成。

以下是一个简单的Verilog模块的例子:```module adder(input [3:0] A, B, output [3:0] sum);assign sum = A + B;endmodule```上述代码定义了一个名为adder的模块,它具有两个输入端口A和B,以及一个输出端口sum。

内部逻辑通过assign语句实现,将输入端口A和B相加,并将结果赋值给输出端口sum。

接下来,让我们了解Verilog中的数据类型和运算符。

Verilog支持多种数据类型,包括位向量(bit vector)、整数(integer)、浮点数(real)等。

其中,位向量是最常用的数据类型。

以下是两个位向量相加的例子:```module adder(input [3:0] A, B, output [3:0] sum);assign sum = A + B;endmodule```在这个例子中,输入端口A和B都是4位的位向量,输出端口sum也是4位的位向量。

通过使用+运算符,我们可以对这两个位向量进行相加操作,并将结果赋值给输出端口sum。

除了基本的数据类型和运算符,Verilog还提供了丰富的条件和循环语句。

条件语句允许您在程序中根据一些条件执行不同的操作。

以下是一个简单的条件语句的例子:```beginif (A == B)equal = 1;elseequal = 0;endendmodule```在这个例子中,我们使用了always块来定义一个连续的行为。

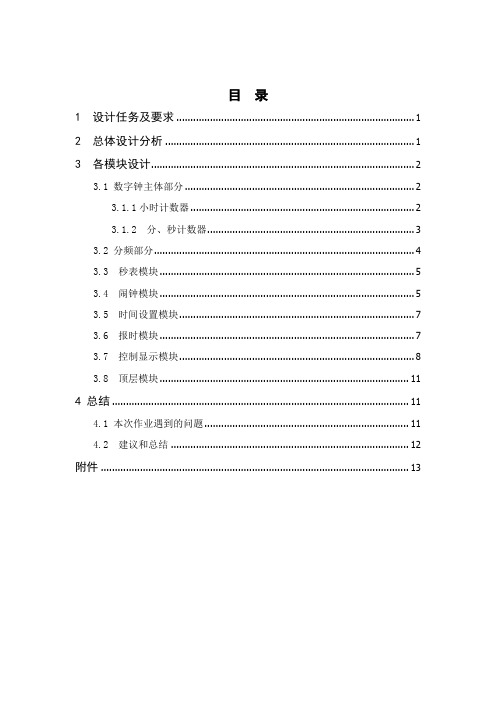

(完整word版)数字钟verilog(word文档良心出品)

目录1 设计任务及要求 (1)2 总体设计分析 (1)3 各模块设计 (2)3.1 数字钟主体部分 (2)3.1.1小时计数器 (2)3.1.2 分、秒计数器 (3)3.2 分频部分 (4)3.3 秒表模块 (5)3.4 闹钟模块 (5)3.5 时间设置模块 (7)3.6 报时模块 (7)3.7 控制显示模块 (8)3.8 顶层模块 (11)4 总结 (11)4.1 本次作业遇到的问题 (11)4.2 建议和总结 (12)附件 (13)1 设计任务及要求本次大作业的要求为设计一个多功能数字钟,其具体要求如下:1.有基础的实时数字钟显示功能,即时、分、秒的正常显示模式,并且在此基础上增加上,下午显示。

2.手动校准。

按动方式键,将电路置于校时状态,则计时电路可用手动方式校准,每按一下校时键,时计数器加1;按动方式键,将电路置于校分状态,以同样方式手动校分。

3.整点报时,仿中央人民广播电台整点报时信号,从59分50秒起每隔2秒发出一次低音“嘟”信号(信号鸣叫持续时间1S,间隙时间1S)连续5次,到达整点(00分00秒时),发一次高音“哒”信号(信号持续时间1S)。

4.闹时功能,按动方式键,使电路工作于预置状态,此时显示器与时钟脱开,而与预置计数器相连,利用前面手动校时,校分方式进行预置,预置后回到正常模式。

当计时计至预置的时间时,扬声器发出闹铃信号,时间为半分钟,闹铃信号可以用开关“止闹”,按下此开关后,闹铃声立刻中止,正常情况下应将此开关释放,否则无闹时作用。

5.秒表功能。

按start键开始计秒,按stop键停止计秒并保持显示数不变,直到复位信号加入。

2 总体设计分析设计的总体部分按照要求可以分为基本的数字时钟显示、手动校准、整点报时、闹钟功能和秒表功能5大部分。

其总体设计框图如下:图1 总体设计框图其中整点报时跟闹钟部分要求不同频率的声响,所以需要加入分频器模块将输入的1kHZ的分频产生500HZ及1HZ的方波信号,其中1HZ的信号对应1S 的周期,可以用作时钟秒的显示及秒表部分。

(完整word版)Verilog-A30分钟快速入门教程.docx

?Verilog-A 30分钟快速入门教程进入正题,学了几天的Verilog-A,平台是Agilent ADS,主要参考“ Verilog- AMS Language Reference Manual”和ADS的帮助文档。

现在的状态算是入门了,写了个简单的PLL。

总结这几天的学习,觉得效率太低,我以前有一定 Verilog 基础,研一时学过一点 VHDL-AMS ,学到现在这个状态应该半天就够了;入门的话, 30 分钟足矣;跟着这个教程走,你会很快了解和熟悉Verilog-A 。

(前提是有一定的 Verilog 基础和电路基础)1、基尔霍夫定律撑起了整个电路学的大厦(当然也可以认为基尔霍夫定律只是麦克斯韦方程的简化版),作为模拟电路描述语言 Verilog-A ,同样将基尔霍夫定律作为其基本,最重要的两个概念便是流量 (Flow) 和位 (Potential) ,在电学里是电流和电压,在力学里可以是力和距离,在热学里可以是功率和温差,等等。

在 Verilog-A中,你可以将电阻电容电感等器件用一个方程式来表述,比如I(out) <+ V(out)/R ,这样就产生了一个电阻,最后 Verilog-A 仿真器会用某种算法( 迭代是最常见的 ) 将 I(out) 和 V(out) 求解出来,然后根据这个解去算下一个时刻的 I 、V 等,当然这仅仅是指时域仿真。

2 、下面讲Verilog-A的语法:begin end //相当于C语言的一对大括号,与Verilog同if ( expression ) true_statement ;[ else false_statement ; ] //与Verilog同case ( expression ) case_item { case_item } endcasefor ( procedural_assignment ; expression;procedural_assignment ) statement//case与for语句都跟Verilog、C语言类似cross( expr [, dir [, time_tol [, expr_tol ]]] );//cross 用来产生一个 event ,如:@(cross(V(sample) -2.0, +1.0))//指 sample 的电压超过 2.0 时触发该事件,将会执行后面的语句, +1.0 表示正向越过, -1.0 则相反ddt( expr )// 求导,如:I(n1,n2) <+ C * ddt(V(n1, n2)); //表示了一个电容idt( expr ,[ ic [, assert [, abstol ]]] ) //积分,如:V(out) <+ gain * idt(V(in) ,0) + gain * V(in);// 比例积分,式中的 0 表示积分的初值transition( expr [, time_delay [, rise_time [, fall_time [, time_tol ]]]] )// 将 expr 的值 delay一下并指定上升下降沿时间,相当于一个传输门laplace_zp( expr ,ζ ,ρ)将 expr 进行拉普拉斯变换,具体表达式参看相关文献,还有laplace_zd()等数据类型:integer 、real ,另外就是 discipline ,不知道怎么翻译比较好,比如说它将电压电流这两个 nature 类型作为一个 discipline ,这些都在 disciplines.vams这个头文件里建好了,编程时要`include "disciplines.vams"。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

•Verilog-A 30分钟快速入门教程

进入正题,学了几天的Verilog-A,平台是Agilent ADS,主要参考“Verilog-AMS Language Reference Manual”和ADS的帮助文档。

现在的状态算是入门了,写了个简单的PLL。

总结这几天的学习,觉得效率太低,我以前有一定Verilog基础,研一时学过一点VHDL-AMS,学到现在这个状态应该半天就够了;入门的话,30分钟足矣;跟着这个教程走,你会很快了解和熟悉Verilog-A。

(前提是有一定的Verilog基础和电路基础)

1、基尔霍夫定律撑起了整个电路学的大厦(当然也可以认为基尔霍夫定律只是麦克斯韦方程的简化版),作为模拟电路描述语言Verilog-A,同样将基尔霍夫定律作为其基本,最重要的两个概念便是流量(Flow)和位(Potential),在电学里是电流和电压,在力学里可以是力和距离,在热学里可以是功率和温差,等等。

在Verilog-A中,你可以将电阻电容电感等器件用一个方程式来表述,比如I(out) <+ V(out)/R,这样就产生了一个电阻,最后Verilog-A仿真器会用某种算法(迭代是最常见的)将I(out)和V(out)求解出来,然后根据这个解去算下一个时刻的I、V等,当然这仅仅是指时域仿真。

2、下面讲Verilog-A的语法:

begin end //相当于C语言的一对大括号,与Verilog同

if ( expression ) true_statement ;

[ else false_statement ; ] //与Verilog同

case ( expression ) case_item { case_item } endcase

for ( procedural_assignment ; expression;

procedural_assignment ) statement

//case与for语句都跟Verilog、C语言类似

cross( expr [, dir [, time_tol [, expr_tol ]]] );

//cross用来产生一个event,如:

@(cross(V(sample) -2.0, +1.0))

//指sample的电压超过2.0时触发该事件,将会执行后面的语句,+1.0表示正向越过,-1.0则相反

ddt( expr ) //求导,如:

I(n1,n2) <+ C * ddt(V(n1, n2)); //表示了一个电容

idt( expr ,[ ic [, assert [, abstol ]]] ) //积分,如:

V(out) <+ gain * idt(V(in) ,0) + gain * V(in);

//比例积分,式中的0表示积分的初值

transition( expr [, time_delay [, rise_time [, fall_time [, time_tol ]]]] ) //将expr的值delay一下并指定上升下降沿时间,相当于一个传输门

laplace_zp( expr ,ζ,ρ)

将expr进行拉普拉斯变换,具体表达式参看相关文献,还有laplace_zd()等数据类型:

integer、real,另外就是discipline,不知道怎么翻译比较好,比如说它将电压电流这两个nature类型作为一个discipline,这些都在disciplines.vams 这个头文件里建好了,编程时要`include "disciplines.vams"。

如果要定义一个电路节点,electrical node_name就好了

parameter {real | integer} list_of_assignments ;

//定义参数,如parameter R = 50 from (0:inf];

在一个模块中调另一个模块和Verilog差不多,如:

blk_a a1(Input1, a_b1);

blk_a a2(Input2, a_b2);

运算符号:

+ - * / > < == & | && || ^ << >> ?: 等,跟Verilog一样

另外,新加的一个符号<+,这个专门给模拟信号赋值用,注意这个赋值符号是可以累加的,就是说赋两次值的话,它会加起来,而不是覆盖,如:

// model input admittance(导纳)

I(in) <+ V(in)/Rin;

I(in) <+ Cin*ddt(V(in));

预处理&宏:

`define `else `ifdef `include `resetall `undef

跟Verilog差不多

3、Verilog-A程序基本结构:

`include "disciplines.vams" //预处理

module load(p); //定义模块,p是端口

electrical p, gnd; //定义节点

ground gnd; //定义gnd为ground节点,电位为0

parameter real R=50.0; //定义R这个参数并赋初值

analog //模拟语句从这开始

V(p) <+ R * I(p, gnd); //在这里表示一个电阻,表示了输出电压与输出电流的关系

endmodule //模块定义结束

4、上面这些基本上是最常用的了,了解之后,你就能看懂一般的Verilog-A程序了,下面是我写的PLL仿真程序,把它看完并看懂(当然第一次并不需要看得很仔细):

提示:振荡频率4~6G,分频器为50分频,Fref为100M,鉴相器为电荷泵型。

`include "disciplines.vams"

`include "constants.vams"

//VCO

module my_vco(in, out);

input in;

output out;

electrical in, out;

parameter real gain=2.0e9, fc=4.0e9;

analog

V(out) <+ sin(2*`M_PI*(fc*$realtime + idt(gain*V(in)))); endmodule

//phase detector

module my_pd(ref,rf,outP,outN);

input ref,rf;

output outP,outN;

electrical ref,rf,outP,outN;

real clr,up,down;

parameter real Ro=1e6, Ro2=1;

analog begin

@(cross(V(ref)-0.5,+1))

up = 1;

@(cross(V(rf)-0.5,+1))

down = 1;

clr = absdelay(up && down, 1e-9);

// clr = transition(up && down, 1e-9); //这两条语句都可以if(clr>0.5) begin

up = 0;

down = 0;

end

if(up) begin

if(V(outP)>= 3)

V(outP) <+ 3-I(outP)*Ro2;

else I(outP) <+ -up*0.01;

end

else begin

I(outP) <+ 0;

end

if(down) begin

if(V(outN) <= 0)

V(outN) <+ 0-I(outN)*Ro2;

else I(outN) <+ down*0.01;

end

else begin

I(outN) <+ 0;

end

end

endmodule

//N divider

module my_divider(in,out);

input in;

output out;

electrical in,out;

integer cnt;

parameter integer K=50;

analog begin

@(cross(V(in),+1))

cnt = cnt+1;

if(cnt>=K)

cnt=0;

if(cnt*2-K>=0)

V(out) <+ 1;

else

V(out) <+ 0;

end

endmodule

以上是VCO、鉴相器和分频器,原理图我是在ADS中画的,如下所示:

以下是仿真结果:

好,看到这儿你已经入门了,想进一步熟悉Verilog-A的话,请参看:。