高速图像采集系统的设计与实现

图像处理系统的设计与实现

图像处理系统的设计与实现一、引言随着科学技术的不断进步,图像处理技术得到了广泛的应用,涵盖了领域众多。

比如医学影像、无人驾驶、智能安防等领域都离不开图像处理技术的支持。

图像处理系统是针对图像信息进行处理和分析的系统,其设计与实现的高效与稳定对应用场景的实现至关重要。

本文将探讨图像处理系统的设计与实现,包括系统架构设计、关键功能模块和算法选择等方面。

二、系统架构设计1.需求分析:在设计图像处理系统之前,首先需要明确系统的应用场景和具体需求。

系统要处理的图像类型、处理的精度要求、处理的速度要求等。

根据不同的需求,系统的架构设计也会有所不同。

2.架构设计:在进行系统架构设计时,可以采用分层架构设计的方式。

通常可以分为应用层、处理层和底层三层架构。

应用层负责用户交互与业务逻辑处理,处理层负责图像处理算法的实现,底层负责图像数据的读取与存储。

3.性能考虑:在进行系统架构设计时,需要充分考虑系统的性能要求。

在处理大规模图像数据时,需要考虑系统的并发能力、响应速度等。

三、关键功能模块1.图像采集模块:图像采集模块是系统的基础模块,负责接收外部输入的图像数据。

通常可以与摄像头、扫描仪等设备进行对接。

2.图像预处理模块:图像预处理模块可以对输入图像进行预处理,包括图像去噪、图像增强、图像分割等操作。

预处理能够提高后续处理的效果。

3.特征提取模块:特征提取模块是系统的核心模块,负责从图像中提取出有价值的特征信息。

可以提取出图像的边缘信息、纹理信息等。

4.图像识别模块:图像识别模块是系统的重要功能模块,负责对图像进行识别和分类。

可以采用机器学习、深度学习等技术实现。

5.结果展示模块:结果展示模块负责将处理后的图像结果展示给用户,可以采用图像显示、图像打印等方式。

四、算法选择1.滤波算法:滤波算法是图像预处理中常用的算法,可以移除图像中的噪声、增强图像的信息等。

常用的滤波算法包括均值滤波、中值滤波、高斯滤波等。

2.特征提取算法:特征提取算法是图像识别中的关键算法,可以从图像中提取出有价值的特征信息。

一种高速实时数据采集系统的设计与实现

(2位 总 线 )2 4M /(4 总 线 )。 3 ,6 Bs6 位 1 2 ] P I 部 总线 一边 与处理 器和 存储 器总线 接 口 C 局

数据后置处理等功能 。用 以完成主机对数据采集前 端 送 出的 1 6位并行数 据 的读取 ,和对传感 器数据 的读

取 、 式的转换 、 送} 格 发 l 】 要 包 括 以下 几 个 功 能 模 块 : 。主 P I 线 控 制 器 、IO缓 存 器 ( 片 C 7 4 7 , 度 C 总 FF 一 Y C 25 深

( olg fMa n E gn eig,Notw sen P ltc nc l nv ri C l e o r e n ie r e i n r etr oye h ia U iest h y,Xia 0 2,Chn ) n 71 7 0 ia

【 btat ei i e o f u r seddt a q it na dt nmi inb sd( C (e p ea C m o et A s c】A ds nn m t do sp = p e aa cus i n r s s o ae m P lP f h rl o pn n r g g h a io a s i

另一边 为外设扩展 提供 高带 宽通道 。这样便将 外设 I / O总线上 移下来 , 不需 C U介 入就可进行数据 传输 P PI C 总线 具有 高性 能 、 使用 方便 、 高协 调性 、 数据 完型

基于USB2.0的高速图像采集实验设计

外公 司的产 品经 常转 产 、 级 换 代 , 至 停 产 , 国 内 升 甚 使

的研制 者受 到制 约 。因此 研制 开发具 有独 立 国外 产 品 的技 术 对 垄 断具 有 重要 的意义 。

与数 据通信 。US 2 0总线 协议 所 支 持 的高 速 模 式 ] B. 传输 速率 为 4 0Mbts 不仅 可 以满 足 目前项 目要 求 , 8 i , /

中 图 分 类 号 : P 9 ; P 3 T 31T 36 文献标志码 : A 文 章 编 号 :1 0 — 9 6 2 1 ) 4 0 1 — 5 0 24 5 ( 0 2 0 — 1 8 0

D s n o ih s edi g c us in e p r n ae nUS 2 0 ei f g -p e g h ma eaq i t x ei t sdo B . io me b

IS S N 1002

. . . . . , . . . . . . . . . . . . . . . . . . . . . . .

-

4 5 9 6

. . . , , , . — —

.

实

验

技

术

与

管

理

第 2 卷 9

第 4期

21 0 2年 4月

CN1 一 2 3 / 】 04T

摘 要 : 速 图像 采 集 技 术 广 泛 应 用 于 图像 信 号 传 输 与 处 理 、 式 识 别 和工 业 控 制领 域 。利 用 F GA 技 术 将 高 模 P

串 行 的 L S和 Hol k格 式 的 图像 信 号 进 行 变 换 和 处 理 , 换 为 标 准 的 1 VD tn i 转 6位 并 行 数 据 , 由 US 再 B接 口 控

嵌入式高速图像采集系统设计

传统的数 字图像处理通 常以 P C机为平台, 但 这 种方 法处理 速 度 较 慢 , 够 灵 活 。随 着 固体 图像 不

传感 器 C D和 C S的 技 术 工 艺不 断 改进 以及 数 C MO

中的最 高性 能 的定 点 D PC 4C U, 有增 强 型 直 S 6x P 具 接 存储 器存 取控 制器 ( D ) 可 以通过 6 E MA , 4个独 立 的通 道 提供 超过 2 y /e Gbt se的 IO带 宽 ; e / 内部包 括 6 4个 3 2位字 长 的通用 寄存 器 以及 8个 独立 的运 算 单元 , 有两 个 专 用 硬 件 乘 法器 。D 6 2还 具 有 3 具 M4

摘 要: 图像数据 的高速 采集在视觉检测 中具有重要意义 , 提出了一种基于 D P C S图像传 感器的嵌 入式高速 图 S 、MO

像处理系统设 计方案。 以高性能数字信号处理器 T S2D 62 为硬件平 台 , 了图像数据的高速获取 。介绍 M 30 M 4 作 实现 了系统 中图像传 感器 、 存储设备 与 D P的硬件接 口设计及系统的软件流程及传感器控 制方式 , 出了利用 网络接 S 并提 口实现图像数据 向上位机传输 的方法 。 关键词 : S ;M S图像采集 ;D A ; D PC O ; S R M 网络传输

图 1 系统设计框

供了每一个像 素 1 0位的色彩分解力 , 具有接 口简 单, 控制功能丰富和信噪比高等的特点。 在本系统中, 选择 T 公 司的 D 62型 D P作 I M4 S

系 统 的 核 心 处 理 器 选 择 , 公 司 的 兀

T S 2 D 4 。D 4 M 3 0 M6 2 M6 2是 基 于 T S 2 C O o系列 M 3O 6o

基于FPGA和USB3.0的高速视频图像采集处理系统设计

摘要随着机器视觉的广泛应用,以及工业4.0和“中国制造2025”的提出,在数字图像的采集、传输、处理等领域也提出了越来越高的要求。

传统的基于ISA接口、PCI接口、串行和并行等接口的图像采集卡已经不能满足人们对于高分辨率、实时性的图像采集的需求了。

一种基于FPGA和USB3.0高速接口,进行实时高速图像采集传输的研究越来越成为国内外在高速图像采集研究领域的一个新的热点。

针对高速传输和实时传输这两点要求,通过采用FPGA作为核心控制芯片与USB3.0高速接口协调工作的架构,实现高帧率、高分辨率、实时性的高速图像的采集和传输,并由上位机进行可视化操作和数据的保存。

整体系统采用先硬件后软件的设计方式进行设计,并对系统各模块进行了测试和仿真验证。

通过在FPGA 内部实现滤波和边缘检测等图像预处理操作,验证了FPGA独特的并行数据处理方式在信号及图像处理方面的巨大优势。

在系统硬件设计部分,采用OV5640传感器作为采集前端,选用Altera的Cyclone IV E系列FPGA作为系统控制芯片,由DDR2存储芯片进行数据缓存,采用Cypress公司的USB3.0集成型USB3.0芯片作为数据高速接口,完成了各模块的电路设计和采集卡PCB实物制作。

系统软件设计,主要分为FPGA逻辑程序部分、USB3.0固件程序部分和上位机应用软件部分。

通过在FPGA上搭建“软核”的方式,由Qsys系统完成OV5640的配置和初始化工作。

由GPIF II接口完成FPGA和FX3之间的数据通路。

通过编写状态机完成Slave FIFO的时序控制,在Eclipse中完成USB3.0固件程序的设计和开发。

上位机采用VS2013软件通过MFC方式设计,从而完成整体图像采集数据通路,并在上位机中显示和保存。

整体设计实现预期要求,各模块功能正常,USB3.0传输速度稳定在320MB/s,通过上位机保存至PC机硬盘的图像分辨率大小为1920*1080,与传感器寄存器设置一致,采集卡图像采集帧率为30fps,滤波及边缘检测预处理符合要求,采集系统具有实际应用价值和研究意义。

高速公路监控系统软件的设计与实现

高速公路监控系统软件的设计与实现一、需求分析高速公路监控系统软件的设计需求主要包括两个方面:一是实时监控高速公路上的交通情况,包括车流量、车速、车辆违章等信息;二是实时监控高速公路上的安全情况,包括交通事故、道路损坏等信息。

根据这些需求,我们需要设计一个具备数据采集、处理和显示功能的软件系统。

二、系统设计1. 数据采集高速公路上的数据主要通过传感器和监控摄像头来采集。

传感器主要用于采集车流量、车速、气象等数据,而监控摄像头用于采集车辆和交通情况的图像数据。

这些采集的数据需要通过网络上传到数据中心进行处理和存储。

2. 数据处理在数据中心,需要对采集到的数据进行处理,包括图像识别、数据分析等工作。

图像识别可以通过计算机视觉技术进行车辆和交通情况的识别,从而得到车辆的数量、车速等信息。

而数据分析可以通过统计和算法分析来得到公路上的安全情况。

3. 数据显示处理好的数据需要通过用户界面进行显示,以便相关人员对高速公路的情况进行监控和管理。

数据显示界面需要清晰直观地展示各项数据指标,并能够实时更新数据信息。

为了方便相关人员进行操作和管理,界面需要具备一定的交互性和可操作性。

三、系统实现高速公路监控系统软件的实现主要包括三个方面:数据采集系统、数据处理系统、数据显示系统。

数据采集系统需要采用传感器技术和监控摄像头技术进行数据采集和传输;数据处理系统需要具备图像识别和数据分析的算法技术;数据显示系统需要具备良好的用户界面设计和数据显示能力。

四、系统优化高速公路监控系统软件的优化主要包括两个方面:系统性能优化、用户体验优化。

系统性能优化需要不断优化数据采集、处理和显示系统的性能,提高系统的响应速度和稳定性。

用户体验优化需要不断改善用户界面的设计,提高用户对系统的使用舒适度和便利性。

1. 系统性能优化在数据采集系统中,可以采用更加先进的传感器和监控摄像头技术,以提高数据的采集速度和准确性。

在数据处理系统中,可以采用更加高效的图像识别算法和数据分析算法,以提高数据处理的速度和精度。

基于FPGA的高速图像采集系统设计.

基于FPGA的高速图像采集系统设计引言在低速的数据采集系统中,往往采用单片机或者DSP进行控制;而对于图像采集这种高速数据采集的场合,这种方案就不能满足需要。

因此这种方案极大浪费了单片机或DSP的端口资源且灵活性差;若改用串口方式收集数据,则一方面降低了数据采集的速度,另一方面极大地耗费CPU的资源。

本系统采用FPGA作为数据采集的主控单元,全部控制逻辑由硬件完成,速度快、成本低、灵活性强。

为了增加缓冲功能,系统在FPGA外扩展了256Mb的RAM,不仅增大了缓冲区容量,而且极大地降低了读写频率,有效地减轻了上位机CPU的负担。

在图像数据接口中,比较常见的是VGA、PCI—Express,而这些接口扩展性差、成本高。

本系统采用高速的USB接口作为与上位机通信的端口,速度快、易安装、灵活性强。

1 系统框图系统框图如图1所示。

FPGA控制单元采用A1tera公司Cyclone II系列的EP2C5F256C6,主要由4个部分组成——主控模块、CMOS传感器接口、RAM 控制器以及EZ—USB接口控制器。

传感器接口负责完成SCCB时序控制,RAM控制器用于实现RAM读写与刷新操作的时序,USB接口模块完成主控模块与EZ—USB之间的数据读写;而主控模块负责对从EZ—USB部分接收过来的上位机命令进行解析,解析完命令后产生相应的信号控制各个对应模块,如CMOS传感器传输的图像格式、RAM的读写方式、突发长度等。

2 OV7620模块设计图像传感器采用OV7620,接口图如图2所示。

该传感器功能强大,提供多种数据格式的输出,自动消除白噪声,白平衡、色彩饱和度、色调控制、窗口大小等均可通过内部的SCCB控制线进行设置。

OV7620属于CMOS彩色图像传感器。

它支持连续和隔行两种扫描方式,VGA与QVGA两种图像格式;最高像素为664×492,帧速率为30fps;数据格式包括YUV、YCrCb、RGB三种。

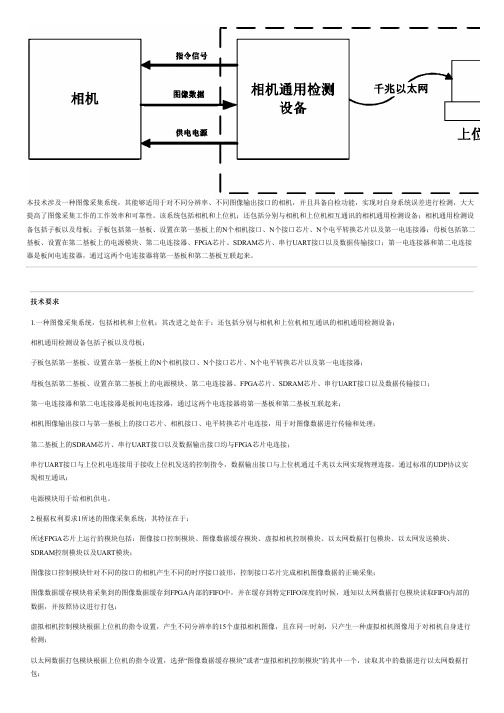

图像采集系统的制作方法

本技术涉及一种图像采集系统,其能够适用于对不同分辨率、不同图像输出接口的相机,并且具备自检功能,实现对自身系统误差进行检测,大大提高了图像采集工作的工作效率和可靠性。

该系统包括相机和上位机;还包括分别与相机和上位机相互通讯的相机通用检测设备;相机通用检测设备包括子板以及母板;子板包括第一基板、设置在第一基板上的N个相机接口、N个接口芯片、N个电平转换芯片以及第一电连接器;母板包括第二基板、设置在第二基板上的电源模块、第二电连接器、FPGA芯片、SDRAM芯片、串行UART接口以及数据传输接口;第一电连接器和第二电连接器是板间电连接器,通过这两个电连接器将第一基板和第二基板互联起来。

技术要求1.一种图像采集系统,包括相机和上位机;其改进之处在于:还包括分别与相机和上位机相互通讯的相机通用检测设备;相机通用检测设备包括子板以及母板;子板包括第一基板、设置在第一基板上的N个相机接口、N个接口芯片、N个电平转换芯片以及第一电连接器;母板包括第二基板、设置在第二基板上的电源模块、第二电连接器、FPGA芯片、SDRAM芯片、串行UART接口以及数据传输接口;第一电连接器和第二电连接器是板间电连接器,通过这两个电连接器将第一基板和第二基板互联起来;相机图像输出接口与第一基板上的接口芯片、相机接口、电平转换芯片电连接,用于对图像数据进行传输和处理;第二基板上的SDRAM芯片、串行UART接口以及数据输出接口均与FPGA芯片电连接;串行UART接口与上位机电连接用于接收上位机发送的控制指令,数据输出接口与上位机通过千兆以太网实现物理连接,通过标准的UDP协议实现相互通讯;电源模块用于给相机供电。

2.根据权利要求1所述的图像采集系统,其特征在于:所述FPGA芯片上运行的模块包括:图像接口控制模块、图像数据缓存模块、虚拟相机控制模块、以太网数据打包模块、以太网发送模块、SDRAM控制模块以及UART模块;图像接口控制模块针对不同的接口的相机产生不同的时序接口波形,控制接口芯片完成相机图像数据的正确采集;图像数据缓存模块将采集到的图像数据缓存到FPGA内部的FIFO中,并在缓存到特定FIFO深度的时候,通知以太网数据打包模块读取FIFO内部的数据,并按照协议进行打包;虚拟相机控制模块根据上位机的指令设置,产生不同分辨率的15个虚拟相机图像,且在同一时刻,只产生一种虚拟相机图像用于对相机自身进行检测;以太网数据打包模块根据上位机的指令设置,选择“图像数据缓存模块”或者“虚拟相机控制模块”的其中一个,读取其中的数据进行以太网数据打包;以太网发送模块依据千兆以太网接口的RGMII接口时序,将打包后的数据,通过RGMII接口发送出去;SDRAM控制模块在FPGA内部的FIFO有限的情况下,将部分要缓存的数据缓存到SDRAM芯片中;UART模块用于实现与上位机或者其他UART接口之间的数据通讯,实时回报相机通用检测设备的工作状态。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

a lc t nsi r po e sd n pp iai ,s p o s d ba e o ARM r e s r n e b dd d n x y tm shih-p e i e m a e a q iiin y t m o p oc s o s a d m e e Li u s se , g s e d v d o i g c u sto s se h r wa e ac ie t r nd s fwa ed sg olto ,n v st y outo o t e p o e Ex e i e t lr s lss o t a he a d r r ht cu e a o t r e i n s u insa d gie heke s l i n t h r blm. p rm n a e u t h w tt h

a plc t n r q ie e s p i ai e ur m nt. o

Ke w o d : y r s CCD; PGA ; a ea q iiin; F I g c u sto Embe d dln x m d e iu

硬件 电路 设 计 本 设计 的硬件系 统 由嵌 入式 AM处理器 、 C R CD图像传 感器 、 / AD 转 换器 、FG PA电路 、JE PG编码器等 组成 ,其 中, C C D图像 传感器 将 光 信号转 换为 模拟 电子信号 ,传送给 AD转换器 ,AD转换器将 模 / / 拟 电子信 号转换 为 By r数字信 号 ,传送 给 FG ,F G ae PA P A将 By r a e 数 字信号 转换 为 Y V 号 , U信 传送 给 3 E 编码 器 , 由 AM控制 J E PG 再 R PG 编 码器生 成 J E P G图像 ,通过 网络传送 给 P C机保存 或显示 。 对 各 部分 电路 的详 细介 绍 如下 : ( )C D 控 制 电路 。C D 控 制 电路 采 用 索尼 公 司 生产 的 一 C C IX0 ,其主 要作 用是 将像 素 的光信 号转 换 为 电信 号 C25 IX0 是 ~款 12英 寸、有 效 像素 为 15 的 cD传感 器 , C25 / 4万 c 每 秒 可 输 出 图 像 7 5 帧 。 其 关 键 参 数 如 下 : 水 平 驱 动 频 率 . 1. 1M z 4 3 8H ,感光 区尺 寸 0 5英寸 ,有 效 像素 19 .0 0 . 32 14 ,可 满足 大 多数 应用 的 需求 。 ( ) / 转 换电路 。 / 转换 电路 的主 要功能是 将 CD - AD AD C 传感 器 输 出的模拟信 号转换 为数字信号 。本设计选用 Aa o e ie公司 n lgDv c 生产 的 A 92A作为 AD 换电路 , D93 /转 它具 有 1 位 3M z / 转换器 , 2 6H D A 内含 6 4 d 可变增 益放大器 ,是针对 数字 图像采 集设备 的前端设 -2B 备 。AM微 处理器 通过 串行接 口控制 AD转换 电路将 C D电路输 出 R / C 的模 拟信号转 换为数字 B yr 号,并将其输 送到 FG ae 信 PA电路 。 ( )F G 控 制 电路 。F G 三 PA PA控制 电路 的主 要功 能是 将 B yr ae 信 号转 换 为 RB信 号 再将 RB 号 转换 生成 YV视频 信 号 。 G G信 U ( ) P G 码 电路 。 P G 码 电路 的主 要功 能是 对输 入 的 四 JE 编 JE 编 Yv视频 信 号进 行编 码 , U 生成 常用 的 J E P G图像本 设计 选用 的 JE PG 编 码 芯 片 是 T yo lcr n e ie L m td 公 司 生 产 的 ok Ee to Dv c i ie T 3 1RF E 30 P (以 下 简 称 T 3 1)芯 片 。 T 3 1 是 基 于 E 30 E3 0 I O IC0 1— C eu n il 方式 的 3 E 编码 芯 片 ,可对 S/ E 198 1D T sq et a PG 6 04 0V A4 :2 的 图像进 行最 大 15p 4x 8 (G/ :2 ) 3 fs的高速 压缩 。 ( )A 控制 电路 。 R 整 个系 统 的中心控 制 部件 ,负 责 五 M R AM是 控 制 C D电路 的输 出 、/ 换 电路 的输 入 输 出, 制 F G U AD转 控 P A将 Y V U 信 号输 送 给 J E P G编码 芯片 , 并将 JE PG编码 芯 片输 出 的 JE PG图像 数 据通 过 网络 传送 给 P 机达 到 显示和 保 存 的 目的 。本 设计 选 用 c

s at c v d e o r i t r u t i t i q v i * e — d t i oi nc de n e r p (n r , o d d v i ,

—

s ru t t t c p

—

rg *e s e sr g)

A m l 司生 产 的 A9 R 90 te 公 T 1M 20微控 制器 。 二 、驱 动程 序设 计 与实 现 ( )驱动 程序 的 各模块 的功 能。在 L nx操 作系 统下 ,设 一 iu 备 驱动 程序 是 系统 内核 与机 器硬 件 之 间的接 口,它 为应 用程 序屏

计 算机 光盘 软件 与 应用

2 1 年第 2 期 01 3

Cm u e DS f w r n p lc t o s o p trC o ta ea dA p i a i n 软 件 设 计 开 发

高速图像采集系统的设计与实现

何 宇矗

( 四川大学,成都

606 ) 1 04

摘 要 : 图像 采 集及传 输技 术在 公共 安 全 、工业 控制 、科 学研 究等 领域 得 到 了广泛 的应 用 ,这 些应 用对 系统 的采 集 、 传 输速 度提 出 了越 来越 高 的要 求。针 对这 些应 用 ,提 出了一种基 于 A I RN 处理 器 和嵌入 式 Ln x系统的 高速视 频 图像 采 集 iu 系统 的硬件 结 构及软 件设 计 方案 , 给 出 了关键 问题 的解 决方 法 。实验 结果表 明 , 设计 方案 能够 以每 秒 1 并 该 O帧的 速率 采 集 并传输 图像 ,且 生成 的图像 质量 较好 ,能 够 满足 大 多数 应 用的要 求。

{

rgw ie IAK 00 0) e r t (M S , x 0 f t s l t s h d l ( e c d r t s l t a ke c eu e& no e— ak e)

HeYu h cu

( i u nU i ri ,h n d 6 0 4Ch a Sc a n es yC e g u 1 6 , i ) h v t 0 n

Absr c :m a ea q st nd ta m iso e h lgy i ubi aft, u tilc n r l ce i cr s ac n t e e ̄ t a tI g c uiii a rns s in tc noo n p lcs eyi sra o to, int e e rh a d o h rf l on nd s i f i h v e n ie y u e ,h s pp iainso e s se ' olc in, a s ison s e d i h ra i e- e ie n sFo e e a e b e w d l s dt e e a lc to n t y tm sc le to t n m s i p e sh g e nd hgh lr qur me t h r rt s h

关键 词 :C D;F G C P A; 图像 采 集 ;嵌 入 式 l u i x n

中图分类号:T 3 1 2 P 1. 5

文献标识码 :A 文章编号:10 — 59( 0 1 3 09— 2 07 99 2 1 )2— 13 0

Hi h s e d I a eAc u st n S se De i n a d I p e n a i n g - p e m g q ii o y t m sg n m lme t to i

—

sr t t uc fi e op ra on t c e o s l e ti s e od r p =

— — — —

{

.

o ne = T S OD L w r HI M U E,

o n = e c e O e ’ pe n Od r p n

—

.

.

r e e = e od r re ea e, el as nc e l s

d s a a t r 0 f me e e o d a d订a se ae o e i g .n er s l n ma e q ai e e b et e s e i c n c pu e 1 a sp rs c n n n g l n frr t f h ma e dt u t g i g u l y i b R ra l o me t t a h e i t s mo t

一

、

蔽 了具 体硬 件 的细节 ,使 应用 程 序可 以像 操作 普通 磁盘 文 件一 样 操作 硬件 设 备 。 系 统 中的驱 动程 序用 于控 制 F G PA模 块及 JE PG编 码器 模 块 , 主要 完成 以下六 项工 作 : 始化 T 3 1 控 制 寄存器 ;申请 内存 空 初 E 30 间暂 存 J E P G数据 ;实现异 步通 知机 制 便于 与应 用层 进行 通信 ; 响 应应 用层 发 出的控 制 T 31 启停 及设 置工 作方 式 的命 令 ; 实现 E 30 m a 函数 把 内核 空 间 映射 到 用户 空 间便 于 大量 数 据 在 内 核和 应 mp 用层 之 间的传 送 ; 申请 中断并 实现 中 断处理 程序 ,用 于 通 知应 用 层保 存 图像数 据 。 ( ) f l o ea in 二 i e p rt o s结构 的 实现 。其 f l— p rt os ie oe a in 结构 的成 员如 下 :