MSP430单片机经典资料

MSP430_单片机_资料

MSP430_单片机_资料MSP430_单片机_资料Ulrt-lao wowep drsien wigthTexas nsItumertn s超功低微耗控制器超低功耗控微器制SM4P0Augus3t 0 0/1MSP430_单片机_资料ltUra-lwo pwored signe withMSP340发展历程性能Flsh aFalhs1.-836. VL CDD riev r. 1….-3.6 8V Bsica lCoc Tiker_A meNwROM/OPT.525 -VL DC DrvireFL TiLmrePor/ tBasc Tiierm8- bi tT/ C33xxCD120L Tmeri_ ASAUTR MPFY14xTiermB _DAC2 21US RT MPAYC mo_Ap4F4NewxF13Tixmr_Be DCA1 2UASTRC op_AmF42x3x2xCDL48 ADC41X1xUSART24F1x3x1xLCD921x1x1Cop_AF40xm***-*****20XX年20XX年0202Agustu0 0 /2UlMSP430_单片机_资料ratl-wop wor eedisgn itwhSM4P3:全新的0微制控R器N THE *****NH ,NT TOH EMIEL. ITs’ lFah MsS430 MPU redCuces pwoer cnsuompton driatiscally s, youo rabtteire surn lnogr.eMS430P的效极能.高/IO和PC U运是行用能同的不时钟PC 功U 的耗关通过开状寄态器存控的位实现制MSP430 的耗功极低. 行执时为601A u@ .81 V(Fasl)h 备用时为0.1u A(Fl sh)a MPS403极地延长大电了池寿命电SM4P0 有3业级工16 itb RISCM CU. -40 8-5 C M SP34 0编程方便,发开工具廉价DA MED1M,EMM ;2EMM=2*****+E2hTeMSP 304 runswith aatcwhcr staylat p tou4MH zitenrnalclck!ouAugst 00 /3MSP430_单片机_资料lUra-ltw powero dsiegnw ith*****Fxx :LASH F列特性系New灵活样多外的围模块RUNTH ***** N,O ONT HTEM IL.ET ’Is lash*****MCU red cuesp wore conumptions drsticaaly, so ylou rabtetiesrrun l ongre. 12b-t iAD /8( +4 通道, 转换1 0s) 61-ib timTe_r wAthi C3C /寄器存1-6bt iTime_B wirth 7/C C存器寄1 2 个-SURA接口T 件硬法器乘模拟号信比较器基本时模钟块- 由可程内部电阻控编频制率-由单一部电外控制阻率频-2 3kHz 振产晶生低频- 高晶振频产高生频可选择外部-时钟源超低功耗1.8V . ..3 6.V 供电电压范2围00 A@ 1MH,z 2.2V,活动模式0.7 A 备用模式0. 1A 保持R AM 据数 6 s备从模式唤醒用强大C的U 内P核16Bit R-IC S构结251n 指令s期周@ MHz8Auugs t00/4UMSP430_单片机_资料lrt-alw oopewr edign swtihSP4M0 系3列注1 - :可C由mopaatorrA_实现2 -可由Ti mr/Poert实现3 -有562 FLASBH 和oot BRM O 4 I-punt/utpuOt+ Otpuu外t模围块: TIMRSE: WT Db8tiT B1T _A T_BT- aWchtdgo 定时器- 8位定器时/计器数-Baic siTemr 1- Tmie_r A(x )捕/捉比较寄存器T-ime_r (Bx 捕)捉比/较寄存器URAT 件实软,或现用通同步异/接口步数MPY硬乘法器I/O件数字I/O ,O及tuputAgusut 00/ 5MSP430_单片机_资料Ulrt-aowlp wore dsegin witMhSP403F LSAH 列系NweFie vnew lFas hcofinurgtiaon avsilaable now!号型LASH 1 FB 4 KB 8 KB 1K6KB 32 B K8 K4 B60KBA/ DlSpeo loSe p2-b1t 12i-itb 12-bti1 2b-it12 bit-Tmire sA3A3 A 3 +B 33 A +3 A3B +B7 A + B3 A7 +3B 7SUART 1 12 2M2P Yvv v/IO 4 114 8 448 8 4484 8FALH 型S超低功耗Falsh 内核10,000 次写/0周期擦程存储器序段:51分2 信B存储息分器:128B段可以分擦段除或整擦除体编和擦程除电由压内产生部有代读出码护保*****101 *****1F211MS P34F031 M3FS*****FMSP 40F317 4SPM*****F *****F94Augst 00 u/6MSP430_单片机_资料低功耗的超现实:速起动和快电省模式其他MCUIUltarlo- powewrd esig nithw* / 4b8tiC UP* 电流耗大消* 唤醒慢Ic c /A45 400 ***-*****IvAgr300 5022 00tVc c=3 V1 se ccylcetime**********ctAvei odMe PML0*****LLPMIAvrg3 t例L:P3, M备模式用(*****C1) 3276xHz 振8荡活动器基。

MSP430资料

D Wake-Up From Standby Mode in 6 µs D 16-Bit RISC Architecture,125-ns Instruction Cycle Time D 12-Bit A/D Converter With InternalReference, Sample-and-Hold and Autoscan FeatureD 16-Bit Timer_B With SevenCapture/Compare-With-Shadow Registers D 16-Bit Timer_A With Three Capture/Compare Registers D On-Chip ComparatorDSerial Onboard Programming,No External Programming Voltage Needed Programmable Code Protection by Security FuseDevicesDFamily Members Include:– MSP430F133:8KB+256B Flash Memory,256B RAM– MSP430F135:16KB+256B Flash Memory,512B RAM– MSP430F147:32KB+256B Flash Memory,1KB RAM– MSP430F148:48KB+256B Flash Memory,2KB RAM– MSP430F149:60KB+256B Flash Memory,2KB RAMD Available in 64-Pin Quad Flat Pack (QFP)DFor Complete Module Descriptions, See the MSP430x1xx Family User’s Guide ,Literature Number SLAU049descriptionThe Texas Instruments MSP430 family of ultralow-power microcontrollers consist of several devices featuring different sets of peripherals targeted for various applications. The architecture, combined with five low power modes is optimized to achieve extended battery life in portable measurement applications. The device features a powerful 16-bit RISC CPU, 16-bit registers, and constant generators that attribute to maximum code efficiency.The digitally controlled oscillator (DCO) allows wake-up from low-power modes to active mode in less than 6µs.The MSP430x13x and the MSP430x14x series are microcontroller configurations with two built-in 16-bit timers,a fast 12-bit A/D converter, one or two universal serial synchronous/asynchronous communication interfaces (USART), and 48 I/O pins.Typical applications include sensor systems that capture analog signals, convert them to digital values, and process and transmit the data to a host system. The timers make the configurations ideal for industrial control applications such as ripple counters, digital motor control, EE-meters, hand-held meters, etc. The hardware multiplier enhances the performance and offers a broad code and hardware-compatible family solution.Copyright 2000 – 2003, Texas Instruments IncorporatedPRODUCTION DATA information is current as of publication date.Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.pin designation, MSP430F133, MSP430F135171819P5.4/MCLK P5.3P5.2P5.1P5.0P4.7/TBCLK P4.6P4.5P4.4P4.3P4.2/TB2P4.1/TB1P4.0/TB0P3.7P3.6P3.5/URXD0484746454443424140393837363534332012345678910111213141516DV CC P6.3/A3P6.4/A4P6.5/A5P6.6/A6P6.7/A7V REF+XINXOUT/TCLKVe REF+V REF –/Ve REF –P1.0/TACLK P1.1/TA0P1.2/TA1P1.3/TA2P1.4/SMCLK21222324P 5.6/A C L K T D O /T D I 63626160596458A V P 6.2/A 2P 6.1/A 1P 6.0/A 0R S T /N M I T C K T M S P 2.6/A D C 12C L K P 2.7/T A 0P 3.0/S T E 0P 3.1/S I M O 0P 1.7/T A 2P 2.1/T A I N C L K P 2.2/C A O U T /T A 0P 2.3/C A 0/T A 1P 2.4/C A 1/T A 2P 2.5/R o s c 5655545725262728295352P 1.5/T A 0X T 2I N X T 2O U T 515049303132P 3.2/S O M I 0P 3.3/U C L K 0P 3.4/U T X D 0P 5.7/T B o u t HT D I P 5.5/S M C L KA V D V PM PACKAGE (TOP VIEW)P 1.6/T A 1P 2.0/A C L K C CS SS Spin designation, MSP430F147, MSP430F148, MSP430F149171819P5.4/MCLK P5.3/UCLK1P5.2/SOMI1P5.1/SIMO1P5.0/STE1P4.7/TBCLK P4.6/TB6P4.5/TB5P4.4/TB4P4.3/TB3P4.2/TB2P4.1/TB1P4.0/TB0P3.7/URXD1P3.6/UTXD1P3.5/URXD0484746454443424140393837363534332012345678910111213141516DV CC P6.3/A3P6.4/A4P6.5/A5P6.6/A6P6.7/A7V REF+XINXOUT/TCLKVe REF+V REF –/Ve REF –P1.0/TACLK P1.1/TA0P1.2/TA1P1.3/TA2P1.4/SMCLK21222324P 5.6/A C L K T D O /T D I 63626160596458A V P 6.2/A 2P 6.1/A 1P 6.0/A 0R S T /N M I T C K T M S P 2.6/A D C 12C L K P 2.7/T A 0P 3.0/S T E 0P 3.1/S I M O 0P 1.7/T A 2P 2.1/T A I N C L K P 2.2/C A O U T /T A 0P 2.3/C A 0/T A 1P 2.4/C A 1/T A 2P 2.5/R o s c 5655545725262728295352P 1.5/T A 0X T 2I N X T 2O U T 515049303132P 3.2/S O M I 0P 3.3/U C L K 0P 3.4/U T X D 0P 5.7/T B o u t HT D I P 5.5/S M C L KA V D V PM PACKAGE (TOP VIEW)P 1.6/T A 1P 2.0/A C L K C CS SS Sfunctional block diagrams MSP430x13xRoscXT2INXT2OUTTMSTCKTDITDO/TDIMSP430x14xRoscXT2INXT2OUTTMSTCKTDITDO/TDITerminal FunctionsTerminal Functions (Continued)General-Purpose Register Program Counter Stack Pointer Status Register Constant Generator General-Purpose Register General-Purpose Register General-Purpose Register PC/R0SP/R1SR/CG1/R2CG2/R3R4R5R12R13General-Purpose Register General-Purpose Register R6R7General-Purpose Register General-Purpose Register R8R9General-Purpose Register General-Purpose Register R10R11General-Purpose Register General-Purpose RegisterR14R15short-form descriptionCPUThe MSP430 CPU has a 16-bit RISC architecture that is highly transparent to the application. All operations, other than program-flow instructions,are performed as register operations in conjunc-tion with seven addressing modes for source operand and four addressing modes for destina-tion operand.The CPU is integrated with 16 registers that provide reduced instruction execution time. The register-to-register operation execution time is one cycle of the CPU clock.Four of the registers, R0 to R3, are dedicated as program counter, stack pointer, status register,and constant generator respectively. The remain-ing registers are general-purpose registers.Peripherals are connected to the CPU using data,address, and control buses, and can be handled with all instructions.instruction setThe instruction set consists of 51 instructions with three formats and seven address modes. Each instruction can operate on word and byte data.Table 1 shows examples of the three types of instruction formats; the address modes are listed in Table 2.Table 1. Instruction Word FormatsTable 2. Address Mode Descriptionsoperating modesThe MSP430 has one active mode and five software selectable low-power modes of operation. An interrupt event can wake up the device from any of the five low-power modes, service the request and restore back to the low-power mode on return from the interrupt program.The following six operating modes can be configured by software:D Active mode AM;–All clocks are activeD Low-power mode 0 (LPM0);–CPU is disabledACLK and SMCLK remain active. MCLK is disabledD Low-power mode 1 (LPM1);–CPU is disabledACLK and SMCLK remain active. MCLK is disabledDCO’s dc-generator is disabled if DCO not used in active modeD Low-power mode 2 (LPM2);–CPU is disabledMCLK and SMCLK are disabledDCO’s dc-generator remains enabledACLK remains activeD Low-power mode 3 (LPM3);–CPU is disabledMCLK and SMCLK are disabledDCO’s dc-generator is disabledACLK remains activeD Low-power mode 4 (LPM4);–CPU is disabledACLK is disabledMCLK and SMCLK are disabledDCO’s dc-generator is disabledCrystal oscillator is stoppedinterrupt vector addressesThe interrupt vectors and the power-up starting address are located in the address range 0FFFFh – 0FFE0h.The vector contains the 16-bit address of the appropriate interrupt-handler instruction sequence.2.Interrupt flags are located in the module.3.Nonmaskable: neither the individual nor the general interrupt-enable bit will disable an interrupt event.4.(Non)maskable: the individual interrupt-enable bit can disable an interrupt event, but the general-interrupt enable can not disableit.5.Timer_B7 in MSP430x14x family has 7 CCRs; Timer_B3 in MSP430x13x family has 3 CCRs. In Timer_B3 there are only interruptflags TBCCR0, 1, and 2 CCIFGs and the interrupt-enable bits TBCCTL0, 1, and 2 CCIEs.special function registersMost interrupt and module-enable bits are collected in the lowest address space. Special-function register bits not allocated to a functional purpose are not physically present in the device. This arrangement provides simple software access.interrupt enable 1 and 2Address 0hWDTIE:Watchdog-timer interrupt enable. Inactive if watchdog mode is selected. Active if watchdog timer is configured in interval timer mode.OFIE:Oscillator-fault-interrupt enable NMIIE:Nonmaskable-interrupt enable ACCVIE:Flash access violation interrupt enableURXIE0:USART0, UART, and SPI receive-interrupt enable UTXIE0:USART0, UART, and SPI transmit-interrupt enablerw-0rw-0Address 01hURXIE1:USART1, UART, and SPI receive-interrupt enable UTXIE1:USART1, UART, and SPI transmit-interrupt enableinterrupt flag register 1 and 2Address 02hWDTIFG:Set on watchdog timer overflow (in watchdog mode) or security key violation. Reset on V CC OFIFG:Flag set on oscillator fault NMIIFG:Set via RST/NMI pinURXIFG0:USART0, UART, and SPI receive flag UTXIFG0:USART0, UART, and SPI transmit flagrw-1rw-0Address 03hURXIFG1:USART1, UART, and SPI receive flag UTXIFG1:USART1, UART, and SPI transmit flagmodule enable registers 1 and 2rw-0rw-0Address 04hURXE0:USART0, UART receive enable UTXE0:USART0, UART transmit enableUSPIE0:USART0, SPI (synchronous peripheral interface) transmit and receive enablerw-0rw-0Address 05hURXE1:USART1, UART receive enable UTXE1:USART1, UART transmit enableUSPIE1:USART1, SPI (synchronous peripheral interface) transmit and receive enableLegend: rw:Bit Can Be Read and WrittenBit Can Be Read and Written. It Is Reset by PUC.SFR Bit Not Present in Devicememory organizationbootstrap loader (BSL)The MSP430 bootstrap loader (BSL) enables users to program the flash memory or RAM using a UART serial interface. Access to the MSP430 memory via the BSL is protected by user-defined password. For complete description of the features of the BSL and its implementation, see the Application report Features of the MSP430Bootstrap Loader , Literature Number SLAA089.flash memoryThe flash memory can be programmed via the JTAG port, the bootstrap loader, or in-system by the CPU. The CPU can perform single-byte and single-word writes to the flash memory. Features of the flash memory include:D Flash memory has n segments of main memory and two segments of information memory (A and B) of 128bytes each. Each segment in main memory is 512 bytes in size.D Segments 0 to n may be erased in one step, or each segment may be individually erased.D Segments A and B can be erased individually, or as a group with segments 0–n.Segments A and B are also called information memory.D New devices may have some bytes programmed in the information memory (needed for test duringmanufacturing). The user should perform an erase of the information memory prior to the first use.Main MemoryInformation Memory8 kB 0FFFFh 0FE00h 0FDFFh 0FC00h 0FBFFh 0FA00h 0F9FFh16 kB 0FFFFh 0FE00h 0FDFFh 0FC00h 0FBFFh 0FA00h 0F9FFh32 kB 0FFFFh 0FE00h 0FDFFh 0FC00h 0FBFFh 0FA00h 0F9FFh48 kB 0FFFFh 0FE00h 0FDFFh 0FC00h 0FBFFh 0FA00h 0F9FFh60 kB 0FFFFh 0FE00h 0FDFFh 0FC00h 0FBFFh 0FA00h 0F9FFh0E400h 0E3FFh 0E200h 0E1FFh 0E000h 010FFh 01080h 0107Fh 01000h0C400h 0C3FFh 0C200h 0C1FFh 0C000h 010FFh 01080h 0107Fh 01000h08400h 083FFh 08200h 081FFh 08000h 010FFh 01080h 0107Fh 01000h04400h 043FFh 04200h 041FFh 04000h 010FFh 01080h 0107Fh 01000h01400h 013FFh01200h 011FFh01100h 010FFh01080h 0107Fh01000hperipheralsPeripherals are connected to the CPU through data, address, and control busses and can be handled using all instructions.digital I/OThere are six 8-bit I/O ports implemented—ports P1 through P6:D All individual I/O bits are independently programmable.D Any combination of input, output, and interrupt conditions is possible.D Edge-selectable interrupt input capability for all the eight bits of ports P1 and P2.D Read/write access to port-control registers is supported by all instructions.oscillator and system clockThe clock system in the MSP430x13x and MSP43x14x family of devices is supported by the basic clock module that includes support for a 32768-Hz watch crystal oscillator, an internal digitally-controlled oscillator (DCO) anda high frequency crystal oscillator. The basic clock module is designed to meet the requirements of both lowsystem cost and low-power consumption. The internal DCO provides a fast turn-on clock source and stabilizes in less than 6 µs. The basic clock module provides the following clock signals:D Auxiliary clock (ACLK), sourced from a 32768-Hz watch crystal or a high frequency crystal.D Main clock (MCLK), the system clock used by the CPU.D Sub-Main clock (SMCLK), the sub-system clock used by the peripheral modules.watchdog timerThe primary function of the watchdog timer (WDT) module is to perform a controlled system restart after a software problem occurs. If the selected time interval expires, a system reset is generated. If the watchdog function is not needed in an application, the module can be configured as an interval timer and can generate interrupts at selected time intervals.multiplication (MSP430x14x Only)The multiplication operation is supported by a dedicated peripheral module. The module performs 1616, 168, 816, and 88 bit operations. The module is capable of supporting signed and unsigned multiplication as well as signed and unsigned multiply and accumulate operations. The result of an operation can be accessed immediately after the operands have been loaded into the peripheral registers. No additional clock cycles are required.USART0The MSP430x13x and the MSP430x14x have one hardware universal synchronous/asynchronous receive transmit (USART0) peripheral module that is used for serial data communication. The USART supports synchronous SPI (3 or 4 pin) and asynchronous UART communication protocols, using double-buffered transmit and receive channels.USART1 (MSP430x14x Only)The MSP430x14x has a second hardware universal synchronous/asynchronous receive transmit (USART1) peripheral module that is used for serial data communication. The USART supports synchronous SPI (3 or 4 pin) and asynchronous UART communication protocols, using double-buffered transmit and receive channels.Operation of USART1 is identical to USART0.timer_A3Timer_A3 is a 16-bit timer/counter with three capture/compare registers. Timer_A3 can support multiple capture/compares, PWM outputs, and interval timing. Timer_A3 also has extensive interrupt capabilities.Interrupts may be generated from the counter on overflow conditions and from each of the capture/compare registers.timer_B7 (MSP430x14x Only)Timer_B7 is a 16-bit timer/counter with seven capture/compare registers. Timer_B7 can support multiple capture/compares, PWM outputs, and interval timing. Timer_B7 also has extensive interrupt capabilities.Interrupts may be generated from the counter on overflow conditions and from each of the capture/compare registers.timer_B3 (MSP430x13x Only)Timer_B3 is a 16-bit timer/counter with three capture/compare registers. Timer_B3 can support multiple capture/compares, PWM outputs, and interval timing. Timer_B3 also has extensive interrupt capabilities.Interrupts may be generated from the counter on overflow conditions and from each of the capture/compare registers.comparator_AThe primary function of the comparator_A module is to support precision slope analog–to–digital conversions, battery–voltage supervision, and monitoring of external analog signals.ADC12The ADC12 module supports fast, 12-bit analog-to-digital conversions. The module implements a 12-bit SAR core, sample select control, reference generator and a 16 word conversion-and-control buffer. The conversion-and-control buffer allows up to 16 independent ADC samples to be converted and stored without any CPU intervention.peripheral file mapperipheral file map (continued)peripheral file map (continued)peripheral file map (continued)absolute maximum ratings over operating free-air temperature (unless otherwise noted)†. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Voltage applied at V CC to V SS–0.3 V to + 4.1 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Voltage applied to any pin (referenced to V SS) –0.3 V to V CC+0.3 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Diode current at any device terminal . ±2 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Storage temperature (unprogrammed device) –55°C to 150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Storage temperature (programmed device) –40°C to 85°C †Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.NOTE:All voltages referenced to V SS.recommended operating conditionsNOTES: 1.In LF mode, the LFXT1 oscillator requires a watch crystal and the LFXT1 oscillator requires a 5.1-M Ω resistor from XOUT to V SS when V CC <2.5 V. In XT1 mode, the LFXT1. and XT2 oscillators accept a ceramic resonator or a 4-MHz crystal frequency at V CC ≥ 2.2 V. In XT1 mode, the LFXT1 and XT2 oscillators accept a ceramic resonator or an 8-MHz crystal frequency at V CC ≥ 2.8V.2.In LF mode, the LFXT1 oscillator requires a watch crystal. In XT1 mode, FXT1 accepts a ceramic resonator or a crystal.3.The cumulative program time must not be exceeded during a block-write operation. This parameter is only relevant if segment write option is used.4.The mass erase duration generated by the flash timing generator is at least 11.1 ms. The cummulative mass erase time needed is 200 ms. This can be achieved by repeating the mass erase operation until the cumulative mass erase time is met (a minimum of 19 cycles may be required).f (MHz)8.0 MHzSupply Voltage – V’F13x/’F14x,Figure 1. Frequency vs Supply Voltage, MSP430F13x or MSP430F14xelectrical characteristics over recommended operating free-air temperature (unless otherwise noted)+ DV excluding external currentsupply current into AVCC2.Timer_B is clocked by f(ACLK) = 32,768 Hz. All inputs are tied to 0 V or to V CC. Outputs do not source or sink any current. The currentconsumption in LPM2 and LPM3 are measured with ACLK selected.electrical characteristics over recommended operating free-air temperature (unless otherwise noted) (continued)Current consumption of active mode versus system frequency, F-versionI(AM) = I(AM) [1 MHz]× f(System) [MHz]Current consumption of active mode versus supply voltage, F-versionI(AM) = I(AM)[3V]+ 175 µA/V × (V CC– 3 V)SCHMITT-trigger inputs – Ports P1, P2, P3, P4, P5, and P6standard inputs – RST/NMI; JTAG: TCK, TMS, TDI, TDO/TDIOH(max)OL(max),specified voltage drop.2.The maximum total current, I OH(max) and I OL(max), for all outputs combined, should not exceed ±24 mA to satisfy the maximumspecified voltage drop.outputs – Ports P1, P2, P3, P4, P5, and P6 (continued)Figure 2V OL – Low-Level Output Voltage – V 02468101214160.00.5 1.0 1.5 2.0 2.5TYPICAL LOW-LEVEL OUTPUT CURRENTvsLOW-LEVEL OUTPUT VOLTAGEO L I – L o w -L e v e l O u t p u t C u r r e n t – m AFigure 3V OL – Low-Level Output Voltage – V05101520250.00.5 1.0 1.5 2.0 2.5 3.03.5TYPICAL LOW-LEVEL OUTPUT CURRENTvsLOW-LEVEL OUTPUT VOLTAGEO L I – L o w -L e v e l O u t p u t C u r r e n t – m AFigure 4V OH – High-Level Output Voltage – V–14–12–10–8–6–4–200.00.51.01.52.02.5TYPICAL HIGH-LEVEL OUTPUT CURRENTvsHIGH-LEVEL OUTPUT VOLTAGEO H I – H i g h -L e v e l O u t p u t C u r r e n t – m AFigure 5V OH – High-Level Output Voltage – V–30–25–20–15–10–50.00.5 1.0 1.5 2.0 2.5 3.03.5TYPICAL HIGH-LEVEL OUTPUT CURRENTvsHIGH-LEVEL OUTPUT VOLTAGEO H I – H i g h -L e v e l O u t p u t C u r r e n t – m Aelectrical characteristics over recommended operating free-air temperature (unless otherwise noted) (continued)output frequencyfrequencies can be different.(int)trigger signals shorter than t(int). Both the cycle and timing specifications must be met to ensure the flag is set. t(int) is measured in MCLK cycles.2.The external capture signal triggers the capture event every time the minimum t(cap) cycle and time parameters are met. A capturemay be triggered with capture signals even shorter than t(cap). Both the cycle and timing specifications must be met to ensure a correct capture of the 16-bit timer value and to ensure the flag is set.3.Seven capture/compare registers in ’x14x and three capture/compare registers in ’x13x.electrical characteristics over recommended operating free-air temperature (unless otherwise noted) (continued)leakage current (see Note 1)SS CC 2.The port pin must be selected as input and there must be no optional pullup or pulldown resistor.should take place during this supply voltage condition.lkg(Px.x)2.The input offset voltage can be cancelled by using the CAEX bit to invert the Comparator_A inputs on successive measurements.The two successive measurements are then summed together.electrical characteristics over recommended operating free-air temperature (unless otherwise noted) (continued)T A – Free-Air Temperature – °C 400450500550600650–45–25–51535557595Figure 6. V (RefVT) vs Temperature, V CC = 3 VV (R E F V T )– R e f e r e n c e V o l t s –m VFigure 7. V (RefVT) vs Temperature, V CC = 2.2 VT A – Free-Air Temperature – °C400450500550600650–45–25–51535557595V (R E F V T )– R e f e r e n c e V o l t s –m VV+τ ≈ 2.0 µsTo Internal ModulesSet CAIFG FlagCAOUT V –Figure 8. Block Diagram of Comparator_A ModuleV Figure 9. Overdrive Definitionelectrical characteristics over recommended operating free-air temperature (unless otherwise noted) (continued)PORVVVFigure 10. Power-On Reset (POR) vs Supply Voltage1.20.800.20.40.60.811.21.41.61.82–40–2020406080T A – Temperature – °CV P O R – VFigure 11. V POR vs Temperatureelectrical characteristics over recommended operating free-air temperature (unless otherwise noted) (continued)DCO (see Note 1)(System)2.This parameter is not production tested.f DCO_0f DCO_7–F r e q u e n c y V a r i a n c eFigure 12. DCO Characteristicselectrical characteristics over recommended operating free-air temperature (unless otherwise noted) (continued)main DCO characteristicsD Individual devices have a minimum and maximum operation frequency. The specified parameters forf DCOx0 to f DCOx7 are valid for all devices.D All ranges selected by Rsel(n) overlap with Rsel(n+1): Rsel0 overlaps with Rsel1, ... Rsel6 overlaps withRsel7.D DCO control bits DCO0, DCO1, and DCO2 have a step size as defined by parameter S DCO.D Modulation control bits MOD0 to MOD4 select how often f DCO+1 is used within the period of 32 DCOCLKcycles. The frequency f(DCO) is used for the remaining cycles. The frequency is an average equal to f(DCO) × (2MOD/32 ).(t) URXS flip-flop is set. The URXS flip-flop is set with negative pulses meeting the minimum-timing condition of t(t). The operating conditions to set the flag must be met independently from this timing constraint. The deglitch circuitry is active only on negative transitions on the URXD0/1 line.electrical characteristics over recommended operating free-air temperature (unless otherwise noted) (continued)12-bit ADC, power supply and input range conditions (see Note 1)‡Not production tested, limits verified by designNOTES: 1.The leakage current is defined in the leakage current table with P6.x/Ax parameter.2.The accuracy limits the minimum positive external reference voltage. Lower reference voltage levels may be applied with reducedaccuracy requirements.3.The accuracy limits the maximum negative external reference voltage. Higher reference voltage levels may be applied with reducedaccuracy requirements.4.The accuracy limits minimum external differential reference voltage. Lower differential reference voltage levels may be applied withreduced accuracy requirements.5.The analog input voltage range must be within the selected reference voltage range V R+ to V R– for valid conversion results.6.The internal reference supply current is not included in current consumption parameter I ADC12.7.The internal reference current is supplied via terminal AV CC. Consumption is independent of the ADC12ON control bit, unless aconversion is active. The REFON bit enables to settle the built-in reference before starting an A/D conversion.electrical characteristics over recommended operating free-air temperature (unless otherwise noted) (continued)12-bit ADC, built-in reference (see Note 1)‡Not production tested, limits verified by designNOTES: 1.The voltage source on V eREF+ and V REF–/V eREF–) needs to have low dynamic impedance for 12-bit accuracy to allow the charge to settle for this accuracy.2.The external reference is used during conversion to charge and discharge the capacitance array. The dynamic impedance shouldfollow the recommendations on analog-source impedance to allow the charge to settle for 12-bit accuracy.3.The internal buffer operational amplifier and the accuracy specifications require an external capacitor.4.The input capacitance is also the dynamic load for an external reference during conversion. The dynamic impedance of the referencesupply should follow the recommendations on analog-source impedance to allow the charge to settle for 12-bit accuracy. All INL and D NL t ests u ses t wo c apacitors b etween p ins V REF+a nd A V SS a nd V REF–/V eREF–a nd A V SS: 10 µF t antalum a nd 100nF c eramic.electrical characteristics over recommended operating free-air temperature (unless otherwise noted) (continued)12-bit ADC, timing parameters‡Not production tested, limits verified by designNOTES: 1.The condition is that the error in a conversion started after t REF(ON) is less than ±0.5 LSB. The settling time depends on the externalcapacitive load.2.The condition is that the error in a conversion started after t ADC12ON is less than ±0.5 LSB. The reference and input signal are alreadysettled.3.Ten Tau (τ) are needed to get an error of less than ±0.5 LSB. t Sample = 10 x (Ri + Zi) x Ci+ 800 nsC 1 µ in µF100 µ10 µFigure 13. Typical Settling Time of Internal Reference t REF(ON) vs External Capacitor on V REF +electrical characteristics over recommended operating free-air temperature (unless otherwise noted) (continued)12-bit ADC, linearity parameters。

msp430

MSP430单片机系列种类

非基于LCD

MSP430x1xx: : 基于闪存/ ROM的MCU提供 伏至3.6伏的工作电压, 基于闪存 的 提供1.8伏至 伏的工作电压, 提供 伏至 伏的工作电压 高达60kB和8MIPS(带有基本时钟 带有基本时钟) 高达 和 带有基本时钟 MSP430F2xx: : 基于闪存的MCU 提供 提供1.8 伏至 伏至3.6 伏工作电压,掉电复位及 伏工作电压, 基于闪存的 16MIPS(带有基本时钟 带有基本时钟) 带有基本时钟 MSP430F5XX: : 基于闪存的MCU 提供 提供1.8 伏至 伏至3.6 伏工作电压,掉电复位及 伏工作电压, 基于闪存的 18MIPS(带有基本时钟 带有基本时钟) 带有基本时钟

各模块简要介绍— 5,Msp430f247的基准时钟系统

系统复位后: 系统复位后: MCLK和SMCLK由DCO提供, 提供, 和 由 提供 ACLK由LFXT1提供 由 提供

以下是DCO设置程序: //设定DCO为16MHZ : BCSCTL1 =CALBC1_16MHZ; DCOCTL =CALDCO_16MHZ; 可选频率1M,8M,12M,16M 读取0x10f9和0x10f8两 个地址里面 16MHzDCO常数分别 装入BCSCTL1和 DCOCTL两个寄存器

MSP430单片机的应用领域

日常公用测量 水表,气表,自动抄表, 水表,气表,自动抄表,先进电 表网络基础设施, 表网络基础设施,热分配表 便携式消费 无线鼠标和键盘,触摸按键, 无线鼠标和键盘,触摸按键, 手机,数码相机, 手机,数码相机,MP3 电动牙刷,剃须刀, 电动牙刷,剃须刀,运动手表等

主要内容

Msp430单片机简介 Msp430单片机简介 Msp430单片机的结构及主要模块 Msp430单片机的结构及主要模块 Msp430单片机的具体应用 Msp430单片机的具体应用 —位移测量装置 位移测量装置

MSP430系列单片机简介

MSP430系列单片机简介MSP430系列单片机是美国德州仪器(TI)推向市场的一个16位、具有精简指令集、超低功耗的混合型单片机,自1996年问世,由于它具有极低的功耗、丰富的片内外设备和方便灵活的开发手段,成为许多电子产品设计的首选,1999年进入中国就受到了中国广大设计工程师的青睐。

目前,该系列单片机不仅在电子工程、测控技术与仪器、自动控制、机电一体化等方面得到广泛应用,而且逐渐走进校园,被越来越多的使用在硕士研究生和高年级本科生的科技实践和毕业设计中,在2005年暑期全国大学生电子设计竞赛中就选用了该系列的单片机[5]。

MSP430系列单片机的型号很多,TI公司用3或4位数字表示单片机型号,其中一位数字表示一个系列。

目前有四大系列:带有液晶驱动的MSP430F4xx 系列单片机、不带液晶驱动器的MSP430F1xx系列单片机、16MIPS高速MSP430F2xx系列单片机、一次性写入(OTP)型低价MSP430C系列单片机,每个系列中又含有许多子系列。

单片机型号的第二位数字表示子系列号,一般子系列号越大包含的功能模块越多,最后一或两位数字表示存储器容量,数字越大表示ROM和RAM的容量越大。

此外,MSP430系列单片机还针对许多热门应用设计了一系列专用单片机,如水表专用单片机、医疗仪器专用单片机,电能计量专用单片机,这些单片机都是在相同型号的通用单片机的基础上增加专用模块构成的[5]。

MSP430F449单片机的主要性能有:●低供电电压范围:1.8V-3.6V及欠电压检测器●超低功耗,具有五种省电模式:活动模式:1MHz,2.2V时为280uA;等待模式:1.6uA;关闭模式(RAM保持):0.1uA●数字控制的振荡器(DCO)可以在6us内将CPU从休眠中唤醒,这也是实现低功耗的重要手段之一●16位精简指令结构,125ns指令时间周期,10个16位的寄存器以及常数发生器,能够最大限度的提高代码的效率●具有内部参考电平,采样保持和自动扫描的12位A/D转换器●带有三个或七个捕捉/比较影子寄存器的16位定时器B●带有三个捕捉/比较寄存器的16位定时器A● 串行通讯接口(USART ),软件选择异步UART 或者同步SPI 接口,对于MSP430F44x 系列的单片机有两个UART (UART0,UART1)● 可编程电平检测的供电电压管理器/监视器● 串行在线编程无需外部编程电压,可编程的安全熔丝代码保护● 集成多达160段的LCD 驱动器如图2.1所示为MSP430F449单片机的引脚图。

第一章MSP430单片机概述

第一章MSP430单片机概述MSP430是一种低功耗、高性能的单片机,由德州仪器(Texas Instruments,TI)公司开发。

它采用了超低功耗的电源管理技术,使其在电池供电下能够持续运行数年之久。

MSP430单片机适用于许多应用领域,包括消费电子、医疗设备、工业自动化、智能家居和传感器网络等。

MSP430单片机的核心是RISC架构的16位处理器,具有较小的指令集,运行速度快,并且能够以较低的能耗完成各种任务。

它采用了哈佛结构,具有16位的定长指令格式,有着高效的编码能力。

此外,它还具有多种中断机制,可以快速响应外部事件或实现多任务操作。

MSP430单片机提供了多个不同的系列,以适应不同应用场景的需求。

不同系列的MSP430单片机在处理器速度、内存容量和外设接口等方面有所差异。

其中,MSP430F系列适用于通用应用,而MSP430G系列适用于低成本和功耗敏感的应用。

此外,MSP430FR系列还具有非易失性存储器,可以在掉电情况下保留数据。

MSP430单片机具有丰富的外设接口,包括通用IO口、模拟输入输出、时钟控制器、串口通信、定时器和比较器等。

这些外设接口使得MSP430单片机能够灵活地与其他设备进行通信,并实现多种功能。

MSP430单片机在低功耗方面具有很大优势。

它采用了多种省电技术,包括多级电源管理、动态电压调节和片上电源管理单元等。

这些技术使得MSP430单片机在待机和运行模式下的功耗都非常低,能够更好地满足移动设备和电池供电设备的需求。

总的来说,MSP430单片机是一种低功耗、高性能的单片机,具有丰富的外设接口和完善的开发工具链。

它适用于多种应用领域,可以满足不同需求的设计要求。

随着物联网的快速发展,MSP430单片机的市场前景十分广阔,并且将继续发挥重要作用。

MSP430简介(超详细·)

msp430简介MSP430是德州公司新开发的一类具有16位总线的带FLASH 的单片机,由于其性价比和集成度高,受到广大技术开发人员的青睐.它采用16位的总线,外设和内存统一编址,寻址范围可达64K,还可以外扩展存储器.具有统一的中断管理,具有丰富的片上外围模块,片内有精密硬件乘法器、两个16位定时器、一个14路的12位的模数转换器、一个看门狗、6路P口、两路USART通信端口、一个比较器、一个DCO内部振荡器和两个外部时钟,支持8M 的时钟.由于为FLASH型,则可以在线对单片机进行调试和下载,且JTAG口直接和FET(FLASH EMULATION TOOL)的相连,不须另外的仿真工具,方便实用,而且,可以在超低功耗模式下工作对环境和人体的辐射小,测量结果为100mw左右的功耗(电流为14mA左右),可靠性能好,加强电干扰运行不受影响,适应工业级的运行环境,适合与做手柄之类的自动控制的设备.我们相信MSP430单片机将会在工程技术应用中得以广泛应用,而且,它是通向DSP系列的桥梁,随着自动控制的高速化和低功耗化, MSP430系列将会得到越来越多人的喜爱.一、IO口(一)、P口端口寄存器:1、PxDIR 输入/输出方向寄存器(0:输入模式 1:输出模式)2、PxIN 输入寄存器输入寄存器是只读寄存器,用户不能对其写入,只能通过读取该寄存器的内容知道I/O口的输入信号。

3、PxOUT 输出寄存器寄存器内的内容不会受引脚方向改变的影响。

4、PxIFG 中断标志寄存器(0:没有中断请求 1:有中断请求)该寄存器有8个标志位,对应相应的引脚是否有待处理的中断请求;这8个中断标志共用一个中断向量,中断标志不会自动复位,必须软件复位;外部中断事件的时间必须>=1.5倍的MCLK的时间,以保证中断请求被接受;5、PxIES 中断触发沿选择寄存器(0:上升沿中断 1:下降沿中断)6、PxSEL 功能选择寄存器(0:选择引脚为I/O端口 1:选择引脚为外围模块功能)7、PxREN 上拉/下拉电阻使能寄存器(0:禁止 1:使能)(二)、常用特殊P口:1、P1和P2口可作为外部中断口。

MSP430简介(超详细·)

MSP430简介(超详细·)msp430简介MSP430是德州公司新开发的⼀类具有16位总线的带FLASH 的单⽚机,由于其性价⽐和集成度⾼,受到⼴⼤技术开发⼈员的青睐.它采⽤16位的总线,外设和内存统⼀编址,寻址范围可达64K,还可以外扩展存储器.具有统⼀的中断管理,具有丰富的⽚上外围模块,⽚内有精密硬件乘法器、两个16位定时器、⼀个14路的12位的模数转换器、⼀个看门狗、6路P⼝、两路USART通信端⼝、⼀个⽐较器、⼀个DCO内部振荡器和两个外部时钟,⽀持8M 的时钟.由于为FLASH型,则可以在线对单⽚机进⾏调试和下载,且JTAG⼝直接和FET(FLASH EMULATION TOOL)的相连,不须另外的仿真⼯具,⽅便实⽤,⽽且,可以在超低功耗模式下⼯作对环境和⼈体的辐射⼩,测量结果为100mw左右的功耗(电流为14mA左右),可靠性能好,加强电⼲扰运⾏不受影响,适应⼯业级的运⾏环境,适合与做⼿柄之类的⾃动控制的设备.我们相信MSP430单⽚机将会在⼯程技术应⽤中得以⼴泛应⽤,⽽且,它是通向DSP 系列的桥梁,随着⾃动控制的⾼速化和低功耗化, MSP430系列将会得到越来越多⼈的喜爱.⼀、IO⼝(⼀)、P⼝端⼝寄存器:1、PxDIR 输⼊/输出⽅向寄存器(0:输⼊模式 1:输出模式)2、PxIN 输⼊寄存器输⼊寄存器是只读寄存器,⽤户不能对其写⼊,只能通过读取该寄存器的内容知道I/O⼝的输⼊信号。

3、PxOUT 输出寄存器寄存器内的内容不会受引脚⽅向改变的影响。

4、PxIFG 中断标志寄存器(0:没有中断请求 1:有中断请求)该寄存器有8个标志位,对应相应的引脚是否有待处理的中断请求;这8个中断标志共⽤⼀个中断向量,中断标志不会⾃动复位,必须软件复位;外部中断事件的时间必须>=1.5倍的MCLK的时间,以保证中断请求被接受;5、PxIES 中断触发沿选择寄存器(0:上升沿中断 1:下降沿中断)6、PxSEL 功能选择寄存器(0:选择引脚为I/O端⼝ 1:选择引脚为外围模块功能)7、PxREN 上拉/下拉电阻使能寄存器(0:禁⽌ 1:使能)(⼆)、常⽤特殊P⼝:1、P1和P2⼝可作为外部中断⼝。

msp430学习资料

MSP430单片机外围模块演讲者:技术部六、USART(UART)异步通讯模块讲解•USART模块(UART)结构、特点•工作模式•介绍相应的寄存器试验:fet440_uart01_09600.cUSART模块(UART)的特点•传输7位或8位数据,带奇校验/偶校验或无校验;•两个独立移位寄存器:输入移位寄存器和输出移位寄存器•独立的收、发缓存;•最低位开始的数据收发;•异步模式,包括线路空闲/地址位通信协议•通过有效的起始位检测将MSP430从低功耗唤醒•编程实现分频因子为整数或小数的波特率•错误检测、抑制和地址检测的状态标志位;•独立的收、发中断;USART模块(UART)的结构USART初始化和复位ART在PUC信号或通过设置SWRST(软件复位位)时复位,当PUC信号后,SWRST位自动置位,保持USART在复位状态。

SWRST位复位URXIEx, UTXIEx, URXIFGx, RXWAKE,TXWAKE, RXERR, BRK, PE, OE, 和FE 位.置位UTXIFGx和TXEPT位. 接收和发送使能位URXEx 和UTXEx不改变.当复位SWRST,USART进入操作模式.2.操作步骤如下:(1)置位SWRST:(BIS.B #SWRST,&UxCTL)(2)设置USART的相关寄存器(3)使能USART模块通过设置MEx寄存器(4)清SWRST位(5)使能收发中断UART模式操作---数据格式UART模式操作---异步通讯格式线路空闲多机模式如何发空闲周期UART模式操作---异步通讯格式地址位多机模式(MM=1)UART模式操作---自动错误检测FE 标志帧错误:当一个接收字符的停止位为0并被装入接收缓存,接收的为一个错误的帧,那么帧错标志被设置成1,即使在多停止位模式时也只检测第一个停止位。

同样,丢失停止位意味着从起始位开始的同步特性被丧失,也是一个错误帧。

在同步的4线模式时,因总线冲突使有效主机停止,并在STE引脚信号出现下降沿时使FE位设置为1PE 奇偶校验错误:当接收字符中1的个数与它的校验位不相符,并被装入接收缓存时,发生校验错,设置PE为1OE 溢出错误标志:当一个字符写入接收缓存URXBUF时,前一个字符还没有被读出,这时前一个字符因被覆盖而丢失,发生溢出(同步与异步情况相同)BRK 打断检测标志:当发生一次打断同时URXEIE置位时,该位被设置为1,表示接收过程被打断过。

电子10级《单片机MSP430》第1章

290 μA/MHz在8MHz,3.0V,Flash Program

150 μA/MHz在8MHz,3.0V,RAM Program --待机模式(LPM3): 实时时钟、看门狗、电源监控、RAM数据保持、快速 唤醒: 1.9μA在2.2V,2.1μA在3.0V(典型) 低功耗振荡器、通用计数器、看门狗、电源监控、

多振荡器时钟系统

8

MSP430单片机的高集成度特点

◆智能外设:MSP430 MCU的外设专为确保最强大之功能性而设 计,许多外设都可以执行自主型操作,因而最大限度减少了CPU处 于工作模式的时间; ◆高性能集成:超过400款MSP430器件都具备高性能集成优势, 完美整合了USB、RF、LCD控制器以及16位Σ-ΔADC等。此外, MSP430 MCU的高集成度还造就物理尺寸较小的解决方案,进而最 大限度地降低总物料成本。 ◆MSP430集成外设一览表:

15

MSP430F5529引脚图

16

MSP430F5529结构框图

17

MSP430G2XXX结构框图

18

19

(1)MSP-EXP430F5529官方网站: /tool/msp-exp430f5529&DCMP=MSP430&HQS=Other+OT+usbexp (2)MSP-EXP430F5529开发板用户指导手册:/lit/pdf/SLAU330 (3)MSP-EXP430F5529开发板硬件电路图:/lit/zip/slar055 (4)MSP430x5xx/x6xx用户指导: /general/docs/lit/getliterature.tsp?baseLiteratureNumber=slau208&fileType= pdf&track=no (5)MSP430F552x数据手册: /general/docs/lit/getliterature.tsp?baseLiteratureNumber=slas590&fileType= pdf&track=no (6)MSP430F552X例程:/lit/zip/slac300 (7)CCSv5下载途径:/index.php/Download_CCS (8)USB开发资源库下载途径: /tool/msp430usbdevpack?DCMP=53xx663x&HQS=msp430usbdevpackpr-tf (9)电容触摸资源库下载途径:/tool/capsenselibrary#1

msp430中文资料_数据手册_参数

因此,寄存器操作执行时间是CPU时钟的一个周期。R0到R3中的四个寄存器分别是程序

计数器、堆栈指针、状msp430态寄存器和常量生成器。外围设备通过数据、地址和控制

总线连接到CPU,可以使用所有指令进行处理。指令msp430集指令集由51条指令组成,

有三种格式和七种地址模式。可对字和字节数据进行操作。表1显示了三种结构格式的示

例;地址模式为listedin表外 通过数据、地址和控制总线连接到CPU,可以使用所有指

令进行处理。有完 的模块描述,

MSP430x1xx家庭用户指南,literaturenumber

SLAU049。时钟系统由基本的时钟模块 ,包括对32768-Hz 表晶体 、内部数字

控msp430制振荡器(DCO)和高频晶体振荡器的 。基本 条模块的设计是为了 低

是一种超低功率混合msp430信号单片机,内置16位定时器和14个I/O引脚。典型的应用包

括捕捉模拟信号、将它们转换为数字值、然后处理数据并显示它们或将它们传输到主机

系统的传感器系统。独立射频传感器前端是另一个msp430应用领域1998年12月

MSP430x11xMIXED信号MICROCONTROLLERSSLAS196D 修订655303年9月20044邮政

列超msp430功率微控制器由几个不同的设备组成,其外围设备针对不同的应用。该体系

结构与五种低功耗模式相结合,优化后msp430可在便携式测量应用中延长电池寿命。该

设备具有强大的16位RISC CPU、16位寄存器和常量生成器,这些属性都具有最高的代码

效率。数控振荡器(DCO)允许从低功耗模式唤醒activemode在不到6 s。MSP430x11x系列

体谐振器 外部时钟的16位Timer_A ThreeCapture /比较RegistersD串行机上

MSP430系列单片机介绍

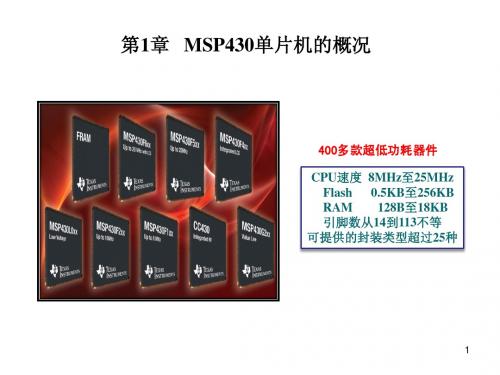

MSP430系列单片机介绍MSP430系列单片机是德州仪器(TI)公司推出的一种低功耗、高集成度、高性能的16位超低功耗单片机。

它采用精确的调度技术和先进的低功耗架构设计,拥有出色的性能、高功耗效率、广泛的外设集成以及丰富的工具和软件支持。

MSP430系列单片机的内核基于RISC架构,拥有16位数据总线和16位地址总线。

它可以工作在多种工作频率下,从几kHz到几十MHz不等,以满足不同的应用需求。

此外,MSP430系列单片机还具有多种睡眠模式,可以进一步降低功耗。

MSP430系列单片机内置了丰富的外设,包括模拟接口、数字接口和通信接口。

模拟接口包括模数转换器(ADC)、数字模拟转换器(DAC)和比较器等,可以实现各种传感器接口和模拟信号处理。

数字接口包括通用输入输出(GPIO)、定时器/计数器、串行通信接口等,可以实现数字信号处理和通信功能。

通信接口包括UART、SPI和I2C等,可以实现与外部设备的数据交换。

MSP430系列单片机广泛应用于各种电子设备中,如便携式设备、智能家居、医疗器械、工业自动化等。

由于其低功耗和高性能的特点,它可以满足不同应用场景下对功耗和性能的需求。

例如,在便携式设备中,MSP430系列单片机可以实现长时间的电池寿命;在智能家居中,它可以实现低功耗的远程控制和数据传输;在医疗器械中,它可以实现高精度的信号处理和通信。

总之,MSP430系列单片机是一种低功耗、高集成度、高性能的16位超低功耗单片机。

通过其先进的架构设计和丰富的外设集成,它可以满足各种应用的需求。

同时,它还提供了丰富的工具和软件支持,方便开发者进行开发和调试。

MSP430单片机简介

一、单片微型计算机(复习)1、计算机组成运算器(加法器)二进制加法(减法=补码加法)寄存器暂存中间结果存储器随机(RAM),只读(ROM)总线地址、数据、控制外设(系统内部)定时器、I/O接口…….2、单片微型计算机组成包括全部计算机系统核心部件集成在一块芯片上(大规模集成电路)各部件数量少或者较简单可以独立运行常用于各种产品中,使其具有智能功能二、MSP430单片微型计算机1、主要特点美国德州仪器设计生产业界功耗最低的16位RISC结构单片微型计算机具有高、中、低多种型号适用于高抗干扰、低功耗、电池供电等2、基本结构、工作特点16位RISC结构单片微型计算机,片内RAM(64字节~16K字节),片内ROM(512字节~1M字节)…….27条基本指令,基本都是单时钟周期片内外设丰富:2~8个双向8位I/O口,1~3个16位定时器(带多个比较、捕获寄存器)……..多种时钟选择内部、外部,高频、低频4种休眠模式,配合多种时钟选择和特殊的休眠唤醒方式实现低功耗运行总线不开放兼容的仿真、烧写接口(4线JTAG或2线SBW),简单廉价的仿真开发工具IAR Embedded Workbench 仿真调试软件3、目前伟思使用的MSP430单片机品种:MSP430F135、MSP430F147、MSP430F149、MSP430F169以及MSP430F2012、MSP430F2013…….4、430_day_2008_final_CN.pdf5、MSP430的开发资源和开发工具.pdf三、MSP430单片微型计算机使用注意事项1、电源MSP430单片微型计算机工作电压:1.8~3.3V,最大不得超过3.6V2、I/O接口电平匹配与其他数字电路或设备接口时注意I/O接口电平匹配,不得超过电源电压。

注意每个I/O接口驱动电流限制与全部I/O接口驱动电流限制。

3、模拟与数字供电分开,注意电源滤波4、I/O接口输入模式时片内无上拉(部分CPU有可设置的上拉或下拉)5、其他。

msp430基础知识

5:完善的中断服务功能。

6:4种计数功能的选择

7:8种输出计数功能的选择。

8:支持多种时序控制

9:DMA使能

TAR 16位计数器

1:修改Timer _A:当计数时钟不是MLCK时,写入应该计数器在计数器停止计数时,因为它与CPU不同步,可能引起时间的竞争。

2:增计数模式

捕获/比较寄存器CCR0用作Timer_A增计数模式的周期寄存器。因为CCR0为16位寄存器,所以该模式适用于定时周期小于65536的连续计数情况。计数器TAR可以增计数到CCR0的值,当计数值与CCR0的值相等(或定时器值大于CCR0的值)时,定时器复位并从0开始重新计数。

LFXT1CLK:低频时钟源

XT2CLK:高频时钟源

DCOCLK:数字控制RC振荡器

时钟发生器的原理说明

问题的提出:

1: 高频,以便对系统硬件请求和事件作出快速的响应。

2:低频 以便将电流消耗降至最小

{

;

}

基本定时器

MSP430具有基本定时器(Basic Timer1),Basic Timer1经常用在低功耗应用中,它的工作目的就是支持软件和外围模块工作在低频率、低功耗条件下。Basic Timer1通过对SMCLK 和ACLK进行分频,向其他外围模块提供低频率控制信号。Basic Timer1非常适合于周期性地产生中断

。(F14系列没有该定时器)

Timer_A 的特性

1:输入时钟可以有多种选择,可以是慢始终、快时钟以及外部时钟。

2:没有自动重装时间常数功能,但产生的定时脉冲或PWM(脉宽调制)信号没有软件带来的误差。

3:不仅能捕获外部事件发生的时间还可以锁定其发生时的高低电平。

MSP430单片机新手上路-资料篇

MSP430单片机新手上路-资料篇(转)MSP430基础介绍Q1. MSP430使用8M的时钟刷新320 * 240的LCD点阵,不能及时刷新,而改用ARM后可以?A1:以前的MSP430为8MIPS的速度,但是并非MSP430的指令都是一个CYC的,MSP430指令的执行时间依赖于指令形式,寻址方式。

对于I/O操作的指令来说,消耗的指令周期为3个CYC,所以相对于I/O操作的效率并没有达到8MIPS。

要解决这个问题,可以使用今后已经推出的2XX系列或即将推出的5XX系列,她们的频率最高分别可达到16M和25M。

Q2.MSP430直接操作FLASH,RAM,是否需要累加器作Buff?A2:不需要,MSP430的寻址采用的Atomic的形式,任何地址的访问都可以做到直接访问,有效地解决了累加器的瓶颈。

Q3. MSP430单片机中乘法器是如何使用的?A3:MSP430单片机中有很多带有硬件乘法器。

如MSP430F149 在汇编中使用硬件乘法器只需要将乘数与被乘数放入相应得寄存器,经过一个CPU时钟后在将结果从寄存器中取出即可。

可参考《MSP430X4XX Family User’s Guide》中的第七章。

在C语言中,乘法的运算会由编译器自动的放入乘法器完成,用户不用直接的去操作乘法器。

Q4. FW和FE的特点?A4:MSP430FW42X是在MSP430F415的基础上集成了一个Scan IF 模块。

Scan IF模块通过对LC传感器震荡幅值的检测来确定L所处的位置,经状态处理机和时间处理机得到物体运动的变化。

目前被广泛用于Giant magneto-resistive、Hall-effect等领域。

MSP430FE42X是在MSP430F42X的基础上集成了一个电能计量模块(ESP430CE1),利用这个模块,可以自动的算出电能表的常用参数如有功功率,无功功率,相位,频率,电压,电流等。

用户只需要直接的去相应得寄存器读取就可以了。

MSP430课件四收集资料

可配置的通道优先权:优先权裁决模块,传输通道的优先级 可以调整,对同时有触发请求的通道进行优先级裁决,确定 哪个通道的优先级最高。MSP430的DMA控制器可以采用固定 优先级,还可以采用循环优先级。

P1DIR |= 0x01;

// P1.0 输出

CACTL1 = CARSEL + CAREF0 + CAON; // 0.25 Vcc = -comp

CACTL2 = P2CA0;

// P2.3 = +comp

while (1)

{

if ((CAOUT & CACTL2))

P1OUT |= 0x01;

The key violation flag KEYV is set when any of the flash control registers are written with an incorrect password. When this occurs, a PUC is generated immediately resetting the device.

// CAOUT =1, 置位 P1.0

else P1OUT &= ~0x01;

// 否则复位

}

}

MSP430--27

MSP430 DMA控制器的特性

数据传送不需要CPU介入,完全由DMA控制器自行管理。 在整个地址空间范围内传输数据,块方式传输可达65536字节。 能够提高片内外设数据吞吐能力,实现高速传输,每个字或者字

MSP430系列超低功耗16位 单片机原理与应用

MSP430系列单片机介绍

典型的 8bit 单片机

20MHz 晶振 内部 4 分频 主时钟:5MHz = 200ns 5 机器周期 / 指令 1000ns 指令周期,8 位操作

The MSP430 runs with a watch crystal at up to 8MHz internal clock!

MSP430 的能效极高. I/O 和 CPU 运行是能用不同的时钟 CPU 功耗的开关通过状态寄存器的 控制位实现

MSP430 的功耗极低. 执行时为 160uA @ 1.8V (Flash) 备用时为 0.1uA (Flash)

灵活多样的外围模块

10/12-bit A/D (8 + 4 通道, 转换<10 µs)

16-bit Timer_A with 3 C/C 寄存器

16-bit Timer_B with 7 C/C 寄存器

1- 2 个 USART接口

硬件乘法器

模拟信号比较器

基本时钟模块 - 由可编程内部电阻控制频率 - 由单一外部电阻控制频率 - 32 kHz 晶振产生低频 - 高频晶振产生高频 - 可选择外部时钟源

FLASH 型的时钟系统(F13x,F14x)

2 个晶振, 1 个DCO, 适应不同频率需要

速度比较: 32 kHz 时的运算快于 20 MHz

MSP430

32kHz 晶振 DCO 作为主时钟发生器 主时钟:4 MHz = 250ns 1 机器周期 / 指令 250ns 指令周期,16 位操作

-

MSP430F11214 KB Slope A3

-

MSP430F1338 KB 12-bit A3 + B3 1

MSP430单片机型号资料

MSP430 单片机型号资料

MSP430 单片机的发展

德州仪器1996 年到2000 年初,先后推出了31x、32x、33x 等几个系列,这些系列具有LCD 驱动模块,对提高系统的集成度较有利。

每一系列有

ROM 型(C)、OTP 型(P)、和EPROM 型(E)等芯片。

EPROM 型的价格昂贵,运行环境温度范围窄,主要用于样机开发。

这也表明了这几个系列的开

发模式,即:用户可以用EPROM 型开发样机;用OTP 型进行小批量生产; 而ROM 型适应大批量生产的产品。

2000 年推出了11x/11x1 系列。

这个系列采用20 脚封装,内存容量、片上功能和I/O 引脚数比较少,但是价格比较低廉。

这个时期的MPS430 已经显露出了它的特低功耗等的一系列技术特点,但

也有不尽如人意之处。

它的许多重要特性如:片内串行通信接口、硬件乘法器、足够的I/O 引脚等,只有33x 系列才具备。

33x 系列价格较高,比较适合于较为复杂的应用系统。

当用户设计需要更多考虑成本时,33x 并不一定

是最适合的。

而片内高精度A/D 转换器又只有32x 系列才有。

2000 年7 月推出了F13x/F14x 系列,在2001 年7 月到2002 年又相继推出F41x、F43x、F44x。

这些全部是Flash 型单片机。

F41x 系列单片机有48 个I/O 口,96 段LCD 驱动。

F43x、F44x 系列是在。

msp430单片机入门知识

PORT2_VECTOR (1 * 2u) /* 0xFFE2 P2 */ PORT1_VECTOR (4 * 2u) /* 0xFFE8 P1 */ TIMERA1_VECTOR (5 * 2u) /* 0xFFEA Timer A CCR1/2*/ TIMERA0_VECTOR (6 * 2u) /* 0xFFEC Timer A CCR0 */ USART0TX_VECTOR (8 * 2u) /* 0xFFF0 串口发送 */ USART0RX_VECTOR (9 * 2u) /* 0xFFF2 串口接收*/ WDT_VECTOR (10 * 2u) /* 0xFFF4 Watchdog Timer */ SD16_VECTOR (12 * 2u) /* 0xFFF8 16位ADC */ NMI_VECTOR (14 * 2u) /* 0xFFFC Non-maskable */ RESET_VECTOR (15 * 2u) /* 0xFFFE Reset */

20

中断的具体过程

1. 事先将中断服务程序入口地址装入中断 向量表。

2. 中断发生后,如果中断被允许(可屏蔽 中断),CPU将当前程序地址和CPU状 态寄存器SR压入堆栈。

3. 跳转到中断服务程序入口,备份寄存器 入堆栈。

4. 开始执行中断服务程序。 5. 退出中断前,恢复寄存器。CPU取回SR

寄存器,跳转回中断前主程序地址。

6

MSP430FE425A资源 1. 8M/s处理速度 2. 512RAM(数据)+16KB Flash(程序代码) 3. 内置Flash控制器,剩余Flash可存数据。 4. 内置时钟管理单元,可内部倍频 5. 3路同步采样、差分输入、32倍程控增益放大器的16位ADC 6. 温度传感器 7. 1.2V基准源和输出缓冲器 8. 128段LCD驱动器 9. 增强UART串口 10. 看门狗 11. BasicTimer定时器 12. 16位TimeA定时器,3路捕获和2路PWM 13. 内置BOR复位电路 14. 16个双向可中断IO口 15. 内置电能计量模块 16. 后缀带A的,比如FE425A带硬件乘法器

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Timer_B ADC12 USART Comp_A

X12x

USART

F41x

x11x1

Comp_A

F40x

F42x

F44x

1996

1999

2000

2001

2002

August 00 / 2

MSP430:全新的微控制器

Ultra-low power design with

RUN THE MARATHON, NOT THE MILE.

2 个晶振, 1 个DCO, 适应不同频率需要

August 00 / 11

Ultra-low power design with

速度比较: 32 kHz 时的运算快于 20 MHz

MSP430

32kHz 晶振 DCO 作为主时钟发生器 主时钟:4 MHz = 250ns 1 机器周期 / 指令 250ns 指令周期,16 位操作

August 00 / 13

MSP430x32x框图

Ultra-low power design with

XIN XOut XBuf

VCC VSS

RST/NMI

P0.0 P0.7

TDI TDO

TMS TCK

Oscillator FLL

System Clock

ACLK MCLK

8kB ROM

16kB ROM

MSP430F1101 1 KB Slope A3

-

MSP430F1121 4 KB Slope A3

-

MSP430F133 8 KB 12-bit A3 + B3

1

MSF430F135 16 KB 12-bit A3 + B3

1

MSP430F147 32 KB 12-bit A3 + B7

2

MSP430F148 48 KB 12-bit A3 + B7

MSP430 编程方便,开发工具廉价

ADD MEM1,MEM2 ;MEM2=MEM1+MEME2

MSP430 的功耗极低. 执行时为 160uA @ 1.8V (Flash) 备用时为 0.1uA (Flash)

MSP430 极大地延长了电电池寿命

The MSP430 runs with a watch crystal at up to 4MHz internal clock!

August 00 / 3

MSP430F1xx: FLASH 系列特性

Ultra-low power design with

New

RUN THE MARATHON, NOT THE MILE. TI’s Flash MSP430 MCU reduces power consumption drastically, so your batteries run longer.

6 1.3 0.1

Active Mode LPM0 LPM1 LPM2 LPM3 LPM4

例:LPM3, 备用模式 (MSP430C31x) 32768Hz 振荡器活动。 基于 Basic Timer1 的实时钟活动。 LCD 驱动有效。

August 00 / 7

超低功耗的实现:FLASH 型

Ultra-low power design with

Oscillator FLL

System Clock

ACLK MCLK

24kB ROM 32kB ROM

32kB EPROM

CPU

MAB, 16bit Test

incl. 16 reg. JTAG

MDB, 16bit

8

8

1024B

RAM

SRAM

Poweron-

Reset

I/O Port

1x8 dig. I/O's

Bus conv.

WDT 15bit

Timer/ Port

A0..5 RI SVCC

TP.0 TP.5 .....TP.4 CIN

8b Timer/ Counter

Serial Protocol Support

I/O Port

RXD

8 I/O's

TXD 3 Int. Vectors

MAB,4bit MCB MDB,8bit

- 由可编程内部电阻控制频率 - 由单一外部电阻控制频率 - 32 kHz 晶振产生低频 - 高频晶振产生高频 - 可选择外部时钟源

August 00 / 4

MSP430 系列

Ultra-low power design with

注: 1 - 可由 Comparator_A 实现 2 - 可由 Timer/Port 实现 3 - 有 256B FLASH 和 Boot ROM

I/O Port

2x8 I/O's all with interr. cap.

2 Int. Vectors

I/O Port

1x8 dig. I/O抯

I/O Port

8 I/O's, all with

interr. cap. 3 Int. Vectors

UART MAB,4bit

MCB

Bus MDB,8bit conv.

B. Timer

LCD

f LCD CMPI

84 Segmente 1, 2, 3, 4 Mux

R03 R23 R13 R33

Com0..3 Seg 0..19 Seg 20/CMPI

August 00 / 14

MSP430x31x框图

Ultra-low power design with

August 00 / 5

MSP430 FLASH 系列

Ultra-low power design with

New

Five new Flash configurations available now!

型号

FLASH A/D Timers USART MPY I/O

FLASH 型

超低功耗 Flash 内核 100,000 次写/擦周期 程序存储器分段:512B

TI’s Flash MSP430 MCU reduces power consumption drastically, so your batteries run longer.

MSP430 的能效极高.

I/O 和 CPU 运行是能用不同的时钟

CPU 功耗的开关通过状态寄存器的 控制位实现

MSP430 有工业级 16 bit RISC MCU. -40 - 85 ºC

16kB EPROM

'C': Prom 'P': OTP 'E': EProm

256B RAM 512B RAM 512B RAM

SRAM

POR

CPU

MAB, 16bit Test

incl. 16 reg. JTAG

MDB, 16bit

ADC 12+2bit

5 Channels Current S.

灵活多样的外围模块 • 12-bit A/D (8 + 4 通道, 转换<10 µs) • 16-bit Timer_A with 3 C/C 寄存器 • 16-bit Timer_B with 7 C/C 寄存器 • 1- 2 个 USART接口 • 硬件乘法器 • 模拟信号比较器 • 基本时钟模块

August 00 / 9

Ultra-low power design with

FLASH 型的时钟系统(F11x,F11x1)

1 个晶振, 1 个DCO, 适应不同频率需要

August 00 / 10

Ultra-low power design with

FLASH 型的时钟系统(F13x,F14x)

4 - Input/Output + Output

外围模块: TIMERS: WDT - Watchdog 定时器

8bit T - 8 位定时器/计数器

BT1 - Basic Timer 1 T_A - Timer_A (x) 捕捉/比较寄存器 T_B - Timer_B (x) 捕捉/比较寄存器

UART 软件实现,或通用同步/异步接口数 MPY 硬件乘法器 I/O 数字 I/O,及Output

x32x

LCD84 ADC14

x33x

LCD120 Timer_A USART

MPY

x31x

LCD92

Flash

1.8-3.6 V Basic Clock Timer_A

Flash

1.8-3.6 V LCD Driver ….

New F14x

New

F13x

Timer_B ADC12 2 USART

MPY Comp_A

典型的 8bit 单片机

20MHz 晶振 内部 4 分频 主时钟:5MHz = 200ns 5 机器周期 / 指令 1000ns 指令周期,8 位操作

MSP430 performs 16 bit instead of 8 bit 4 times faster than a typical 8 bit C !!

其他 MCU

I IAvrg

MSP430

I

IAvrg

* 4/ 8bit CPU * 电流消耗大 * 唤醒慢

t

* 16bit CPU * 突发式模式切换 * 电流消耗小 * 唤醒快 (<6 µs)

t

Icc / µA

450 400

400

350

300

250

200

150

100

50 50