IO端口地址分配

单片机io分配表

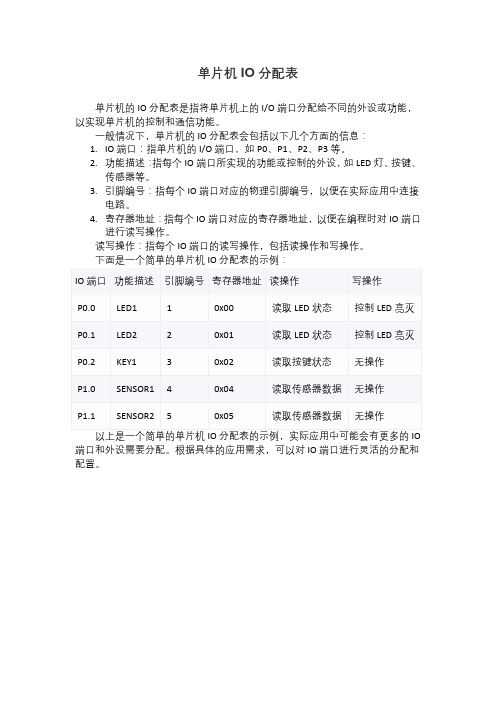

单片机IO分配表

单片机的IO分配表是指将单片机上的I/O端口分配给不同的外设或功能,以实现单片机的控制和通信功能。

一般情况下,单片机的IO分配表会包括以下几个方面的信息:

1.IO端口:指单片机的I/O端口,如P0、P1、P2、P3等。

2.功能描述:指每个IO端口所实现的功能或控制的外设,如LED灯、按键、

传感器等。

3.引脚编号:指每个IO端口对应的物理引脚编号,以便在实际应用中连接

电路。

4.寄存器地址:指每个IO端口对应的寄存器地址,以便在编程时对IO端口

进行读写操作。

读写操作:指每个IO端口的读写操作,包括读操作和写操作。

端口和外设需要分配。

根据具体的应用需求,可以对IO端口进行灵活的分配和配置。

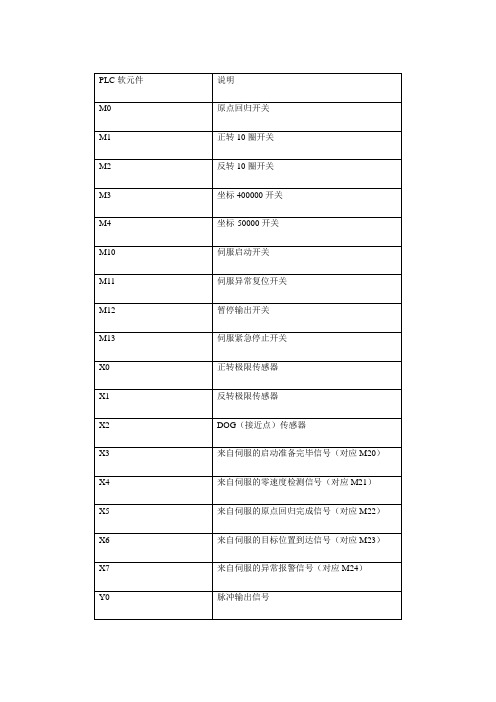

PLC IO口分配

PLC软元件说明

M0 原点回归开关

M1 正转10圈开关

M2 反转10圈开关

M3 坐标400000开关

M4 坐标-50000开关

M10 伺服启动开关

M11 伺服异常复位开关

M12 暂停输出开关

M13 伺服紧急停止开关

X0 正转极限传感器

X1 反转极限传感器

X2 DOG(接近点)传感器

X3 来自伺服的启动准备完毕信号(对应M20)X4 来自伺服的零速度检测信号(对应M21)X5 来自伺服的原点回归完成信号(对应M22)X6 来自伺服的目标位置到达信号(对应M23)X7 来自伺服的异常报警信号(对应M24)

Y0 脉冲输出信号

Y1 伺服电机旋转方向信号输出Y4 清除伺服脉冲计数寄存器信号Y6 伺服启动信号

Y7 伺服异常复位信号

Y10 伺服电机正方向运转禁止信号Y11 伺服电机反方向运转禁止信号Y12 伺服紧急停止信号

M20 伺服启动完毕状态

M21 伺服零速度状态

M22 伺服原回归完成状态

M23 伺服目标位置到达状态

M24 伺服异常报警状态。

8086对存储器和io端口的编址方式

8086是intel公司推出的一款16位微处理器,它采用了20位位置区域总线,能够寻址1MB的内存空间。

在8086中,存储器和I/O端口的编址方式对于系统的设计和应用具有重要意义。

本文将围绕8086对存储器和I/O端口的编址方式展开深入探讨。

一、存储器的编址方式1. 实位置区域模式8086微处理器最初工作在实位置区域模式下,通过物理位置区域直接对存储器进行寻址。

在实位置区域模式下,8086可以访问的存储器空间为1MB,位置区域空间范围为0xxxx~0xFFFFF。

2. 分段位置区域模式为了克服实位置区域模式下1MB内存的局限性,8086引入了分段位置区域模式。

在分段位置区域模式下,8086通过段基址寄存器和偏移位置区域的组合来访问存储器,可以实现对更大容量的存储器进行访问。

3. 段基址寄存器在分段位置区域模式下,8086中的段基址寄存器包括CS(代码段寄存器)、DS(数据段寄存器)、ES(额外段寄存器)和SS(堆栈段寄存器),它们分别用来存放代码段、数据段、额外段和堆栈段的基址。

4. 偏移位置区域8086微处理器中,偏移位置区域用来表示段内的相对位置区域,它的范围为0~xxx。

5. 分段位置区域的形式在8086中,物理位置区域的计算方式为:物理位置区域=段基址×16+偏移位置区域。

通过这样的方式,8086可以实现对1MB范围内的存储器进行寻址。

二、 I/O端口的编址方式1. 端口编址方式8086微处理器通过端口编址方式来对I/O设备进行访问,I/O端口的位置区域空间范围为0~xxx。

2. IN指令和OUT指令8086微处理器提供了IN指令和OUT指令用于进行I/O端口的读写操作。

IN指令用于从指定端口读取数据,OUT指令用于向指定端口写入数据。

3. I/O端口位置区域的分配在8086系统中,I/O端口位置区域的分配由外围设备的制造商进行规划,保证不同的外围设备具有不同的端口位置区域,从而避免了位置区域冲突。

电动机正反转io分配表

电动机正反转io分配表

在设计 PLC 控制系统时,为了控制电动机的正反转,需要使用IO 地址分配表来分配 PLC 输入和输出信号。

以下是一个基本的电动机正反转 IO 地址分配表:

| 输入信号 | 输出信号 | IO 地址 |

|------|------------|--------|

| 电机正转 | 电机反转 | 10 |

| 电源接通 | 电源断开 | 11 |

| 限位开关 | 复位开关 | 12 |

| 急停开关 | 启动开关 | 13 |

| 温度传感器 | 温度报警器 | 14 |

| 计数器 | 计数清零 | 15 |

在这个表中,10、11、12、13 和 14 号端口是 PLC 的输入端口,用于监测电机正转、电机反转、电源接通、限位开关和急停开关等信号。

15 号端口是 PLC 的输出端口,用于控制电机的正反转。

此外,还需要绘制电动机正反转的 PLC 控制接线图和梯形图,以便在 PLC 内部传输和处理输入和输出信号。

在接线图中,需要将电动机的电源和控制线路与 PLC 的输入和输出端口进行连接。

在梯形图中,需要绘制 PLC 内部的控制逻辑,例如当输入信号满足特定条件时,如何触发输出信号来控制电机的正反转。

IO端口地址分配

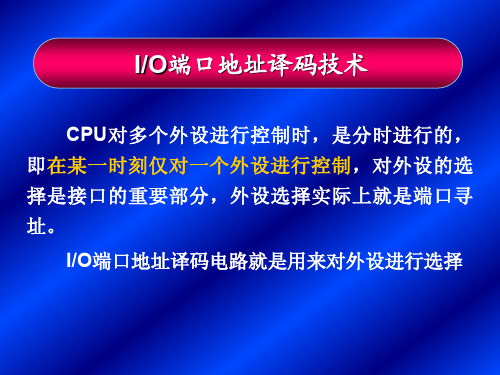

I/O端口地址译码技术

1

I/O端口及其编址方式

I/O端口访问—— CPU对I/O端口读/写。 通常所说的CPU从端口读数据或向端口写数 据仅仅是指I/O端口与CPU累加器之间的数据传送, 并未涉及数据是否传送到存储器(RAM)的问题。 当要求输入时,将端口的数据传送到存储器, 除了把数据读入CPU的累加器外,还要将累加器 中的数据再传送到内存。或者输出时,数据从存 储器先送到CPU的累加器,再从累加器传送到I/O 端口。

CPU对多个外设进行控制时,是分时进行的, 即在某一时刻仅对一个外设进行控制,对外设的选 择是接口的重要部分,外设选择实际上就是端口寻 址。 I/O端口地址译码电路就是用来对外设进行选择

1.

I/O端口及其编址方式

一、I/O端口和I/O操作

二、端口地址编址方式

三、独立编址方式的端口访问

1

I/O端口及其编址方式

15

1

I/O端口及其编址方式

2、间接方式 :

把端口地址放在DX寄存器中,对该端口进行读写 输入: IN AL, DX 输出: OUT DX, AL

当端口地址大于255时,采用该方式,且间址寄 存器只能用DX,最多可寻址216 =64K个端口。

18

2.

I/O端口地址分配

不同的微机系统其I/O端口地址的分配是不同的。 每一个外设都要占用一定的I/O地址空间。 要把新的I/O设备加入到系统中。 以IBM-PC系统为例来分析I/O端口地址分配情况。

S7-300的扩展及I-O地址分配

1.2 S7-300的扩展

S7-300是模块化的结构,S7-300 PLC由安装在导 轨上的模块集合而成。最多可以扩展3个导轨,最多可 带32个模块,扩展时每个导轨需要加连接模块。

1.3 S7-300的I/O地址分配

S7-300 原则上采用槽位与地址相对应的固定编址方式 每个槽位占4Byte(32bit),而不管实际的连接模块的I

/O点数是否与之相同,每个字节有8点

可编程控制器与现场总线网络控制

可编程控制器与现场总线网络控制

S7-300的扩展及I/O地址分配

1.1 S7-300 PLC的基本结构

一台S7-300 PLC基本单元由安装在专用导轨上 的各种模块化组成,模块可挂在导轨的上部, 下面用螺丝固定,导轨中的模块采用u形总线 的插头连接。

电源PS模块、CPU模块和接口模块IM在导轨上 的位置是固定的,顺次占1号、2号、3号槽, 其他模块(SM、FM、CP)在4号~11号槽之间 可以自由安排槽位

在连接模块时必须注意以下几点:

(1) CPU模块需要将电源模块的24V电源接入才 能工作,其他模块的接口也需要接入外部电源。

(2) 无3) 除电源PS模块、CPU模块和接口模块IM外, 基本单元的导轨上最多可以有8个连接模块。

(4) 如果一根导轨不够用,则需另加导轨进行 扩展,但有些S7-300的CPU(如CPU312、 CPU312IFM、CPU312C和CPU313等)只能用于单机 架。

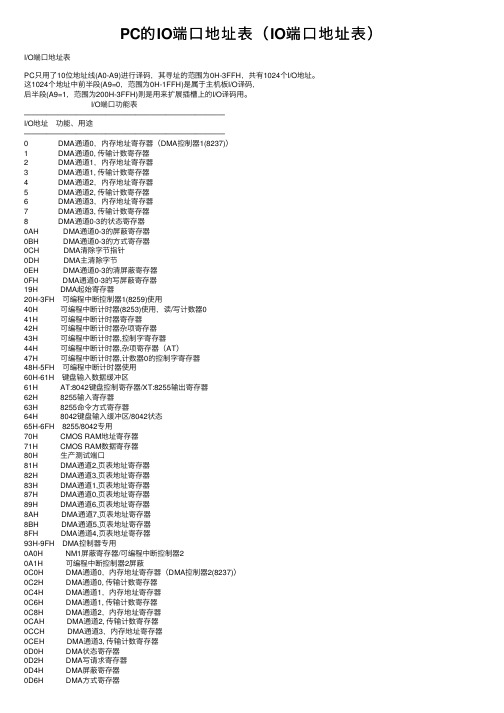

PC的IO端口地址表(IO端口地址表)

PC的IO端⼝地址表(IO端⼝地址表)I/O端⼝地址表PC只⽤了10位地址线(A0-A9)进⾏译码,其寻址的范围为0H-3FFH,共有1024个I/O地址。

这1024个地址中前半段(A9=0,范围为0H-1FFH)是属于主机板I/O译码,后半段(A9=1,范围为200H-3FFH)则是⽤来扩展插槽上的I/O译码⽤。

I/O端⼝功能表———————————————————————————I/O地址 功能、⽤途———————————————————————————0 DMA通道0,内存地址寄存器(DMA控制器1(8237))1 DMA通道0, 传输计数寄存器2 DMA通道1,内存地址寄存器3 DMA通道1, 传输计数寄存器4 DMA通道2,内存地址寄存器5 DMA通道2, 传输计数寄存器6 DMA通道3,内存地址寄存器7 DMA通道3, 传输计数寄存器8 DMA通道0-3的状态寄存器0AH DMA通道0-3的屏蔽寄存器0BH DMA通道0-3的⽅式寄存器0CH DMA清除字节指针0DH DMA主清除字节0EH DMA通道0-3的清屏蔽寄存器0FH DMA通道0-3的写屏蔽寄存器19H DMA起始寄存器20H-3FH 可编程中断控制器1(8259)使⽤40H 可编程中断计时器(8253)使⽤,读/写计数器041H 可编程中断计时器寄存器42H 可编程中断计时器杂项寄存器43H 可编程中断计时器,控制字寄存器44H 可编程中断计时器,杂项寄存器(AT)47H 可编程中断计时器,计数器0的控制字寄存器48H-5FH 可编程中断计时器使⽤60H-61H 键盘输⼊数据缓冲区61H AT:8042键盘控制寄存器/XT:8255输出寄存器62H 8255输⼊寄存器63H 8255命令⽅式寄存器64H 8042键盘输⼊缓冲区/8042状态65H-6FH 8255/8042专⽤70H CMOS RAM地址寄存器71H CMOS RAM数据寄存器80H ⽣产测试端⼝81H DMA通道2,页表地址寄存器82H DMA通道3,页表地址寄存器83H DMA通道1,页表地址寄存器87H DMA通道0,页表地址寄存器89H DMA通道6,页表地址寄存器8AH DMA通道7,页表地址寄存器8BH DMA通道5,页表地址寄存器8FH DMA通道4,页表地址寄存器93H-9FH DMA控制器专⽤0A0H NM1屏蔽寄存器/可编程中断控制器20A1H 可编程中断控制器2屏蔽0C0H DMA通道0,内存地址寄存器(DMA控制器2(8237))0C2H DMA通道0, 传输计数寄存器0C4H DMA通道1,内存地址寄存器0C6H DMA通道1, 传输计数寄存器0C8H DMA通道2,内存地址寄存器0CAH DMA通道2, 传输计数寄存器0CCH DMA通道3,内存地址寄存器0CEH DMA通道3, 传输计数寄存器0D0H DMA状态寄存器0D2H DMA写请求寄存器0D4H DMA屏蔽寄存器0D6H DMA⽅式寄存器0D8H DMA清除字节指针0DAH DMA主清0DCH DMA清屏蔽寄存器0DEH DMA写屏蔽寄存器0DFH-0EFH 保留0F0H-0FFH 协处理器使⽤100H-16FH保留170H 1号硬盘数据寄存器171H 1号硬盘错误寄存器172H 1号硬盘数据扇区计数173H 1号硬盘扇区数174H 1号硬盘柱⾯(低字节)175H 1号硬盘柱⾯(⾼字节)176H 1号硬盘驱动器/磁头寄存器177H 1号硬盘状态寄存器1F0H 0号硬盘数据寄存器1F1H 0号硬盘错误寄存器1F2H 0号硬盘数据扇区计数1F3H 0号硬盘扇区数1F4H 0号硬盘柱⾯(低字节)1F5H 0号硬盘柱⾯(⾼字节)1F6H 0号硬盘驱动器/磁头寄存器1F7H 0号硬盘状态寄存器1F9H-1FFH保留200H-20FH游戏控制端⼝210H-21FH扩展单元278H 3号并⾏⼝,数据端⼝279H 3号并⾏⼝,状态端⼝27AH 3号并⾏⼝,控制端⼝2B0H-2DFH保留2E0H EGA/VGA使⽤2E1H GPIP(0号适配器)2E2H 数据获取(0号适配器)2E3H 数据获取(1号适配器)2E4H-2F7H保留2F8H 2号串⾏⼝,发送/保持寄存器(RS232接⼝卡2) 2F9H 2号串⾏⼝,中断有效寄存器2FAH 2号串⾏⼝,中断ID寄存器2FBH 2号串⾏⼝,线控制寄存器2FCH 2号串⾏⼝,调制解调控制寄存器2FDH 2号串⾏⼝,线状态寄存器2FEH 2号串⾏⼝,调制解调状态寄存器2FFH 保留300H-31FH原形卡320H 硬盘适配器寄存器322H 硬盘适配器控制/状态寄存器324H 硬盘适配器提⽰/中断状态寄存器325H-347H保留348H-357H DCA3278366H-36FH PC⽹络372H 软盘适配器数据输出/状态寄存器375H-376H 软盘适配器数据寄存器377H 软盘适配器数据输⼊寄存器378H 2号并⾏⼝,数据端⼝379H 2号并⾏⼝,状态端⼝37AH 2号并⾏⼝,控制端⼝380H-38FH SDLC及BSC通讯390H-393H Cluster适配器03A0H-3AFH BSC通讯3B0H-3B H MDA视频寄存器3BCH 1号并⾏⼝,数据端⼝3BDH 1号并⾏⼝,状态端⼝3BEH 1号并⾏⼝,控制端⼝3C0H-3CFH EGA/VGA视频寄存器3D0H-3D7H CGA视频寄存器3F0H-3F7H 软盘控制器寄存器3F8H 1号串⾏⼝,发送/保持寄存器(RS232接⼝卡1) 3F9H 1号串⾏⼝,中断有效寄存器3FAH 1号串⾏⼝,中断ID寄存器3FBH 1号串⾏⼝,线控制寄存器3FCH 1号串⾏⼝,调制解调控制寄存器3FDH 1号串⾏⼝,线状态寄存器3FEH 1号串⾏⼝,调制解调状态寄存器3FFH 保留2.2.1 I/O端⼝和寻址2.2 I/O端⼝寻址和访问控制⽅式2.2.1 I/O端⼝和寻址CPU为了访问I/O接⼝控制器或控制卡上的数据和状态信息,需要⾸先指定它们的地址。

欧姆龙PLC的地址分配

欧姆龙PLC的地址分配————————————————————————————————作者: ————————————————————————————————日期:ﻩ欧姆龙PLC的地址分配欧姆龙PLC系统中的单元,根据前后位置或单元的特殊性,分别占用CIO区不同的地址,了解地址分配、知道输入、输出数据的具体存放位置,就能够利用编程对数据进行正确的处理。

第一讲欧姆龙PLC的地址分配在I/O存储器中,CPU单元和CP1W扩展单元的输入地址占用000 ~ 016通道,输出地址占用100 ~ 116通道,而1个通道就是我们所说的1个字,它也等于16个位,本篇我们以CP1H为例,来说明PLC地址分配的规律。

1、CPU单元地址分配X和XA型CPUX和XA型CPU单元自带40点I/O,其中输入24点,输出16点,在CIO区输入部分占用0 ~ 1通道,总共分配24个输入位:①其中12个位为0通道的位00 ~ 位11②另12个位为1通道的位00 ~ 位11③0通道和1通道中不使用的位12 ~ 位15,将始终被清除,且不可用作内部辅助工作位X和XA型CPU单元的输出16点,在CIO区输出部分占用100 ~ 101通道,总共分配16个输出位:①其中8个位为100通道的位00 ~ 位07②另8个位为101通道的位00~位07③100通道和101通道的位08 ~ 位15,可用作内部辅助工作位CP1H-XA型CPU中自带了模拟量输入和输出,其中4路模拟量输入占用200 ~ 203通道,2路模拟量输出占用210 ~ 211通道。

Y型CPUCP1H-Y型CPU中自带20点I/O,其中输入12点,输出8点,由于脉冲输入输出专用端子占用,输入输出被分配到不连续的地址:①所以Y型CPU单元的输入,占用CIO区0通道和1通道的共计12点②0通道和1通道中不使用的位12 ~ 位15,将始终被清除,且不可用作内部辅助工作位Y型CPU单元的输出8点,也是由于脉冲输入输出专用端子占用:①CPU单元的输出占用CIO区100通道和101通道的共计8点②100通道和101通道中不使用的位08 ~位15,可用作内部辅助工作位2、扩展单元地址分配扩展单元的作用是扩展输入、输出,扩展单元从CPU单元的分配通道之后的下一个通道开始,依次往后分配地址。

接口_第3章 IO端口地址译码技术

或

MOV DX, XXXXH OUT DX, AL OUT DX,AX

;8位传送(输出) ;16位传送(输出)

这里,XXXXH为16位的两字节地址。

2、I/O端口的寻址方式

I/O端口寻址有直接I/O端口寻址和间接I/O端口 寻址,其差别在I/O端口寻址是否经过DX传输。 例如:输入时 IN AL,0E0H ;直接寻址 MOV DX,300H ;间接寻址 IN AL,DX 例如:输出时 OUT 0E0H,AL ;直接寻址 MOV DX,300H ;间接寻址 OUT DX,AL

16位微处理器的I/O地址线是16位,实际上 只使用A0-A9地址线,地址线的选择应遵循下 列规则: 高位地址作为片间寻址,低位地址作为片 内寻址。 片内地址线数由接口中寄存器的数目决定。

2、I/O端口地址译码电路的输入与输出信号线

I/O地址译码电路的输入信号

I/O地址译码电路不仅仅与地址信号有关,而 且与控制信号有关。例如:

地址线 0 0 A 9 A8 A7 A6 A5 A4 A3 A 2 A1 A0

二进制

0

0 0

控制信号

0

C

B

A

? ? ? ? ?

片内地址

片选地址

地址范围在00H-0FFH区间的译码电路

开关式I/O地址译码电路设计

例:某微机系统的I/O空间为000H-3FFH,分成连 续的16段可选地址,每个段包括8个接口芯片, 每个接口芯片拥有8个端口。 分析:采用部分译码方法,允许16个段可以选择, 所以采用4位开关。

3.4

I/O端口地址分配及选用原则

第一章第二部分 端口地址及译码技术

3

2.独立编址 这种方式是接口中的端口单独编址而不占用 存储空间,大型计算机通常采用这种方式。有些 微机,如IBM-PC系列也采用这种方式。 这种方式的优点: ①专门的I/O指令对端口操作,可读性好, 指令短,执行速度快。 ②端口单独编址,不会与存储器地址相互混 淆。

4

三、独立编址方式的端口访问 通过I/O指令访问I/O端口 在汇编语言中有I/O指令。用于I/O端口与累加 器(AX、AL)之间的数据传送。 在I/O指令中有单字节地址或双字节地址寻址 方式。用单字节作为端口地址,则最多可访问 256(0~0FFH)个端口。若用双字节地址作为端口地 址,则最多可寻址216=64K个端口。 系统主板上的I/O端口,采用单字节地址。在 I/O扩展槽上的接口控制卡上,采用双字节地址。 I/O指令格式为; 输入 IN AX/AL,PORT/DX 输出 OUT PORT/DX,AX/AL 这里,PORT是一个8位的字节地址。

24

1.地址信号的分析与选择: ①PC机提供的用于I/O端口寻址的地址信号是: A9A8A7A6A5A4A3A2A1A0,共10位。 系统板上A9A8=00

②片内需寻址32个口,共需要低位地址线5根,选 A4A3A2A1A0 ③选A7A6A5作为译码器译码输入信号。

25

2.控制信号的选择

用AEN信号来禁止译码电路在DMA方式下工作。 非DMA操作时AEN=0, DMA操作时AEN=1。

②用A4A3A2信号作为译码输入信号并采用3-8译码器 就能获得8个不同的片选信号,实现在扩展板上对8个 接口芯片的片选。

③地址线A9A8A7A6A5可作为改变地址范围所需的信 号。 31

2. 地址范围可选的处理实现分析:

本例中要求的地址范围可选的含义是:该接口电 路设计成功后,既能用于地址范围300H~31FH,也 能用于其它地址范围,如:200H~21FH。 具体做法是: 把高4位A9A8A7A6接入比较器的A输入端,B输 入端通过开关DIP接入四个预定的输入信号,若二者 相等就会产生FA=B=1信号。并把它作为译码器的G1信 号来控制3-8译码器工作。 本例把DIP接入的信号定为:B3B2B1B0=1100, 这就保证只有在A9A8A7A6=1100时译码器才能工作 。假如需要的地址范围是200H~21FH,那么,就只 要把DIP的接入信号拨定为B3B2B1B0=1000即可。

微机接口技术-第3章IO端口地址译码技术

内存 内存接口

系统总线:地址总线XA19-0,数据总线XD7-0,控制总线/XIOR ……

智能仪器接口 通信接口 过程控制接口 输入接口

输出接口

外存接口

数字化存储示 波器,数字化

万用表

终端 调制解调器 TTY 电传机

A/D转换器 开关量输入 D/A转换器 开关量输出

键盘 数字化仪 点阵打印 CRT 显示

么?

思考:在PC机上设计接口,你设计的接口IO地址必须不能与其他设备 接口IO地址冲突,你能想到用什么办法解决这个问题?

方案一:先查PC机硬件说明书,看那些IO 地址已经被占用。

缺点是麻烦,且非PC机器厂家生产的设备 (如扩展接口卡)地址,必须通过查该卡

说明书才能了解它占用的IO地址。

不可能!!你怎么知道你的卡被客户装在 哪台机器上?客户计算机上装了哪些其它 厂家的卡,你怎么能预先知道呢?客户买

Y X 9X A 8 X A 7 X A 6 X A 5 X A 4 X A 3X A 2 A X 1 X A 0 X AX I O A XA9 XA8 XA7 XA6 XA5 XA4 XA3 XA2

/+Y

例2。 使用74LS138设计一个系统板上IO端口地址译码电路,并且让每个接口芯片内部 可以有32个端口,非DMA期间可以访问接口芯片。

分析:输入 XA9-5,XAEN。因为低5位地址用来选中芯片内部端口,不作为外部译码器 的输入。一片138只能译码3位地址,这里用138对XA7-XA5译码。

输出 8个芯片选中信号/Y0-/Y7。 逻辑关系:XAEN=0,XA9XA8=00时,使译码器工作。 XA7-XA5=000时,输出/Y0=0, 其余全无效为1。 XA7-XA5=001时,输出/Y1=0, 其余全无效为1 XA7-XA5=010时,输出/Y2=0, 其余全无效为1 ……

零点远程io模块io点分配问题

零点远程IO模块IO点分配问题随着信息技术的不断发展,远程监控与控制系统在各个领域得到了广泛的应用。

在这些系统中,IO模块的IO点分配问题是一个关键的技术挑战。

本文将围绕这一问题展开讨论,从IO模块的基本原理、IO 点的分配方法以及常见的应用场景等方面进行阐述。

一、IO模块的基本原理1. IO模块的作用IO模块是远程监控与控制系统中的重要组成部分,其作用是将外部的数字或模拟信号转换成数字信号,以便与上位机进行通信。

IO模块还可以将上位机下发的指令转换成对外部设备的控制信号。

2. IO模块的结构典型的IO模块包括输入端和输出端两部分。

输入端接收外部信号,经过电路处理后输出到上位机;输出端则接收上位机的指令信号,经过处理后输出到外部设备。

3. IO模块的工作原理IO模块在工作时,需要完成信号的转换、处理和传输等功能。

其内部一般由信号输入接口、采集处理电路、通信接口和输出接口等模块组成。

二、IO点的分配方法1. 静态IO点分配静态IO点分配是指在系统设计阶段就确定好各个IO点的分配关系。

这种方法简单直接,适用于IO点数量较少、不会频繁变动的场景。

2. 动态IO点分配动态IO点分配是指系统在运行时根据需要动态进行IO点的分配。

这种方法灵活性较强,能够适应IO点数量较多、需求频繁变动的应用环境。

3. 混合IO点分配混合IO点分配是指将静态IO点分配和动态IO点分配相结合的方法。

在实际应用中,可以根据具体情况灵活选择静态或动态IO点分配,以满足系统的实际需求。

三、常见的应用场景1. 工业自动化在工业自动化领域,IO模块的IO点分配对整个生产过程起着至关重要的作用。

通过合理的IO点分配,可以实现对生产设备的远程监控和控制,提高生产效率和产品质量。

2. 智能建筑智能建筑系统中的IO模块通常需要对大量的传感器和执行器进行接口。

合理的IO点分配可以实现对建筑内部环境的监控和调节,提高能源利用效率和居住舒适度。

3. 物联网在物联网应用中,IO模块的IO点分配直接关系到设备间的信息交互和协同工作。

IO端口的编址方式

I/O端口的编址方式

I/O端口的编址方式有两种,即独立编址和统一编址。

1.独立编址(专用的I/O端口编址)----存储器和I/O端口在两个独立的地址空间中

(1)优点:I/O端口的地址码较短,译码电路简单,存储器同I/O端口的操作指令不同,程序比较清晰;存储器和I/O端口的控制结构相互独立,可以分别设计

(2)缺点:需要有专用的I/O指令,程序设计的灵活性较差

2.统一编址(存储器映像编址)----存储器和I/O端口共用统一的地址空间,当一个地址空间分配给I/O端口以后,存储器就不能再占有这一部分的地址空间

(1)优点:不需要专用的I/O指令,任何对存储器数据进行操作的指令都可用于I/O端口的数据操作,程序设计比较灵活;由于I/O端口的地址空间是内存空间的一部分,这样,I/O端口的地址空间可大可小,从而使外设的数量几乎不受限制

(2)缺点:I/O端口占用了内存空间的一部分,影响了系统的内存容量;访问I/O端口也要同访问内存一样,由于内存地址较长,导致执行时间增加

使用ISA汇流排结构的传统PC机其I/O位址空间范围是0x000--0x3FF,有1024个I/O端口位址可供使用

对於使用EISA或PCI等汇流排结构的现代PC机,有64KB的I/O位址空间可供使用。

在普通Linux 系统下透过查看/proc/ioports-(对应的I/O口),可以得到相关控制器或设置使用的I/O位址范围。

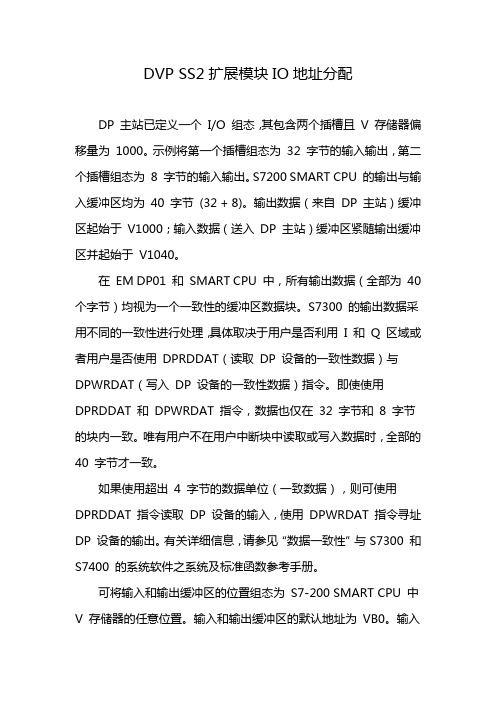

DVP SS2扩展模块IO地址分配

DVP SS2扩展模块IO地址分配DP 主站已定义一个I/O 组态,其包含两个插槽且V 存储器偏移量为1000。

示例将第一个插槽组态为32 字节的输入输出,第二个插槽组态为8 字节的输入输出。

S7200 SMART CPU 的输出与输入缓冲区均为40 字节(32 + 8)。

输出数据(来自DP 主站)缓冲区起始于V1000;输入数据(送入DP 主站)缓冲区紧随输出缓冲区并起始于V1040。

在EM DP01 和SMART CPU 中,所有输出数据(全部为40 个字节)均视为一个一致性的缓冲区数据块。

S7300 的输出数据采用不同的一致性进行处理,具体取决于用户是否利用I 和Q 区域或者用户是否使用DPRDDAT(读取DP 设备的一致性数据)与DPWRDAT(写入DP 设备的一致性数据)指令。

即使使用DPRDDAT 和DPWRDAT 指令,数据也仅在32 字节和8 字节的块内一致。

唯有用户不在用户中断块中读取或写入数据时,全部的40 字节才一致。

如果使用超出4 字节的数据单位(一致数据),则可使用DPRDDAT 指令读取DP 设备的输入,使用DPWRDAT 指令寻址DP 设备的输出。

有关详细信息,请参见“数据一致性”与 S7300 和S7400 的系统软件之系统及标准函数参考手册。

可将输入和输出缓冲区的位置组态为S7-200 SMART CPU 中V 存储器的任意位置。

输入和输出缓冲区的默认地址为VB0。

输入输出缓冲区的位置是DP 主站写入S7-200 SMART CPU 的参数分配信息的一部分。

用户需要组态DP 主站以识别DP 设备并将所需参数和I/O 组态写入主站的每个DP 设备。

使用STEP 7 编程软件组态SIMATIC S7 DP 主站。

有关使用组态和编程软件包的详细信息,请参见这些设备的手册。

有关PROFIBUS 网络及其组件的详细信息,请参见 ET 200 分布式I/O 系统手册。

10-IO地址译码技术

(Port) Acc=AL,AX或EAX

间接输出(变量)

输入字节串 输入字串 输入双字串

OUT DX, Acc

INSB INSW INSD

(ES:DI) (ES:DI) (ES:DI)

(Acc)

((DX)) ((DX)) ((DX))

((DX))

E(DI) E(DI) E(DI) E(DI) ±1 E(DI) ±2 E(DI) ±4

9

表 系统板上接口芯片的端口地址 I/O芯片名称 DMA控制器1 DMA控制器2 DMA页面寄存器 中断控制器1 中断控制器2 定时器 并行接口芯片(键盘接口) RT/CMOS RAM 协处理器

10.1

I/O端口及其编址方式

端口地址 200~20FH 370~37FH 270~27FH 3F8~3FFH 2F0~2FFH 300~31FH 3A0~3AFH 380~38FH 3B0~3BFFH 3D0~3DFH 3C0~3CFH 1F0~1FFH 3F0~23F7H 360~36FH

2) 扩展槽上的I / O接口控制卡。 由若干个集成电路按一定的逻辑功能组成的接口部件 例:图形卡、声卡、网卡 端口地址:后768个端口(100~3FFH) 16位地址

8

10.1

I/O端口及其编址方式

端口地址 000~01FH 0C0~0DFH 080~09FH 020~03FH 0A0~0BFH 040~05FH 060~06FH 070~07FH 0F0~0FFH

表 扩展槽上接口控制卡的端口地址

I/O接口名称 游戏控制卡 并行口控制卡1 并行口控制卡2 串行口控制卡1 串行口控制卡2 原型插件板(用户可用) 同步通信卡1 同步通信卡2 单显MDA 彩显CGA 彩显EGA/VGA 硬驱控制卡 软驱控制卡 PC网卡

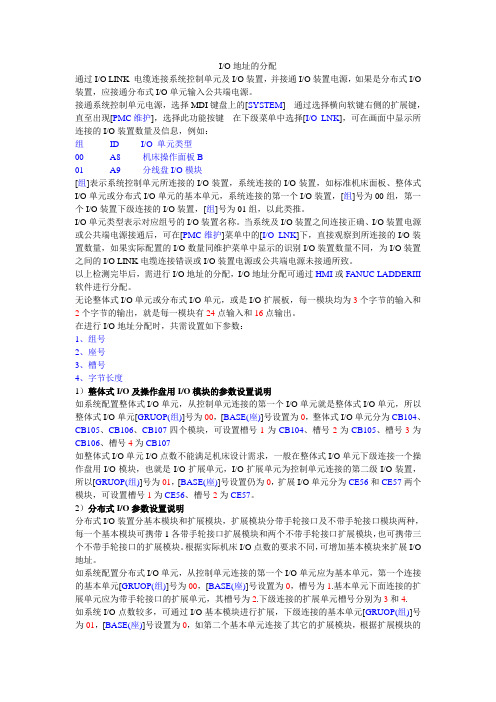

8、IO地址的分配

I/O地址的分配通过I/O LINK 电缆连接系统控制单元及I/O装置,并接通I/O装置电源,如果是分布式I/O 装置,应接通分布式I/O单元输入公共端电源。

接通系统控制单元电源,选择MDI键盘上的[SYSTEM]---通过选择横向软键右侧的扩展键,直至出现[PMC维护],选择此功能按键---在下级菜单中选择[I/O LNK],可在画面中显示所连接的I/O装置数量及信息,例如:组ID I/O 单元类型00 A8 机床操作面板B01 A9 分线盘I/O模块[组]表示系统控制单元所连接的I/O装置,系统连接的I/O装置,如标准机床面板、整体式I/O单元或分布式I/O单元的基本单元,系统连接的第一个I/O装置,[组]号为00组,第一个I/O装置下级连接的I/O装置,[组]号为01组,以此类推。

I/O单元类型表示对应组号的I/O装置名称。

当系统及I/O装置之间连接正确、I/O装置电源或公共端电源接通后,可在[PMC维护]菜单中的[I/O LNK]下,直接观察到所连接的I/O装置数量,如果实际配置的I/O数量同维护菜单中显示的识别I/O装置数量不同,为I/O装置之间的I/O LINK电缆连接错误或I/O装置电源或公共端电源未接通所致。

以上检测完毕后,需进行I/O地址的分配,I/O地址分配可通过HMI或FANUC LADDERIII 软件进行分配。

无论整体式I/O单元或分布式I/O单元,或是I/O扩展板,每一模块均为3个字节的输入和2个字节的输出,就是每一模块有24点输入和16点输出。

在进行I/O地址分配时,共需设置如下参数:1、组号2、座号3、槽号4、字节长度1)整体式I/O及操作盘用I/O模块的参数设置说明如系统配置整体式I/O单元,从控制单元连接的第一个I/O单元就是整体式I/O单元,所以整体式I/O单元[GRUOP(组)]号为00,[BASE(座)]号设置为0,整体式I/O单元分为CB104、CB105、CB106、CB107四个模块,可设置槽号1为CB104、槽号2为CB105、槽号3为CB106、槽号4为CB107如整体式I/O单元I/O点数不能满足机床设计需求,一般在整体式I/O单元下级连接一个操作盘用I/O模块,也就是I/O扩展单元,I/O扩展单元为控制单元连接的第二级I/O装置,所以[GRUOP(组)]号为01,[BASE(座)]号设置仍为0,扩展I/O单元分为CE56和CE57两个模块,可设置槽号1为CE56、槽号2为CE57。

第05章IO接口

举例

IN AL, 60H ;8位输 入指令 IN AX, 78H ;16位输 入指令 MOV DX, 312H ;端口 地址送DX IN AX, DX ;16位间 接输入指令

功能

把指定端口中 的数据读入AL 或AX中

IN ACC, DX

AL/AX ← (DX)

OUT ACC OUT ACC

PORT, DX,

图5-4 输出锁存电路

简单的输入/输出接口(图5-5)

• • 把地址译码、数据锁存与缓冲、状态寄存器、命令寄 存器各个电路组合起来,构成简单输入/输出接口 接口连接的信号: – 与系统总线连接:

地址总线A0~A15 数据总线D0~D7 控制总线M/IO#、RD# 、WR# (最小模式时)或 IOWC#、IORC#(最大模式时)相连接

高电平(无效):缓冲器输出端呈高阻态。 低电平(有效,端口被选中 ):已锁存的数据通过 74LS244送往系统数据总线,被CPU所接收。

图5-3 输入设备接口的数据锁存和缓冲电路

数据(命令)输出端口:

•

CPU送往外设的数据或命令,应由接口进行锁存, 以便使外设有充分的时间接收和处理。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

PC机I/O端口地址分配

29

2. I/O端口地址分配

PC机I/O端口地址分配

30

2. I/O端口地址分配

PC机I/O端口地址分配

2. I/O端口地址分配

PC机I/O端口地址分配

32

2. I/O端口地址分配

PC机I/O端口地址分配

33

2. I/O端口地址分配

PC机I/O端口地址分配

34

2. I/O端口地址分配

1

I/O端口及其编址方式

CPU给每个寄存器分配了一个地址(端 口)。 CPU在访问这些寄存器时,只需指明它 们的端口,不需指出是什么寄存器。 CPU在控制I/O设备时,只需指明与该设 备相关的端口 。 通常所说的I/O操作,是对I/O端口的操 作,而不是对I/O设备的操作,即CPU所访 问的是与I/O设备相关的端口,而不是I/O 设备本身。

I/O端口地址译码技术

CPU对多个外设进行控制时,是分时进行的, 即在某一时刻仅对一个外设进行控制,对外设的选 择是接口的重要部分,外设选择实际上就是端口寻 址。 I/O端口地址译码电路就是用来对外设进行选择

1.

I/O端口及其编址方式

一、I/O端口和I/O操作

二、端口地址编址方式

三、独立编址方式的端口访问

25

2. I/O端口地址分配

PC机I/O端口地址分配 如何了解微机系统中已经使用了哪些端口地址?

可以通过Windows系统中“控制面板”中的系 统程序查看I/O端口的分配。

26

2. I/O端口地址分配

PC机I/O端口地址分配

27

2. I/O端口地址分配

PC机I/O端口地址分配

28

2. I/O端口地址分配

PC机I/O端口地址分配

35

2. I/O端口地址分配

PC机I/O端口地址分配

36

2. I/O端口地址分配

三、I/O端口地址选用的原则 1、凡是被系统配置两个占用了的地址,和

已保留的地址不能使用。 2、可使用300~31FH地址,是IBM-PC留作 实验卡用的,用户可以使用。

37

3.

I/O端口地址译码

23

2. I/O端口地址分配

二、I/O端口地址分配 PC机的I/O地址线只用了低10根A9~A0 (高6位未用)。 故地此范围0000H~03FFH

(210=1024=1K个端口)

24

2. I/O端口地址分配

PC机I/O端口地址分配

在Intel系列微机系统中采用I/O独立编址方式。I/O操作 只使用20根地址线中的16根A15~A0,可寻址的I/O端口 数为64K(65536)个。 I/O地址范围为0000H~FFFFH。在 IBM-PC机中只使用了1024个I/O端口地址(0~3FFH)。 在目前的微型计算机系统中,系统为主板保留了1024 个端口,分配了最低端的1024个地址(0000H~03FFH)。 1K以上的地址(0400H~FFFFH)作为用户扩展使用。用户 在设计扩展接口时,应注意不能使用系统已经占用的地址。

1

I/O端口及其编址方式

3)使用专门的信号来区分CPU是访问存储器 地址总线上是一个有 还是访问I/O端口。

效的I/O端口地址

8086CPU用 M/IO

{

IN,OUT指令时,M/IO=0 执行访问内存指令时,M/IO=1

地址总线上传送的是一 个访问内存的地址

4)I/O端口地址和存储器地址可以重叠, 不会混淆。

15

1

I/O端口及其编址方式

2、间接方式 :

把端口地址放在DX寄存器中,对该端口进行读写 输入: IN AL, DX 输出: OUT DX, AL

当端口地址大于255时,采用该方式,且间址寄 存器只能用DX,最多可寻址216 =64K个端口。

18

2.

I/O端口地址分配

不同的微机系统其I/O端口地址的分配是不同的。 每一个外设都要占用一定的I/O地址空间。 要把新的I/O设备加入到系统中。 以IBM-PC系统为例来分析I/O端口地址分配情况。

22Leabharlann 2.I/O端口地址分配

一、I/O接口硬件分类

分两类: 1、系统板上的I/O芯片:大多数是可编程的大规 模集成电路,如定时/计数器,中断控制器,DMA控 制器,并行接口等。 2、I/O扩展槽上的接口控制卡,由若干个集成电路 按一定的逻辑组成的一个部件,如软驱卡、硬驱卡、 图形卡、声卡、串行通信卡等。

FFFFH

IBM PC 系列,Intel 80x86 系列微机 Z80 系列机、大型机

I/O端口地址空间不占用存储器地址空间, 二者的地址空间相互独立完全分开,两者各自有一套独立的地址空间,相互 不会影响。

存储器 FFFFFH 以80x86为例

Port 65535

PC系列机采用独立编址方式

Port 255

将来自于地址总线上的地址代码翻译为所 需要访问的端口(寄存器)

一、I/O地址译码电路工作原理及作用 二、I/O地址译码方法 三、I/O端口地址译码电路设计

38

补充: 常用逻辑符号

名称 非门 或门 与门 或非门 与非门 异或门 异或非门

国外流行符号

A A B A B A B Y Y Y Y

国标符号

1

分为(I/O指令中端口地址的宽度): 直接方式(单字节地址) 间接方式(双字节地址)。

1

I/O端口及其编址方式

输入指令完成外设数据输入 IN AL, PORT (字节输入) 直接 IN AX, PORT (字输入) IN AL, DX (字节输入) 间接 IN AX, DX (字输入) 输出指令完成外设数据输出 OUT PORT, AL (字节输出) 直接 OUT PORT, AX (字输出) (字节输出) 间接 OUT DX, AL OUT DX, AX (字输出)

1

I/O端口及其编址方式

3)能给I/O端口有较大的编址空间,这对大型控 制系统和数据通信系统是很有意义的。

缺点:

• 端口占用了存储器的地址空间,使存储器容量减小。 • 指令长度比专门I/O指令要长,执行时间较长,降低 了数据交换速度,I/O程序不易读。

1

I/O端口及其编址方式

2、独立编址

{

I/O端口

≥1

表达式 Y=A Y=A+B Y=A•B Y=A+B

&

≥1

A B

A B A B

Y

Y

&

=1 =1

Y=A•B

Y=A + B Y=A + B

43

Y

●

CPU给每个寄存器分配了一个地址

● CPU在访问这些寄存器时,只需指明它们的端口

●

CPU在控制I/O设备时,只需指明与该设备相关的端口

1

I/O端口及其编址方式

I/O端口访问—— CPU对I/O端口读/写。 通常所说的CPU从端口读数据或向端口写数 据仅仅是指I/O端口与CPU累加器之间的数据传送, 并未涉及数据是否传送到存储器(RAM)的问题。 当要求输入时,将端口的数据传送到存储器, 除了把数据读入CPU的累加器外,还要将累加器 中的数据再传送到内存。或者输出时,数据从存 储器先送到CPU的累加器,再从累加器传送到I/O 端口。

07FFFH

00000H

0000H

1MB

Port 3 Port 2 Port 1 Port 0 64KB

Port 1(16位) Port 0 (32位) Port 0(16位)

1

I/O端口及其编址方式

特点 1)端口地址不占用存储器空间,需独立的I/O 端口地址 译码电路选取I/O端口。 2)需要用专门的I/O指令(IN,OUT)对端口进行操 作,I/O指令短,执行速度快。由于I/O指令和存储 器访问指令有明显的区别,从而使I/O程序便于阅 读,层次清晰。

1

I/O端口及其编址方式

一、I/O端口和I/O操作

端口(port)是接口电路中能被CPU直接访问 的寄存器的地址。 CPU通过这些地址(端口)向接口电路中的寄 存器发送命令、读取状态和传送数据。 一个接口可以有几个端口

{

命令口(命令寄存器)--------写口 状态口(状态寄存器)--------读口 数据口(数据寄存器)--------读、写

1

I/O端口及其编址方式 统一编址:

FFFFFH

存储器

Port 65535

总共1M字节

I/O与存储器单元 在同一地址空间

其中64K个I/O端口

I/O

F0000H EFFFFH

Port 3 Port 2 Port 1 Port 0

M

00000H

1

I/O端口及其编址方式

优点:

1)不需设置专门的I/O指令,凡对存储器可使用的 指令(即所有访问内存指令)均可用于对端口 的访问,不需要单独的I/O 端口地址译码电路。 2)可采用丰富的访存指令操作I/O单元。由于访问 内存指令类型多、功能齐全,用这些指令访问 I/O设备,不仅使输入/输出操作灵活、方便,而 且还可直接对端口内容进一步进行算术逻辑运算、 移位等。

1

I/O端口及其编址方式

端口地址是一种重要资源

PC机I/O端口地址分配

1

I/O端口及其编址方式

二. 端口地址编址方式

1、统一编址(存储器映射方式)

{

Motorola68、 65系列 Apple系列、 小型机

将存储器空间划出一部分给I/O设备,把I/O接口中的 每一个接口当作存储单元一样进行访问,每一个端口占用 一个存储单元地址。

缺点:I/O指令功能简单、类型少,使I/O操作受到 限制,要用专门信号区分访问内存还是访问I/O端 口。