杭电计组实验8-实现R型指令的CPU设计实验

计算机组成原理实验报告 单周期CPU的设计与实现

1个时钟周期 Clock 电子科技大学计算机科学与工程学院标 准 实 验 报 告(实验)课程名称: 计算机组成原理实验 电子科技大学教务处制表电 子 科 技 大 学 实 验 报 告学生姓名: 郫县尼克杨 学 号: 2014 指导教师:陈虹 实验地点: 主楼A2-411 实验时间:12周-15周一、 实验室名称:主楼A2-411二、 实验项目名称:单周期CPU 的设计与实现。

三、 实验学时:8学时四、 实验原理:(一) 概述单周期(Single Cycle )CPU 是指CPU 从取出1条指令到执行完该指令只需1个时钟周期。

一条指令的执行过程包括:取指令→分析指令→取操作数→执行指令→保存结果。

对于单周期CPU 来说,这些执行步骤均在一个时钟周期内完成。

(二) 单周期cpu 总体电路本实验所设计的单周期CPU 的总体电路结构如下。

(三) MIPS 指令格式化MIPS 指令系统结构有MIPS-32和MIPS-64两种。

本实验的MIPS 指令选用MIPS-32。

以下所说的MIPS 指令均指MIPS-32。

MIPS 的指令格式为32位。

下图给出MIPS 指令的3种格式。

本实验只选取了9条典型的MIPS 指令来描述CPU 逻辑电路的设计方法。

下图列出了本实验的所涉及到的9条MIPS 指令。

五、 实验目的1、掌握单周期CPU 的工作原理、实现方法及其组成部件的原理和设计方法,如控制器、运算器等。

?2、认识和掌握指令与CPU 的关系、指令的执行过程。

?3、熟练使用硬件描述语言Verilog 、EDA 工具软件进行软件设计与仿真,以培养学生的分析和设计CPU 的能力。

六、 实验内容(一)拟定本实验的指令系统,指令应包含R 型指令、I 型指令和J 型指令,指令数为9条。

(二)CPU 各功能模块的设计与实现。

(三)对设计的各个模块的仿真测试。

(四)整个CPU 的封装与测试。

七、 实验器材(设备、元器件):(一)安装了Xilinx ISE Design Suite 13.4的PC 机一台(二)FPGA 开发板:Anvyl Spartan6/XC6SLX45(三)计算机与FPGA 开发板通过JTAG (Joint Test Action Group )接口连接,其连接方式如图所示。

杭电计算机组成原理寄存器堆设计实验

杭电计算机组成原理寄存器堆设计实验计算机组成原理是计算机科学与技术的基础课程之一,它涉及到计算机的基本组成部分和原理。

在这门课程中,学生通常需要进行一系列的实验来加深对计算机组成原理的理解和应用。

其中之一是关于寄存器堆的设计实验。

寄存器堆是计算机中重要的组成部分之一,它用于存储、读取和写入数据。

在计算机中,数据通常被存储在寄存器中,然后进行各种操作。

因此,设计一个高效可靠的寄存器堆对于计算机的性能至关重要。

根据实验要求,我们需要设计一个8位的寄存器堆,并实现读取、写入和清零等操作。

以下是针对该实验的设计思路和实施步骤。

首先,我们需要确定寄存器堆的结构。

由于该寄存器堆为8位宽度,我们选择使用一个8x8的存储单元阵列。

每个存储单元都可以存储一个8位的数据。

整个寄存器堆由8个存储单元组成,每个存储单元对应一个地址,即0~7接下来,我们需要设计寄存器堆的读写电路。

对于读操作,我们需要通过地址线来选择要读取的存储单元,并将其输出到数据线。

对于写操作,我们同样需要通过地址线来选择要写入的存储单元,并将数据线上的数据写入该存储单元。

为了实现这些操作,我们需要使用多路选择器和数据解码器。

在设计中,我们还需要考虑到时钟信号的输入,以确保读写操作在时钟的上升沿或下降沿进行。

此外,我们还需要添加清零功能,以便将寄存器堆的值重置为零。

为实现清零功能,我们可以将一个额外的输入线与所有存储单元的清零输入连接。

在实施阶段,我们需要使用Verilog或其他硬件描述语言来实现设计。

在代码中,我们首先声明一个8位宽的存储单元阵列作为寄存器堆的基本组成部分。

然后,我们定义读写电路,包括地址线、数据线、多路选择器和数据解码器。

最后,我们添加时钟信号和清零功能。

在完成设计后,我们可以通过仿真工具进行验证。

通过输入不同的数据和地址,观察输出结果是否符合预期。

如果存在问题,我们可以进行调试并进行必要的修改。

一旦仿真结果正确无误,我们就可以开始进行硬件实验了。

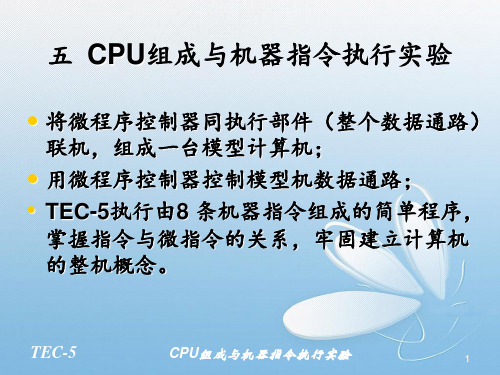

cpu组成与机器指令执行实验实验报告

cpu组成与机器指令执行实验实验报告CPU组成与机器指令执行实验实验报告一、引言计算机是现代社会不可或缺的工具,而中央处理器(CPU)则是计算机的核心组成部分。

理解CPU的组成和机器指令的执行过程对于深入理解计算机的工作原理至关重要。

本实验旨在通过搭建一个简单的CPU模型,探究CPU的组成结构和机器指令的执行过程。

二、实验原理1. CPU的组成结构CPU主要由运算器、控制器和寄存器组成。

运算器负责进行各种算术和逻辑运算,控制器则负责指挥各个部件的工作,寄存器用于存储数据和指令。

2. 机器指令的执行过程机器指令的执行包括取指令、译码、执行和访存四个阶段。

取指令阶段从内存中读取指令,译码阶段将指令翻译成对应的操作,执行阶段进行运算或逻辑操作,访存阶段用于读取或写入数据。

三、实验过程1. 搭建CPU模型根据实验要求,我们搭建了一个简单的CPU模型,包括运算器、控制器和寄存器。

通过将这些部件连接起来,我们可以模拟CPU的工作过程。

2. 编写指令为了测试CPU的功能,我们编写了一些简单的指令,包括加法、减法和逻辑运算等。

这些指令将被存储在内存中,CPU在执行过程中会逐条读取并执行。

3. 执行指令我们按照预定的顺序执行指令,观察CPU的工作状态和输出结果。

通过这个过程,我们可以更好地理解指令的执行过程和CPU的工作原理。

四、实验结果在实验过程中,我们成功搭建了一个简单的CPU模型,并编写了一些指令进行测试。

通过执行这些指令,我们观察到CPU按照预期工作,并得到了正确的输出结果。

五、实验分析通过本次实验,我们深入了解了CPU的组成结构和机器指令的执行过程。

我们发现,CPU的运算器、控制器和寄存器相互配合,完成了复杂的运算和逻辑操作。

同时,我们也注意到指令的执行过程需要经过多个阶段,每个阶段都起到了重要的作用。

六、实验总结本次实验让我们对CPU的组成与机器指令的执行有了更深入的理解。

通过搭建CPU模型并执行指令,我们亲身体验了CPU的工作过程,加深了对计算机原理的理解。

电子科技大学CPU设计:《单周期CPU的设计与实现》-实验指导书

电子科技大学计算机科学与工程学院单周期CPU的设计与实现实验指导书[计算机组成原理实验]张建2013-12-13目录前言 (1)1.1 实验内容 (2)1.2实验要求 (2)2. 实验环境 (3)2.1 硬件平台 (3)2.2 软件平台 (3)2.3 实验主要仪器设备连接框图 (4)3. 实验原理 (5)3.1 概述 (5)3.2 单周期CPU的总体电路 (5)3.3 MIPS指令格式 (6)3.4 数据路径设计 (7)3.4.1 下一条指令地址的选择 (7)3.4.2 ALU的输入端 (8)3.4.3寄存器堆的输入端 (8)4. 基本功能部件的设计与实现 (10)4.1 32位2选1选择器的设计与实现 (10)4.2 32位4选1选择器的设计与实现 (18)4.3 5位2选1选择器的设计与实现 (19)4.4 带有异步清零的32位D触发器的设计与实现 (19)4.5 移位器的设计 (20)4.6 32位加/减法器的设计与实现 (20)5.运算器(ALU)的设计与实现 (21)6.寄存器堆(Register File)的设计与实现 (24)7.控制器(Control Unit)的设计与实现 (27)8. CPU的封装 (30)9. 测试 (32)9.1 指令存储器及测试程序 (32)9.2 数据存储器及测试数据 (33)9.3 仿真测试 (33)9.4 下载到开发板验证 (35)附件: (39)BTN_Anti_Jitter模块 (39)Hex7seg_decode模块 (39)前言《计算机组成原理》是计算机科学专业的一门重要专业基础课。

在该课程中的理论学习中系统地阐述了计算机各组成部件的工作原理、逻辑实现和设计方法及将各部件连接成整机的方法,计算机硬件与底层软件的接口,培养了学生对计算机硬件系统的分析、开发与设计的基本技能能力。

本实验开设的目的是让学生通过设计一个单周期的CPU,加深对计算机各组成部件功能的理解和掌握,更好地理解计算机的基本工作原理,培养和锻炼学生掌握计算机硬件设计的基本方法和技能。

计组实验报告(共10篇)

计组实验报告(共10篇)计组实验报告计算机组成原理实验报告一一、算术逻辑运算器1. 实验目的与要求:目的:①掌握算术逻辑运算器单元ALU(74LS181)的工作原理。

②掌握简单运算器的数据传输通道。

③验算由74LS181等组合逻辑电路组成的运输功能发生器运输功能。

④能够按给定数据,完成实验指定的算术/逻辑运算。

要求:完成实验接线和所有练习题操作。

实验前,要求做好实验预习,掌握运算器的数据传送通道和ALU 的特性,并熟悉本实验中所用的模拟开关的作用和使用方法。

实验过程中,要认真进行实验操作,仔细思考实验有关的内容,把自己想得不太明白的问题通过实验去理解清楚,争取得到最好的实验结果,达到预期的实验教学目的。

实验完成后,要求每个学生写出实验报告。

2. 实验方案:1.两片74LS181(每片4位)以并/串联形式构成字长为8为的运算器。

2.8为运算器的输出经过一个输入双向三态门(74LS245)与数据总线相连,运算器的两个数据输入端分别与两个8位寄存器(74LS273)DR1和DR2的输出端相连,DR1和DR2寄存器是用于保存参加运算的数据和运算的结果。

寄存器的输入端于数据总线相连。

3.8位数据D7~D0(在“INPUT DEVICE”中)用来产生参与运算的数据,并经过一个输出三态门(74LS245)与数据总线相连。

数据显示灯(BUS UNIT)已与数据总线相连,用来显示数据总线上所内容。

4.S3、S2、S1、S0是运算选择控制端,由它们决定运算器执行哪一种运算(16种算术运算或16种逻辑运算)。

5.M是算术/逻辑运算选择,M=0时,执行算术运算,M=1时,执行逻辑运算。

6.Cn是算术运算的进位控制端,Cn=0(低电平),表示有进位,运算时相当于在最低位上加进位1,Cn=1(高电平),表示无进位。

逻辑运算与进位无关。

7.ALU-B是输出三态门的控制端,控制运算器的运算结果是否送到数据总线BUS上。

低电平有效。

cpu组成与机器指令执行实验报告

CPU组成与机器指令执行实验报告1. 引言本实验旨在探究中央处理器(CPU)的组成以及机器指令的执行过程。

通过深入理解CPU的工作原理和机器指令的执行流程,我们可以更好地理解计算机的数据处理过程。

2. CPU的组成CPU是计算机的核心组件之一,它负责执行计算机上的所有任务。

一个典型的CPU由以下几个重要组成部分构成:2.1 控制单元(Control Unit)控制单元是CPU的核心组件之一,负责协调和控制整个CPU的操作。

它从存储器中读取指令,并解码这些指令以确定下一步的操作。

2.2 算术逻辑单元(Arithmetic Logic Unit,ALU)算术逻辑单元是CPU的另一个重要组成部分,负责执行各种算术和逻辑运算,如加法、减法、乘法、除法等。

ALU能够执行基本的数学计算和布尔逻辑运算。

2.3 寄存器(Registers)寄存器是CPU内部的临时存储器,用于存储指令和数据。

CPU拥有多个寄存器,每个寄存器都有特定的功能,如程序计数器(Program Counter,PC)用于存储下一条指令的地址,累加器(Accumulator)用于存储运算结果等。

3. 机器指令的执行过程机器指令是计算机能够理解和执行的指令,它们以二进制的形式表示。

机器指令的执行过程可以分为以下几个步骤:3.1 取指令(Fetch)控制单元从存储器中读取下一条指令,并将其存储在指令寄存器(Instruction Register,IR)中。

3.2 解码指令(Decode)控制单元解码指令寄存器中的指令,确定需要执行的操作类型和操作数。

3.3 执行指令(Execute)根据解码的结果,CPU执行指令中指定的操作。

这可能涉及到从寄存器中读取数据、进行算术运算、修改寄存器的值等。

3.4 存储结果(Store)执行指令后,结果可能需要存储在寄存器或存储器中,以备后续操作使用。

4. 实验步骤在本次实验中,我们将使用一个简单的汇编语言程序来演示机器指令的执行过程。

实验三 R指令设计实现

实验三R指令设计实现实验目的通过实现R指令的数据通路,理解R指令的工作原理,为进一步实现核心指令集的数据通路打下基础。

实验设备1.装有ISE10.1的PC机一台2.EDK-3SAISE实验箱一台实验内容1、用verilog描述MIPS通用寄存器组,并进行功能仿真2、用verilog描述MIPS的R指令数据通路,并进行功能仿真3、将R指令数据通路加载到实验箱运行。

要求6位Func码的低4位由拨动开关输入;寄存器号rs的低4位用4位拨动开关输入;寄存器号rt、td的低4位相等,用4位拨动开关输入;reset信息用拨动开关输入。

ALU运算结果的低12位输出到12位led指示灯上显示。

实验报告格式一、实验目的二、实验设备三、实验内容1.模块代码2.功能仿真测试代码3.功能仿真测试时序图四、实验小结参考资料一、MIPS通用寄存器组MIPS通用寄存器组包含32个32位的通用寄存器,其中0号通用寄存器存储常量0。

寄存器组有两个只读端口和一个只写端口,写操作在时钟上升沿触发,且可控制是否写。

寄存器组模型示意图如下:二、R指令数据通路R类型指令主要执行寄存器间的算术逻辑运算,原理图如下。

从指令中取得源寄存器号,在寄存器组中读出相应内容,送到ALU计算,并将结果写回到寄存器中。

ALU的控制通过指令中的功能字段实现。

R指令格式及编码如下:R指令码示例寄存器名与寄存器号的对应关系三、12位LED灯四、12位拨动开关五、独立的1位拨动开关六、时钟源实验箱提供40MHz的时钟信号,从FPGA的P9引脚输入。

必要时,可对时钟信号做分频操作。

将40MHz时钟信号送给计数器计数,则每秒可计数10,0110,0010,0101,1010,0000,0000B次,将计数器的第25位输出做为时钟信号,则可以得到频率约为1秒的时钟。

module ReduceFreq(clkin,clkout);input clkin;output clkout;reg [25:0] counter;always@(posedge clkin)counter=counter+1;assign clkout=counter[25];endmodule。

杭电实验报告模版

一、实验模块实验名称:____________________实验课程:____________________实验时间:____________________实验地点:____________________实验人员:____________________二、实验标题____________________三、实验目的1. 了解____________________2. 掌握____________________3. 培养____________________四、实验原理____________________五、实验仪器与设备1. 仪器名称:____________________2. 仪器型号:____________________3. 仪器规格:____________________4. 其他设备:____________________六、实验步骤1. 实验步骤一:(1)____________________(2)____________________(3)____________________2. 实验步骤二:(1)____________________(2)____________________(3)____________________3. 实验步骤三:(1)____________________(2)____________________(3)____________________(注:根据实际实验内容,添加相应步骤)七、实验过程1. 实验过程一:(1)____________________(2)____________________(3)____________________2. 实验过程二:(1)____________________(2)____________________(3)____________________3. 实验过程三:(1)____________________(2)____________________(3)____________________(注:根据实际实验内容,添加相应过程)八、实验数据记录与分析1. 实验数据记录:(注:根据实际实验内容,添加数据记录表格)2. 实验数据分析:(注:根据实际实验内容,对实验数据进行分析)九、实验结论1. 实验结果:(1)____________________(2)____________________(3)____________________2. 实验结论:(1)____________________(2)____________________(3)____________________十、实验讨论1. 实验中遇到的问题及解决方法:(1)____________________(2)____________________(3)____________________2. 实验改进建议:(1)____________________(2)____________________(3)____________________十一、实验总结通过本次实验,我了解了____________________,掌握了____________________,培养了____________________。

杭电计组实验8-实现R型指令的CPU设计实验

杭电计组实验8-实现R型指令的CPU设计实验实验报告2018 年 6 月 1 日成绩:一、实验程序源代码顶层LED测试模块:module Top_LED(clk,rst,SW,LED);input clk,rst;input [2:0]SW;output reg[7:0]LED;wire ZF,OF;wire [31:0]ALU_F;top_R_cpu test_cpu(rst,clk,ZF,OF,ALU_F);always@(*)begincase(SW)3'b000:LED=ALU_F[7:0];3'b001:LED=ALU_F[15:8];3'b010:LED=ALU_F[23:16];3'b011:LED=ALU_F[31:24];3'b100:begin LED[7:2]=0;LED[1]=OF;LED[0]=ZF;enddefault:LED=0;endcaseendendmodule顶层R型CPU模块:module top_R_cpu(input rst,input clk,output ZF,output OF,output [31:0]F); reg write_reg;wire [31:0]Inst_code;wire [31:0]R_Data_A;wire [31:0]R_Data_B;reg [2:0]ALU_OP;pc pc_connect(clk,rst,Inst_code);Register_file R_connect(Inst_code[25:21],Inst_code[20:16],Inst_code[15:11],write_reg,F,~clk,rst,R_Data_A,R_Data_B);ALU ALU_connect(R_Data_A,R_Data_B,F,ALU_OP,ZF,OF);always@(*)beginwrite_reg=0;ALU_OP=0;if(Inst_code[31:26]==0)begincase(Inst_code[5:0])6'b100000:ALU_OP=3'b100;6'b100010:ALU_OP=3'b101;6'b100100:ALU_OP=3'b000;6'b100101:ALU_OP=3'b001;6'b100110:ALU_OP=3'b010;6'b100111:ALU_OP=3'b011;6'b101011:ALU_OP=3'b110;6'b000100:ALU_OP=3'b111;endcasewrite_reg=1;endendendmodulePC取指令模块:module pc(input clk,input rst,output [31:0]Inst_code);reg [31:0]PC;wire[31:0]PC_new;initialPC<=32'h00000000;Inst_ROM Inst_ROM1 (.clka(clk),.addra(PC[7:2]),.douta(Inst_code));assign PC_new={24'h000000,PC_new[7:0]};always@(negedge clk or posedge rst)beginif(rst)PC=32'h00000000;else PC=PC_new;endendmodule寄存器堆模块:moduleRegister_file(R_Addr_A,R_Addr_B,W_Addr,Write_Reg,W_Data,Clk,Reset,R_Data_A,R_Data_B); input [4:0]R_Addr_A;input [4:0]R_Addr_B;input [4:0]W_Addr;input Write_Reg;input [31:0]W_Data;input Clk;input Reset;output [31:0]R_Data_A;output [31:0]R_Data_B;reg [31:0]REG_Files[0:31];reg [5:0]i;initial//仿真过程中的初始化beginfor(i=0;i<=31;i=i+1)REG_Files[i]=0;endassign R_Data_A=REG_Files[R_Addr_A];assign R_Data_B=REG_Files[R_Addr_B];always@(posedge Clk or posedge Reset)beginif(Reset)for(i=0;i<=31;i=i+1)REG_Files[i]=0;elseif(Write_Reg&&W_Addr!=0)REG_Files[W_Addr]=W_Data;endendmoduleALU算术逻辑运算单元模块:module ALU(A,B,F,ALU_OP,ZF,OF);input [31:0]A,B;input [2:0]ALU_OP;output reg ZF,OF;output reg[31:0]F;reg C32;always@(*)beginOF=1'b0;C32=1'b0;case(ALU_OP)3'b000:F=A&B;3'b001:F=A|B;3'b010:F=A^B;3'b011:F=~(A^B);3'b100:begin {C32,F}=A+B;OF=A[31]^B[31]^F[31]^C32;end 3'b101:begin {C32,F}=A-B;OF=A[31]^B[31]^F[31]^C32;end3'b110:if(A<B)F=1;elseF=0;3'b111:F=B<<A;endcaseif(F==0)ZF=1;elseZF=0;endendmodule测试代码:module test;// Inputsreg rst;reg clk;// Outputswire ZF;wire OF;wire [31:0] F;// Instantiate the Unit Under Test (UUT) top_R_cpu uut (.rst(rst),.clk(clk),.ZF(ZF),.OF(OF),.F(F));initial begin// Initialize Inputsrst = 0;clk = 0;// Wait 100 ns for global reset to finish#100;clk=1;// Add stimulus hereforeverbegin#50;clk=~clk;endendendmodule二、仿真波形三、电路图顶层电路模块顶层电路内部结构:四、引脚配置(约束文件)NET "LED[7]" LOC = T11;NET "LED[6]" LOC = R11;NET "LED[5]" LOC = N11;NET "LED[4]" LOC = M11;NET "LED[3]" LOC = V15;NET "LED[2]" LOC = U15;NET "LED[1]" LOC = V16;NET "LED[0]" LOC = U16;NET "SW[2]" LOC = V9;NET "SW[1]" LOC = T9;NET "SW[0]" LOC = T10;NET "clk" LOC = C9;NET "rst" LOC = C4;五、思考与探索(1)R型指令CPU实验结果记录表序号指令执行结果标志结论1 0000827 FFFFFFFF 0 0 正确2 0001102b 0000_0001 0 0 正确3 00421820 0000_0002 0 0 正确4 00622020 0000_0003 0 0 正确5 00832820 0000_0005 0 0 正确6 00a33020 0000_0007 0 0 正确7 00463804 0000_000E 0 0 正确8 00a64820 0000_000C 0 0 正确9 01264004 0000_7000 0 0 正确10 00284826 FFFF_8FFF 0 0 正确11 01215020 FFFF_8FFE 0 0 正确12 01075822 0000_6FF2 0 0 正确13 00e86022 FFFF_900E 0 0 正确14 012c6824 FFFF_800E 0 0 正确15 012c7025 FFFF_9FFF 0 0 正确16 00c77825 0000_FFFF 0 0 正确。

杭电2018计组期末Test chapter 7 CPU Controller

Test 1

某高级语言源程序中的语句:

while ( A[i] == k ) i+ = 1

若对其编译时,编译器将i和k分别分配在寄存器$s3和 $s5中,数组A的基址存放在$s6中,则生成的MIPS汇 编代码段如下:

add $s3, $zero, $zero loop: sll $t1, $s3, 2 add $t1, $t1, $s6 lw $t0, 0($t1) bne $t0, $s5, exit addi $s3, $s3, 1 j loop exit: … #左移: R[$t1]=R[$s3]<<2, 即R[$t1]=i×4 #算术加:R[$t1]=R[$t1]+ R[$s6],即R[$t1]=address of A[i] #取数: R[$t0]=M[R[$t1]+ 0], 即R[$t0]=A[i] #不相等转移:R[$t0]≠R[$s5] then goto exit #算术加: R[$s3]=R[$s3]+ 1,即i=i+1 #无条件转移:goto loop

译码及 控制单元

Write_Reg R_Addr_A R_Addr_B W_Addr

32 ALU_OP

令 b[25:21](rs)

PC rst

Inst_addr Inst_code 指令存储器

机 b[20:16](rt) 器

R_Data_A 寄存器堆

rt_imm_s

A

指 码 b[15:11](rd) 令 机 器 码

ALU

0 1

B

clk rst

32

imm offset

16

符号 扩展

wr_data_s 0 1 2 3

杭电计组实验10-实现R-I-J型指令的CPU设计实验

实验报告2018年6月9 日成绩:、实验程序源代码顶层RI型指令CPU模块测试文件: module test;//In putsreg rst;reg clk_100MH z;reg clk;// Outputs wire ZF; wire OF;wire [31:0] F;wire [31:0] M_R_Data; wire [31:0] PC;// I nsta ntiate the Unit Un der Test (UUT) TOP_RIJ_CPU uut ( .rst(rst), .clk_100F .clk(clk), •ZF(ZF), •OF(OF),.M_R_Data(M_R_Data), .PC(PC));in itial begi n//I nitialize In putsrst = 0;clk_100MHz = 0;clk = 0;// Wait 100 ns for global reset to fin ish #100;// Add stimulus hereforeverbegi n#2;clk=~clk;#10;clk_100MHz=~clk_100MH z;endenden dmodule顶层LED验证模块module TOP_LED(clk_100M Hz, oclk,rst,SW 丄ED); in put clk_100MH z; in put oclk,rst;in put [3:0]SW;output reg[7:0]LED;4'b0001:LED二F[15:8];4'b0010:LED=F[23:16];4'b0011:LED=F[31:24];4'b0100:LED=M_R_Data[7:0];4'b0101:LED=M_R_Data[15:8];4'b0110:LED二M_R_Data[23:16];4'b0111:LED=M_R_Data[31:24];4'b1000:begin LED[7:2]=0;LED[1]=OF;LED[0]=ZF;e nd4'b1100:LED=PC[7:0];4'b1101:LED=PC[15:8];4'b1110:LED=PC[23:16];4'b1111:LED=PC[31:24];default:LED=0;endcaseenden dmodule顶层RIJ型指令CPU验证模块:module TOP RIJ CPU(i nput rst, in put elk 100MHz,i nput clk,output ZF, output OF,output [31:0]F,output [31:0]M_R_Data,output [31:0]PC);wire Write_Reg;wire [31:0]lnst_code;wire [4:0]rs;wire [4:0]rt;wire [4:0]rd;wire [31:0]rs_data;wire [31:0]rt_data;wire [31:0]rd_data;wire [31:0]imm_data;〃被扩展的立即数wire [15:0]imm;//wire rd_rt_s;wire [1:0]w_r_s;wire imm_s;〃判断是否需要扩展wire rt_imm_s;//B 端选择rt或者是扩展后的immwire Mem_Write;//wire alu_mem_s;wire [1:0]wr_data_s;wire [31:0]W_Addr;wire [31:0]W_Data;wire [31:0]R_Data_A;wire [31:0]R_Data_B;wire [31:0]F;wire [31:0]ALU_B;//B 端口数据wire [2:0]ALU_OP;wire [1:0]PC_s;wire [31:0]PC_ new;wire [31:0]PC;wire [25:0]address;pc pc_c onn ect(clk,rst,PC_s,R_Data_A,imm_data,address,l nst_code,PC);OP_YIMA op(I nst_code,ALU_QP;,rt,rd,Write_Reg,imm,imm_s,rt_imm_s,Mem_Write,address,w_r_s,wr_data_s,PC_s,ZF);elsebeg in case(PC_s)2'b00:PC<二PC_ new;2'bO1:PC<二R_Data_A;2'b10:PC<=PC_ new+(imm_data<<2);2'b11:PC<={PC_ new[31:28],address,2'b00};endcaseendenden dmoduleOP指令功能译码模块:module OP_YIMA(i nst,ALU_OPfe,rt,rd,Write_Reg,imm,imm_s,rt_imm_s,Mem_Write,address,w_r_s,wr_data_s,PC_s,ZF) in put [31:0]i nst; output reg[2:0]ALU_OP;output reg[4:0]rs;output reg[4:0]rt;output reg[4:0]rd;output reg Write_Reg;output reg[15:0]imm;//output reg rd_rt_s;output reg imm_s;output reg rt_imm_s;output reg Mem_Write;output reg [25:0]address;output reg[1:0] w_r_s;output reg[1:0] wr_data_s;output reg[1:0] PC_s;in put ZF;always@(*)begi nw_r_s=2'b01;Write_Reg=1; wr_data_s=2'b00;case(i nst[31:26])6'b001000:begin imm_s=1;ALU_OP=3'b100;e nd 6'b001100:begin imm_s=0;ALU_OP=3'b000;e nd 6'b001110:begin imm_s=0;ALU_OP=3'b010;e nd 6'b001011:begin imm_s=0;ALU_OP=3'b110;e nd endcaseend// ------- 处理I型取数/存数指令------if((i nst[31:30]==2'b10)&&(in st[28:26]==3'b011))imm=i nst[15:0];rt=i nst[20:16];//rt 寄存器rs=inst[25:21];//rs 寄存器//rd_rt_s=1;//rt作为目的存储器rt_imm_s=1;//imm 作为源操作数imm_s=1;w_r_s=2'b01;wr_data_s=2'b01;PC_s=2'b00;case(i nst[31:26])6'b100011:begin Mem_Write=O; Write_Reg=1;ALU_OP=3'b100;e nd 6'b101011:begin Mem_Write=1; Write_Reg=0;ALU_OP=3'b100;e nd endcaseend// ---------- 处理I型跳转指令-------if(i nst[31:27]==5'b00010)begi nimm=i nst[15:0];rt=i nst[20:16];//rtrs=i nst[25:21];//rscase(i nst[31:26])for(i=0;iv=31;i二i+1)REG_Files[i]=O;endassign R_Data_A=REG_Files[R_Addr_A]; assign R_Data_B=REG_Files[R_Addr_B]; always@(posedge Clk or posedge Reset) begi nif(Reset)for(i=0;i<=31;i=i+1)REG_Files[i]v=O;elseif(Write_Reg&&W_Addr!=0)REG_Files[W_Addr]<=W_Data; enden dmoduleALU运算模块:module ALU(A,B,F,ALU_QZF,OF); in put [31:0]A,B;in put [2:0]ALU_OP;output reg ZF,OF;output reg[31:0]F;reg C32;always@(*)begi nOF=1'b0;C32=1'b0;case(ALU_OP)3'b000:F=A&B;3'b001:F=A|B;3'b010:F=A A B;3'bO11:F=~(A^B);3'b100:begin {C32,F}=A+B;OF=A[31]A B[31]A F[31]A C32;e nd3'b101:begin {C32,F}二A-B;OF二A[31]AB[31]AF[31FC32;e nd 3'b110: if(A<B)F=1;elseF=0;3'b111:F=B<< A;endcaseif(F==0)ZF=1;elseZF=0;enden dmodule三、电路图J!仿真波形NjmeVtki*曲饶k ■ FIJI*]•电M_R_Dala[11fl]0 1吃网IIIhO Q10000(X1 悴259^353顶层电路内部结构:四、引脚配置(约束文件)NET "LED[7]" LOC = T11; NET "LED[6]" LOC = R11; NET "LED[5]" LOC = N11; NET "LED[4]" LOC = M11; NET "LED[3]" LOC = V15; NET "LED[2]" LOC = U15; NET "LED[1]" LOC = V16; NET "LED[0]" LOC = U16; NET "SW[3]" LOC = M8; NET "SW[1]" LOC = T9; NET "SW[01" LOC = T10;顶层电路模块SW(3:D)TOP LEDLED(7:0)elk 100MH2odknsl■ /TOP_LEDTOP LED.1NET "clk_100MHz" LOC = V10;NET "oclk" LOC = C9;NET "rst" LOC = C4;NET "SW[2]" LOC = V9;五、思考与探索(1) R-l-J型指令CPU实验结果记录表序号指令执行结果标志结论1 00004020 $8=0000_0000 0 0 正确2 00004820 $9=0000_0000 0 0 正确3 200a0014 $10=0000_0014 0 0 正确4 8d2b0010 $11=0000_0010 0 0 正确5 010b4020 $8=0000_2222 0 0 正确6 21290004 $9=0000_0004 0 0 正确7 214affff $10=000_0013 0 0 正确8 11400001 判断:$10不为0 0 0 正确0 0 正确9 08000003 返回去执行地址为0000_0010 的指令,即序号4:8d2b001010 ac0b0030 存储器地址:0000 0030 0 0 正确。

CPU组成与机器指令执行实验

R3=07H;存储器存储单元[10H]=55H。

TEC-5

CPU组成与机器指令执行实验

12

模型机连线示意图

控制台 开关控制 DP DB QD CLR# 时序发生器

开关控制

SWC SWB SWA

指示灯 信号

P0~P2

微程序控制器

操作和执行定时、数据加工等。

• 控制器:程序计数器,指令寄存器,指令译码器,时

序发生器,操作控制器等,取指、译码产生控制信号, 控制CPU、内存,输入/输出之间的数据传输。

• 运算器:算数逻辑单元ALU,累加器AC,数据缓冲

寄存器DR,状态条件寄存器PSW等,数据加工,算 数逻辑运算,产生运算结果或逻辑判断。

• 写存储器(WRM):按下复位按钮CRL#,置

SWC=0,SWB=0,SWA=1。①在 SW7~SW0中设置存储器地址,采用单拍或连 续方式,按QD按钮将此地址打入AR,注意 观察AR指示灯。②在SW7~SW0置好数据, 按QD按钮,将数据写入AR指定的存储器单 元,这时AR加1。③返回②。依次进行下去, 直到按复位按钮CRL#为止。实现对RAM的

1D

0A

SW→DBUS DBUS→AR

02

09

SW→DBUS DBUS→AR

TJ

04

SW→DBUS RAM→DBUS SW→DBUS

DBUS→RAM

TJ

DBUS→RAM

PR(000) 08

SW→DBUS DBUS→PC

0F

06

RAM→IBUS

07

Rs→DBUS TJ

1E

TEC-5

0D

杭电计组实验9-实现R-I型指令地CPU设计实验

clk=1;

// Add stimulus here

forever

begin

#50;

clk=~clk;

end

end

endmodule

顶层LED验证模块:

module TOP_LED(clk_100MHz,oclk,rst,SW,LED);

input clk_100MHz;

input oclk,rst;

begin

if(rst)

PC=32'h00000000;

else

PC={24'h000000,PC_new[7:0]};

end

endmodule

OP指令功能译码模块

module OP_YIMA(inst,ALU_OP,rs,rt,rd,Write_Reg,

imm,rd_rt_s,imm_s,rt_imm_s,Mem_Write,alu_mem_s);

wire [31:0]ALU_B;

wire [2:0]ALU_OP;

pc pc_connect(clk,rst,Inst_code);

OP_YIMA op(Inst_code,ALU_OP,rs,rt,rd,Write_Reg,imm,rd_rt_s,imm_s,rt_imm_s,Mem_Write,alu_mem_s);

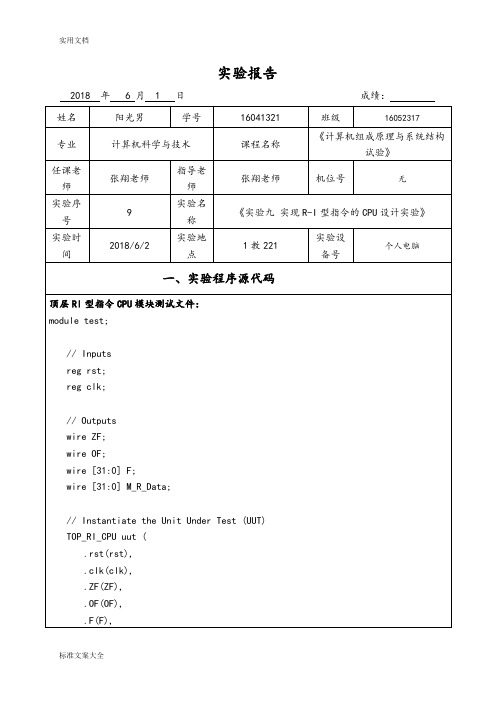

实验报告

2018年

班级

16052317

专业

计算机科学与技术

课程名称

《计算机组成原理与系统结构试验》

任课老师

张翔老师

指导老师

张翔老师

机位号

无

实验序号

9

实验名称

《实验九实现R-I型指令的CPU设计实验》

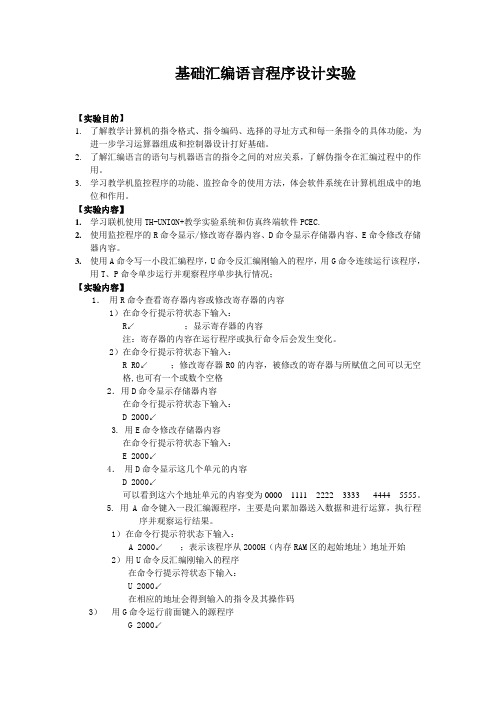

计组实验报告基础汇编语言程序设计实验

基础汇编语言程序设计实验【实验目的】1.了解教学计算机的指令格式、指令编码、选择的寻址方式和每一条指令的具体功能,为进一步学习运算器组成和控制器设计打好基础。

2.了解汇编语言的语句与机器语言的指令之间的对应关系,了解伪指令在汇编过程中的作用。

3.学习教学机监控程序的功能、监控命令的使用方法,体会软件系统在计算机组成中的地位和作用。

【实验内容】1.学习联机使用TH-UNION+教学实验系统和仿真终端软件PCEC.2.使用监控程序的R命令显示/修改寄存器内容、D命令显示存储器内容、E命令修改存储器内容。

3.使用A命令写一小段汇编程序,U命令反汇编刚输入的程序,用G命令连续运行该程序,用T、P命令单步运行并观察程序单步执行情况;【实验内容】1.用R命令查看寄存器内容或修改寄存器的内容1)在命令行提示符状态下输入:R↙;显示寄存器的内容注:寄存器的内容在运行程序或执行命令后会发生变化。

2)在命令行提示符状态下输入:R R0↙;修改寄存器R0的内容,被修改的寄存器与所赋值之间可以无空格,也可有一个或数个空格2.用D命令显示存储器内容在命令行提示符状态下输入:D 2000↙3. 用E命令修改存储器内容在命令行提示符状态下输入:E 2000↙4.用D命令显示这几个单元的内容D 2000↙可以看到这六个地址单元的内容变为0000 1111 2222 3333 4444 5555。

5. 用A命令键入一段汇编源程序,主要是向累加器送入数据和进行运算,执行程序并观察运行结果。

1)在命令行提示符状态下输入:A 2000↙;表示该程序从2000H(内存RAM区的起始地址)地址开始2)用U命令反汇编刚输入的程序在命令行提示符状态下输入:U 2000↙在相应的地址会得到输入的指令及其操作码3)用G命令运行前面键入的源程序G 2000↙4)用P或T命令,单步执行这段程序,观察指令执行结果在命令行提示符状态下输入:T 2000↙<12020:MVRD R2,00OA2022:MVRD R0,00302024:OUT 802025:DEC R22026:JRZ 202E2027:PUSH R02028:IN 812029:SHR R0202A:JRNC 2028202B:POP R0202C:INC R0202D:JR 2024202E:RET202F:↙<2(2100) MVRD R2,001AMVRD R0,0041(2104) OUT 80DEC R2JRZ 210EPUSH R0(2108)IN 81SHR R0JRNC 2108POP R0INC R0JR 2104(210E)RET【实验结果】<1屏幕上输出'0'到'9'十个数字符<2屏幕上显示“A”~“Z”26个英文字母【实验过程中遇到的问题以及解决办法】在验证例3的实验时,输入语句“JC 2053”,执行时系统一直提示有错误,无法进行运算查表得知语句中没有JC ,只有JRC,所以修改语句即可解决。

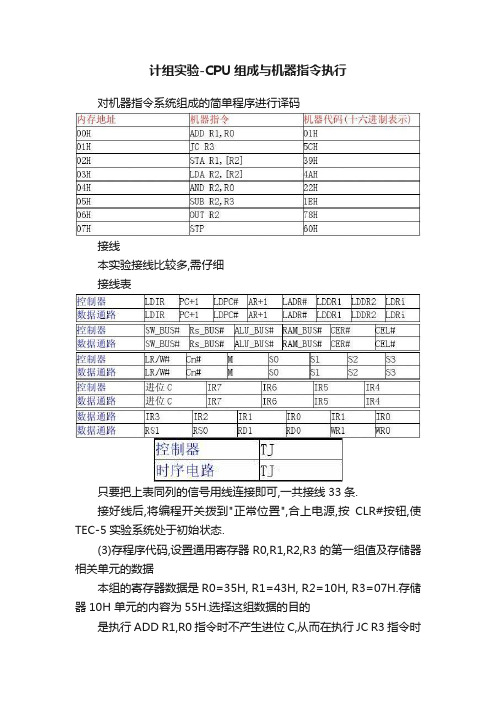

计组实验-CPU组成与机器指令执行

计组实验-CPU组成与机器指令执行对机器指令系统组成的简单程序进行译码接线本实验接线比较多,需仔细接线表只要把上表同列的信号用线连接即可,一共接线33条.接好线后,将编程开关拨到"正常位置",合上电源,按CLR#按钮,使TEC-5实验系统处于初始状态.(3)存程序代码,设置通用寄存器R0,R1,R2,R3的第一组值及存储器相关单元的数据本组的寄存器数据是R0=35H, R1=43H, R2=10H, R3=07H.存储器10H 单元的内容为55H.选择这组数据的目的是执行ADD R1,R0指令时不产生进位C,从而在执行JC R3指令时不产生跳转,而是顺序执行.●设置通用寄存器R0,R1,R2,R3的值.本操作中我们使R0=35H, R1=43H, R2=10H, R3=07H.1.令DP=0,DB=0,使系统处于连续运行状态.令SWC=0, SWB=1, SWA=1,使系统处于写寄存器状态WRF.按CLR#,使实验系统处于初始状态.2.在SW7-SW0上设置一个存储器地址,该存储器地址供设置通用寄存器使用.(该存储器地址最好是不常用的一个地址,以免设置通用寄存器操作破坏重要的存储器单元的内容.)这里我们将该地址设置为0FFH.按一次QD按钮,将0FFH写入左端口地址寄存器AR.3.在SW7-SW0上设置00H,作为通用寄存器R0的寄存器号.按一次QD按钮,将00H写入指令寄存器IR.4.在SW7-SW0上设置35H.按一次QD按钮,将35H写入IR指定的R0寄存器.5.在SW7-SW0上设置01H,作为通用寄存器R1的寄存器号.按一次QD按钮,将01H写入指令寄存器IR.6.在SW7-SW0上设置43H.按一次QD按钮,将35H写入IR指定的R1寄存器.7.在SW7-SW0上设置02H,作为通用寄存器R2的寄存器号.按一次QD按钮,将02H写入指令寄存器IR.8.在SW7-SW0上设置10H.按一次QD按钮,将10H写入IR指定的R2寄存器.9.在SW7-SW0上设置03H,作为通用寄存器R3的寄存器号.按一次QD按钮,将03H写入指令寄存器IR.10.在SW7-SW0上设置07H.按一次QD按钮,将07H写入IR指定的R3寄存器.11.设置寄存器内容完毕.按CLR#按钮,使系统恢复到初始状态.注意:设置完R0,R1,R2,R3的值后,最好用读寄存器控制台操作检查一下写入的内容是否正确.●存程序机器代码本操作中,我们从00地址开始存8个机器代码:01H, 5CH, 39H, 4AH, 22H, 1EH, 78H, 60H.在10H单元存入55H,作为10H单元的初值,以检查LDA和STA两条指令的作用.1.令DP=0,DB=0,使系统处于连续运行状态.令SWC=0, SWB=0, SWA=1,使系统处于写双端口存储器工作方式WRM.按CLR#,使实验系统处于初始状态.2.置SW7-SW0为00H,按QD按钮,将00H写入左端口地址寄存器AR.3.置SW7-SW0为01H,按QD按钮,将01H写入存储器00H单元.AR自动加1,变为01H.4.置SW7-SW0为5CH,按QD按钮,将5CH写入存储器01H单元.AR自动加1,变为02H.5.置SW7-SW0为39H,按QD按钮,将39H写入存储器02H单元.AR自动加1,变为03H.6.置SW7-SW0为4AH,按QD按钮,将4AH写入存储器03H单元.AR自动加1,变为04H.7.置SW7-SW0为22H,按QD按钮,将22H写入存储器04H单元.AR自动加1,变为05H.8.置SW7-SW0为1EH,按QD按钮,将1EH写入存储器05H单元.AR自动加1,变为06H.9.置SW7-SW0为78H,按QD按钮,将78H写入存储器06H单元.AR自动加1,变为07H.10.置SW7-SW0为60H,按QD按钮,将60H写入存储器07H单元.AR自动加1,变为08H.11.按QD按钮,使实验系统恢复到初始状态.12.置SW7-SW0为10H,按QD按钮,将10H写入左端口地址寄存器AR.13.置SW7-SW0为55H,按QD按钮,将55H写入存储器10H单元.AR自动加1,变为11H.14.往存储器输入程序和数据结束,按CLR#按钮,使实验系统恢复到初始状态.注意:设置完存储器的程序和数据后,最好用存储器控制台操作检查一下写入的内容是否正确.●用单拍(DP)方式执行一遍程序置SWC=0, SWB=0, SWA=0, DP=1, DB=0,使实验系统处于单拍运行状态.置SW7-SW0=00H,使程序从地址00H开始执行.按CLR#按钮,使实验系统处于初始状态,然后一次一次按QD按钮,使程序一拍一拍执行.在单拍执行过程中,首先要随时监测AR, PC, μA5-μA0和IR的值,以判定程序执行到何处,正在执行哪条指令和微指令.对照微程序流程图,可以判断出指令的地址和正在进行的微操作.程序执行的结果如下:初值:R0=35H, R1=43H, R2=10H, R3=07H.存储器10H单元的内容为55H.1. ADD R1, R0执行结果R0=35H, R1=78H, R2=10H, R3=07H.存储器10H单元的内容为55H.无进位C.2. JC R3执行结果R0=35H, R1=78H, R2=10H, R3=07H.存储器10H单元的内容为55H.PC为02H,进位C不变.3. STA R1, [R2]执行结果R0=35H, R1=78H, R2=10H, R3=07H.存储器10H单元的内容为78H.4. LDA R2,[R2]执行结果R0=35H, R1=78H, R2=78H, R3=07H.存储器10H单元的内容为78H.5. AND R2, R0执行结果R0=35H, R1=78H, R2=30H, R3=07H.存储器10H单元的内容为78H.6. SUB R2, R3执行结果R0=35H, R1=78H, R2=29H, R3=07H.存储器10H单元的内容为78H.进位C为1.7. OUT R2执行结果R0=35H, R1=78H, R2=29H, R3=07H.存储器10H单元的内容为78H.可在DBUS指示灯上观察到29H.8. STP执行结果R0=35H, R1=78H, R2=29H, R3=07H.存储器10H单元的内容为78H.最后执行的结果可通过控制台的读寄存器操作和读存储器操作观察到,在观察作后结果之前,首先应按CLR#按钮,使实验系统处于初始状态.演示第一步,其他类似●用连续方式执行一遍程序1.由于上面的单拍执行程序,已破坏了寄存器R1,R2和存储器10单元的内容(程序没有破坏),因而需要重新设置寄存器R1,R2和存储器10单元的值.初值:R0=35H, R1=43H, R2=10H, R3=07H.存储器10H单元的内容为55H.2.置SWC=0, SWB=0, SWA=0, DP=0, DB=0,使实验系统处于连续运行状态.置SW7-SW0=00H,使程序从地址00H开始执行.按CLR#按钮,使实验系统处于初始状态,然后按一次QD按钮,则程序自动连续运行到地址为07H的STP指令.执行结果R0=35H, R1=78H, R2=29H, R3=07H.存储器10H单元内容为78H.最后执行的结果可通过控制台的读寄存器操作和读存储器操作观察到,在观察作后结果之前,首先应按CLR#按钮,使实验系统处于初始状态.(4)存程序代码,设置通用寄存器R0,R1,R2,R3的第二组值及存储器相关单元的数据本组的寄存器数据是R0=86H, R1=88H, R2=10H, R3=07H.存储器10H 单元的内容为55H.选择这组数据的目的是执行ADD R1,R0指令时产生进位C,从而在执行JC R3指令时产生跳转,而不是顺序执行.●设置通用寄存器R0,R1,R2,R3的值.本操作中我们使R0=86H, R1=88H, R2=10H, R3=07H.1.令DP=0,DB=0,使系统处于连续运行状态.令SWC=0, SWB=1, SWA=1,使系统处于写寄存器状态WRF.按CLR#,使实验系统处于初始状态.2.在SW7-SW0上设置一个存储器地址,该存储器地址供设置通用寄存器使用.(该存储器地址最好是不常用的一个地址,以免设置通用寄存器操作破坏重要的存储器单元的内容.)这里我们将该地址设置为0FFH.按一次QD按钮,将0FFH写入左端口地址寄存器AR.3.在SW7-SW0上设置00H,作为通用寄存器R0的寄存器号.按一次QD按钮,将00H写入指令寄存器IR.4.在SW7-SW0上设置86H.按一次QD按钮,将86H写入IR指定的R0寄存器.5.在SW7-SW0上设置01H,作为通用寄存器R1的寄存器号.按一次QD按钮,将01H写入指令寄存器IR.6.在SW7-SW0上设置88H.按一次QD按钮,将88H写入IR指定的R1寄存器.7.在SW7-SW0上设置02H,作为通用寄存器R2的寄存器号.按一次QD按钮,将02H写入指令寄存器IR.8.在SW7-SW0上设置10H.按一次QD按钮,将10H写入IR指定的R2寄存器.9.在SW7-SW0上设置03H,作为通用寄存器R3的寄存器号.按一次QD按钮,将03H写入指令寄存器IR.10.在SW7-SW0上设置07H.按一次QD按钮,将07H写入IR指定的R3寄存器.11.设置寄存器内容完毕.按CLR#按钮,使系统恢复到初始状态.注意:设置完R0,R1,R2,R3的值后,最好用读寄存器控制台操作检查一下写入的内容是否正确.●存程序机器代码本操作中,我们从00地址开始存8个机器代码:01H, 5CH, 39H, 4AH, 22H, 1EH, 78H, 60H.在10H单元存入55H,作为10H单元的初值,以检查LDA和STA两条指令的作用.1.令DP=0,DB=0,使系统处于连续运行状态.令SWC=0, SWB=0, SWA=1,使系统处于写双端口存储器工作方式WRM.按CLR#,使实验系统处于初始状态.2.置SW7-SW0为00H,按QD按钮,将00H写入左端口地址寄存器AR.1,变为01H.4.置SW7-SW0为5CH,按QD按钮,将5CH写入存储器01H单元.AR自动加1,变为02H.5.置SW7-SW0为39H,按QD按钮,将39H写入存储器02H单元.AR自动加1,变为03H.6.置SW7-SW0为4AH,按QD按钮,将4AH写入存储器03H单元.AR自动加1,变为04H.7.置SW7-SW0为22H,按QD按钮,将22H写入存储器04H单元.AR自动加1,变为05H.8.置SW7-SW0为1EH,按QD按钮,将1EH写入存储器05H单元.AR自动加1,变为06H.9.置SW7-SW0为78H,按QD按钮,将78H写入存储器06H单元.AR自动加1,变为07H.10.置SW7-SW0为60H,按QD按钮,将60H写入存储器07H单元.AR自动加1,变为08H.11.按QD按钮,使实验系统恢复到初始状态.12.置SW7-SW0为10H,按QD按钮,将10H写入左端口地址寄存器AR.加1,变为11H.14.往存储器输入程序和数据结束,按CLR#按钮,使实验系统恢复到初始状态.注意:设置完存储器的程序和数据后,最好用存储器控制台操作检查一下写入的内容是否正确.●用单拍(DP)方式执行一遍程序置SWC=0, SWB=0, SWA=0, DP=1, DB=0,使实验系统处于单拍运行状态.置SW7-SW0=00H,使程序从地址00H开始执行.按CLR#按钮,使实验系统处于初始状态,然后一次一次按QD按钮,使程序一拍一拍执行.在单拍执行过程中,首先要随时监测AR, PC, μA5-μA0和IR的值,以判定程序执行到何处,正在执行哪条指令和微指令.对照微程序流程图,可以判断出指令的地址和正在进行的微操作.程序执行的结果如下:初值:R0=86H, R1=88H, R2=10H, R3=07H.存储器10H单元的内容为55H.1. ADD R1, R0执行结果R0=86H, R1=0EH, R2=10H, R3=07H.存储器10H单元的内容为55H.有进位C.2. JC R3执行结果R0=86H, R1=0EH, R2=10H, R3=07H.存储器10H单元的内容为55H.PC为07H,进位C不变.3. STP执行结果R0=86H, R1=0EH, R2=10H, R3=07H.存储器10H单元的内容为55H.进位C为1.最后执行的结果可通过控制台的读寄存器操作和读存储器操作观察到,在观察作后结果之前,首先应按CLR#按钮,使实验系统处于初始状态.演示●用连续方式执行一遍程序1.由于上面的单拍执行程序,已破坏了寄存器R1的内容(程序没有破坏),因而需要重新设置寄存器R1的值.初值:R0=86H, R1=88H, R2=10H, R3=07H.存储器10H单元的内容为55H.2.置SWC=0, SWB=0, SWA=0, DP=0, DB=0,使实验系统处于连续运行状态.置SW7-SW0=00H,使程序从地址00H开始执行.按CLR#按钮,使实验系统处于初始状态,然后按一次QD按钮,则程序自动连续运行到地址为07H的STP指令.执行结果R0=86H, R1=0EH, R2=10H, R3=07H.存储器10H单元内容为55H.最后执行的结果可通过控制台的读寄存器操作和读存储器操作观察到,在观察作后结果之前,首先应按CLR#按钮,使实验系统处于初始状态.。

实验六_CPU_微程序控制器实验

CPU__微程序控制器实验实验目的1.理解微程序控制器的控制原理2.进一步掌握指令流程和功能3.了解掌握微程序控制器的设计思路和方法实验原理微程序控制器的设计思想是由英国剑桥大学的威尔克斯(Wilkes)教授于1951年提出来的, 即将机器指令的操作(从取指令到执行)分解成若干个更基本的微操作序列, 并将有关的控制信号(微命令)按照一定的格式编成微指令, 存放到一个只读存储器中, 当机器运行时, 一条一条地读出这些微指令, 从而产生全机所需要的各种操作控制信号, 使相应部件执行所规定的操作。

微指令格式:N _µA 0N _µA 1N _µA 2N _µA 3N _µA 4P 0P 1P 2P C _i n cl j _i n s t r u c tc _z _j _f l a gl d _I Ro p _c o d e 0o p _c o d e 1o p _c o d e 2c h a n g e _zc h a n g e _cD R W rs e l _m e m d a t aM e m _W r i t e1234567891011121314151617181920D W _i n s t r u c t实验步骤(1)实验台设置成FPGA-CPU 独立调试模式, REGSEL=0、CLKSEL=1.FDSEL=0.使用实验台上的单脉冲, 即STEP_CLK 短路子短接, 短路子RUN_CLK 断开;(2)将设计在Quartus II 下输入, 编译后下载到TEC-CA 上的FPGA 中;(3)按复位键后, 拨动实验台上的开关SD5~SD0, 改变IR[15…12]、进位标志C 和结果为0标志Z, 观察指示灯R15~R0、A4~A0、A12~A8、A14和A15显示的信号, 追踪每条指令的执行过程并把相应数据填在表6-1中。

(4)观察每条指令的执行过程, 每个节拍进行的微操作和微操作控制信号。

杭电计组实验5-6-7(章老师不插板实验报告)

sllv $19,$3,$17;#$19=0002_0000

sllv $20,$19,$7;#$20=8000_0000

sub $21,$1,$20; #$21=7FFF_FFFF

or $22,$18,$21;#$22=7FFF_FFFF

add $23,$20,$22; #$23=FFFF_FFFF

sub $24,$18,$19; #$24=6FFE_0000

sub $25,$19,$18; #$25=9002_0000

xor $26,$1,$18;#$26=8FFF_FFFF

sltu $27,$22,$20;#$27=0000_0001

sltu $28,$26,$20;#$28=0000_0000

#10;

Clk=1;

B

#100;

clka=0;

wea=0;

addra=6'b000001;

dina=32'b11111111110001111111111101101111;

#100;

clka=1;

wea=0;

addra=6'b000001;

dina=32'b11111111110001111111$1=FFFF_FFFF

sltu $2,$0,$1;#$2=0,000_0001

add $3,$2,$2; #$3=0000_0002

add $4,$3,$2; #$4=0000_0003

add $5,$4,$3; #$5=0000_0005

add $6,$5,$3; #$6=0000_0007

实验报告

2016年5月10日 成绩:

R0、R1、R2、R3寄存器实验

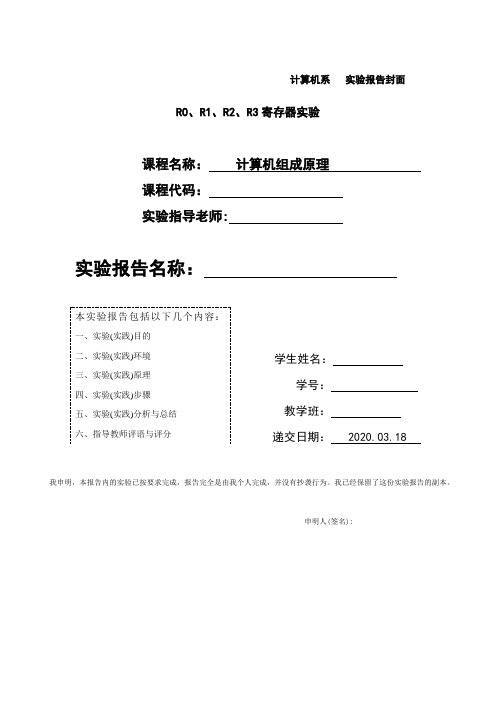

计算机系 实验报告封面

R0、R1、R2、R3寄存器实验

课程名称: 计算机组成原理 课程代码: 实验指导老师:

实验报告名称:

学生姓名:

学号: 教学班:

递交日期: 2020.03.18

我申明,本报告内的实验已按要求完成,报告完全是由我个人完成,并没有抄袭行为。

我已经保留了这份实验报告的副本。

申明人(签名):

本实验报告包括以下几个内容:

一、实验(实践)目的 二、实验(实践)环境 三、实验(实践)原理 四、实验(实践)步骤 五、实验(实践)分析与总结 六、指导教师评语与评分

四、实验步骤

1.10芯扁平线连接J1和J2,打开电源开关之后断开J1和J2,连接J

1和J3

2.按“1”键,选择“8位机部份分部实验”

3.将K8、K9、K10、K11置1

4.将11H写入R0寄存器

5.将22H写入R1寄存器

6.将33H写入R2寄存器

7.将44H写入R3寄存器

8.读R0寄存器

9.读R1寄存器

10.读R2寄存器

11.读R3寄存器

12.

五、实验结果、分析、总结

1.实验结果与分析

2.实验总结

了解了寄存器R0、R1、R2、R3的组成原理,还有如何操作、如何使用,同时,激发了我对计算机的兴趣。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1101215020FFFF_8FFE0 0正确

12010758220000_6FF20 0正确

1300e86022FFFF_900E0 0正确

14012c6824FFFF_800E0 0正确

15012c7025FFFF_9FFF0 0正确

1600c778250000_FFFF 0 0正确

一、实验程序源代码

顶层LED测试模块:

module Top_LED(clk,rst,SW,LED);

input clk,rst;

input [2:0]SW;

output reg[7:0]LED;

wire ZF,OF;

wire [31:0]ALU_F;

top_R_cpu test_cpu(rst,clk,ZF,OF,ALU_F);

// Instantiate the Unit Under Test (UUT)

top_R_cpu uut (

.rst(rst),

.clk(clk),

.ZF(ZF),

.OF(OF),

.F(F)

);

initial begin

// Initialize Inputs

rst = 0;

clk = 0;

// Wait 100 ns for global reset to finish

NET "LED[5]" LOC = N11;

NET "LED[4]" LOC = M11;

NET "LED[3]" LOC = V15;

NET "LED[2]" LOC = U15;

NET "LED[1]" LOC = V16;

NET "LED[0]" LOC = U16;

NET "SW[2]" LOC = V9;

6'b000100:ALU_OP=3'b111;

endcase

write_reg=1;

end

end

endmodule

PC取指令模块:

module pc(input clk,input rst,output [31:0]Inst_code);

reg [31:0]PC;

wire[31:0]PC_new;

input [4:0]R_Addr_A;

input [4:0]R_Addr_B;

input [4:0]W_Addr;

input Write_Reg;

input [31:0]W_Data;

input Clk;

input Reset;

output [31:0]R_Data_A;

output [31:0]R_Data_B;

initial

PC<=32'h00000000;

Inst_ROM Inst_ROM1 (

.clka(clk),

.addra(PC[7:2]),

.douta(Inst_code)

);

assign PC_new={24'h000000,PC_new[7:0]};

always@(negedge clk or posedge rst)

R_Data_A,R_Data_B);

ALU ALU_connect(R_Data_A,R_Data_B,F,ALU_OP,ZF,OF);

always@(*)

begin

write_reg=0;

ALU_OP=0;

if(Inst_code[31:26]==0)

begin

case(Inst_code[5:0])

always@(posedge Clk or posedge Reset)

begin

if(Reset)

for(i=0;i<=31;i=i+1)

REG_Files[i]=0;

else

if(Write_Reg&&W_Addr!=0)

REG_Files[W_Addr]=W_Data;

end

endmodule

6'b100000:ALU_OP=3'b100;

6'b100010:ALU_OP=3'b101;

6'b100100:ALU_OP=3'b000;

6'b100101:ALU_OP=3'b001;

6'b100110:ALU_OP=3'b010;

6'b100111:ALU_OP=3'b011;

6'b101011:ALU_OP=3'b110;

begin

if(rst)

PC=32'h00000000;

else PC=PC_new;

end

endmodule

寄存器堆模块:

module Register_file(R_Addr_A,R_Addr_B,W_Addr,Write_Reg,W_Data,Clk,Reset,R_Data_A,R_Data_B);

3'b110:

if(A<B)

F=1;

else

F=0;

3'b111:F=B<<A;

endcase

if(F==0)

ZF=1;

else

ZF=0;

end

endmodule

测试代码:

module test;

// Inputs

reg rst;

reg clk;

// Outputs

wire ZF;

wire OF;

wire [31:0] F;

NET "SW[1]" LOC = T9;

NET "SW[0]" LOC = T10;

NET "clk" LOC = C9;

NET "rst" LOC = C4;

五、思考与探索

(1)R型指令CPU实验结果记录表

序号指令执行结果标志结论

1 0000827 FFFFFFFF 0 0正确

20001102b0000_00010 0正确

ALU算术逻辑运算单元模块:

module ALU(A,B,F,ALU_OP,ZF,OF);

input [31:0]A,B;

input [2:0]ALU_OP;

output reg ZF,OF;

output reg[31:0]F;

reg C32;

always@(*)

begin

OF=1'b0;

C32=1'b0;

default:LED=0;

endcase

end

endmodule

顶层R型CPU模块:

module top_R_cpu(input rst,input clk,output ZF,output OF,output [31:0]F);

reg write_reg;

wire [31:0]Inst_code;

3004218200000_00020 0正确

4006220200000_00030 0正确

5008328200000_00050 0正确

600a330200000_00070 0正确

7004638040000_000E0 0正确

800a648200000_000C0 0正确

9012640040000_70000 0正确

always@(*)

begin

case(SW)

3'b000:LED=ALU_F[7:0];

3'b001:LED=ALU_F[15:8];

3'b010:LED=ALU_F[23:16];

3'b011:LED=ALU_F[31:24];

3'b100:begin LED[7:2]=0;LED[1]=OF;LED[0]=ZF;end

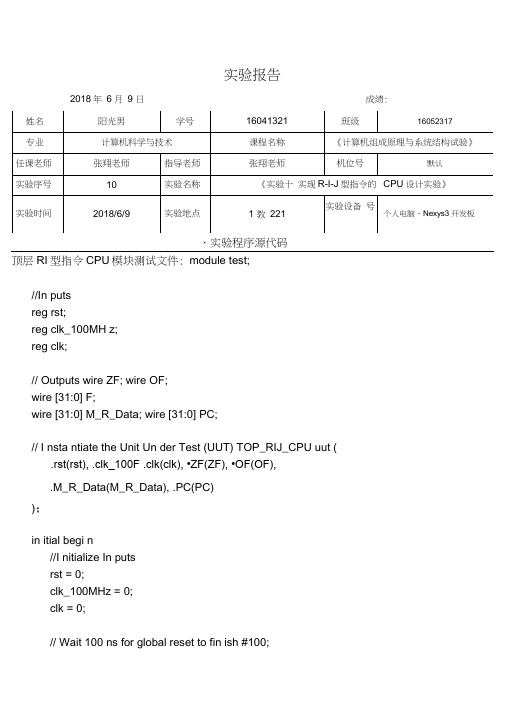

实验报告

2018年6月1日成绩:

姓名

阳光男

学号

16041321

班级

16052317

专业

计算机科学与技术

课程名称

《计算机组成原理与系统结构试验》

任课老师

张翔老师

指导老师

张翔老师

机位号

无

实验序号

8

实验名称

《实验八实现R型指令的CPU设计实验》

实验时间

2018/5/25

实验地点

1教225

实验设备号

个人电脑

#100;

clk=1;

// Add stimulus here

forever

begin

#50;

clk=~clk;

end

end

endmodule

二、仿真波形

三、电路图

顶层电路模块

顶层电路内部结构:

四、引脚配置(约束文件)

NET "LED[7]" LOC = T11;

NET "LED[6]" LOC = R11;

reg [31:0]REG_Files[0:31];

reg [5:0]i;

initial//仿真过程中的初始化

begin

for(i=0;i<=31;i=i+1)

REG_Files[i]=0;

end

assign R_Data_A=REG_Files[R_Addr_A];

assign R_Data_B=REG_Files[R_Addr_B];

wire [31:0]R_Data_A;

wire [31:0]R_Data_B;