实验一 1位全加器的设计

一位全加器VHDL的设计实验报告

EDA技术及应用实验报告——一位全加器VHDL的设计班级:XXX姓名:XXX学号:XXX一位全加器的VHDL设计一、实验目的:1、学习MAX+PLUSⅡ软件的使用,包括软件安装及基本的使用流程。

2、掌握用VHDL设计简单组合电路的方法和详细设计流程。

3、掌握VHDL的层次化设计方法。

二、实验原理:本实验要用VHDL输入设计方法完成1位全加器的设计。

1位全加器可以用两个半加器及一个或门连接构成,因此需要首先完成半加器的VHDL设计。

采用VHDL层次化的设计方法,用文本编辑器设计一个半加器,并将其封装成模块,然后在顶层调用半加器模块完成1位全加器的VHDL设计。

三、实验内容和步骤:1、打开文本编辑器,完成半加器的设计。

2、完成1位半加器的设计输入、目标器件选择、编译。

3、打开文本编辑器,完成或门的设计。

4、完成或门的设计输入、目标器件选择、编译。

5、打开文本编辑器,完成全加器的设计。

6、完成全加器的设计输入、目标器件选择、编译。

7、全加器仿真8、全加器引脚锁定四、结果及分析:该一位加法器是由两个半加器组成,在半加器的基础上,采用元件的调用和例化语句,将元件连接起来,而实现全加器的VHDL编程和整体功能。

全加器包含两个半加器和一或门,1位半加器的端口a和b分别是两位相加的二进制输入信号,h是相加和输出信号,c是进位输出信号。

构成的全加器中,A,B,C分别是该一位全加器的三个二进制输入端,H是进位端,Ci是相加和输出信号的和,下图是根据试验箱上得出的结果写出的真值表:信号输入端信号输出端Ai Bi Ci Si Ci0 0 0 0 00 0 1 1 00 1 0 1 00 1 1 0 11 0 0 1 01 0 1 0 11 1 0 0 11 1 1 1 1。

一位全加器的设计

一位全加器的设计一.实验目的1.掌握原理图输入设计。

2.利用一位半加器实现一位全加器。

二.实验原理1.一位半加器输入a,b;输出co,so;其中co为进位输出;so为和的输出;真值表如下图所示。

2.一位全加器真值表如下图所示。

三.实验内容1.以原理图输入作为设计输入,设计半加器。

2.利用设计好的半加器,实现全加器的设计。

3.通过仿真,观察设计的正确性。

4.仿真完成后,将原理图设计转换为VHDL文件。

四.设计提示仔细阅读真值表,思考如何将半加器设计为全加器。

五.实验报告要求1.写出原理图设计。

(半加器电路原理图)(全加器原理图)2.分析设计过程。

用两个半加器构成全加器。

3.记录仿真波形,保存生成的元件以及RTL,将原理图文件转变为VHDL文件。

(全加器仿真图)(符号元件)(全加器RTL)(全加器VHDL文件)LIBRARY ieee;USE ieee.std_logic_1164.all;LIBRARY work;ENTITY quan2 ISPORT(a : IN STD_LOGIC;b : IN STD_LOGIC;c : IN STD_LOGIC;ci : OUT STD_LOGIC;si : OUT STD_LOGIC);END quan2;ARCHITECTURE bdf_type OF quan2 ISCOMPONENT quanPORT(a : IN STD_LOGIC;b : IN STD_LOGIC;co : OUT STD_LOGIC;so : OUT STD_LOGIC);END COMPONENT;SIGNAL SYNTHESIZED_WIRE_0 : STD_LOGIC;SIGNAL SYNTHESIZED_WIRE_1 : STD_LOGIC;SIGNAL SYNTHESIZED_WIRE_2 : STD_LOGIC;BEGINb2v_inst : quanPORT MAP(a => a,b => b,co => SYNTHESIZED_WIRE_2,so => SYNTHESIZED_WIRE_0);b2v_inst1 : quanPORT MAP(a => SYNTHESIZED_WIRE_0,b => c,co => SYNTHESIZED_WIRE_1,so => si);ci <= SYNTHESIZED_WIRE_1 OR SYNTHESIZED_WIRE_2;END bdf_type;4.书写实验报告时要结构合理,层次分明,在分析描述的时候,注意语言的流畅。

实验一 1位二进制全加器的设计

实验一基于原理图输入法的1位二进制全加器的设计一、实验目的1、学习、掌握QuartusⅡ开发平台的基本使用。

2、学习基于原理图输入设计法设计数字电路的方法,能用原理图输入设计法设计1位二进制半加器、1位二进制全加器。

3、学习EDA-V型实验系统的基本使用方法。

二、实验内容1、根据1位二进制半加器、1位二进制全加器的真值表,设计并画出1位二进制半加器的原理框图,由半加器及门电路设计并画出1位二进制全加器的原理框图(最终设计的是1位二进制全加器)。

2、用QuartusⅡ原理图输入输入法输入1位二进制半加器的原理框图,并进行编译。

如有输入错误,修改后再进行编译。

4、根据1位二进制半加器的工作原理,选择输入合适的输入信号和波形及其输出信号,进行仿真,得到器件的输入与输出波形,验证设计是否正确。

5、创建1位二进制半加器的的元件图形符号。

6、用QuartusⅡ原理图输入输入法输入1位二进制半加器的原理框图(要求用半加器及门电路设计),并进行编译,仿真。

7、确定实验箱电源关闭的情况下,连接好下载线,然后打开实验箱电源,对器件进行编程下载。

8、编程下载成功后,关闭实验箱电源,拆除下载线,按器件引脚设定及功能要求,连接好各测试线,进行硬件测试验证。

三、实验预习要求1、学习、掌握QuartusⅡ的基本使用,学习本EDA-V实验开发系统。

2、根据1位二进制半加器、1位二进制全加器的真值表,设计并画出1位二进制半加器的原理框图,由半加器及门电路设计并画出1位二进制全加器的原理框图。

3、根据1位二进制半加器、1位二进制全加器的工作原理,设计并画出它们的输入、输出的理论工作波形。

4、初步制定全加器的引脚锁定。

四、实验要求1、实验原理中详细写出1位二进制半加器、1位二进制全加器的设计过程,及它们的输入、输出的理论工作波形。

2、根据实验内容,详细写出实验的各个步骤,方法。

3、记录实验现象或波形,并与理论值比较、分析。

(如仿真波形与理论工作波形的比较分析,硬件测试与理论真值表的比较分析)。

实验一 1位全加器的设计(修改后)

• 步骤三:编辑全加器的原理图: 步骤三:编辑全加器的原理图:

• 由file->new,打开原理图文件Block Diaoram/Schematic File,并存盘为full_adder.bdf

左键双击原理图编辑窗空白处,弹出如下窗口

• 调入 1)半加器:half_adder, 2)二输入或门:2or, 3)输入,输出引脚

实验一 1位全加器的设计 位全加器的设计

一位全加器的原理分析

• 一位全加器可由两个一位半加器与一个或 门构成,其原理图如下图。

该设计利用层次结构描述法, • 首先设计半加器电路,将其打包为半加器 模块; • 然后在顶层调用半加器模块 半加器模块和ALTERA提供 半加器模块 的二输入或门 输入或门组成全加器电路; 输入或门 • 最后将全加器电路编译下载到实验箱,

输入是 两个加数:ain,bin, 一个进位:cin 这三个输入数据是1位(1bit),可由DE2的 SW0,SW1,SW2提供 为了显示更加清楚,可以将ain,bin,cin的输出引 出到DE2上的红色发光二极管显示,可选用 LEDR0,LEDR1,LEDR2. 输出是: 输出是: 和:sum 进位:cout 输出可由DE2的绿色发光二极管显示,可选用 LEDG0,LEDG1

• 步骤一:建立full_adder的工程 (project)

新建立full_adder工程(project)

设置project相关参数

• 设置project放置的位置及其名称,随后按 Next继续

• 添加文件到工程(project)中,在无相关文件需要 添加的情况下,按Next继续

• 选择FPGA目标器件,根据DE2的平台情况,选 择cyclone II系列的EP2C35F672C6,继续

实验一1 1位全加器的设计

实验一1位全加器的设计一、实验目的1.熟悉ISE软件的使用;2.熟悉下载平台的使用;3.掌握利用层次结构描述法设计电路。

二、实验原理及说明由数字电路知识可知,一位全加器可由两个一位半加器与一个或门构成,其原理图如图1所示。

该设计利用层次结构描述法,首先设计半加器电路,将其打包为半加器模块;然后在顶层调用半加器模块组成全加器电路;最后将全加器电路编译下载到实验板,其中a,b,cin 信号可采用实验箱上SW0,SW1,SW2键作为输入,输出sum,cout信号采用发光二极管LED3,LED2来显示。

图1 全加器原理图三、实验步骤1.在ISE软件下创建一工程,工程名为full_adder,工程路径在E盘,或DATA盘,并以学号为文件夹,注意不要有中文路径,注意:不可将工程放到默认的软件安装目录中。

芯片名为Spartan3E系列的XC3S500E-PQG2082.新建Verilog HDL文件,首先设计半加器,输入如下源程序;module half_adder(a,b,s,co);input a,b;output s,co;wire s,co;assign co=a & b;assign s=a ^ b;endmodule3.保存半加器程序为half_adder.v,通过HDL Bench画仿真波形,获得仿真用激励文件,随后进行功能仿真、时序仿真,验证设计的正确性,观察两种仿真波形的差异。

4.在Design窗口中,选择Design Utilities→Create Schematic Symbol创建半加器模块;5.新建一原理图(Schematic)文件,在原理图中调用两个半加器模块、一个或门模块,按照图1所示连接电路,并连接输入、输出引脚。

完成后另保存full_adder.sch。

6.对设计进行综合,如出现错误请按照错误提示进行修改。

7.HDL Bench画仿真波形,获得仿真用激励文件,分别进行功能与时序仿真,验证全加器的逻辑功能,观察两类波形的差异。

FPGA一位全加器设计实验报告

FPGA一位全加器设计实验报告

本实验的目的是学习使用FPGA设计一个全加器,通过实践掌握FPGA硬件描述语言和数字电路设计的一些基础知识和技能。

一、实验背景

数字逻辑电路是计算机硬件的基础,而硬件描述语言是数字电路设计的重要手段。

FPGA是可编程逻辑器件,它可以根据用户的需求进行编程,实现不同的数电逻辑电路。

全加器是组成加法器的重要单元,也是我们学习数字逻辑的重要基础。

二、实验设计

本实验我们将采用Verilog硬件描述语言来设计一个全加器。

代码如下:

module full_add(

input A,B,Cin,

output S,Cout

);

wire w1,w2,w3;

xor(S,w1,A^B);//A异或B

xor(Cout,w2,A&Cin);//A与Cin之后异或

xor(w3,B&Cin,A&Cin);//B与Cin之后异或

xor(Cout,Cout,w3);//再次异或

endmodule

三、测试结果

我们使用Quartus II软件进行仿真和综合。

通过对代码的仿真和波形分析,我们发现该全加器符合设计要求,并且可以正确地输出结果。

四、实验总结

本实验我们学习了FPGA硬件描述语言,掌握了数字电路设计的一些基础知识和技能。

通过设计全加器,我们更深入地理解了数字逻辑电路的原理和应用。

希望在今后的学习中,能够继续深入研究数字电路的知识,为我们掌握计算机硬件设计打下坚实的基础。

EXP01实验一 一位全加器设计

实验一一位全加器电路设计实验目的:1.熟悉EDA软件开发工具(MAX+plus II)的基本操作;2.熟悉KHF-4型CPLD/FPGA实验箱的板上资源分布。

3. 以原理图方式设计一位全加器,进行软件仿真、下载和硬件测试。

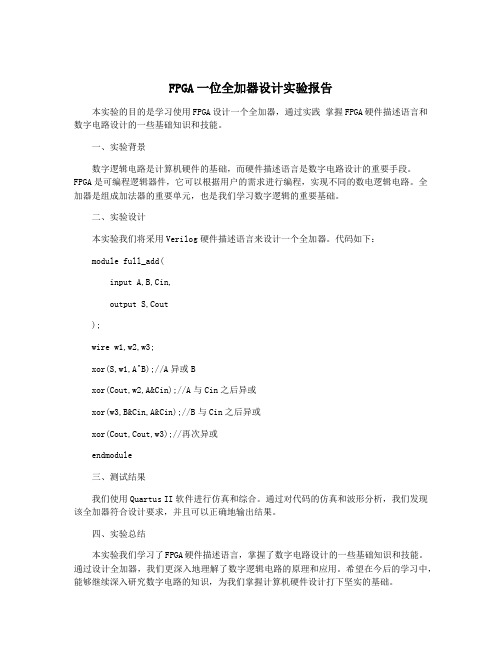

实验设备:微型计算机一台、KHF-4型实验箱一个实验原理:全加器原理图和真值表分别如图1和表1所示:图1. 半加器原理图表1. 半加器真值表全加器原理图和真值表分别如图2和表2所示:图2. 全加器原理图表2. 全加器真值表实验步骤:1)打开MAX+plus II设计软件。

2)新建图形编辑文件(File/New/Graphic Edit file),在文件空白处双击鼠标左键(或选择菜单Symbol/Enter Symbol)打开添加符号对话框(Enter Symbol),在“Symbol Libraries”框中双击选择“../maxplus2/max2lib/prim”库,在Symbol Files添加半加器原理图中各元件、输入(input)和输出(output)管脚,修改管脚名称后完成半加器原理图的绘制如图1;保存文件到具体设计目下。

图3.新建文件、添加符号和保存文件3)将半加器文件设为顶层文件(File/Project/Set Project to Current File),打开编译器(MAX+plus II/Complier)进行编译综合。

图4.设为顶层和编译4)创建半加器符号(File/Creat Default Symble)。

5)新建图形编辑文件(File/New/Graphic Edit file),在文件空白处双击鼠标左键打开添加符号对话框(Enter Symbol),从“File Symbol”框中调用半加器符号,完成全加器原理图的绘制如图2,保存文件到具体设计目录。

6)将全加器文件设为顶层文件,打开编译器进行编译综合。

7)新建波形编辑文件(File/New/Waveform Edit file),添加节点信号(在Name下点击鼠标右键选择Enter Nodes from SNF…)并编辑输入信号波形;保存(File/Save)波形文件(按默认文件名点击OK保存)。

1位全加器电路设计

1位全加器电路设计全加器是一种组合逻辑电路,用于将两个二进制数相加,并输出和及进位。

一个1位全加器包含两个输入(被加数和加数)和两个输出(和和进位)。

全加器具有一个额外的输入(进位输入)来接收来自上一位的进位。

一个1位全加器可以使用与门(AND)、异或门(XOR)和或门(OR)来实现。

设计思路如下:1.将两个输入(被加数和加数)分别与一个异或门(XOR)连接,得到一个输出(和)。

2.将两个输入(被加数和加数)分别与一个与门(AND)连接,得到一个输出(进位)。

3.将两个输入的与门(AND)的输出(进位)与进位输入进行异或运算,得到最终的进位输出。

4.将输出(和)和最终进位输出作为全加器的输出。

下面是我对1位全加器的详细设计:首先,我们需要定义输入和输出信号:输入信号:A, B, Cin(被加数,加数,进位输入)输出信号:S, Cout(和,进位输出)接下来,我们可以按照设计思路,逐步实现1位全加器:Step 1: 设计异或门(XOR)的电路将输入A和B连接到一个异或门,得到一个信号X(X=AXORB)Step 2: 设计与门(AND)的电路将输入A和B连接到一个与门,得到一个信号Y(Y=AANDB)Step 3: 设计第一个异或门(XOR)的电路将信号X和进位输入Cin连接到一个异或门,得到一个信号Z(Z = X XOR Cin)Step 4: 设计与门(AND)的电路将信号X和进位输入Cin连接到一个与门,得到一个信号CarryOut (CarryOut = X AND Cin)Step 5: 设计或门(OR)的电路将信号Y和信号CarryOut连接到一个或门,得到输出信号Cout (Cout = Y OR CarryOut)Step 6: 设计或门(OR)的电路将信号X和信号Z连接到一个或门,得到输出信号S(S=XORZ)最后,我们将输入A、B和Cin以及输出S、Cout连接到1位全加器的电路中,即可实现1位全加器。

实验一--一位全加器的原理图设计【范本模板】

桂林电子科技大学实验报告2015-2016学年第二学期开课单位海洋信息工程学院适用年级、专业13级电子信息工程课程名称EDA技术与应用主讲教师覃琴实验名称一位全加器学号1316030515姓名魏春梅实验一一位全加器的原理图设计一、实验目的①掌握Quartus II原理图输入法的编辑、编译(综合)、仿真和编程下载的操作过程.②用原理图输入法设计全加器电路,并通过电路仿真和硬件验证,进一步了解全加器的功能.③熟悉EDA实训仪的使用方法。

二、实验原理考虑来自低位来的进位的加法运算称为”全加”,能实现全加运算的电路称为全加器.1位全加器的真值表如表1。

1所列,表中的A、B是两个一位二进制加数的输入端。

CI是来自低位来的进位输入端。

SO是和数输出端,CO是向高位的进位输出端。

根据真值表写出电路输出与输入之间的逻辑关系表达式为:A B CI SO CO三、实验设备①EDA实训仪1台.②计算机1台(装有Quartus II软件)。

四、实验内容在Quartus II软件中,采用原理图输入法设计1位的全加器电路,编辑、编译(综合)、仿真,引脚锁定,并下载到EDA实训仪中进行验证。

注:用EDA实训仪上的拨动开关S1、S2、SO分别作为加数A、加数B、低位进位输入端CI,用发光二极管L1、L0分别作为和输出端SO、仅为输出端CO。

五、实验预习要求①查阅资料,复习有关全加器的内容,并认真阅读实验指导书,分析、掌握实验原理.②预习理论课本有关Quartus II软件的使用方法,并简要地写出Quartus II软件的操作步骤。

③复习数字逻辑电路有关全加器的内容,设计1位全加器的逻辑电路图。

1、实验电路图路径:E/1316030515/adder2、实验波形仿真图路径:E/1316030515/adder3、实验结果图六、实验总结①用Quartus II软件的原理图输入法进行数字电路设计的方法及步骤。

1、建立工程项目(文件夹、工程名、芯片选择);2、编辑设计文件(元件、连线、输入输出、检查电路正确性);3、时序仿真(波形验证设计结果);4、引脚锁定(参考文件锁定输入输出引脚);5、编译下载;6、硬件调试。

FPGA一位全加器设计

实验一一位全加器的设计一. 实验目的1.熟悉QUARTUSII软件的使用;2.熟悉实验硬件平台的使用;3.掌握利用层次结构描述法设计电路。

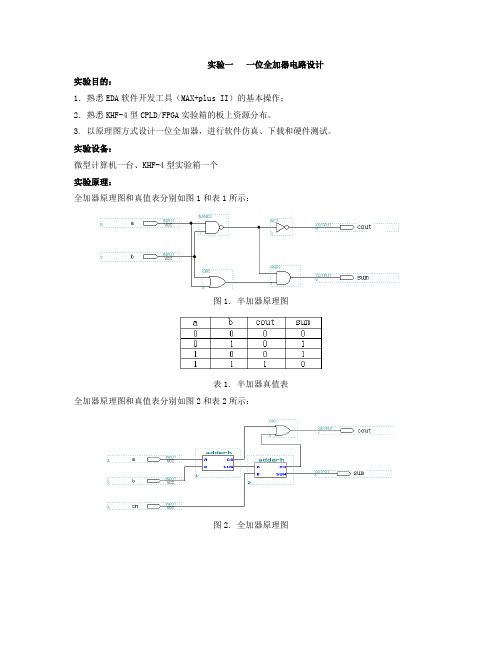

二. 实验原理三.由于一位全加器可由两个一位半加器与一个或门构成, 首先设计半加器电路, 将其打包为半加器模块;从输出的波形图来验证半加器正确性, 然后在顶层调用半加器模块组成全加器电路;。

从全加器的波形图来验证全加器正确性。

四.实验步骤1.在QUARTUSII软件下创建一工程, 工程名为full_adder, 芯片名为****(查看硬件平台);新建Verilog语言文件, 输入如下半加器Verilog语言源程序;module half_adder(a,b,s,co);input a,b;output s,co;wire s,co;assign co=a & b;assign s=a ^ b;Endmodule保存半加器程序为half_adder.v, 进行功能仿真、时序仿真, 验证设计的正确性。

其初始值、功能仿真波形和时序仿真波形分别如下所示仿真前的波形:仿真后的波形:4.选择菜单File→Create/Update →Create Symbol Files for current file, 创建半加器模块;5.新建一原理图文件, 在原理图中调用半加器、或门模块和输入, 输出引脚, 按照图1所示连接电路。

并将输入ain,bin,cin连接到FPGA的输出端, 便于观察。

完成后另保存full_adder。

电路图如下6.对设计进行全编译, 然后分别进行功能与时序仿真, 验证全加器的逻辑功能。

其初始值、功能仿真波形和时序仿真波形分别如下所示四.思考题为什么在实验步骤3中, 将半加器保存为half_adder, 可否保存为full_adder?答:不能, 因为在程序中, module half_adder(a,b,s,co)已经给程序定义了一个名字叫half_adder, VHDL语言中, 要求程序名与实体名一致, 因此保存的文件名必须和程序名一致, 否则在编译程序的时候就会出现错误。

实验1 1位全加器设计

实验1 一位全加器设计【实验目的】1.掌握数字电路的两种设计方法2.掌握在Cadence中绘制原理图的方法3.掌握芯片外围特性与实现硬件电路4.掌握Verilog HDL设计电路的方法。

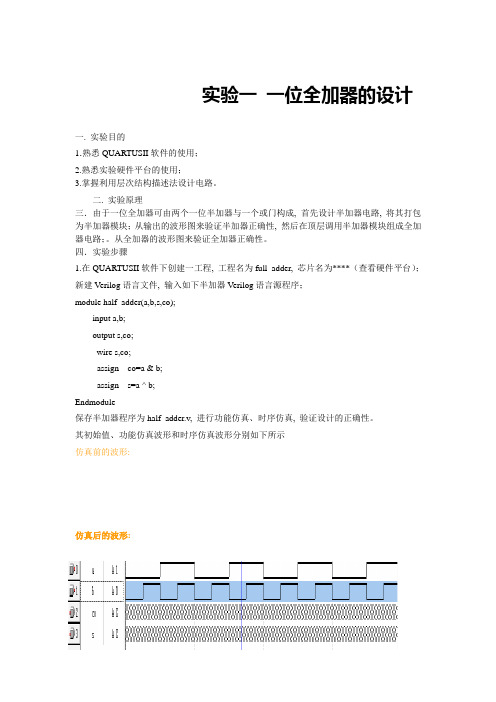

【实验内容】1.设计1位全加器2.绘制1位全加器原理图3.在面包板上实现1位全加器设计4.用Verilog HDL行为描述法设计实现1位全加器并仿真【实验器件】1.异或门电路74HC86一片,内含四个异或门,异或门的引脚封装图与内部原理如图1-1所示。

图1-1 异或门74HC86的内部原理图与芯片封装图2.与门电路芯片74HC08一片,内含四个与门,与门的引脚封装图与内部原理如图1-2所示。

图1-2与门74HC08的内部原理图与芯片封装图3.或门电路芯片74HC32一片,内含四个或门,或门的引脚封装图与内部原理如图1-3所示。

图1-3或门74HC32的内部原理图与芯片封装图4.3个1k的电阻和两个发光二极管,一个8路开关,5v电源,面包板一块,导线若干条。

【实验步骤】1.设计1位全加器1)设1位全加器的输入为被加数为A,加数B,低位进位Cin;输出为本位和Sum,对高位的进位为Cout。

2)根据1位加法器的运算{Cout,Sum}=A+B+Cin列真值表如表吗-1所示。

表1-1 1位加法器真值表3)根据真值表列出逻辑表达式CinBACinBACinBACinBABACinABBAABCinCinBACinBACinBASum⊕⊕=⊕+⊕=+++=+++=)()()()(ABCinBAABCinCinABCinBABCinACout+⊕=+++=)(4)手动绘制该原理图,为电路加上开关控制数据输入,用发光二极管显示输出,电路图如图1-4所示。

图1-4 1位全加器原理图2.在实验板上连接实现该电路并分析电路元件构成3.在protel软件中绘制原理图1)绘制元件符号2)绘制原理图4. .在protel软件中绘制pcb1)封装绘制2)pcb绘制。

1位全加器原理图输入设计

实验步骤

(6)波形文件存盘。 (7)运行仿真器。 (注意,刚进入窗口时,应该将最下方的滑标拖 向最左侧,以便可观察到初始波形)。 (8)观察分析波形。 MAX+plusII项及其中的Timing Analyzer选 项,点击跳出的分析器窗口中的Start键。

实验步骤

6. 包装元件入库 7. 设计顶层文件 (1)仿照前面的“步骤2”,打开一个新的原理图 编辑窗,然后在元件输入窗的本工程目录中找到 已包装好的半加器元件,并将它调入原理图编辑 窗中。这时如果对编辑窗中的半加器元件双击, 即刻弹出此元件内部的原理图。 (2)完成全加器原理图设计。 (3)将当前文件设置成Project。

实验步骤

最后启动编译器,首先选择左上角MAX+plusII 选项,在其下拉菜单中选择编译器项Compiler。 点击Start,开始编译!如果发现有错,排除错误 后再次编译。 5. 时序仿真 (1)建立波形文件。选菜单 FileNew,再选择 Waveform Editer..项,打开波形编辑窗。

实验步骤

首先在Assign选项的下拉菜单中选择器件选择项 Device,此窗口的Device Family是器件序列 栏,应该首先在此拦中选定目标器件对应的序列 名,为了选择EPF10K10LC84-4器件,应将此 栏下方标有Show only Fastest Speed Grades 的勾消去以便显示出所有速度级别的器件。完成 器件选择后,按OK键。

一位全加器_可编程逻辑器件VHDL实验报告

1.一位全加器实验报告一、实验目的要求学习计数器的设计、仿真和硬件测试,进一步熟悉VHDL设计技术。

设计程序独立完成全加器的仿真。

全加器由两个半加器组合而成,原理类似。

半加器不考虑低位进位,但有高位进位;全加器要考虑低位的进位且该进位和求和的二进制相加,可能获得更高的进位。

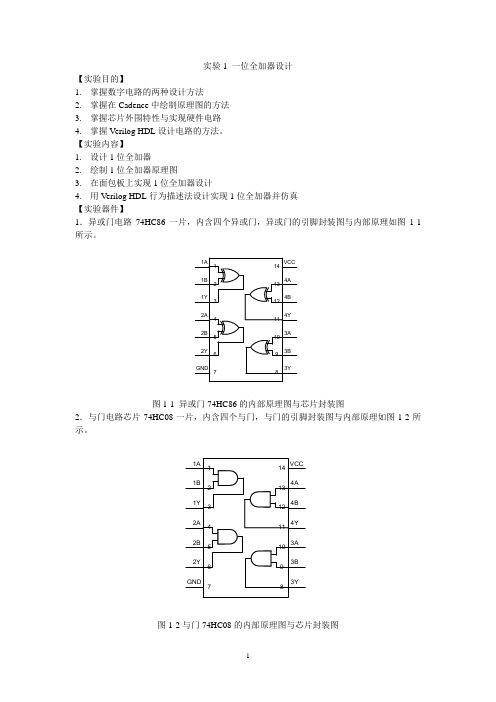

二、设计方法与原理图图1是一个一位二进制全加器电路图,由图1所示,由两个半加器和一个或门构成一个一位二进制全加器;ain,bin为全加器的输入端,cin为全加器的低位进位,sum是全加器的全加和,cout是全加器的全加进位端;从而实现一位二进制全加器。

(图1)一位二进制全加器原理图三、实验内容按照教材上的步骤,在max plus II上进行编辑、编译、综合、适配、仿真。

说明例中各语句的作用,详细描述示例的功能特点,给出其所有信号的时序仿真波形。

四、源程序library ieee;use ieee.std_logic_1164.all;entity full_adder isport(a,b,cin:in std_logic;cout,sum:out std_logic);end entity full_adder;architecture fd1 of full_adder iscomponent h_adderport(a,b:in std_logic;co,so:out std_logic);end component;component or2aport(a,b:in std_logic;c:out std_logic);end component;signal d,e,f:std_logic;beginu1:h_adder port map(a=>ain,b=>bin,co=>d,so=>e); u2:h_adder port map(a=>e,b=>cin,co=>f,so=>sum); u3:or2a port map(a=>d,b=>f,c=>cout);end fd1;五过程性截图六、仿真结果(图2)一位二进制全加器仿真结果七、分析结果与总结由图2,本实验的目标已达成,及通过编写VHDL语言实现一个一位二进制全加器。

实验一一位二进制全加器设计实验

大学实验报告学生: 学 号: 专业班级: 中兴101实验类型:■ 验证 □ 综合 □设计 □ 创新 实验日期: 2012 9 28 实验成绩:实验一 一位二进制全加器设计实验一.实验目的(1)掌握Quartus II 的VHDL 文本设计和原理图输入方法设计全过程; (2)熟悉简单组合电路的设计,掌握系统仿真,学会分析硬件测试结果; (3) 熟悉设备和软件,掌握实验操作。

二.实验容与要求(1)在利用VHDL 编辑程序实现半加器和或门,再利用原理图连接半加器和或门完成全加器的设计,熟悉层次设计概念;(2)给出此项设计的仿真波形;(3)参照实验板1K100的引脚号,选定和锁定引脚,编程下载,进行硬件测试。

三.设计思路一个1位全加器可以用两个1位半加器及一个或门连接而成。

而一个1位半加器可由基本门电路组成。

(1) 半加器设计原理能对两个1位二进制数进行相加而求得和及进位的逻辑电路称为半加器。

或:只考虑两个一位二进制数的相加,而不考虑来自低位进位数的运算电路,称为半加器。

图1为半加器原理图。

其中:a 、b 分别为被加数与加数,作为电路的输入端;so 为两数相加产生的本位和,它和两数相加产生的向高位的进位co 一起作为电路的输出。

半加器的真值表为表1 半加器真值表absoco0 0 0 0 0 1 1 0 1 0 1 0 111由真值表可分别写出和数so ,进位数co 的逻辑函数表达式为:b a b a b a so ⊕=+=--(1)ab co = (2)图1半加器原理图(2) 全加器设计原理除本位两个数相加外,还要加上从低位来的进位数,称为全加器。

图2全加器原理图。

全加器的真值表如下:表2全加器真值表c a b co so0 0 0 0 00 0 1 0 10 1 0 0 10 1 1 1 01 0 0 0 11 0 1 1 01 1 0 1 01 1 1 1 1其中a为加数,b为加数,c为低位向本位的进位,co为本位向高位的进位,so为本位和。

数字电路实验报告-组合逻辑电路的设计:一位全加器

Si

Ci

0

0

0

0

0

0

0

1

1

0

0

1

0

1

0

0

1

1

0

1

1

0

0

1

0

1

0

1

0

1

1

1

0

0

1

1

1

1

1

1

描述

一位全加器的表达式如下:

Si=Ai⊕Bi⊕Ci-1

实验仪器

1.电子技术综合实验箱

2.芯片74LS86、74LS08、74LS32

实验内容及步骤

各芯片的管脚图如下图所示:

一位全加器逻辑电路图如下所示:

1.按上图连线

电学实验报告模板

电学虚拟仿真实验室

实验名称

组合逻辑电路的设计:一位全加器

实验目的

1.学习组合逻辑电路的设计方法

2.掌握组合逻辑电路的调试方法

实验原理

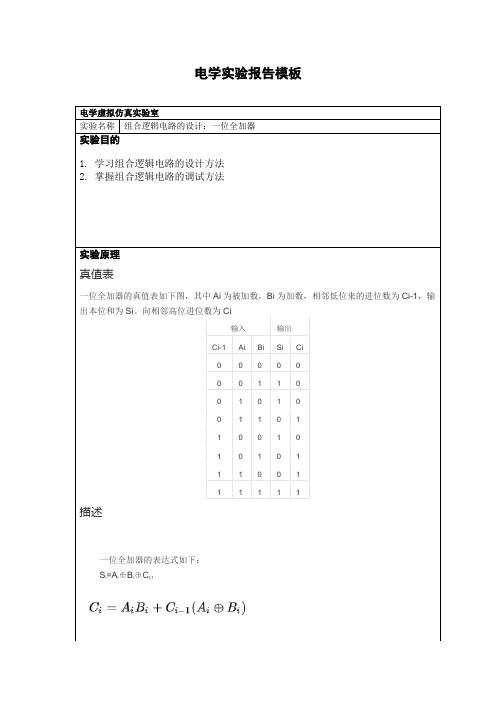

真值表

一位全加器的真值表如下图,其中Ai为被加数,Bi为加数,相邻低位来的进位数为Ci-1,输出本位和为Si。向相邻高位进位数为Ci

输入

输出

Ci-1

Ai

2.测试其逻辑功能,并记录数据

实验结果及分析

实验数据:

Ci-1

Ai

Bi

Si

Ci

0

0

0

0

0

0

0

1

1

0

0

1

0

1

0

0

1

1

0

1

10010 Nhomakorabea1

0

1

0

1

一位全加器 实验报告

一位全加器实验报告一位全加器实验报告引言:全加器是数字电路中常见的一种逻辑电路,用于实现二进制加法运算。

在本次实验中,我们将学习并实现一位全加器电路,并通过实验验证其功能和性能。

实验目的:1. 理解全加器的原理和工作方式;2. 掌握全加器的电路设计和实现方法;3. 验证全加器的功能和性能。

实验器材:1. 电路仿真软件(如Proteus、Multisim等);2. 逻辑门集成电路(如与门、或门、异或门等);3. 连线材料;4. 示波器(可选)。

实验步骤:1. 确定全加器的真值表,包括输入信号和输出结果的对应关系。

例如,输入信号为A、B和进位Cin,输出结果为和S和进位Cout;2. 根据真值表,设计并搭建全加器电路,使用逻辑门集成电路进行布线;3. 使用电路仿真软件进行仿真验证,输入不同的二进制数值,观察输出结果是否符合预期;4. 如有需要,使用示波器观察电路的工作波形,以进一步验证电路的性能。

实验结果与分析:通过实验,我们成功地实现了一位全加器电路,并验证了其功能和性能。

输入不同的二进制数值,我们观察到输出结果与真值表相符,表明电路的逻辑运算正确。

同时,我们还观察到了电路的工作波形,进一步确认了电路的稳定性和响应速度。

结论:本次实验中,我们学习并实现了一位全加器电路,通过实验验证了其功能和性能。

全加器作为数字电路中常见的逻辑电路,具有重要的应用价值。

在实际应用中,全加器可以被组合成更复杂的电路,用于实现多位二进制加法运算。

通过本次实验,我们不仅掌握了全加器的设计和实现方法,还对数字电路的原理和工作方式有了更深入的了解。

展望:在今后的学习和研究中,我们可以进一步深入研究全加器电路的性能优化和扩展。

例如,可以通过引入更高级的逻辑门集成电路,减少电路的延迟和功耗,提高电路的工作速度和效率。

此外,还可以研究全加器电路在其他领域的应用,如计算机算术单元、密码学等。

通过不断的学习和实践,我们将能够更好地理解和应用数字电路中的全加器。

EDA实验一 1位全加器和四位全加器的设计

实验一1位全加器和四位全加器的设计一、实验目的1、掌握Quartus Ⅱ6.0软件使用流程。

2、初步掌握VHDL的编程方法。

3、掌握图形层次设计方法;4、掌握全加器原理,能进行多位加法器的设计。

二、实验原理(一位全加器的逻辑表达式为:sum=a^b^Cl;Ch= a&b|(a^b)&Cl.(2)四位加法器加法器是数字系统中的基本逻辑器件。

多位加法器的构成有两种方式:并行进位和串行进位方式。

并行进位加法器设有并行进位产生逻辑,运算速度快;串行进位方式是将全加器级联构成多位加法器。

通常,并行加法器比串行级联加法器占用更多的资源,并且随着位数的增加,相同位数的并行加法器比串行加法器的资源占用差距也会越来越大。

三、实验连线(1)一位全加器1、将EP2C5适配板左下角的JTAG用十芯排线和万用下载区左下角的SOPC JTAG 口连接起来,万用下载区右下角的电源开关拨到SOPC下载的一边2、将JPLED1短路帽右插,JPLED的短路帽全部上插。

3、请将JP103的短路帽全部插上,,打开实验箱电源。

( 2 ) 四位加法器1、将EP2C5适配板左下角的JTAG用十芯排线和万用下载区左下角的SOPC JTAG 口连接起来,万用下载区右下角的电源开关拨到SOPC下载的一边2、JPLED1短路帽右插,JPLED的短路帽全部上插。

3、请将JP103的短路帽全部插上,,打开实验箱电源。

四、实验代码LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;ENTITY fulladder ISPORT(A,B,C1 :IN STD_LOGIC;CH,SUM : OUT STD_LOGIC);END ENTITY fulladder;ARCHITECTURE ADO OF fulladder isSIGNAL AB :STD_LOGIC;BEGINSUM<=A XOR B XOR C1;AB<=A XOR B;CH<=(A AND B) OR (AB AND C1);END ARCHITECTURE ADO;一位全加器波形如下:图4-1四位加法器波形如下:图4-2五、实验仿真过程SW1,SW2,SW3对应a,b,Cl;D101,D102分别对应sum和Ch,当结果为0时彩色LED灯熄灭,当结果为1时彩灯点亮,改变SW1,SW2,SW3的输入状态,观察实验结果。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

• 激励文件生成:由file->new,打开如下选项框,选择 Other Files中的Vector Waveform File :

• 由Edit->end time,打开如下对话框,选择 仿真时间区域,这次实验选择1us,然后点ok

• 点击保存,将波形文件存盘为half_adder.vwf:

• 步骤四:锁定引脚,下载 • 锁定引脚,参考DE2的引脚说明文件 DE2_pin_assignments

To ain bin cut

DE2上的名称 SW[0] SW[1] SW[2] LEDR[0] LEDR[1] LEDR[2] LEDG[0] LEDG[1]

• 也可以将打开的窗口中选择出现在设计中的所有 端口,用鼠标拖至波形编辑窗口:

编辑好波形文件(点击左边 设置a,b的波形,可以自 行选中一段修改),点击保存:

进行功能仿真

• 设置仿真器进行功能仿真: Assignments->setting,选择simulation setting,在 simulation mode中选择functional

Memory • 8-MB SDRAM, 512-KB SRAM, 4-MB Flash • SD memory card slot

Switches, LEDs, Displays, and Clocks • 18 toggle switches • 4 debounced pushbutton switches • 18 red LEDs, 9 green LEDs • Eight 7-segment displays • 16 x 2 LCD display • 27-MHz and 50-MHz oscillators, external SMA clock input

• 步骤一:建立full_adder的工程(project)

新建立full_adder工程(project)

设置project相关参数

• 设置project放置的位置及其名称,随后按 Next继续

• 添加文件到工程(project)中,在无相关文件需要 添加的情况下,按Next继续

• 选择FPGA目标器件,根据DE2的平台情况,选 择cyclone II系列的EP2C35F672C6,继续

• 波动波动开关并观察红色、绿色LED的变化, 验证设计的正确性。

实验一 1位全加器的设计

一位全加器的原理分析

• 一位全加器可由两个一位半加器与一个或 门构成,其原理图如下图。

该设计利用层次结构描述法, • 首先设计半加器电路,将其打包为半加器 模块; • 然后在顶层调用半加器模块和ALTERA提供 的二输入或门组成全加器电路; • 最后将全加器电路编译下载到实验箱,

在library窗口的project下选中创建好的half_adder模 块,并在quartus自带的library中选择需要的其他模 块

可以在左边 里直接输入要 添加的模块,如input、output等

• 用 将各个单元连接起来 • 对输入,输出引脚进行命名。(左键双击 相应模块即可修改)

连接好后,要将top-level改回full_adder,在左边project Navigator窗口下选择files右击full_adder.bdf,在弹出的菜单 中选择set as top-Level entity。然后再编译。

• 将模块的端口信号选入波形编辑框中。打 开view->utility windows->node finder

也可以双击下图所示空白处,在弹出的窗口右 边单击Node finder出现Node finder的选择窗 口

Fitter项选择pins:all,然后点list,左边窗口会 出现端口名称,点>>加入右边窗口后,OK

• 进行时序仿真

• 改变仿真器的设置,Assignments-> setting 选择仿真器设置,更改仿真模式,选择timing:

• 由Processingstart Compilation对设计进行编译 • 由Processingstart simulation得到时序仿真波形。

•

验证half_adder.v设计正确后,将half_adder封 装成一个模块,选择菜单 File→Create/Update→Create Symbol Files for current file,创建半加器模块;供后续的原理图 调用:

• 步骤三:编辑全加器的原理图:

• 由file->new,打开原理图文件Block Diaoram/Schematic File,并存盘为full_adder.bdf

左键双击原理图编辑窗空白处,弹出如下窗口

• 调入 1)半加器:half_adder, 2)二输入或门:2or, 3)输入,输出引脚

• 设置综合,仿真,时序分析软件,在此可以捆绑 第三方工具,本次实验,选用软件自带的工具, 按Next继续

• 设置参数的总结,按Finish完成project的建 立。

• 步骤二:设计half_adder的Verilog模块

• 由File->new,可打开下面的选项,选择 Verilog HDL File,按OK继续

DE2介绍

FPGA • Cyclone II EP2C35F672C6 FPGA and EPCS16 serial configuration device

I/O Devices • Built-in USB Blaster for FPGA configuration • 10/100 Ethernet, RS-232, Infrared port • Video Out (VGA 10-bit DAC) • Video In (NTSC/PAL/Multi-format) • USB 2.0 (type A and type B) • PS/2 mouse or keyboard port • Line-in, Line-out, microphone-in (24-bit audio CODEC) • Expansion headers (76 signal pins)

输入是 两个加数:ain,bin, 一个进位:cin 这三个输入数据是1位(1bit),可由DE2的 SW0,SW1,SW2提供 为了显示更加清楚,可以将ain,bin,cin的输出引 出到DE2上的红色发光二极管显示,可选用 LEDR0,LEDR1,LEDR2. 输出是: 和:sum 进位:cout 输出可由DE2的绿色发光二极管显示,可选用 LEDG0,LEDG1

• 步骤五:下载

• 首次使用,须安装DE2的驱动程序, • 将DE2通过USB端口连接到计算机,并接上电源。(可能 需要关闭杀毒软件) • 由Tools->Programmer,弹出对话框:

• 双击Hardware setup,在弹出的对话框中双击 USB-Blaster,选中下载的硬件

• 选中full_adder.sof,选择Start开始下载:

Location PIN_N25 PIN_N26 PIN_P25 PIN_AE23 PIN_AF23 PIN_AB21 PIN_AE22 PIN_AF22

• 锁定引脚的方法: 方法一:选择Assignments->Assignment Editor,进入编辑窗口,在category栏中选择 Pin,再双击TO栏,分别选择要锁定的引脚 名,并双击Location栏中的New,选择相应 的引脚号

• 在对话框中的simulation input中选择half_adder.vwf, 指定激励文件(一般软件都自行加入了)

• 由Processinggenerat functional simulation netlist 得到功能仿真的网表文件 • 由Processingstart simulation得到功能仿真波形。

• 在打开的空白文档,编辑半加器的Verilog描述,并保存

在左边project Navigator窗口下选择files右击half_adder.v, 在弹出的菜单中选择set as top-Level entity。然后编译。

• 验证half_adder.v的正确与否,进行仿真,一般先 进行功能仿真,再进行时序仿真。 • 为了仿真,首先编辑测试文件。本次实验由于系 统简单,采用对输入信号进行输入波形编辑的方 法得到激励文件

• 锁定引脚方法二: 1)根据DE2_pin_assignments文件内容、 格式制作本设计引脚对应文件的引脚锁定 文件:full_adder.csv 2) 由Assignments->Import Assignment,打 开对话框,调入引脚对应文件即可。

• 仿照半加器的步骤,进行全加器的功能仿 真和时序仿真。得到仿真波形,确认全加 器设计正确。