IC设计中逻辑综合的一般步骤及相关基本概念

逻辑综合

逻辑综合

可逻辑综合的VHDL代码示例

• 异步复位D触发器

DFFA: PROCESS(clk, reset) BEGEN IF (reset = ‘0’) THEN data_out <= (OTHERS => ‘0’); ELSIF (clk’EVENT AND clk = ‘1’) THEN data_out <= data_in; END IF; END PROCESS DFFA;

3

4

5

6

7

8

逻辑综合

• 优化策略

数字电路的设计原则上是分 层次的。最高层(Top-Level) 通常是由互相联系的块组成 右图显示了从VHDL语言到目 标网表的步骤 优化策略包含两项:

• 平面化 • 结构化

technology: mapping netlist in target technology gate level: netlist logical level: boolean equations VHDL description flattening structuring

data_out <= (OTHERS => ‘0’); ELSIF (clk ‘EVENT AND clk = ‘1’) THEN data_out <= in1 XOR in2; END IF; END PROCESS SYNC;

逻辑综合

可逻辑综合的VHDL代码示例

• 带反馈回路的触发器

PROCESS (clk) BEGIN IF (clk ‘EVENT AND clk = ‘1’) THEN IF (ena = ‘1’) THEN data_out <= a; END IF; END IF; END PROCESS;

第7章 ASIC逻辑综合

从上图可以看出,综合是将逻辑电路的寄存器 传输级表现形式转换成为门级网表的表现形式。综 合的输入是寄存器传输级电路描述,综合的输出是 门级网表。寄存器传输级电路描述是对门级网表的 抽象,门级网表是采用实际的逻辑库单元对寄存器 传输级电路的实现。 门级网表主要包含两个部分:第一个部分是实 现逻辑功能的基本逻辑单元及它们之间的连接方式; 第二个部分是这些逻辑单元的时序关系。

asic逻辑综合71综合原理和思想72可综合代码的编写规范73综合步骤74综合的若干问题及解决71综合原理和思想综合简介在集成电路设计领域综合是指设计人员使用高级设计语言对系统逻辑功能的描述在一个包含众多结构功能性能均已知的逻辑元件的逻辑单元库的支持下将其转换成使用这些基本的逻辑单元组成的逻辑网络结构实现

综合策略分为两种:

一种是自上而下(Top-Down), 一种是自下而上(Bottom-Up)。 这两种综合策略适合的目录组织结构分别如下 图所示。

2、 选择和设置逻辑单元库

综合工具利用逻辑单元库中的逻辑器件将 RTL逻辑描述文件进行编译和优化,转换成门级 电路。选择和设置逻辑单元库是综合过程开始的 前提。

文件扩展名

数据类型 设计源代码 扩展名 .v .vhd .edif .con .scr 描述 Veirlog VHDL EDIF 约束条件 脚本文件

综合脚本 报告和日志 设计数据库

.rpt

.log

报告文件

日志文件

.db

Synopsy库文件

在文件的组织过程中,为了对文件进行有效的 控制,简化文件的使用和查找,必须采用一定的文 件目录结构,将文件一一对应放置。文件目录结构 的选择和采用的综合策略有关。

(2)模块划分应注意模块的复用性。可复用的模 块设计可以减轻模块整合和测试的工作量。模块的复 用性设计应注意模块接口的标准化和模块内部的参数 化。 (3)模块的输出信号采用寄存器方式输出。输出 信号采用寄存器方式输出能够使模块综合时输入的信 号延时估计更加容易,也有易于子模块综合出较好的 结果。 (4)将功能上相关联的组合逻辑尽可能放入一个 模块中,在自下而上的综合过程中,综合工具能够很 好地处理模块内部的时序优化问题,而处于模块边缘 的组合逻辑分布在不同的逻辑模块中会导致时序预估 不准确,从而增加了综合的复杂程度。如下图所示。

芯片设计中的逻辑综合与布图方法教程

芯片设计中的逻辑综合与布图方法教程在芯片设计中,逻辑综合和布图是非常关键的步骤。

逻辑综合是将设计描述转换为逻辑电路,而布图则是将逻辑电路转换为物理实现。

本文将为您介绍芯片设计中的逻辑综合和布图方法。

逻辑综合是将高级语言描述的功能转换为门电路和触发器等逻辑元件的过程。

它的目的是将功能描述转换为可实现的电路结构。

下面是逻辑综合的一般步骤:1. 门级综合:根据设计描述,通过逻辑综合工具将逻辑电路转换为与非门、或门和异或门等基本逻辑门的级联组合。

这一步骤涉及到的主要问题是逻辑优化,即如何用更少的门电路实现相同的功能。

逻辑优化可以提高电路的性能和功耗。

2. 触发器综合:将存储元素(如触发器和锁存器)添加到电路中,以实现需要在不同时间点存储和处理数据的功能。

触发器综合的目标是实现高性能、低功耗的存储元素。

3. 时钟综合:确定电路中的时钟域,设置时钟的频率和相位以及时序约束。

时钟综合是确保电路能够按照设计要求正确工作的关键步骤。

它涉及到时钟分配、时钟树合成和时序优化等问题。

逻辑综合的输入是设计描述,通常是以高级语言(如Verilog或VHDL)编写的。

输出是门级网表,描述了逻辑电路的结构和功能。

门级网表可以作为后续步骤的输入,如布图和物理综合。

布图是将逻辑电路映射到实际器件上的过程。

它涉及到选择和放置逻辑元件、布线和时钟树的设计。

下面是布图的一般步骤:1. 逻辑映射:将门级网表映射到目标技术库中的逻辑元件。

技术库提供了不同类型的逻辑元件,如与非门、或门、触发器等。

在逻辑映射过程中,优化电路的资源利用率和延迟。

2. 布局:选择逻辑元件的具体位置,以及逻辑元件之间的连线路径。

布局是关键的步骤,它决定了电路的性能和功耗。

在布局过程中,需要考虑电路的物理约束,如芯片面积、功耗和信号完整性等。

3. 布线:确定逻辑元件之间的具体连线路径。

布线的目标是实现低延迟、低功耗的互连结构。

布线涉及到的问题包括线长匹配、电源和地线的规划、时钟树设计等。

集成电路(IC)设计完整流程详解及各个阶段工具简介

IC设计完整流程及工具IC的设计过程可分为两个部分,分别为:前端设计(也称逻辑设计)和后端设计(也称物理设计),这两个部分并没有统一严格的界限,凡涉及到与工艺有关的设计可称为后端设计。

前端设计的主要流程:1、规格制定芯片规格,也就像功能列表一样,是客户向芯片设计公司(称为Fabless,无晶圆设计公司)提出的设计要求,包括芯片需要达到的具体功能和性能方面的要求。

2、详细设计Fabless根据客户提出的规格要求,拿出设计解决方案和具体实现架构,划分模块功能。

3、HDL编码使用硬件描述语言(VHDL,Verilog HDL,业界公司一般都是使用后者)将模块功能以代码来描述实现,也就是将实际的硬件电路功能通过HDL语言描述出来,形成RTL(寄存器传输级)代码。

4、仿真验证仿真验证就是检验编码设计的正确性,检验的标准就是第一步制定的规格。

看设计是否精确地满足了规格中的所有要求。

规格是设计正确与否的黄金标准,一切违反,不符合规格要求的,就需要重新修改设计和编码。

设计和仿真验证是反复迭代的过程,直到验证结果显示完全符合规格标准。

仿真验证工具Mentor 公司的Modelsim,Synopsys的VCS,还有Cadence的NC-Verilog均可以对RTL 级的代码进行设计验证,该部分个人一般使用第一个-Modelsim。

该部分称为前仿真,接下来逻辑部分综合之后再一次进行的仿真可称为后仿真。

5、逻辑综合――Design Compiler仿真验证通过,进行逻辑综合。

逻辑综合的结果就是把设计实现的HDL代码翻译成门级网表netlist。

综合需要设定约束条件,就是你希望综合出来的电路在面积,时序等目标参数上达到的标准。

逻辑综合需要基于特定的综合库,不同的库中,门电路基本标准单元(standard cell)的面积,时序参数是不一样的。

所以,选用的综合库不一样,综合出来的电路在时序,面积上是有差异的。

一般来说,综合完成后需要再次做仿真验证(这个也称为后仿真,之前的称为前仿真)逻辑综合工具Synopsys的Design Compiler,仿真工具选择上面的三种仿真工具均可。

IC设计基础-综合

IC设计基础-综合⼀、综合的概念⽤verilog或者vhdl设计电路,需要将语⾔描述转换为电路图描述,即⽤芯⽚制造商提供的基本电路单元(综合库)实现我们⽤硬件描述语⾔(verilog或vhdl)描述的(RTL级)电路的功能,这个过程就称为综合。

1.综合的步骤●转译(Translation):读⼊电路的RTL级描述,将语⾔转译成每条语句所对应的功能块以及功能块之间的拓扑结构,这⼀过程的结果是在综合器内部⽣成电路的布尔函数的表达,不做任何的逻辑重组和优化。

●优化(optimization):基于所施加的⼀定时序和⾯积的约束条件,综合器按照⼀定的算法对转译结果作逻辑重组和优化。

●映射(mapping):根据所施加的⼀定的时序和⾯积的约束条件,综合器从⽬标⼯艺库(Target Technology)中搜索符合条件的单元来构成实际电路。

由芯⽚制造商(Foundry)提供的⼯艺库,是⼀系列的基本单元,如与⾮、或⾮、反相器、锁存器、触发器、选择器等等。

对这些单元的电⽓可以进⾏描述,例如:单元的⾯积、输⼊电容。

输出端的驱动能⼒、单元的逻辑能⼒、单元的时序等等。

综合的⽬标就是⽤⼯艺库⽂件提供的这些单元来实现⽤RTL代码描述的逻辑功能,并满⾜设计者提出的⾯积和时序要求。

2.对设计者的要求⼀个合格的设计者,应该能够在⾃⼰脑⼦⾥再现“转译”这个过程,即清楚⾃⼰⽤HDL 语⾔所构造的电路结构是什么样⼦的。

写代码时,请时刻记住三个准则:“think hardware”:要时刻想着代码所描述的电路结构,熟悉不同代码的结构,清楚通过综合能获得怎样的硬件实现,这个是芯⽚设计者所必须具备的素质。

同时必须记住,综合器⽆法帮助⽤户实现功能,⽆法做算法或功能的优化,⽽只能够在已有功能的基础上按照⽤户的要求选择较优的实现。

“think synchronous”:要时刻关⼼电路的同步问题。

同步电路设计的有点在于系统中信号流的可预见性,因此避免了诸如时序设定和实现上的困难。

集成电路(IC)设计完整流程详解及各个阶段工具简介

IC设计完整流程及工具IC的设计过程可分为两个部分,分别为:前端设计(也称逻辑设计)和后端设计(也称物理设计),这两个部分并没有统一严格的界限,凡涉及到与工艺有关的设计可称为后端设计。

前端设计的主要流程:1、规格制定芯片规格,也就像功能列表一样,是客户向芯片设计公司(称为Fabless,无晶圆设计公司)提出的设计要求,包括芯片需要达到的具体功能和性能方面的要求。

2、详细设计Fabless根据客户提出的规格要求,拿出设计解决方案和具体实现架构,划分模块功能。

3、HDL编码使用硬件描述语言(VHDL,Verilog HDL,业界公司一般都是使用后者)将模块功能以代码来描述实现,也就是将实际的硬件电路功能通过HDL语言描述出来,形成RTL(寄存器传输级)代码。

4、仿真验证仿真验证就是检验编码设计的正确性,检验的标准就是第一步制定的规格。

看设计是否精确地满足了规格中的所有要求。

规格是设计正确与否的黄金标准,一切违反,不符合规格要求的,就需要重新修改设计和编码。

设计和仿真验证是反复迭代的过程,直到验证结果显示完全符合规格标准。

仿真验证工具Mentor 公司的Modelsim,Synopsys的VCS,还有Cadence的NC-Verilog均可以对RTL 级的代码进行设计验证,该部分个人一般使用第一个-Modelsim。

该部分称为前仿真,接下来逻辑部分综合之后再一次进行的仿真可称为后仿真。

5、逻辑综合――Design Compiler仿真验证通过,进行逻辑综合。

逻辑综合的结果就是把设计实现的HDL代码翻译成门级网表netlist。

综合需要设定约束条件,就是你希望综合出来的电路在面积,时序等目标参数上达到的标准。

逻辑综合需要基于特定的综合库,不同的库中,门电路基本标准单元(standard cell)的面积,时序参数是不一样的。

所以,选用的综合库不一样,综合出来的电路在时序,面积上是有差异的。

一般来说,综合完成后需要再次做仿真验证(这个也称为后仿真,之前的称为前仿真)逻辑综合工具Synopsys的Design Compiler,仿真工具选择上面的三种仿真工具均可。

第5章 逻辑综合

第5章逻辑综合5.1 逻辑综合(Synthesis)的概念逻辑综合是指将硬件描述语言描述的RTL级的代码转换为由芯片制造商(Foundry)提供的基本单元电路实现的门级网表的过程。

逻辑综合是由综合工具完成的,但设计者必须提供对芯片的时序、面积、功耗等方面的约束。

综合过程可以分为三个步骤:(1)翻译(Translation)将硬件描述语言翻译为符合综合工具内部规定的逻辑方程,不做任何逻辑优化,与具体工艺无关。

(2)优化(Optimization)根据时序和面积约束,对逻辑方程进行重组和优化。

(3)映射(Mapping)根据时序和面积约束,从目标工艺库(Target Technology)中搜索适当的单元来实现实际电路。

芯片制造商(Foundry)提供的工艺库中,有各种基本单元,如各种逻辑门、触发器、数据选择器等。

在工艺库中,对这些基本单元电路的特性有完整的描述,如面积、输入端电容、输出端的驱动能力等等。

综合的目标就是用工艺库中的这些单元实现RTL代码描述的逻辑功能,并满足设计者提出的面积和时序要求。

逻辑综合将生成门级网表文件、标准延迟文件(SDF)和各种报告。

面向ASIC的主流综合工具是Synopsys公司的Design Compiler。

本章主要介绍用基于的Design Compiler逻辑综合方法。

5.2 Design Compiler 简介5.2.1 Linux Red Hat 7.2 基本操作Design Compiler有Unix和Linux两种平台下的版本,Linux下的版本必须使用Linux Red Hat 7.2操作系统。

软件安装参见本章附录。

以下介绍Linux文件系统的基本思想和基本操作命令。

●基本思想初学Linux要适应文件系统基本思想,Linux将整个计算机中的各种软件、硬件都理解为文件,以统一的文件系统方式组织。

其中/ 为最上层的根目录,其它都是根目录下的子目录。

Linux的文件路径分为绝对路径和相对路径。

逻辑综合中的基本概念

逻辑综合中的基本概念第一篇:逻辑综合中的基本概念1.逻辑综合(Logic Synthesis)EDA工具把数字电路的功能描述(或结构描述)转化为电路的结构描述。

实现上述转换的同时要满足用户给定的约束条件,即速度、功耗、成本等方面的要求。

2.逻辑电路(Logic Circuit)逻辑电路又称数字电路,在没有特别说明的情况下指的是二值逻辑电路。

其电平在某个阈值之上时看作高电平,在该阈值之下时看作低电平。

通常把高电平看作逻辑值1;把低电平看作逻辑值0。

3.约束(restriction)设计者给EDA工具提出的附加条件,对逻辑综合而言,约束条件一般包括速度、功耗、成本等方面的要求。

4.真值表(Truth Table)布尔函数的表格描述形式,描述输入变量每一种组合情况下函数的取值。

输入变量组合以最小项形式表示,函数的取值为真或假(1 或0)。

5.卡诺图(Karnaugh Map)布尔函数的图形描述形式,图中最小方格和最小项对应,两个相邻的最小方格所对应的最小项只有一个变量的取值不同。

卡诺图适合于用观察法化简布尔函数,但是当变量的个数大于4时,卡诺图的绘制和观察都变得很困难。

6.单输出函数(Single-output Function)一个布尔函数的单独描述。

7.多输出函数(Multiple-output Function)输入变量相同的多个布尔函数的统一描述。

8.最小项(Minterm)设a1,a2,…ai,…an是n个布尔变量,p为n个因子的乘积。

如果在p中每一变量都以原变量ai或反变量的形式作为因子出现一次且仅出现一次,则称p为n个变量的一个最小项。

最小项在卡诺图中对应于最小的方格;在立方体表示中对应于顶点。

9.蕴涵项(Implicant)布尔函数f的“与-或”表达式中的每一乘积项都叫作f的蕴涵项。

例如:f=+中的乘积项和都是函数f的蕴涵项。

蕴涵项对应于立方体表示法中的立方体。

10.质蕴涵项(Prime Implicant,PI)设函数f有多个蕴涵项,若某个蕴涵项i所包含的最小项集合不是任何别的蕴涵项所包含的最小项集合的子集的话,则称i为函数f的质蕴涵项。

第六章_可编程器件_IC systhesis_IC逻辑综合

IC 综合

什么是综合?

设计描述

–高层次描述:对整个系统的数学模型描述,它试图

在系统设计的初始阶段,通过对系统行为描述的仿真

来发现系统设计中存在的问题,此时考虑更多的是系

统结构和工作过程能够达到设计规格的要求,而与具

体的工艺和器件无关

–逻辑描述:对设计进行RTL级描述,导出逻辑表达

式,并用功能仿真工具进行仿真

–门级描述:设计的门级实现,相当于系统的逻辑原理

图

–物理描述:或称版图描述,ASIC设计中表现为

GDSII 文件

综合指不同描述之间的转换

IC设计中的综合

约束条件:输入/输出延时示意。

pnr ic设计流程

pnr ic设计流程

PNR(Place and Route)是集成电路设计中的一个重要步骤,

它涉及将逻辑电路映射到物理布局,并进行布线以实现最终的芯片

设计。

PNR IC设计流程通常包括以下几个主要步骤:

1. 逻辑综合,在PNR流程之前,需要进行逻辑综合,将高级综

合后的RTL描述转换为逻辑门级的网表描述。

逻辑综合的目标是优

化电路的面积、功耗和时序性能。

2. 物理综合,物理综合是将逻辑网表映射到实际的物理单元

(如标准单元库中的逻辑门、存储单元等)上的过程。

在这一步中,需要考虑面积、时序、功耗等方面的优化。

3. 布局,在布局阶段,设计工程师将设计的电路映射到芯片的

物理布局上,包括放置逻辑单元、布线通道、时钟树等。

布局需要

考虑信号完整性、功耗分布、散热等因素。

4. 布线,布线是将逻辑单元之间的连接线路进行规划和布置的

过程,目标是最小化延迟、功耗和面积。

在布线过程中,需要考虑

时序约束、信号完整性、电磁兼容等问题。

5. 物理验证,完成布局和布线后,需要进行物理验证,包括DRC(Design Rule Check)、LVS(Layout vs. Schematic)等验证

步骤,以确保设计符合工艺规则和逻辑一致性。

6. 后端仿真,在完成PNR流程后,需要进行后端仿真,验证设

计的时序、功耗、电磁兼容等性能指标是否符合要求。

总的来说,PNR IC设计流程涉及到逻辑综合、物理综合、布局、布线、物理验证和后端仿真等多个步骤,需要综合考虑面积、功耗、时序等多个方面的优化目标,以实现高性能、低功耗、小面积的集

成电路设计。

第4章 逻辑综合(重点)

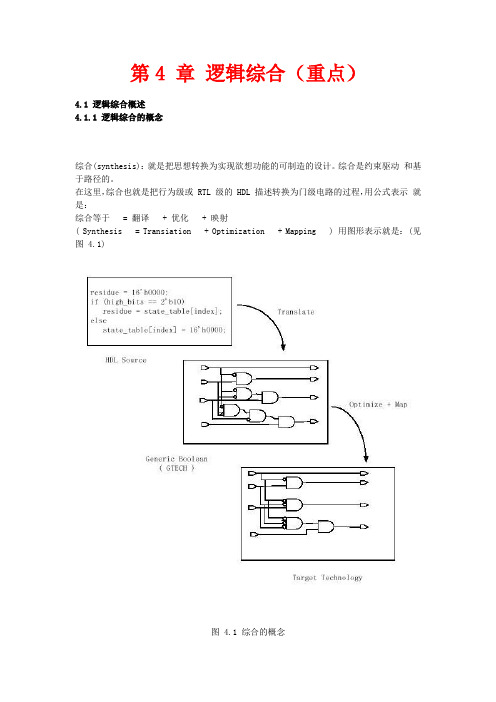

第4 章逻辑综合(重点)4.1 逻辑综合概述4.1.1 逻辑综合的概念综合(synthesis):就是把思想转换为实现欲想功能的可制造的设计。

综合是约束驱动和基于路径的。

在这里,综合也就是把行为级或 RTL 级的 HDL 描述转换为门级电路的过程,用公式表示就是:综合等于 = 翻译 + 优化 + 映射( Synthesis = Transiation + Optimization + Mapping ) 用图形表示就是:(见图4.1)图 4.1 综合的概念4.1.2 逻辑综合的工具介绍。

工具操作界面设计编译器(Design Compiler 简称 DC)是 Synopsys 综合工具的核心。

综合一个设计时,可以选用两种界面: A 。

设计分析器(Design Analyzer 简称 DA)-图形窗口界面。

B 。

dc_shell—命令行界面。

DA 图形窗口界面的启动:%dadc_shell 命令行界面的启动;%dc_shelldc_shell 界面的提示符为:dc_shell >dc_shell 命令行界面支持两种脚本语言:dcsh 模式和 dctcl 模式。

dcsh 是使用源于 Synopsys 的语言。

dctcl 使用工具命令语言( Tool Command Langugae )。

dcsh 模式和 dctcl 模式比较tcl 是一种开放型的工业标准语言。

它比 dc_shell 更加强大。

启动 dcsh 模式用 dc_shell 命令,启动 dctcl 模式用 dc_shell -t如果你已经有了 dcsh 的 setup 文件或脚本文件(.scr),你想转换为 Tcl 的 setup 文件和约束文件,则我们只需执行下面命令即可.setup 文件的转换:设 dcsh 的 setup 文件为.synopsys_dc.setup.old,要转换为 Tcl 的 setup 文件.synopsys_dc.setup 则% dc-transcript .synopsys_dc.setup.old .synopsys_dc.setup 脚本文件的转换:设 dcsh 的约束文件为 old_scriptfile.scr,dctcl 的约束文件为 tcl_script.tcl ,则 % dc-transcript old_scriptfile.scr tcl_script.tcl由于 dcsh 和 dctcl 是可以转换的,以下的介绍中,在支持 dcsh 的地方,将都用 dcsh 命令。

ic设计流程

ic设计流程IC设计流程。

IC设计是集成电路设计的简称,是指设计和制造芯片的过程。

IC设计流程是一个非常复杂的过程,需要经过多个阶段的设计、验证和制造。

本文将介绍IC设计的整体流程,并对每个阶段进行详细的分析和说明。

第一阶段,需求分析。

在IC设计的初期阶段,需要进行需求分析,明确设计的功能和性能指标。

这一阶段需要与客户进行深入的沟通和交流,了解客户的需求和要求,明确设计的目标和方向。

第二阶段,架构设计。

在需求分析的基础上,进行芯片的整体架构设计。

这一阶段需要考虑芯片的功能划分、模块划分、接口设计等,确定芯片的整体结构和功能分布。

第三阶段,逻辑设计。

在芯片的整体架构设计确定后,进行逻辑设计,包括逻辑电路设计、逻辑仿真和逻辑综合。

这一阶段需要进行逻辑电路的设计和验证,确保设计的正确性和稳定性。

第四阶段,物理设计。

在逻辑设计完成后,进行芯片的物理设计,包括布局设计、布线设计和物理验证。

这一阶段需要进行芯片的版图设计和布线,确保芯片的物理结构和布局符合设计要求。

第五阶段,验证与测试。

在芯片的物理设计完成后,进行验证与测试,包括功能验证、时序验证和功耗验证。

这一阶段需要对芯片进行全面的验证和测试,确保芯片的功能和性能符合设计要求。

第六阶段,制造与封装。

在芯片的验证与测试完成后,进行芯片的制造和封装。

这一阶段需要进行芯片的生产制造和封装,确保芯片的质量和可靠性。

总结。

IC设计流程是一个复杂而又严谨的过程,需要经过多个阶段的设计、验证和制造。

每个阶段都需要进行详细的分析和设计,确保芯片的功能和性能符合设计要求。

只有经过严格的流程和严谨的设计,才能设计出高质量的集成电路产品。

利用DC进行逻辑综合

详细布线

版图设计后进 行STA

时序满足将要求吗

no yes

信号一致性(Sign-off) 将设计备份

综合是基于路径的。 设计编辑器(DC)通过使用静态时序分析来计算设计中各路径的时序。时 序路径的种类有四种:输入到寄存器;寄存器到寄存器;寄存器到输出;输入到 输出 1.1.2 初始化文件及系统保留变量 工艺库一般由 ASIC 供应商提供,它必须与 DC 兼容以便用 DC 进行综合。 单元综合的流程:综合的过程 = 转化 + 优化 + 映射。一般,设计的 HDL 源代

它是子设计在设计中的实例(instance)名,在 Synopsys 术语中单元和实 例不区分对待,它们都是单元。 7).引脚(Pin)

它是设计内部单元的输入、输出端,与端口不同的是,端口是设计用来对外

联系的。 这是七类对象类型。不同类型的对象可以使用相同的名字。如果要在在 dc_

shell-t 中发现对象可以使用以下命令: get_designs: 可以得到指定的设计。 get_cells:可以得到指定的单元。 get_nets:可以得到指定的内连线。 get_ports:可以得到指定的端口。 get_clocks:可以得到指定的时钟。 all_inputs:可以得到所有的输入端口。 all_outputs 可以得到所有的输出端口。

(整理)数字ic设计流程.

数字集成电路设计流程数字集成电路设计流程数字集成电路设计流程1.设计输入电路图或硬件描述语言2.逻辑综合处理硬件描述语言,产生电路网表3.系统划分将电路分成大小合适的块4.功能仿真State Key Lab of ASIC & Systems, Fudan University数字集成电路设计流程5.布图规划芯片上安排各宏模块的位置6.布局安排宏模块中标准单元的位置7.布线宏模块与单元之间的连接8.寄生参数提取提取连线的电阻、电容9.版图后仿真检查考虑连线后功能和时序是否正确State Key Lab of ASIC & Systems, Fudan University数字集成电路设计工具. 主要的EDA vendor–Synopsys :逻辑综合,仿真器,DFT–Cadence :版图设计工具,仿真器等–Avanti :版图设计工具–Mentor :DFT,物理验证工具–Magma: BlastRTL, Blast FusionState Key Lab of ASIC & Systems, Fudan University选择设计工具的原则.. 只用“ sign- off ”的工具–保证可靠性,兼容性.. 必须针对芯片的特点–不同的芯片需要不同的设计工具.. 了解设计工具的能力–速度、规模等State Key Lab of ASIC & Systems, Fudan University设计工具的选择.. 设计输入–任何文本编辑工具–Ultraedit, vi, 仿真器自带编辑器⋯..RTL 级功能仿真–Modelsim (Mentor),–VCS/VSS ( Synopsys )–NC-Verilog ( Cadence )–Verilog-XL ( Cadence )State Key Lab of ASIC & Systems, Fudan University设计工具的选择.. 逻辑综合–Cadence: Ambit, PKS;–Synopsys: Design Compiler;–Magma: Blast RTL.. 物理综合–Synopsys: Physical CompilerMagma: Blast Fusion State Key Lab of ASIC & Systems, Fudan University 设计工具的选择. 形式验证工具–Formality ( Synopsys )–FormalPro ( Mentor ). Floorplanning / 布局/布线–Synopsys: Apollo, Astro,–Cadence: SoC Encounter, Silicon Ensemble . 参数提取. Cadence: Nautilus DC. Synopsys: Star-RC XT. 时序验证–Cadence: PearlSynopsys: PrimeTimeState Key Lab of ASIC & Systems, Fudan University设计工具的选择. DRC/LVS–Dracula (Cadence)–Calibre (Mentor )–Hercules (Synopsys). 可测试性设计(DFT) 编译器和自动测试模式生成–Synopsys: DFT 编译器,DFT Compiler; 自动测试生成(ATPG) 与故障仿真, Tetra MAX–Mentor: FastScan. 晶体管级功耗模拟–Synopsys: PowerMillState Key Lab of ASIC & Systems, Fudan University中国大陆EDA 工具的使用状况State Key Lab of ASIC & Systems, FudanUniversity集成电路设计流程.. 数字集成电路设计流程.. 模拟集成电路设计流程.. 混合信号集成电路设计流程..SoC 芯片设计流程State Key Lab of ASIC & Systems, Fudan University模拟集成电路设计流程State Key Lab of ASIC & Systems, Fudan UniversitySchematicEntrySimulationLayoutentryRCextractionPostlayoutsimulationStartFinishFull-chipDRC/LVSOnline DRC“ 集成电路导论” 扬之廉State Key Lab of ASIC & Systems, Fudan UniversityState Key Lab of ASIC & Systems, Fudan UniversityState Key Lab of ASIC & Systems, Fudan UniversityState Key Lab of ASIC & Systems, Fudan University设计工具的选择..Circuit:–Cadence Virtuoso Composer (Cadence) ..Simulation–Synopsys: NanoSim, HSPICEyout–Cadence Virtuoso (Cadence)State Key Lab of ASIC & Systems, Fudan University集成电路设计流程.. 数字集成电路设计流程.. 模拟集成电路设计流程.. 混合信号集成电路设计流程..SoC 芯片设计流程State Key Lab of ASIC & Systems, Fudan University混合信号芯片设计流程.. 首先,进行模拟/数字划分.. 然后,分别设计模拟和数字部分.. 最后,将模拟/数字模块协同仿真,并进行版图拼接,验证State Key Lab of ASIC & Systems, Fudan UniversityState Key Lab of ASIC & Systems, Fudan University混合信号芯片设计流程State Key Lab of ASIC & Systems, Fudan University集成电路设计流程.. 数字集成电路设计流程.. 模拟集成电路设计流程.. 混合信号集成电路设计流程.. SoC 芯片设计流程State Key Lab of ASIC & Systems, Fudan UniversitySoC 芯片设计流程.. SOC 以嵌入式系统为核心,集软硬件于一体,并追求产品系统最大包容的集成SoC 芯片设计流程.. 软硬件协同设计State Key Lab of ASIC & Systems, Fudan UniversitySoC 芯片设计流程.. 芯片规划、划分.. 分系统之间的连线最少。

逻辑综合理论

关于RM逻辑介绍逻辑综合与优化是一类用逻辑门实现电路功能或描述的完整过程,而逻辑优化的关键内容之一是电路表达式或函数的化简。

这是由于电路的面积,功耗,速度和可验证性与电路结构直接相关,而具体的电路结构可由表达式或函数的繁简程度反映。

因此,函数表达式的化简是很有必要的,IC 设计者可根据需求对电路表达式进行改善,以实现理想的面积、速度和功耗等性能。

对于运算电路、通信电路、奇偶检测电路等特定电路,使用 RM 逻辑往往能够实现更好的面积、速度和功耗等性能RM 逻辑电路主要包括 XOR/AND 和XNOR/OR 这两种表示形式,依据极性分为固定极性 Reed-Muller(FPRM)表达式、混合极性 Reed-Muller(MPRM)表达式; fixed polarity固定;mixedpolarity 混合;XOR——异或门,符号标志为“⊕”;XNOR——同或门,数学符号为“⊙”;Boolean 逻辑仍是当前电路设计的主流逻辑形式,为了更好的使用 RM 逻辑并进行相关优化,首先就需要实现从 Boolean 逻辑函数到 RM 逻辑函数的转换。

极性转换方法提供了 Boolean 逻辑到RM 逻辑以及 RM 逻辑中极性间的转换。

FPRM 电路相较于MPRM 电路实现更简单,其极性转换方法更简便适用;FPRM 电路相关的极性转换方法较多,主要有:列表法、系数矩阵法、不相交乘积项等;MPRM 电路的极性转换方法主要有:图形变换法、OKFDDs(Ordered Kronecker Functional Decision Diagrams)法。

逻辑综合概述认识逻辑综合用Verilog之类的程序设计语言将硬件的高级描述转换成一个优化的数字电路网表,一个由相互连接的布尔逻辑门组成的网络,从而实现该功能。

逻辑综合设计流程大型数字电路设计流程如下:EDA是用来完成芯片的功能设计、综合、验证、物理设计等流程的设计方式,其中,逻辑级自动综合与优化属于EDA前端设计技术;逻辑综合完成就进入后端设计阶段;布局:就是将综合后的门级电路网表的每个工艺单元合理的摆放到芯片的各个位置;布局的任务是确定每个单元的位置,尽可能减小布线的开销。

集成电路设计中的逻辑综合算法与实践

集成电路设计中的逻辑综合算法与实践集成电路是现代计算机系统中不可或缺的组成部分,尤其是现代人类普遍使用的电子产品,几乎都需要采用集成电路。

而集成电路的设计和制造需要多种技术的综合应用,逻辑综合算法是其中之一。

本文将重点讲解集成电路设计中的逻辑综合算法和实践,从而更好地理解和应用这项技术。

一、逻辑综合算法的概述逻辑综合是IC(Integrated Circuit,集成电路)设计中的一个重要环节,是将高层次的抽象电路设计转化为底层物理电路实现的关键步骤。

逻辑综合算法可以把高级语言设计描述形式的RTL Verilog或VHDL描述文件逐步转化为与目标工艺匹配的门级电路网表,实现从逻辑层面到布局层面的综合。

逻辑综合算法最终的目标是通过逻辑优化和物理映射等技术,使得设计的电路具有更好的性能、可靠性和面积效率。

逻辑综合算法通常包含以下步骤:(1)寻找设计中的数据依赖性和控制流,根据传统电路逻辑门电路模型将RTL程序划分为若干逻辑块。

(2)拆解逻辑块,通过逻辑优化技术得到全局最优目标电路,然后通过自下而上的方式将逻辑块组装成大规模电路。

(3)通过物理布局和版本控制技术在特定的工艺下实现电路实现,完成逻辑综合。

二、逻辑综合算法的应用逻辑综合算法广泛应用于计算机芯片设计和VLSI(Very Large Scale Integration,超大规模集成)电路的设计中。

由于逻辑综合算法能够完成大规模、高效率和高度复杂的电路实现,因此在现代电子产品中得到了广泛的应用。

例如,CPU(Central Processing Unit,中央处理器)和GPU(Graphics Processing Unit,图形处理器)等都运用了逻辑综合算法。

此外,进一步的发展也使得逻辑综合算法得到了越来越广泛的应用。

三、逻辑综合算法的实践在逻辑综合算法的应用过程中,实践扮演了至关重要的角色。

具体而言,逻辑综合算法的实践需要对以下因素进行深入研究和理解:(1)综合目标的设定。

IC设计中逻辑综合的一般步骤及相关基本概念

IC设计中逻辑综合的一般步骤及相关基本概念第一篇:IC设计中逻辑综合的一般步骤及相关基本概念IC设计中逻辑综合的一般步骤及相关基本概念综合中的延迟及关键路径图1 常见的时序路径示意图图1中给出了常见的两个寄存器R1和R2之间的时序路径。

R1和R2分别具有延迟T ck-q和Tsetup,TM和TN分别是M和N逻辑具有的延迟。

B对R1来说是输出端口,输出延迟为Tsetup+TN,而对R2是输入端口,输入延迟为T ck-q+TM,于是这条单周期路径的总延迟为Tck-q+TM+Tsetup+TN。

从延迟的角度来说,关键路径就是指那些总延迟大于相应周期时间的路径。

消减关键路径的延迟要从消减路径中的各部分延迟入手,主要方法就是利用综合工具对路径施加约束条件来限制优化,达到减小路径延迟的目的。

综合的主要过程1.翻译:读入电路的RTL级描述,并将语言描述翻译成相应的功能块以及功能块之间的拓扑结构。

这一过程的结果是在综合器内部生成电路的布尔函数表达式,不做任何逻辑重组和优化。

2.优化:根据所施加的时序和面积约束,按照一定的算法对翻译结果进行逻辑重组和优化。

3.映射:根据所施加的时序和面积约束,从目标工艺库中搜索符合条件的单元来构成实际电路的逻辑网表。

一般的综合步骤如表1所示。

从表1中可以看出,约束条件是综合过程的重要组成部分。

综合正是通过设置约束条件来优化设计,以达到设计要求的。

对关键路径延迟的主要约束处理方法通过选择器件的处理方法从最直观的角度看,时序逻辑和组合逻辑都由基本的电路单元组成,因此,选择延迟小且不影响芯片性能的器件是既简易又高效的处理方法。

例如,基本电路单元库中的DFFXL寄存器虽然面积较小,但它的延迟相关参数T ck-q、Tsetup较大,容易形成关键路径,于是可以通过设置set_dont_use等约束来禁用它。

在一些特殊情况下,基本电路单元库中的器件不能满足要求,这时需要采用自定义的电路单元。

对端口间逻辑的处理方法这是诸方法中最常用、最有效、最重要的,一般通过set_input_delay、set_output_delay、set_max_delay等来实现,有以下几种情况:如果两个寄存器之间的逻辑比较少,那么可以对其输入延迟和输出延迟施加较宽裕的约束,即设置较大的set_input_delay和set_output_delay值,表明所做逻辑不受压缩,映射电路基本单元库的自由度较大。

IC设计与方法

IC设计与方法IC设计,即集成电路设计,是通过EDA( Electronic Design Automation)工具实现的,以满足电路功能、性能、功耗、可制造和可测试性的全过程。

它是现代电子技术中最重要和最具挑战性的领域之一。

IC设计中需要考虑的因素非常多,在整个设计过程中,需要许多方法和技术的支持。

一、IC设计流程IC设计通常包括以下几个步骤:1、概念设计:根据设计需求,确定设计目标和基本架构。

2、RTL(Register Transfer Level)设计:以硬件描述语言(例如Verilog,VHDL等)编写模块级代码,设计不同模块的位级和时序。

3、逻辑综合:将RTL设计转换成门级网表,使用逻辑综合工具,可实现高效率、低功耗、可测试和可制造的电路结构。

4、布局与同步:首先,需要完成底层布局,布置电路的物理要素以提高电路的性能,包括功率分配、信号小区分离优化等;其次是时序约束,根据不同设计启示与技术规则,协调所有定时与时序限制。

5、布线:自动布线工具可以使得间距、相邻阻抗、时序要求等尽量满足要求,以实现更高的性能和更低的功耗。

6、验证:在验证阶段,使用仿真工具和其他验证方法,对设计进行逐个测试,以确保电路可以按照预期进行操作。

7、物理验证:然后使用物理验证工具进行精细检查和核实。

8、生产准备:最后,进行DRC(Design Rule Check)和LVS (Layout Versus Schematic)的检查,以确保设计能够正确制造。

二、IC设计方法1、高层次设计在IC设计的早期阶段,需要对设计进行高层次的规划和设计,例如,定义电路的功能、模块划分、详细功能规范的定义等。

2、分层次设计在IC设计中,可以通过分层次来对电路进行更好的管理和设计。

通过将电路划分为多个模块,在整个设计过程中可以更好地处理各个模块之间的功能和时序关系。

3、RTL设计在RTL设计阶段,需要对电路进行位级设计和时序设计,并根据不同的需求来进行代码编写。

DC逻辑综合(Design Compiler)

DC综合1.概述1.1. 综合的目的综合是完成从RTL代码到门级电路的转换。

如果在综合时,链接了厂家的库文件,则门级电路使用的器件是厂家库文件中提供的器件。

综合在整个IC设计中,起到的作用如图1所示。

图 1 综合在IC设计中的作用由于目前IC设计规模日益增大,设计难度不断提高,设计人员必须通过综合工具实现综合任务。

目前IC所采用的是综合工具是Synopsys公司的Design Compiler。

本讲义紧密结合了Design Compiler的应用。

1.2. 综合的特性1.2.1. 综合是由约束驱动的对于一个设计来说,在进行综合前,需要给这个设计加上约束,约束也就是综合的目标,综合工具会竭力满足约束,以实现综合的目标。

约束可分为多方面,如时序方面的约束、面积方面的约束、环境属性方面的约束、驱动和负载方面的约束等。

其中最重要的约束是对时钟等与时序相关的属性进行约束。

在综合时,约束的各个方面可能存在一定的矛盾,如对速度和面积的约束,见图2所示。

综合的过程就是找到一个最好的平衡点,满足各个方面的约束。

图 2 约束中速度与面积间的关系好的、合理的约束,是综合成功的关键。

不同的约束会导致不同的综合效果。

1.2.2. 综合是基于path分析的在整个综合的过程中,完成是基于path进行时序分析的,因此path的概念非常重要。

何谓path?如下图所示。

图 3 Timing Path的概念Path是综合工具进行时序分析的基本单位。

对于一条path而言,它的起点只能是输入端口,或者触发器/寄存器的时钟端;终点只能是输出端口,或者触发器/寄存器的数据输入端(对D触发器而言,就是D端)。

结合图3而言,其中共有4条path,分别为:1)输入端口A -> FF2的D端;2)FF2的CK端-> FF3的D端;3)FF3的CK端-> 输出端口Z;4)输入端口A -> 输出端口Z。

同一个时钟域多条path,组成一个组,称为path group。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

IC设计中逻辑综合的一般步骤及相关基本概念

综合中的延迟及关键路径

图1 常见的时序路径示意图

图1中给出了常见的两个寄存器R1和R2之间的时序路径。

R1和R2分别具有延迟Tck-q 和Tsetup,TM和TN分别是M和N逻辑具有的延迟。

B对R1来说是输出端口,输出延迟为Tsetup+TN,而对R2是输入端口,输入延迟为Tck-q+TM,于是这条单周期路径的总延迟为Tck-q+TM+Tsetup+TN。

从延迟的角度来说,关键路径就是指那些总延迟大于相应周期时间的路径。

消减关键路径的延迟要从消减路径中的各部分延迟入手,主要方法就是利用综合工具对路径施加约束条件来限制优化,达到减小路径延迟的目的。

综合的主要过程

1.翻译:读入电路的RTL级描述,并将语言描述翻译成相应的功能块以及功能块之间的拓扑结构。

这一过程的结果是在综合器内部生成电路的布尔函数表达式,不做任何逻辑重组和优化。

2.优化:根据所施加的时序和面积约束,按照一定的算法对翻译结果进行逻辑重组和优化。

3.映射:根据所施加的时序和面积约束,从目标工艺库中搜索符合条件的单元来构成实际电路的逻辑网表。

一般的综合步骤如表1所示。

从表1中可以看出,约束条件是综合过程的重要组成部分。

综合正是通过设置约束条件来优化设计,以达到设计要求的。

对关键路径延迟的

主要约束处理方法

通过选择器件的处理方法

从最直观的角度看,时序逻辑和组合逻辑都由基本的电路单元组成,因此,选择延迟小且不影响芯片性能的器件是既简易又高效的处理方法。

例如,基本电路单元库中的DFFXL寄存器虽然面积较小,但它的延迟相关参数Tck-q、Tsetup较大,容易形成关键路径,于是可以通过设置set_dont_use等约束来禁用它。

在一些特殊情况下,基本电路单元库中的器件不能满足要求,这时需要采用自定义的电路单元。

对端口间逻辑的处理方法

这是诸方法中最常用、最有效、最重要的,一般通过set_input_delay、set_output_delay、set_max_delay等来实现,有以下几种情况:

如果两个寄存器之间的逻辑比较少,那么可以对其输入延迟和输出延迟施加较宽裕的约束,即设置较大的set_input_delay和set_output_delay值,表明所做逻辑不受压缩,映射电路基本单元库的自由度较大。

这样,两者的实际延迟之和将不大于单周期时间(非关键路径),不仅满足设计要求,而且对其他关键路径的影响很小。

如果两个寄存器之间的逻辑比较多,那么就要对其输入延迟和输出延迟施加较严厉的约束,即设置较小的set_input_delay和set_output_delay值,表明所做逻辑需要压缩,而映射电路基本单元库的自由度也较小。

但这并不表示越小越好,如果设的值很小(甚至为零),那么会使综合器对这条路径的逻辑压缩得过大,而导致其它关键路径的延迟增加,甚至导致其它非关键路径转化为关键路径。

因此要凭借经验,不断改变所设的约束值,最终使所有路径的延迟都不大于单周期时间,满足设计要求。

对于一般芯片设计(中小规模),在以上两种情况下,对其输入延迟和输出延迟合理施加约束,基本就能满足设计要求。

如有个别几条关键路径延迟仍然较长,可以通过设置

set_critical_range和group_path来加以约束。

这两种约束对所约束路径的逻辑压缩效果较好,且不会影响其它路径的延迟。

采用这样的约束之后,关键路径通常都能被消除了。

对于一些大规模的芯片设计和上述处理后仍然存在关键路径的情况,就要用set_max_delay 来进行约束,这种约束的效果非常明显,但会影响其它路径的延迟。

因此也要凭借经验,不断改变所设的约束值,最终使所有路径的延迟都能满足设计要求。

对层次间边界的处理方法

图2 边界转化示意图

硬件描述语言描述的RTL级电路通常是多层次模块,对其进行综合后得到的电路依然以独立模块的方式存在,即存在边界问题,因此综合中有专门针对边界问题的约束,利用这些约束可以打散边界、保持边界,或重新整合边界,从而优化边界,达到设计要求。

如图2所示,约束group用来生成新的层次模块,而约束ungroup的作用刚好相反,它用来打散边界,消除层次模块。

通常它们都会结合起来使用,但不管以哪种方式选择边界,都应该根据具体的设计要求,参照综合结果,选择最好的方法。

在用硬件描述语言描述RTL级电路时,有时会专门设计某些单独模块(类似全定制电路)来简化实现一定的功能,从而缩短延迟并减小面积。

在综合中利用约束set_dont_touch可以保证这类模块不受影响,保持边界。

对电路结构的处理方法

综合概述

一般情况下,设计者在描述RTL级电路时就应该考虑诸多因素,对电路结构进行规划,而在综合中只要将RTL代码映射到基本电路单元库几乎就能达到预期要求。

但在有些状况下,还是需要利用一些约束来进行优化,这里仅以最常见的set_structure和set_flatten来加以说明。

structuring是综合中默认的逻辑优化策略,它同时考虑了延迟(速度)优化及面积优化;而flattening这种策略往往以牺牲面积来达到缩短延迟的目的。

对某一逻辑的RTL级描述采用structuring和flattening两种策略得到的综合电路分别如图3、图4所示。

flattening策略下得到的电路只有两级,延迟小于structuring策略下得到的三级电路,但电路面积比较大。

当今IC工艺已经进入深亚微米级,因而在设计中往往需要首先考虑延迟因素,但究竟选择哪种策略,还是要根据具体的设计要求而决定。

如果采用上述方法后还不能消除关键路径达到设计要求,就需要改进系统级设计,修改RTL 代码,再重新进行综合。