元器件IC说明书3-8线译码器74LS138

74ls138管脚图及功能

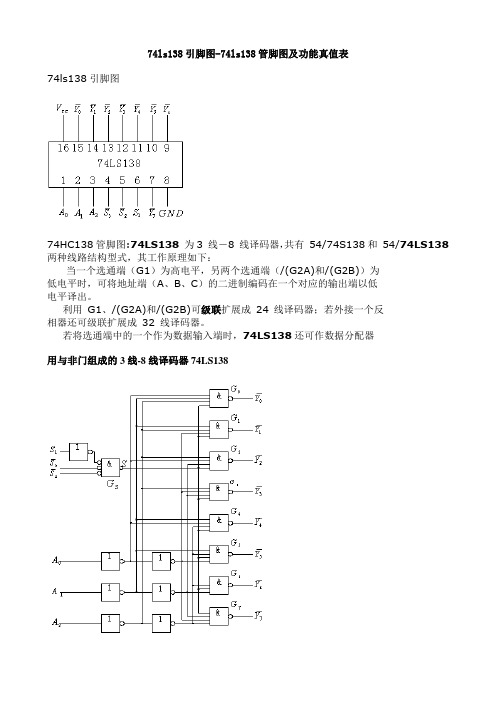

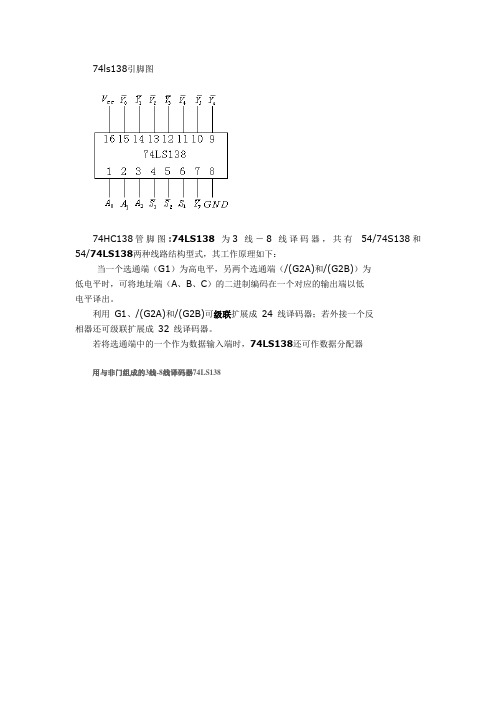

74ls138引脚图-74ls138管脚图及功能真值表74ls138引脚图74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

【例3.3.2】试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。

IC74LS138引脚及说明

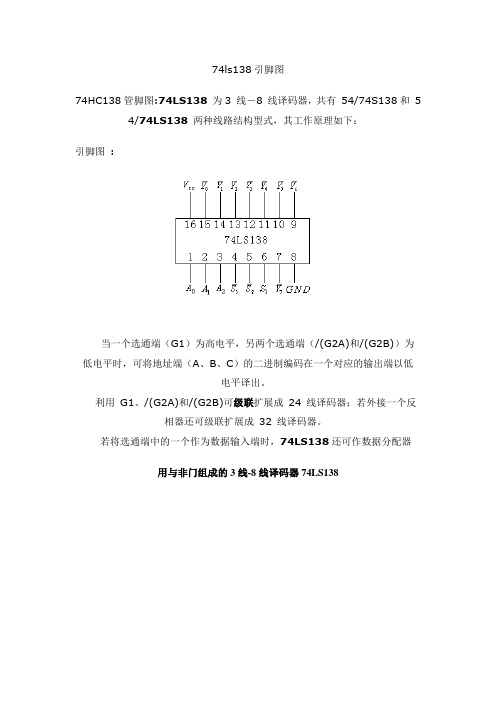

74ls138引脚图74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和5 4/74LS138两种线路结构型式,其工作原理如下:引脚图:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3. 5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

【例3.3.2】试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。

三位二进制译码器-74LS138

H H H H L H H H H H H

H H H H H L H H H H H

H H H H H H L H H H H

H H H H H H H L H H H

H H H H H H H H L H H

H H H H H H H H H L H

H H H H H H H H H H L

3. 逻辑符号

D1

输

D2 D3 D4 D5

出

D6 D7

使能端 的作用

G1 G 2 A G2 B

× × L H H H H H H H H H × × L L L L L L L L × H × L L L L L L L L

译码 功能

× × × × × × L L L L L H L H H L H L H H H H

&

G=G 1⋅G 2A⋅ G 2B

3线/8线译码器

G 2B

输入 缓冲门

1 1

1 1

1 1

B2 B1 B0

1

G1 G 2A

3功能表

74LS138 的功能表

输 入 B2 B1 B0 D0 × × × L H L H L H L H H H H L H H H H H H H

三位二进制译码器—74LS138

——常用中规模集成译码电路 1. 内部结构 2. 功能表 3. 逻辑符号 4. 扩展 5. 应用—实现逻辑函数 6.管脚排列

1. 74LS138最小项译码器的电路结构

D7 D6 D5 D4 D3 D2 D1 D0

Di = G ⋅ mi

&

&

&

&

&

&

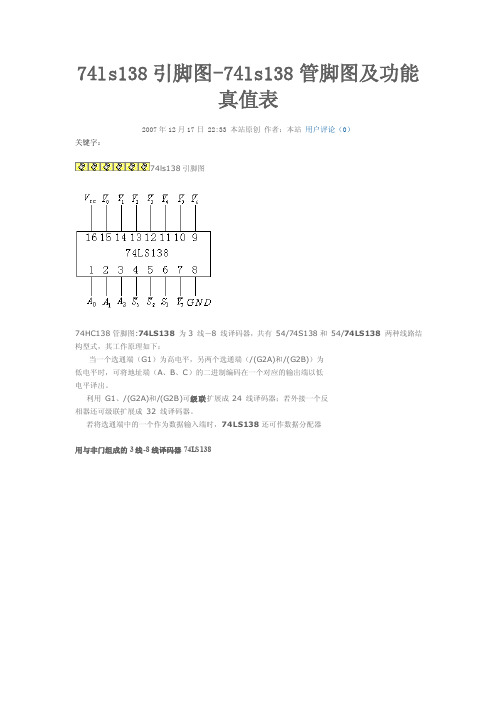

74ls138引脚图-74ls138管脚图及功能真值表

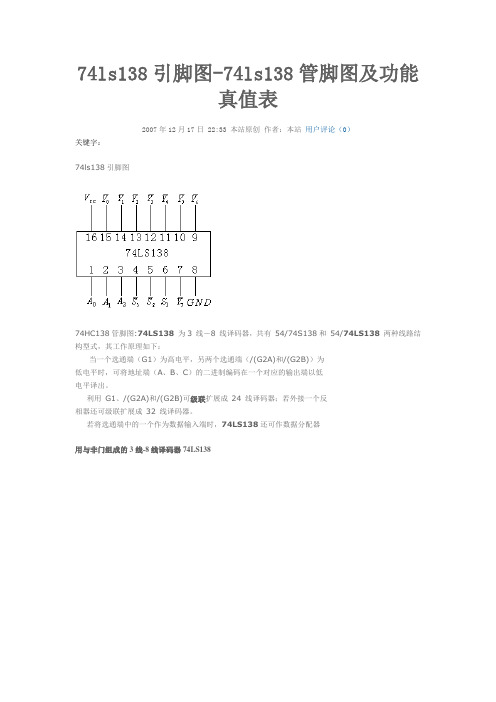

74ls138引脚图-74ls138管脚图及功能真值表2007年12月17日 22:33 本站原创作者:本站用户评论(0)关键字:74ls138引脚图74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

74ls138管脚图及功能真值表

74ls138引脚图74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

【例3.3.2】试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。

74ls138功能介绍

74ls138功能介绍

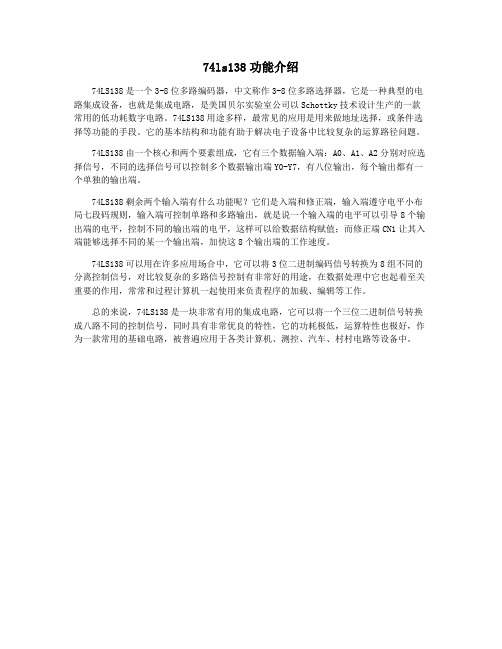

74LS138是一个3-8位多路编码器,中文称作3-8位多路选择器,它是一种典型的电路集成设备,也就是集成电路,是美国贝尔实验室公司以Schottky技术设计生产的一款常用的低功耗数字电路。

74LS138用途多样,最常见的应用是用来做地址选择,或条件选择等功能的手段。

它的基本结构和功能有助于解决电子设备中比较复杂的运算路径问题。

74LS138由一个核心和两个要素组成,它有三个数据输入端:A0、A1、A2分别对应选择信号,不同的选择信号可以控制多个数据输出端Y0-Y7,有八位输出,每个输出都有一个单独的输出端。

74LS138剩余两个输入端有什么功能呢?它们是入端和修正端,输入端遵守电平小布局七段码规则,输入端可控制单路和多路输出,就是说一个输入端的电平可以引导8个输出端的电平,控制不同的输出端的电平,这样可以给数据结构赋值;而修正端CN1让其入端能够选择不同的某一个输出端,加快这8个输出端的工作速度。

74LS138可以用在许多应用场合中,它可以将3位二进制编码信号转换为8组不同的分离控制信号,对比较复杂的多路信号控制有非常好的用途,在数据处理中它也起着至关重要的作用,常常和过程计算机一起使用来负责程序的加载、编辑等工作。

总的来说,74LS138是一块非常有用的集成电路,它可以将一个三位二进制信号转换成八路不同的控制信号,同时具有非常优良的特性,它的功耗极低,运算特性也极好,作为一款常用的基础电路,被普遍应用于各类计算机、测控、汽车、村村电路等设备中。

74ls138译码器内部电路逻辑图功能表简单应用

74ls138译码器内部电路逻辑图功能表简单应用74HC138:74LS138 为3 线-8 线译码器,共有54/74S138和54/74LS138 两种线路结构型式,其74LS138工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

74LS138的作用:利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS138<74ls138译码器内部电路>3线-8线译码器74LS138的功能表<74ls138功能表>无论从逻辑图还是功能表我们都可以看到74LS138的八个输出管脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出管脚全为高电平1。

如果出现两个输出管脚在同一个时间为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出<74ls138逻辑图>由上式可以看出,在同一个时间又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(在同一个时间),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

用3线8线译码器74LS138和门电路设计1位二进制全减器

1、用3线—8线译码器74LS138和门电路设计1位二进制全减器,输入为被减数、减数和来自低位的借位;输出为两数之差和向高位的借位信号(74LS138的逻辑框图如图1.1所示)。

CO---向高位的借位; Y---两位数之差;C I ---来自低位的借位;

故:

Y=m 1+m 2+m 4+m 7;CO=m 3+m 5+m 6+m 7; 其逻辑图如下:

Y

2、试用8选1数据选择器74LS152和必要的门电路设计一个路灯控制电路,要求在四个不同的地方都能独立地开灯和关灯,画出逻辑电路图(74LS152的逻辑框图如图2.1所示)。

i i i m D A A A D A A A D Y ∑

==++⋅⋅=7001270120 图2.1 74LS152的逻辑框图

D3

D2D1

D0

Y A0A1

A2

D7

D6D5D4

74L S 152

m m m

m

其中A3,A2,A1,A0分别代表四个不同的地方;Y代表灯;1代表亮,或是开关闭合;0代表灯灭;

Y=A3(m1+m2+m4+m0)

对照着所给的逻辑表达式可得:

D0=D1=D2=D4=A3

D3=D5=D6=D7=0; A2=A2;A1=A1;A0=A0;

故逻辑图如下所示:

A3

Y

1。

74LS138中文资料P.pdf

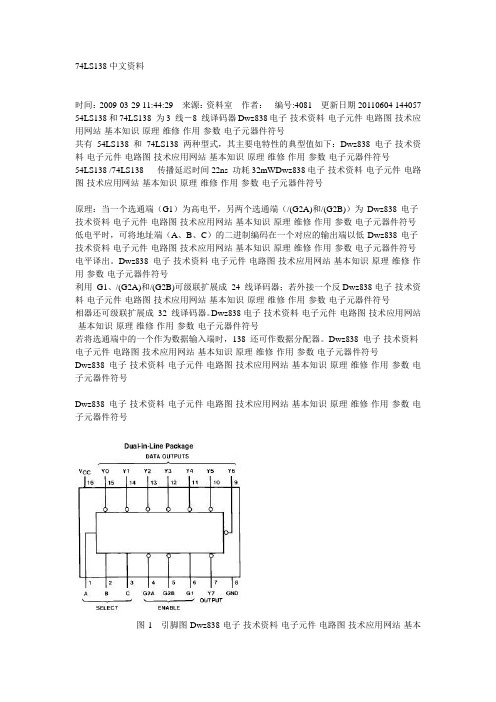

74LS138中文资料54LS138和74LS138 为3 线-8 线译码器共有54LS138 和74LS138 两种型式,其主要电特性的典型值如下:54LS138 /74LS138 传播延迟时间22ns 功耗32mW原理:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,138 还可作数据分配器。

图1 引脚图图2 内部逻辑管脚图引脚功能:A、B、C 译码地址输入端G1 选通端/(G2A)、/(G2B) 选通端(低电平有效)Y0~Y7 译码输出端(低电平有效)真值表:建议操作条件:电气参数:符号参数测试条件最大值典型值最大值单位VI 输入钳位电压VCC = Min, II = -18 mA- - -1.5 VVOH 输出高电平电压VCC = Min, IOH = Max,VIL = Max, VIH = Min2.73.4 - VVOL 输出低电平电压VCC = Min, IOL = Max,VIL = Max, VIH = Min- 0.35 0.5V IOL = 4 mA, VCC = Min - 0.25 0.4II 最大输入电压时输入电流VCC = Max, VI = 7V - - 0.1 mAIIH 输入高电平电流VCC = Max, VI = 2.7V - - 20 mA IIL 输入低电平电流VCC = Max, VI = 0.4V - - -0.36 mA IOS 输出短路电流VCC = Max (Note 4) -20 - -100 mA ICC 电源电流VCC = Max (Note 5) - 6.3 10 mA 动态特性表:符号参数To (Output) 时滞RL = 2 kW单位CL = 15pF CL = 50 pF最大值最大值最大值最大值tPLH 低到高电平输出传递延迟时间Select to Output 2 - 18 - 27 nstPHL 高到低电平输出传递延迟时间Select to Output 2 - 27 - 40 nstPLH 低到高电平输出传递延迟时间Select to Output 3 - 18 - 27 nstPHL 高到低电平输出传递延迟时间Select to Output 3 - 27 - 40 nstPLH 低到高电平输出传递延迟时间Enable to Output 2 - 18 - 27 nstPHL 高到低电平输出传递延迟时间Enable to Output 2 - 24 - 40 nstPLH 低到高电平输出传递延迟时间Enable to Output 3 - 18 - 27 nstPHL 传递延迟时间Enable to Output 3 - 28 - 40 ns。

74LS138中文资料

74LS138中文资料时间:2009-03-29 11:44:29 来源:资料室作者:编号:4081 更新日期20110604 144057 54LS138和74LS138 为3 线-8 线译码器Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号共有54LS138 和74LS138 两种型式,其主要电特性的典型值如下:Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号54LS138 /74LS138 传播延迟时间22ns 功耗32mWDwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号原理:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号电平译出。

Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号相器还可级联扩展成32 线译码器。

Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号若将选通端中的一个作为数据输入端时,138 还可作数据分配器。

Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号图1 引脚图Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号图2 内部逻辑管脚图Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号引脚功能:Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号A、B、C 译码地址输入端Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号G1 选通端Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号/(G2A)、/(G2B) 选通端(低电平有效)Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号Y0~Y7 译码输出端(低电平有效)Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号真值表:Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号本文来自【838电子】:/ad/PCB/1039.html本文来自【838电子】:/ad/PCB/1039.html本文来自【838电子】:/ad/PCB/1039.html本文来自【838电子】:/ad/PCB/1039.html。

74ls138译码器内部电路逻辑图功能表简单应用

74ls138译码器内部电路逻辑图功能表简单应用74HC138:74LS138 为3 线-8 线译码器,共有54/74S138和54/74LS138 两种线路结构型式,其74LS138工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

74LS138的作用:利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS138<74ls138译码器内部电路>3线-8线译码器74LS138的功能表<74ls138功能表>无论从逻辑图还是功能表我们都可以看到74LS138的八个输出管脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出管脚全为高电平1。

如果出现两个输出管脚在同一个时间为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出<74ls138逻辑图>由上式可以看出,在同一个时间又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(在同一个时间),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

3-8译码器74LS138

3-8译码器74LS138引脚图及真值表

74LS138除了3线到8线的基本译码输入输出端外,为便于扩展成更多位的译码电路和实现数据分配功能,74LS138还有三个输入使能端EN1,EN2A和EN2B。

74LS138真值表和内部逻辑图

74LS138真值表和内部逻辑图分别见表1和图1(a)。

图1(c)所示符号图中,输入输出有效用极性指示符表示,同时极性指示符又标明了信号方向。

74138的三个输入使能(又称选通ST)信号之间是与逻辑关系,EN1高电平有效,EN2A 和EN2B低电平有效。

只有在所有使能端都为有效电平(EN1EN2A EN2B=100)时,74138才对输入进行译码,相应输出端为低电平,即输出信号为低电平有效。

在EN1EN2A EN2B≠100时,译码器停止译码,输出无效电平(高电平)。

图1 3线-8线译码器74LS138

(a)逻辑图(b)方框图(c)符号图

表1 74LS138真值表

集成译码器通过给使能端施加恰当的控制信号,就可以扩展其输入位数。

以下用74138为例,

说明集成译码器扩展应用的方法。

图3中,用两片74138实现4线/16线的译码器。

图3 74138扩展成4/16线译码器

74LS138引脚图

图4 74138引脚图。

芯片74LS138_中文资料

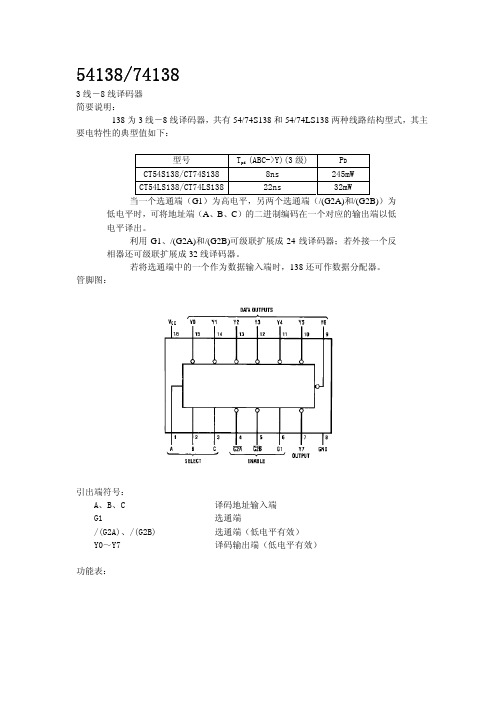

54138/741383线-8线译码器简要说明:138为3线-8线译码器,共有54/74S138和54/74LS138两种线路结构型式,其主要电特性的典型值如下:型号 T pd (ABC->Y)(3级) P DCT54S138/CT74S138 8ns 245mWCT54LS138/CT74LS13822ns 32mW当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24线译码器;若外接一个反相器还可级联扩展成32线译码器。

若将选通端中的一个作为数据输入端时,138还可作数据分配器。

管脚图:引出端符号:A、B、C 译码地址输入端G1 选通端/(G2A)、/(G2B) 选通端(低电平有效)Y0~Y7 译码输出端(低电平有效)功能表:/G2*=G2A+G2BH=高电平L=低电平X=任意极限值电源电压------------------------------------------------7V输入电压54/74S138----------------------------------------5.5V54/74LS138---------------------------------------7V 工作环境温度54×××------------------------------ -55~125℃74×××------------------------------------0~70℃ 贮存温度-------------------------------------- -65~150℃推荐工作条件:CT54S138/CT74S138 CT54LS138/CT74LS138单位最小额定最大最小额定最大54 4.5 5 5.54.5 5 5.5V 电源电压Vcc74 4.75 5 5.254.75 5 5.25输入高电平电压V IH 2 2 V54 0.80.7V 输入低电平电压V IL74 0.80.8输出高电平电流I OH-1000-400 µA54 20 4mA 输出低电平电流I OL74 20 8逻辑图静态特性(T A 为工作环境温度范围)`S138`LS138 参数 测试条件【1】 最小最大最小最大 单位 VIK 输入钳位电压Vcc 最小 IIK=-12mA -1.2 -1.5 V54 2.5 2.5VOH 输出高电平电压 Vcc=最小,VIH=2V,VIL=最大,IOH=最大 74 2.7 2.7 V54 0.5 0.4 VOL 输出低电平电压 VCC=最小,VIH=2V,VIL=最大,IOL=最大 740.5 0.5 V VI=5.5V 1 II 最大输入电压时输入电流 Vcc=5VVI=7V 0.1 mA IH 输入高电平电流Vcc=5V,VIH=2.7V 50 20 μA VI=5.5V 1 II 最大输入电压时输入电流 Vcc=最大VI=7V0.1 mA IIH 输入高电平电流 Vcc=最大 VIH=2.7V50 20 μAVIL=0.4V -0.4VIL 输入低电平电流Vcc=最大VIL=0.5V-2 mA 54-40 -100-6 -40 IOS 输出短路电流Vcc=最大 74-40-100-5 -42 mA Icc 电源电流Vcc=最大7410mA 【1】:测试条件中的“最大”和“最小”用推荐工作条件中的相应值。

3-8线译码器74LS138

FeaturesYDesigned specifically for high speed: Memory decodersData transmission systemsY LS138 3-to-8-line decoders incorporates 3 enable in- puts to simplify cascading and/or data receptionY LS139 contains two fully independent 2-to-4-line decod- ers/demultiplexersY Schottky clamped for high performance Y Typical propagation delay (3 levels of logic)LS138 21 ns LS139 21 nsY Typical power dissipationLS138 32 mW LS139 34 mW Y Alternate Military/Aerospace devices (54LS138, 54LS139) are available. Contact a National Semicon- ductor Sales Office/Distributor for specifications.Connection DiagramsDual-in-Line PackageThese Schottky-clamped circuits are designed to be used in high-performance memory-decoding or data-routing appli- cations, requiring very short propagation delay times. In high-performance memory systems these decoders can be used to minimize the effects of system decoding. When used with high-speed memories, the delay times of these decoders are usually less than the typical access time of the memory. This means that the effective system delay intro- duced by the decoder is negligible.The LS138 decodes one-of-eight lines, based upon the con- ditions at the three binary select inputs and the three enable inputs. Two active-low and one active-high enable inputs reduce the need for external gates or inverters when ex- panding. A 24-line decoder can be implemented with no ex- ternal inverters, and a 32-line decoder requires only one inverter. An enable input can be used as a data input for demultiplexing applications.The LS139 comprises two separate two-line-to-four-line de- coders in a single package. The active-low enable input can be used as a data line in demultiplexing applications. All of these decoders/demultiplexers feature fully buffered inputs, presenting only one normalized load to its driving circuit. All inputs are clamped with high-performanceC 1995 National Semiconductor CorporationTL/F/6391RRD-B30M105/Printed in U. S. A.TL/F/6391 – 2Order Number 54LS139DMQB, 54LS139FMQB, 54LS139LMQB, DM54LS139J, D M54LS139W,DM74LS139M or D M74LS139N See NS Package Number E20A, J16A,M16A, N16E or W16ATL/F/6391 – 1 Order Number 54LS138DMQB, 54LS138FMQB, 54LS138LMQB, DM54LS138J, D M54LS138W,DM74LS138M or D M74LS138N See NS Package Number E20A, J16A,M16A, N16E or W16ADual-in-Line PackageSchottky diodes to suppress line-ringing and simplify systemdesign.54LS138/DM54LS138/DM74LS138,54LS139/DM54LS139/DM74LS139 Decoders/DemultiplexersGeneral DescriptionJune 198954LS138/DM54LS138/DM74LS138, 54LS139/DM54LS139/DM74LS139 Decoders/DemultiplexersLogic DiagramsLS138TL/F/6391 – 3LS139TL/F/6391 – 4Physical Dimensions inches (millimeters)Ceramic Leadless Chip Carrier Package (E)Order Number 54LS138LMQB or 54LS139LMQBNS Package Number E20A Array16-Lead Ceramic Dual-In-Line Package (J)Order Number 54LS138DMQB, 54LS139DMQB, DM54LS138J or DM54LS139JNS Package Number J16APhysical Dimensions inches (millimeters) (Continued)16-Lead Small Outline Molded Package (M)Order Number DM74LS138M or DM74LS139MNS Packge Number M16A16-Lead Molded Dual-In-Line Package (N)Order Number DM74LS138N or DM74LS139NNS Package Number N16ENational Semiconductor Japan Ltd.Tel: 81-043-299-2309 Fax: 81-043-299-2408National Semiconductor Hong Kong Ltd.13th Floor, Straight Block, Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon Hong KongTel: (852) 2737-1600 Fax: (852) 2736-9960National Semiconductor EuropeFax: (a 49) 0-180-530 85 86 Email: cnjwge @ Deutsch Tel: (a 49) 0-180-530 85 85 English Tel: (a 49) 0-180-532 78 32 Fran çais Tel: (a 49) 0-180-532 93 58 Italiano Tel: (a 49) 0-180-534 16 80National Semiconductor Corporation1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018LIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:1. Life support devices or systems are devices or2. A critical component is any component of a life systems which, (a) are intended for surgical implant support device or system whose failure to perform can into the body, or (b) support or sustain life, and whose be reasonably expected to cause the failure of the life failure to perform, when properly used in accordance support device or system, or to affect its safety or with instructions for use provided in the labeling, can effectiveness. be reasonably expected to result in a significant injury to the user.16-Lead Ceramic Flat Package (W)Order Number 54LS138FMQB, 54LS139FMQB, DM54LS138W or DM54LS139WNS Package Number W16APhysical Dimensions inches (millimeters) (Continued)54L S 138/D M 54L S 138/D M 74L S 138, 54L S 139/D M 54L S 139/D M 74L S 139 D e c o d e r s /D e m u l t i p l e x e r s。

74ls138引脚图-74ls138管脚图及功能真值表

74ls138引脚图-74ls138管脚图及功能真值表2007年12月17日 22:33 本站原创作者:本站用户评论(0)关键字:74ls138引脚图74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成 24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74L S1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

74ls138芯片

74ls138译码器74ls138译码器内部电路逻辑图功能表简单应用74HC138:74LS138 为3 线-8 线译码器,共有 54/74S138和 54/74LS138 两种线路结构型式,其74LS138工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

74LS138的作用:利用 G1、/(G2A)和/(G2B)可级联扩展成 24 线译码器;若外接一个反相器还可级联扩展成 32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS138<74ls138译码器内部电路>3线-8线译码器74LS138的功能表<74ls138功能表>无论从逻辑图还是功能表我们都可以看到74LS138的八个输出管脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出管脚全为高电平1。

如果出现两个输出管脚在同一个时间为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出<74ls138逻辑图>由上式可以看出,在同一个时间又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(在同一个时间),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

74LS138的工作原理

74LS138的工作原理

74LS138是一个3-8线译码器/解码器集成电路。

它有3个输入线A0,A1和A2,以及8个输出线Y0-Y7。

其工作原理如下:

1. 输入选择:根据输入线A2、A1和A0的逻辑电平,选择要

激活的输出线。

2. 译码功能:当输入线的逻辑电平满足特定条件时,将激活相应的输出线。

输出线上的逻辑电平取决于电路连接的方式,可以是高电平、低电平或三态(输出线不连接到任何电路)。

3. 解码功能:74LS138还可以作为解码器使用。

在解码模式下,输入线A2、A1和A0信号负逻辑,将会选择并激活一个输出线,其余输出线处于三态。

4. 输出端:输出线Y0-Y7的状态由输入线A2、A1和A0的逻

辑电平决定。

其中,只有一个输出线为低电平,其余输出线为高电平或三态(解码模式下)。

5. 使能端:除了输入线和输出线之外,74LS138还具有使能端(通常标记为G),通过对使能端进行控制,可以控制

74LS138的工作状态。

综上所述,74LS138通过输入选择和译码功能,根据输入信号

的逻辑电平激活特定的输出线,实现3-8线的译码器/解码器

功能。

用3线8线译码器74LS138和门电路设计1位二进制全减器

1、用3线—8线译码器74LS138和门电路设计1位二进制全减器,输入为被减数、减数和来自低位的借位;输出为两数之差和向高位的借位信号(74LS138的逻辑框图如图1.1所示)。

CO---向高位的借位; Y---两位数之差;C I ---来自低位的借位;

故:

Y=m 1+m 2+m 4+m 7;CO=m 3+m 5+m 6+m 7; 其逻辑图如下:

Y

2、试用8选1数据选择器74LS152和必要的门电路设计一个路灯控制电路,要求在四个不同的地方都能独立地开灯和关灯,画出逻辑电路图(74LS152的逻辑框图如图2.1所示)。

i i i m D A A A D A A A D Y ∑

==++⋅⋅=7001270120 图2.1 74LS152的逻辑框图

D3

D2D1

D0

Y A0A1

A2

D7

D6D5D4

74L S 152

m m m

m

其中A3,A2,A1,A0分别代表四个不同的地方;Y代表灯;1代表亮,或是开关闭合;0代表灯灭;

Y=A3(m1+m2+m4+m0)

对照着所给的逻辑表达式可得:

D0=D1=D2=D4=A3

D3=D5=D6=D7=0; A2=A2;A1=A1;A0=A0;

故逻辑图如下所示:

A3

Y

1。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

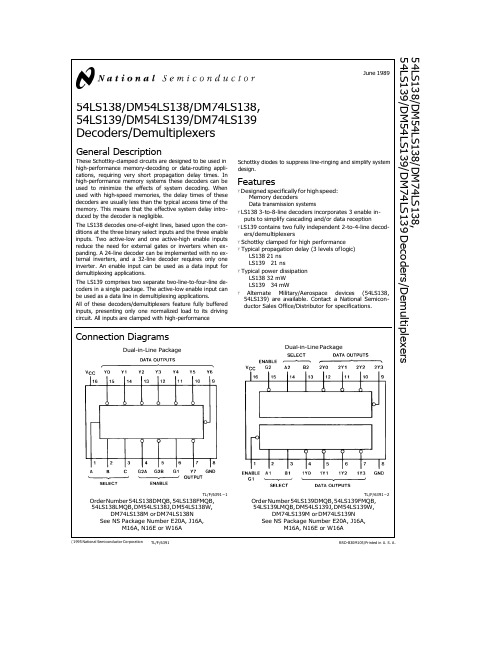

Connection Diagrams

Dual-in-Line Package

Dual-in-Line Package

TL F 6391 – 1

Order Number 54LS138DMQB 54LS138FMQB 54LS138LMQB DM54LS138J DM54LS138W

DM74LS138M or DM74LS138N See NS Package Number E20A J16A

The LS138 decodes one-of-eight lines based upon the conditions at the three binary select inputs and the three enable inputs Two active-low and one active-high enable inputs reduce the need for external gates or inverters when expanding A 24-line decoder can be implemented with no external inverters and a 32-line decoder requires only one inverter An enable input can be used as a data input for demultiplexing applications

Y LS138 3-to-8-line decoders incorporates 3 enable inputs to simplify cascading and or data reception

Y LS139 contains two fully independent 2-to-4-line decoders demultiplexers

Y Schottky clamped for high performance Y Typical propagation delay (3 levels of logic)

LS138 21 ns LS139 21 ns Y Typical power dissipation LS138 32 mW LS139 34 mW Y Alternate Military Aerospace devices (54LS138 54LS139) are available Contact a National Semiconductor Sales Office Distributor for specifications

54LS138 DM54LS138 DM74LS138 54LS139 DM54LS139 DM74LS139 Decoders Demultiplexers

June 1989

54LS138 DM54LS138 DM74LS138 54LS139 DM54LS139 DM74LS139 Decoders Demultiplexers

General Description

These Schottky-clamped circuits are designed to be used in high-performance memory-decoding or data-routing applications requiring very short propagation delay times In high-performance memory systems these decoders can be used to minimize the effects of system decoding When used with high-speed memories the delay times of these decoders are usually less than the typical access time of the memory This means that the effective system delay introduced by the decoder is negligible

DM74LS139M or DM74LS139N See NS Package Number E20A J16A

M16A N16E or W16A

RRD-B30M1Hale Waihona Puke 5 Printed in U S A

M16A N16E or W16A

C1995 National Semiconductor Corporation TL F 6391

TL F 6391 – 2

Order Number 54LS139DMQB 54LS139FMQB 54LS139LMQB DM54LS139J DM54LS139W

Schottky diodes to suppress line-ringing and simplify system design

Features

Y Designed specifically for high speed Memory decoders Data transmission systems

All of these decoders demultiplexers feature fully buffered inputs presenting only one normalized load to its driving circuit All inputs are clamped with high-performance