单片机控制74LS138译码器

74ls138管脚图及功能

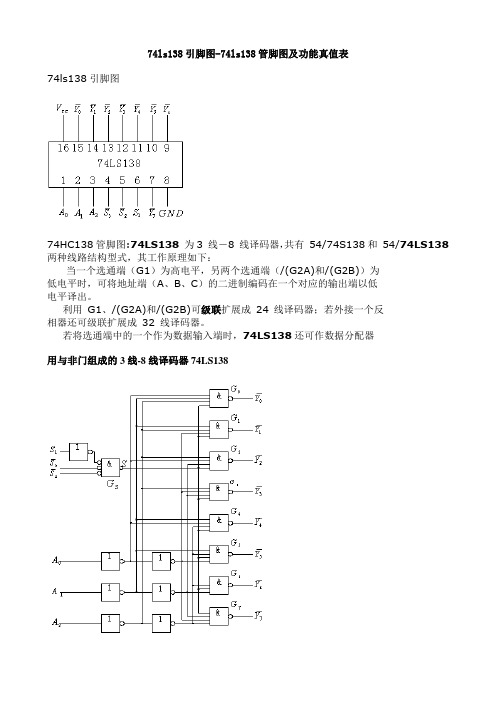

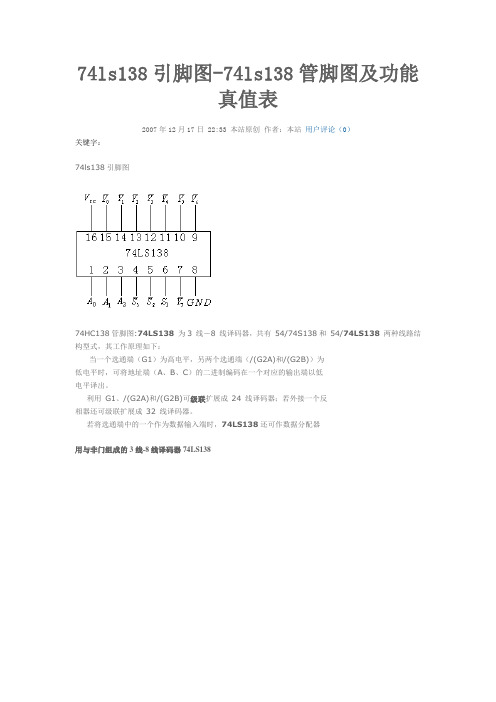

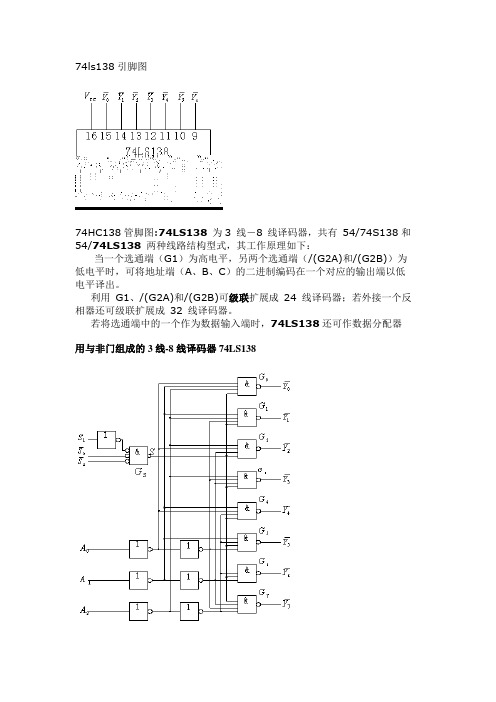

74ls138引脚图-74ls138管脚图及功能真值表74ls138引脚图74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

【例3.3.2】试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。

74ls138引脚图-74ls138管脚图及功能真值表

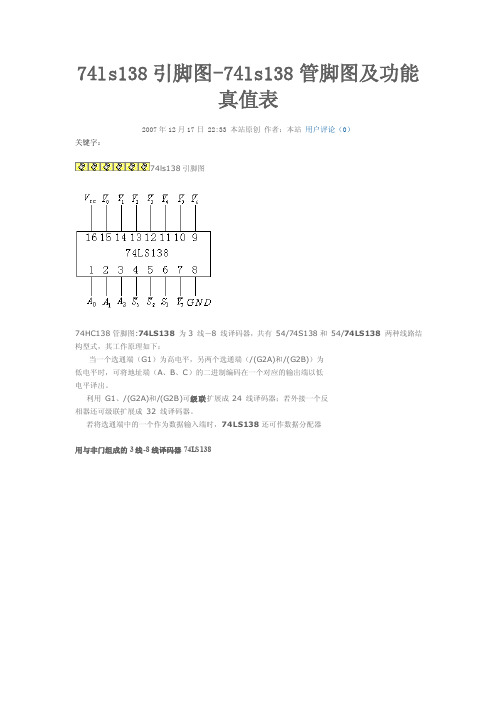

74ls138引脚图-74ls138管脚图及功能真值表2007年12月17日 22:33 本站原创作者:本站用户评论(0)关键字:74ls138引脚图74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

74ls138管脚图及功能真值表

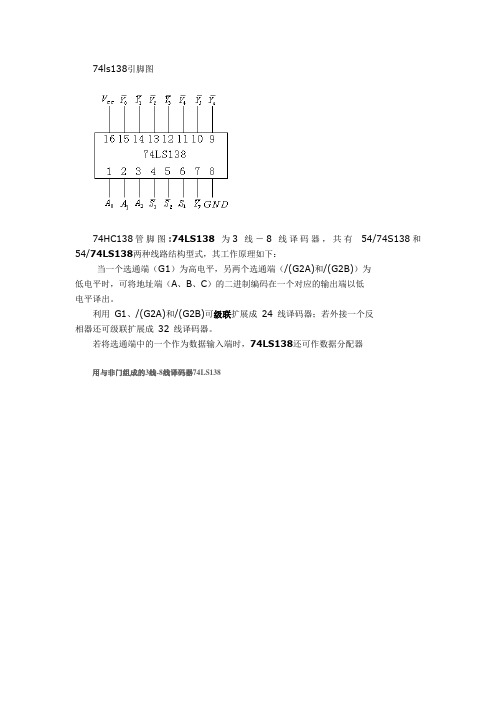

74ls138引脚图74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

【例3.3.2】试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。

74LS138D译码器真值表仿真以及逻辑分析_数字电子电路分析与应用_[共2页]

![74LS138D译码器真值表仿真以及逻辑分析_数字电子电路分析与应用_[共2页]](https://img.taocdn.com/s3/m/025a68febd64783e08122bca.png)

附录 Multisim 软件介绍及应用实例

– 211 –

2.连接电路

将元件之间用导线连接好,并连接好仪器,得到附图1.5.3所示电路。

附图1.5.3 8421码转余3码电路图

3.仿真结果分析

附图1.5.3中可以看出,输入为“0000”,输出为“0011”,其他的状态可以单击开关来改变输入的值,从而得到对应的输出余3码值,依次如表8.5.1所示,同学们可以依次验证。

附表1.5.1 8421转余3码真值表

1.5.2 74LS138D 译码器真值表仿真以及逻辑分析

74LS138D 译码器真值表的仿真测试可用图1.5.4来实现,即输入部分用单刀双掷开关来改变输入信号的高、低电平,输出用指示灯的亮和灭来指示高低电平的状态,就可看哪个通道处在译码状态。

若该通道就输出低电平(唯一性),该通道对应的输出指示灯就会亮。

也可以调用虚拟仪器工具栏中的字函数信号发生器XWG1和逻辑分析仪XLA2,组成译码器的仿真电路。

字函数信号发生器(Word Generator )是一个最多能产生32位同步数字信号的多路逻辑信号源,也称为数字逻辑信号源。

逻辑分析仪(Logic Analyzer )用于数字逻辑信号的高速采集和时序分析。

1.元件清单、仪器和选取途径

集成3-8译码器74LS138N :Place TTL →74LS →74LS138D 。

电源和地:Place Sources →V CC ;Place Sources →DGND 。

字函数信号发生器:单击虚拟仪器图标即可。

逻辑分析仪:单击虚拟仪器图标即可。

74LS138管脚功能

74ls138引脚图之阿布丰王创作74HC138管脚图:74LS138为3 线-8 线译码器,共有 54/74S138和 54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用 G1、/(G2A)和/(G2B)可级联扩展成 24 线译码器;若外接一个反相器还可级联扩展成 32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

【例3.3.2】试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。

通信工程设计与监理《74LS138优先译码器功能教案》

74LS138优先译码器功能

一、教学目标:

熟练运用74LS138优先译码器功能

二、教学重点、难点:

重点掌握74LS138的逻辑功能

三、教学过程设计:

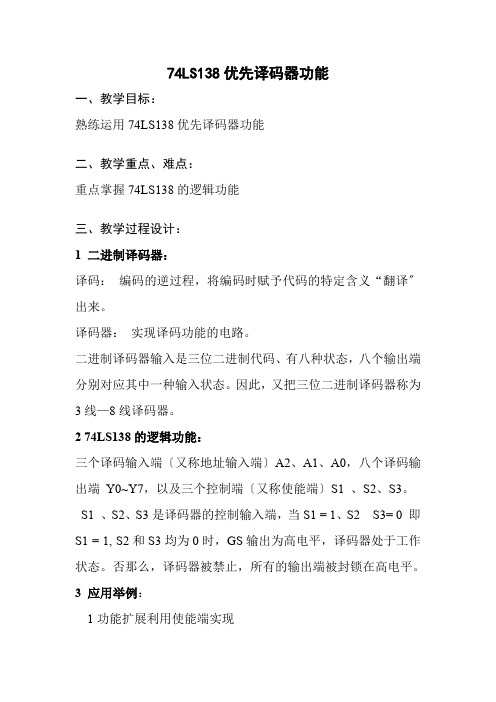

1二进制译码器:

译码:编码的逆过程,将编码时赋予代码的特定含义“翻译〞出来。

译码器:实现译码功能的电路。

二进制译码器输入是三位二进制代码、有八种状态,八个输出端分别对应其中一种输入状态。

因此,又把三位二进制译码器称为3线—8线译码器。

274LS138的逻辑功能:

三个译码输入端〔又称地址输入端〕A2、A1、A0,八个译码输出端Y0~Y7,以及三个控制端〔又称使能端〕S1 、S2、S3。

S1 、S2、S3是译码器的控制输入端,当S1 = 1、S2 S3= 0 即S1 = 1, S2和S3均为0时,GS输出为高电平,译码器处于工作状态。

否那么,译码器被禁止,所有的输出端被封锁在高电平。

3应用举例:

1功能扩展利用使能端实现

五、本节小结:

对本节内容进行小结。

74LS138管脚功能的主要 介绍

74ls138引脚图74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

【例3.3.2】试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。

74ls138译码器内部电路逻辑图功能表简单应用

74ls138译码器内部电路逻辑图功能表简单应用74HC138:74LS138 为3 线-8 线译码器,共有 54/74S138和 54/74LS138 两种线路结构型式,其74LS138工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

74LS138的作用:利用 G1、/(G2A)和/(G2B)可级联扩展成 24 线译码器;若外接一个反相器还可级联扩展成 32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS138<74ls138译码器内部电路>3线-8线译码器74LS138的功能表<74ls138功能表>无论从逻辑图还是功能表我们都可以看到74LS138的八个输出管脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出管脚全为高电平1。

如果出现两个输出管脚在同一个时间为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出<74ls138逻辑图>由上式可以看出,在同一个时间又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(在同一个时间),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

电子技术基础(数字部分)译码器74LS138功能验证实验

试验二译码器74LS138功效验证试验

试验目标:

验证译码器74LS138功效;掌握74LS138作为数据分配器时应用。

试验器材:

数字逻辑试验箱一个;数字万用表一个;5V电源一个;导线若干;

(1)验证74LS138功效:

74LS138为3-8译码器,试验原理图以下图所表示:

LED

试验过程:分别在74LS138A2、A1、A0、E3、/E2和/E1加上高、低不一样电平,用万用表测量出输出Y7-Y0电平,统计下来,验证逻辑关系是否正确

测量结果:

试验结论:当E3输入非高电平时,不管其它输入怎样,电路输出全部为高电平,即译码器不处于工作状态;只有当E3输入为高电平,/E2和/E1同时为低电平时,译码器才处于工作状态,输出低电平有效。

(2)验证74LS138作为数据分配器时功效(设信号从/E1输入,从/Y5输出)。

电路原理以下:

试验过程以下:先将K1闭合,测量/E1引脚电平关态和/Y5引脚电平状态;再将先将K1断开,测量/E1引脚电平关态和/Y5引脚电平状态,没量结果以下:

结论: /E1引脚电平关态和/Y5引脚电平状态永远相同,说明接在/E1信号被分配到/Y5输出。

LED。

译码器74LS138组成彩灯控制器

实验5 译码器74LS138组成彩灯控制器一、实验内容1. 练习逻辑转换器的使用。

2 熟悉74LS138集成电路的应用。

2. 用74LS138组成彩灯控制器。

二、演示电路用74LS138组成的彩灯控制器如图1所示。

图1 用74LS138组成的彩灯控制器74LS138的真值表如表4-2-8所示,也就是74LS138的功能表。

输 入输 出 G1 G2A ’ G2B ’ C B A0Y 1Y 2Y 3Y 4Y 5Y 6Y 7Y0 × × × × ×1 1 1 1 1 1 1 1 × × 1 × × ×1 1 1 1 1 1 1 1 × 1 × × × ×1 1 1 1 1 1 1 1 1 0 0 0 0 00 1 1 1 1 1 1 1 1 0 0 0 0 11 0 1 1 1 1 1 1 1 0 0 0 1 01 1 0 1 1 1 1 1 1 0 0 0 1 11 1 1 0 1 1 1 1 1 0 0 1 0 01 1 1 1 0 1 1 1 1 0 0 1 0 11 1 1 1 1 0 1 1 1 0 0 1 1 01 1 1 1 1 1 0 1 1 0 0 1 1 1 1 1 1 1 1 1 1 0其中C=2A ,B=1A ,A=0A 是输入端,0Y ~7Y 是输出端。

1S =G1, 2S =G2A ’, 3S =G2B ’是控制端。

2S 和 3S 低电平有效, 1S 高电平有效.当2S 3S 均为低电平及1S 为高电平时,译码器使能,输出0Y ~7Y 依赖当前输入逻辑变量2A 1A 0A 的状态。

如果2S 3S 和1S 有一个不满足要求,则输出0Y ~7Y 全为高电平,译码器被禁止。

由表可见,74LS138输出低电平有效。

三、数字信号发生器设置面板编辑和存放以4位16进制数表示的16位字信号,可以存放1024条字信号,地址范围为0—3FF (十六进制数),其显示内容可以通过滚动条上下移动。

74ls138译码器

仿真完毕,可以检验波形,看波形。

将此电路转化为比较简单的电路

转化过程如下:

点击File—>Create/Update—>Create Symbol Files for Current File

点击保存。

(4)新建图层BDF格式,

在Project中找到以ls138命名的简单元件。

再点击右键,选中Generate Pins for System Ports

页面如下:

保存,再运行仿真。

(4)分配引脚:

观察引脚颜色变化:

再将所绘制的电路,输入硬件设备中。

点击Start开始。

选择abc三个引脚放入一个模块中点击右键grouping和group在groupname中输入in点击ok第一栏位主线显示

(1)启动Quartus II,作电路图如下:

(2)

建立波形文件:

进入如下页面:

点击右键,选e Finder,点击

再点击At random intervals

点击OK

(3)点击Procesing,选中Simulator Tool进行仿真

进入后选中Simulator Tool,选中Functional,进行功能仿真。

点击Generate Functional Simulation Netlist,进行仿真,波形输出;

将引脚导入。

点击>>,将引脚导入Selected Nodes

回主页面:选择a、b、c三个引脚放入一个模块中,点击右键Grouping和Group

在Group name中输入IN,点击OK,第一栏位主线显示。

将a、b、c三个管脚全选,单击右键,选择Value—Random Value

设置仿真时间间隔。

3-8线译码器74LS138

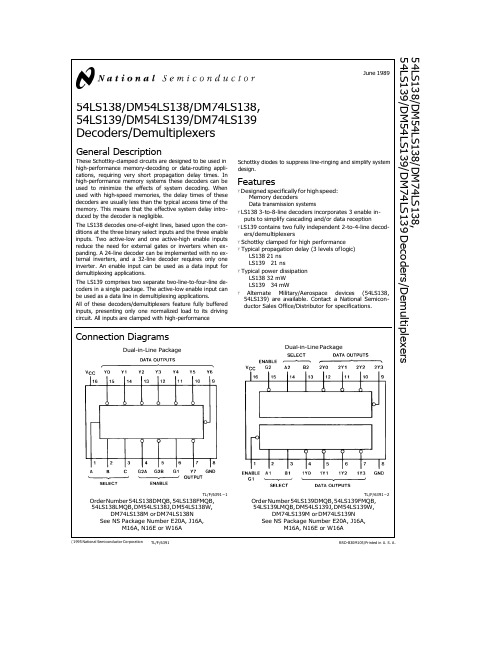

FeaturesYDesigned specifically for high speed: Memory decodersData transmission systemsY LS138 3-to-8-line decoders incorporates 3 enable in- puts to simplify cascading and/or data receptionY LS139 contains two fully independent 2-to-4-line decod- ers/demultiplexersY Schottky clamped for high performance Y Typical propagation delay (3 levels of logic)LS138 21 ns LS139 21 nsY Typical power dissipationLS138 32 mW LS139 34 mW Y Alternate Military/Aerospace devices (54LS138, 54LS139) are available. Contact a National Semicon- ductor Sales Office/Distributor for specifications.Connection DiagramsDual-in-Line PackageThese Schottky-clamped circuits are designed to be used in high-performance memory-decoding or data-routing appli- cations, requiring very short propagation delay times. In high-performance memory systems these decoders can be used to minimize the effects of system decoding. When used with high-speed memories, the delay times of these decoders are usually less than the typical access time of the memory. This means that the effective system delay intro- duced by the decoder is negligible.The LS138 decodes one-of-eight lines, based upon the con- ditions at the three binary select inputs and the three enable inputs. Two active-low and one active-high enable inputs reduce the need for external gates or inverters when ex- panding. A 24-line decoder can be implemented with no ex- ternal inverters, and a 32-line decoder requires only one inverter. An enable input can be used as a data input for demultiplexing applications.The LS139 comprises two separate two-line-to-four-line de- coders in a single package. The active-low enable input can be used as a data line in demultiplexing applications. All of these decoders/demultiplexers feature fully buffered inputs, presenting only one normalized load to its driving circuit. All inputs are clamped with high-performanceC 1995 National Semiconductor CorporationTL/F/6391RRD-B30M105/Printed in U. S. A.TL/F/6391 – 2Order Number 54LS139DMQB, 54LS139FMQB, 54LS139LMQB, DM54LS139J, D M54LS139W,DM74LS139M or D M74LS139N See NS Package Number E20A, J16A,M16A, N16E or W16ATL/F/6391 – 1 Order Number 54LS138DMQB, 54LS138FMQB, 54LS138LMQB, DM54LS138J, D M54LS138W,DM74LS138M or D M74LS138N See NS Package Number E20A, J16A,M16A, N16E or W16ADual-in-Line PackageSchottky diodes to suppress line-ringing and simplify systemdesign.54LS138/DM54LS138/DM74LS138,54LS139/DM54LS139/DM74LS139 Decoders/DemultiplexersGeneral DescriptionJune 198954LS138/DM54LS138/DM74LS138, 54LS139/DM54LS139/DM74LS139 Decoders/DemultiplexersLogic DiagramsLS138TL/F/6391 – 3LS139TL/F/6391 – 4Physical Dimensions inches (millimeters)Ceramic Leadless Chip Carrier Package (E)Order Number 54LS138LMQB or 54LS139LMQBNS Package Number E20A Array16-Lead Ceramic Dual-In-Line Package (J)Order Number 54LS138DMQB, 54LS139DMQB, DM54LS138J or DM54LS139JNS Package Number J16APhysical Dimensions inches (millimeters) (Continued)16-Lead Small Outline Molded Package (M)Order Number DM74LS138M or DM74LS139MNS Packge Number M16A16-Lead Molded Dual-In-Line Package (N)Order Number DM74LS138N or DM74LS139NNS Package Number N16ENational Semiconductor Japan Ltd.Tel: 81-043-299-2309 Fax: 81-043-299-2408National Semiconductor Hong Kong Ltd.13th Floor, Straight Block, Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon Hong KongTel: (852) 2737-1600 Fax: (852) 2736-9960National Semiconductor EuropeFax: (a 49) 0-180-530 85 86 Email: cnjwge @ Deutsch Tel: (a 49) 0-180-530 85 85 English Tel: (a 49) 0-180-532 78 32 Fran çais Tel: (a 49) 0-180-532 93 58 Italiano Tel: (a 49) 0-180-534 16 80National Semiconductor Corporation1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018LIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:1. Life support devices or systems are devices or2. A critical component is any component of a life systems which, (a) are intended for surgical implant support device or system whose failure to perform can into the body, or (b) support or sustain life, and whose be reasonably expected to cause the failure of the life failure to perform, when properly used in accordance support device or system, or to affect its safety or with instructions for use provided in the labeling, can effectiveness. be reasonably expected to result in a significant injury to the user.16-Lead Ceramic Flat Package (W)Order Number 54LS138FMQB, 54LS139FMQB, DM54LS138W or DM54LS139WNS Package Number W16APhysical Dimensions inches (millimeters) (Continued)54L S 138/D M 54L S 138/D M 74L S 138, 54L S 139/D M 54L S 139/D M 74L S 139 D e c o d e r s /D e m u l t i p l e x e r s。

74ls138引脚图-74ls138管脚图及功能真值表

74ls138引脚图-74ls138管脚图及功能真值表2007年12月17日 22:33 本站原创作者:本站用户评论(0)关键字:74ls138引脚图74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成 24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74L S1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

74ls138管脚图及功能真值表

74ls138引脚图74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

【例3.3.2】试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。

实验四74LS138实现全减器1页

实验四74LS138实现全减器1页

实验目的:

1. 了解74LS138译码器的工作原理。

实验材料:

1片74LS138译码器,1片74LS04反相器,1片74LS86异或门,若干个开关,若干个LED灯,几个电阻,面包板,连线等。

实验原理:

全减器是减数器的一种,可以用来完成两个数的减法运算。

全减器的输入包括两个减

数和上一位的借位,输出包括差和下一位的借位。

74LS138是一种八-三译码器,其输入有八路,输出有三路。

在74LS138的8个输入端中,只有1个输入端能够有效。

当某一输入端接到低电平时,将对应的输出端输出高电平,其余输出为低电平。

74LS04是一款集成电路,在六个反相器输出被用于构建至关重要的逻辑电路。

异或门是一种逻辑电路。

两个输入,一个输出。

如果两个输入相同,则输出为低电平;否则,输出为高电平。

实验步骤:

1. 用面包板连接电路如下图所示:

2. 将开关接入电路,拨动开关,观察LED灯的亮熄。

3. 分析电路,了解全减器的工作原理。

4. 用手动输入二进制数的方式,来测试全减器的运算结果。

实验结果:

1. 实现了全减器。

2. 能够通过拨动开关,测试全减器的运算结果。

通过学习和实践,了解了译码器的工作原理,并且实现了全减器。

实验中掌握了观察LED灯的亮熄,手动输入二进制测试全减器的方法,并且成功得到预期的运算结果。

二进制译码器74ls138

1

1

1

1

1

Y2

1

1

1

1

1

0

1

1

1

1

1

输出

Y3 Y4

1

1

1

1

1

1

1

1

1

1

1

1

0

1

1

0

1

1

1

1

1

1

Y5

1

1

1

1

1

1

1

1

0

1

1

Y6

1

1111来自111

1

0

1

Y7

1

1

1

1

1

1

1

1

1

1

0

4. 74LS138逻辑表达式

Y0 G1G 2A G 2B C B A

Y1 G1G 2A G 2B C BA

Y2 G1G 2A G 2B C B A

1 1

1 1

0 1

1 0

1 1

1 1

1 1

Y5

1

1

1

1

1

1

1

1

0

1

1

Y6

1

1

1

1

1

1

1

1

1

0

1

Y7

1

1

1

1

1

1

1

1

1

1

0

4. 74LS138逻辑表达式

Y 0 G1G 2 A G 2 B C B A

(1)

Y1 G1G 2 A G 2 B C B A

(2)