二输入端与非门设计

2输入数据选择器(mux2)集成电路课设报告

课程设计任务书学生姓名:助人为乐专业班级:不计得失指导教师:一定过工作单位:信息工程学院题目: 二输入数据选择器版图设计初始条件:计算机、ORCAD软件、L-EDIT软件要求完成的主要任务:1、课程设计工作量:2周2、技术要求:(1)学习ORCAD软件、L-EDIT软件软件。

(2)设计一个二输入数据选择器电路。

(3)利用ORCAD软件、L-EDIT软件对该电路进行系统设计、电路设计和版图设计,并进行相应的设计、模拟和仿真工作。

3、查阅至少5篇参考文献。

按《武汉理工大学课程设计工作规范》要求撰写设计报告书。

全文用A4纸打印,图纸应符合绘图规范。

时间安排:2013.11.22布置课程设计任务、选题;讲解课程设计具体实施计划与课程设计报告格式的要求;课程设计答疑事项。

2013.11.25-11.27学习ORCAD软件、L-EDIT软件,查阅相关资料,复习所设计内容的基本理论知识。

2013.11.28-12.5对二输入数据选择器电路进行设计仿真工作,完成课设报告的撰写。

2013.12.6提交课程设计报告,进行答辩。

指导教师签名:年月日系主任(或责任教师)签名:年月日目录1.绪论 (2)2.软件简介 (3)2.1Cadence简介 (3)2.2L-edit简介 (3)3.二输入多路选择器电路设计及仿真 (4)3.1数据选择器原理 (4)3.2电路原理图的绘制 (5)3.3电路图仿真 (6)4.集成电路版图设计 (7)4.1CMOS数字电路基本单元版图设计 (7)4.1.1反相器版图设计 (7)4.1.2与非门版图设计 (8)4.2整体版图设计 (9)4.3设计规则的验证及结果 (9)5.总结 (10)参考文献 (11)摘要I C(“集成电路”)产业是全球高新技术产业的前沿与核心,是最具活力和挑战性的战略产业。

自2000年来,在国家政策的大力支持下,我国集成电路产业得到了长足的发展,而作为集成电路产业最前沿的设计业更是呈现出“百花齐放”的繁荣景象。

二输入与非门表达式

二输入与非门表达式二输入与非门是数字电路中常见的逻辑门,其逻辑功能是对两个输入信号进行与操作,并将结果取反输出。

在本文中,我们将深入探讨二输入与非门的表达式及其应用。

二输入与非门的表达式可以表示为:输出等于输入A与输入B的逻辑与操作的结果取反。

即输出为非(A与B)。

在数字电路中,与非门通常用于控制电路中的开关,实现逻辑功能的控制。

以一个简单的例子来说明,假设我们要设计一个电路,当输入A和输入B同时为高电平时,输出为低电平;否则,输出为高电平。

这个功能可以通过二输入与非门来实现。

具体的电路设计如下:首先,我们将输入A和输入B连接到二输入与非门的两个输入端口上;然后,将二输入与非门的输出连接到输出端口上。

这样,当输入A和输入B同时为高电平时,经过与非门的逻辑与操作,输出为低电平;否则,输出为高电平。

通过这个例子,我们可以看出二输入与非门的表达式非常简单,但是在数字电路中的应用非常广泛。

它可以用于逻辑电路的设计、控制电路的开关控制等方面。

在实际应用中,我们可以通过多个二输入与非门的组合来实现更复杂的逻辑功能。

除了二输入与非门,数字电路中还有其他常见的逻辑门,如与门、非门、或门、异或门等。

它们都有各自的表达式和应用场景。

在数字电路的设计和实现中,我们可以根据具体的需求选择适合的逻辑门来实现所需的功能。

总结起来,二输入与非门是数字电路中常见的逻辑门之一,其表达式为非(A与B),用于对两个输入信号进行与操作,并将结果取反输出。

它在数字电路的设计和实现中有着广泛的应用。

通过合理的组合和应用,我们可以设计出满足各种需求的数字电路。

希望通过本文的介绍,读者对二输入与非门有更深入的了解,并能够在实际应用中灵活运用。

二输入端与非门设计.ppt

(6) 引入输入和输出脚:按步骤 (5) 选出2个输入脚

和1个输出脚。

第5章

组合逻辑电路设计

(7) 更 改 输 入 和 输 出 脚 的 脚 位 名 称 : 在 PIN_NAME 处双击鼠标左键,进行更名,输入脚为A、 B,输出脚为C。

Edit画面,2输入端与非门的电路符号如图5-2所示。

第5章

组合逻辑电路设计

(14) 创建电路包含文件:选取窗口菜单 File→Create Default Include File,产生用来代表目前所 设计电路的nand2.inc文件,供其他VHDL编译时使用, 如图5-3所示。 (15) 时间分析:选取窗口菜单Utilities→Analyze

(2) 保存:选取窗口菜单 File→Save ,出现对话框,

键入文件名nand2.gdf,单击OK按钮。

第5章

组合逻辑电路设计

(3) 指定项目名称,要求与文件名相同:选取窗口

菜单File→Project→Name,键入文件名nand2,单击OK 按钮。

(4) 确定对象的输入位置:在图形窗口内单击鼠标

电路的nand2 .inc文件,供其他VHDL编译时使用。 (11) 时间分析:选取窗口菜单Utilities→Analyze

第5章

组合逻辑电路设计

(6) 保存并查错:选取窗口菜单

File→Project→Save&Check,即可针对电路文件进行检查。 (7) 修改错误:针对Massage-Compiler窗口所提供的 信息修改电路文件,直到没有错误为止。 (8) 保存并编译:选取窗口菜单 File→Project→Save&Compile,即可进行编译,产生 nand2.sof烧写文件。

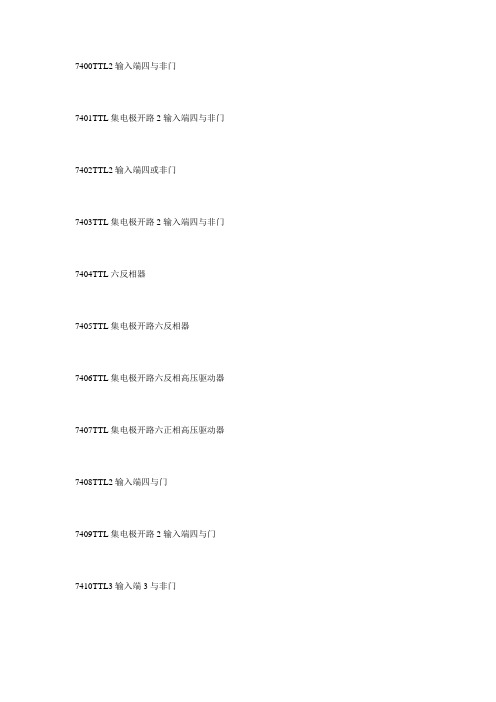

TTL2输入端四与非门

7400TTL2输入端四与非门7401TTL集电极开路2输入端四与非门7402TTL2输入端四或非门7403TTL集电极开路2输入端四与非门7404TTL六反相器7405TTL集电极开路六反相器7406TTL集电极开路六反相高压驱动器7407TTL集电极开路六正相高压驱动器7408TTL2输入端四与门7409TTL集电极开路2输入端四与门7410TTL3输入端3与非门74107TTL带清除主从双J-K触发器74109TTL带预置清除正触发双J-K触发器7411TTL3输入端3与门74112TTL带预置清除负触发双J-K触发器7412TTL开路输出3输入端三与非门74121TTL单稳态多谐振荡器74122TTL可再触发单稳态多谐振荡器74123TTL双可再触发单稳态多谐振荡器74125TTL三态输出高有效四总线缓冲门74126TTL三态输出低有效四总线缓冲门7413TTL4输入端双与非施密特触发器74132TTL2输入端四与非施密特触发器74133TTL13输入端与非门74136TTL四异或门74138TTL3-8线译码器/复工器74139TTL双2-4线译码器/复工器7414TTL六反相施密特触发器74145TTLBCD—十进制译码/驱动器7415TTL开路输出3输入端三与门74150TTL16选1数据选择/多路开关74153TTL双4选1数据选择器74154TTL4线—16线译码器74155TTL图腾柱输出译码器/分配器74156TTL开路输出译码器/分配器74157TTL同相输出四2选1数据选择器74158TTL反相输出四2选1数据选择器7416TTL开路输出六反相缓冲/驱动器74160TTL可预置BCD异步清除计数器74161TTL可予制四位二进制异步清除计数器74162TTL可预置BCD同步清除计数器74164TTL八位串行入/并行输出移位寄存器74165TTL八位并行入/串行输出移位寄存器74166TTL八位并入/串出移位寄存器74169TTL二进制四位加/减同步计数器7417TTL开路输出六同相缓冲/驱动器74170TTL开路输出4×4寄存器堆74173TTL三态输出四位D型寄存器74174TTL带公共时钟和复位六D触发器74175TTL带公共时钟和复位四D触发器74180TTL9位奇数/偶数发生器/校验器74181TTL算术逻辑单元/函数发生器74185TTL二进制—BCD代码转换器74190TTLBCD同步加/减计数器74191TTL二进制同步可逆计数器74192TTL可预置BCD双时钟可逆计数器74193TTL可预置四位二进制双时钟可逆计数器74194TTL四位双向通用移位寄存器74195TTL四位并行通道移位寄存器74196TTL十进制/二-十进制可预置计数锁存器74197TTL二进制可预置锁存器/计数器7420TTL4输入端双与非门7421TTL4输入端双与门7422TTL开路输出4输入端双与非门74221TTL双/单稳态多谐振荡器74240TTL八反相三态缓冲器/线驱动器74241TTL八同相三态缓冲器/线驱动器74243TTL四同相三态总线收发器74244TTL八同相三态缓冲器/线驱动器74245TTL八同相三态总线收发器74247TTLBCD—7段15V输出译码/驱动器74248TTLBCD—7段译码/升压输出驱动器74249TTLBCD—7段译码/开路输出驱动器74251TTL三态输出8选1数据选择器/复工器74253TTL三态输出双4选1数据选择器/复工器74256TTL双四位可寻址锁存器74257TTL三态原码四2选1数据选择器/复工器74258TTL三态反码四2选1数据选择器/复工器74259TTL八位可寻址锁存器/3-8线译码器7426TTL2输入端高压接口四与非门74260TTL5输入端双或非门74266TTL2输入端四异或非门7427TTL3输入端三或非门74273TTL带公共时钟复位八D触发器74279TTL四图腾柱输出S-R锁存器7428TTL2输入端四或非门缓冲器74283TTL4位二进制全加器74290TTL二/五分频十进制计数器74293TTL二/八分频四位二进制计数器74295TTL四位双向通用移位寄存器74298TTL四2输入多路带存贮开关74299TTL三态输出八位通用移位寄存器7430TTL8输入端与非门7432TTL2输入端四或门74322TTL带符号扩展端八位移位寄存器74323TTL三态输出八位双向移位/存贮寄存器7433TTL开路输出2输入端四或非缓冲器74347TTLBCD—7段译码器/驱动器74352TTL双4选1数据选择器/复工器74353TTL三态输出双4选1数据选择器/复工器74365TTL门使能输入三态输出六同相线驱动器74365TTL门使能输入三态输出六同相线驱动器74366TTL门使能输入三态输出六反相线驱动器74367TTL4/2线使能输入三态六同相线驱动器74368TTL4/2线使能输入三态六反相线驱动器7437TTL开路输出2输入端四与非缓冲器74373TTL三态同相八D锁存器74374TTL三态反相八D锁存器74375TTL4位双稳态锁存器74377TTL单边输出公共使能八D锁存器74378TTL单边输出公共使能六D锁存器74379TTL双边输出公共使能四D锁存器7438TTL开路输出2输入端四与非缓冲器74380TTL多功能八进制寄存器7439TTL开路输出2输入端四与非缓冲器74390TTL双十进制计数器74393TTL双四位二进制计数器7440TTL4输入端双与非缓冲器7442TTLBCD—十进制代码转换器74352TTL双4选1数据选择器/复工器74353TTL三态输出双4选1数据选择器/复工器74365TTL门使能输入三态输出六同相线驱动器74366TTL门使能输入三态输出六反相线驱动器74367TTL4/2线使能输入三态六同相线驱动器74368TTL4/2线使能输入三态六反相线驱动器7437TTL开路输出2输入端四与非缓冲器74373TTL三态同相八D锁存器74374TTL三态反相八D锁存器74375TTL4位双稳态锁存器74377TTL单边输出公共使能八D锁存器74378TTL单边输出公共使能六D锁存器74379TTL双边输出公共使能四D锁存器7438TTL开路输出2输入端四与非缓冲器74380TTL多功能八进制寄存器7439TTL开路输出2输入端四与非缓冲器74390TTL双十进制计数器74393TTL双四位二进制计数器7440TTL4输入端双与非缓冲器7442TTLBCD—十进制代码转换器74447TTLBCD—7段译码器/驱动器7445TTLBCD—十进制代码转换/驱动器74450TTL16:1多路转接复用器多工器74451TTL双8:1多路转接复用器多工器74453TTL四4:1多路转接复用器多工器7446TTLBCD—7段低有效译码/驱动器74460TTL十位比较器74461TTL八进制计数器74465TTL三态同相2与使能端八总线缓冲器74466TTL三态反相2与使能八总线缓冲器74467TTL三态同相2使能端八总线缓冲器74468TTL三态反相2使能端八总线缓冲器74469TTL八位双向计数器7447TTLBCD—7段高有效译码/驱动器7448TTLBCD—7段译码器/内部上拉输出驱动74490TTL双十进制计数器74491TTL十位计数器74498TTL八进制移位寄存器7450TTL2-3/2-2输入端双与或非门74502TTL八位逐次逼近寄存器74503TTL八位逐次逼近寄存器7451TTL2-3/2-2输入端双与或非门74533TTL三态反相八D锁存器74534TTL三态反相八D锁存器7454TTL四路输入与或非门74540TTL八位三态反相输出总线缓冲器7455TTL4输入端二路输入与或非门74563TTL八位三态反相输出触发器74564TTL八位三态反相输出D触发器74573TTL八位三态输出触发器74574TTL八位三态输出D触发器74645TTL三态输出八同相总线传送接收器74670TTL三态输出4×4寄存器堆7473TTL带清除负触发双J-K触发器7474TTL带置位复位正触发双D触发器7476TTL带预置清除双J-K触发器7483TTL四位二进制快速进位全加器7485TTL四位数字比较器7486TTL2输入端四异或门7490TTL可二/五分频十进制计数器7493TTL可二/八分频二进制计数器7495TTL四位并行输入\输出移位寄存器7497TTL6位同步二进制乘法器。

二输入与非门、或非门版图设计

课程名称Course 集成电路设计技术项目名称Item二输入与非门、或非门版图设计与非门电路的版图:.spc文件(瞬时分析):* Circuit Extracted by Tanner Research's L-Edit V7.12 / Extract V4.00 ;* TDB File: E:\cmos\yufeimen, Cell: Cell0* Extract Definition File: C:\Program Files\Tanner EDA\L-Edit\spr\morbn20.ext * Extract Date and Time: 05/25/2011 - 10:03.include H:\ml2_125.mdVPower VDD GND 5va A GND PULSE (0 5 0 5n 5n 100n 200n)vb B GND PULSE (0 5 0 5n 5n 50n 100n).tran 1n 400n.print tran v(A) v(B) v(F)* WARNING: Layers with Unassigned AREA Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* WARNING: Layers with Unassigned FRINGE Capacitance.* <Pad Comment>* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* <Poly1-Poly2 Capacitor>* WARNING: Layers with Zero Resistance.* <Pad Comment>* <Poly1-Poly2 Capacitor>* <NMOS Capacitor>* <PMOS Capacitor>* NODE NAME ALIASES* 1 = VDD (34,37)* 2 = A (29.5,6.5)* 3 = B (55.5,6.5)* 4 = F (42.5,6.5)* 6 = GND (25,-22)M1 VDD B F VDD PMOS L=2u W=9u AD=99p PD=58u AS=54p PS=30u* M1 DRAIN GATE SOURCE BULK (47.5 14.5 49.5 23.5)M2 F A VDD VDD PMOS L=2u W=9u AD=54p PD=30u AS=99p PS=58u* M2 DRAIN GATE SOURCE BULK (39.5 14.5 41.5 23.5)M3 F B 5 GND NMOS L=2u W=9.5u AD=52.25p PD=30u AS=57p PS=31u * M3 DRAIN GATE SOURCE BULK (47.5 -18 49.5 -8.5)M4 5 A GND GND NMOS L=2u W=9.5u AD=57p PD=31u AS=52.25p PS=30u * M4 DRAIN GATE SOURCE BULK (39.5 -18 41.5 -8.5)* Total Nodes: 6* Total Elements: 4* Extract Elapsed Time: 0 seconds.END与非门电路仿真波形图(瞬时分析):.spc文件(直流分析):* Circuit Extracted by Tanner Research's L-Edit V7.12 / Extract V4.00 ;* TDB File: E:\cmos\yufeimen, Cell: Cell0* Extract Definition File: C:\Program Files\Tanner EDA\L-Edit\spr\morbn20.ext * Extract Date and Time: 05/25/2011 - 10:03.include H:\ml2_125.mdVPower VDD GND 5va A GND 5vb B GND 5.dc va 0 5 0.02 vb 0 5 0.02.print dc v(F)* WARNING: Layers with Unassigned AREA Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* WARNING: Layers with Unassigned FRINGE Capacitance.* <Pad Comment>* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* <Poly1-Poly2 Capacitor>* WARNING: Layers with Zero Resistance.* <Pad Comment>* <Poly1-Poly2 Capacitor>* <NMOS Capacitor>* <PMOS Capacitor>* NODE NAME ALIASES* 1 = VDD (34,37)* 2 = A (29.5,6.5)* 3 = B (55.5,6.5)* 4 = F (42.5,6.5)* 6 = GND (25,-22)M1 VDD B F VDD PMOS L=2u W=9u AD=99p PD=58u AS=54p PS=30u* M1 DRAIN GATE SOURCE BULK (47.5 14.5 49.5 23.5)M2 F A VDD VDD PMOS L=2u W=9u AD=54p PD=30u AS=99p PS=58u* M2 DRAIN GATE SOURCE BULK (39.5 14.5 41.5 23.5)M3 F B 5 GND NMOS L=2u W=9.5u AD=52.25p PD=30u AS=57p PS=31u * M3 DRAIN GATE SOURCE BULK (47.5 -18 49.5 -8.5)M4 5 A GND GND NMOS L=2u W=9.5u AD=57p PD=31u AS=52.25p PS=30u * M4 DRAIN GATE SOURCE BULK (39.5 -18 41.5 -8.5)* Total Nodes: 6* Total Elements: 4* Extract Elapsed Time: 0 seconds.END与非门电路仿真波形图(直流分析):或非门电路的版图:.spc文件(瞬时分析):* Circuit Extracted by Tanner Research's L-Edit V7.12 / Extract V4.00 ;* TDB File: E:\cmos\huofeimen, Cell: Cell0* Extract Definition File: C:\Program Files\Tanner EDA\L-Edit\spr\morbn20.ext * Extract Date and Time: 05/25/2011 - 10:04.include H:\CMOS\ml2_125.mdVPower VDD GND 5va A GND PULSE (0 5 0 5n 5n 100n 200n)vb B GND PULSE (0 5 0 5n 5n 50n 100n).tran 1n 400n.print tran v(A) v(B) v(F)* WARNING: Layers with Unassigned AREA Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* WARNING: Layers with Unassigned FRINGE Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <Pad Comment>* <P Base Resistor>* <Poly1-Poly2 Capacitor>* WARNING: Layers with Zero Resistance.* <Pad Comment>* <Poly1-Poly2 Capacitor>* <NMOS Capacitor>* <PMOS Capacitor>* NODE NAME ALIASES* 1 = VDD (34,37)* 2 = A (29.5,6.5)* 3 = B (55.5,6)* 4 = F (42.5,6.5)* 5 = GND (25,-22)M1 6 A VDD VDD PMOS L=2u W=9u AD=54p PD=30u AS=49.5p PS=29u* M1 DRAIN GATE SOURCE BULK (39.5 14.5 41.5 23.5)M2 F B 6 VDD PMOS L=2u W=9u AD=49.5p PD=29u AS=54p PS=30u* M2 DRAIN GATE SOURCE BULK (47.5 14.5 49.5 23.5)M3 F A GND GND NMOS L=2u W=9.5u AD=57p PD=31u AS=104.5p PS=60u * M3 DRAIN GATE SOURCE BULK (39.5 -18 41.5 -8.5)M4 GND B F GND NMOS L=2u W=9.5u AD=104.5p PD=60u AS=57p PS=31u * M4 DRAIN GATE SOURCE BULK (47.5 -18 49.5 -8.5)* Total Nodes: 6* Total Elements: 4* Extract Elapsed Time: 0 seconds.END或非门电路仿真波形图(瞬时分析):.spc文件(直流分析):* Circuit Extracted by Tanner Research's L-Edit V7.12 / Extract V4.00 ;* TDB File: E:\cmos\huofeimen, Cell: Cell0* Extract Definition File: C:\Program Files\Tanner EDA\L-Edit\spr\morbn20.ext * Extract Date and Time: 05/25/2011 - 10:04.include H:\CMOS\ml2_125.mdVPower VDD GND 5va A GND 5vb B GND 5.dc va 0 5 0.02 vb 0 5 0.02.print dc v(F)* WARNING: Layers with Unassigned AREA Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* WARNING: Layers with Unassigned FRINGE Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <Pad Comment>* <P Base Resistor>* <Poly1-Poly2 Capacitor>* WARNING: Layers with Zero Resistance.* <Pad Comment>* <Poly1-Poly2 Capacitor>* <NMOS Capacitor>* <PMOS Capacitor>* NODE NAME ALIASES* 1 = VDD (34,37)* 2 = A (29.5,6.5)* 3 = B (55.5,6)* 4 = F (42.5,6.5)* 5 = GND (25,-22)M1 6 A VDD VDD PMOS L=2u W=9u AD=54p PD=30u AS=49.5p PS=29u* M1 DRAIN GATE SOURCE BULK (39.5 14.5 41.5 23.5)M2 F B 6 VDD PMOS L=2u W=9u AD=49.5p PD=29u AS=54p PS=30u* M2 DRAIN GATE SOURCE BULK (47.5 14.5 49.5 23.5)M3 F A GND GND NMOS L=2u W=9.5u AD=57p PD=31u AS=104.5p PS=60u * M3 DRAIN GATE SOURCE BULK (39.5 -18 41.5 -8.5)M4 GND B F GND NMOS L=2u W=9.5u AD=104.5p PD=60u AS=57p PS=31u * M4 DRAIN GATE SOURCE BULK (47.5 -18 49.5 -8.5)* Total Nodes: 6* Total Elements: 4* Extract Elapsed Time: 0 seconds.END或非门电路仿真波形图(直流分析):内容(方法、步骤、要求或考核标准及所需工具、设备等)一、实训设备与工具1.PVI计算机一台;2.Tanner Pro集成电路设计软件二、实训方法、步骤与要求1.二输入与非门电路的线路结构2.二输入或非门电路的线路结构3.CMOS倒相器电路的版图4.根据与非门、或非门线路结构,在一个工程中,重新新建两个新CELL,分别对应与非门和或非门版图,并设计与非门、或非版图结构。

非线性元件特性曲线和TTL与非门传输特性的测定讲解

能够实现与逻辑运算的单元电路叫做与门,实现或逻辑运 算的单元电路叫做或门,实现非逻辑运算的单元电路叫做非 门,非门也被叫做反相器。 在数字电路中,通常高电平用 1 表示,低电平用 0 表示。 这种逻辑表示方法称为正逻辑。

如果用 0 表示高电平,用 1 表示低电平,则这种逻辑表示 方法称为负逻辑。

一般情况下,都用正逻辑。

i

对于二极管等非线性元件来 说,电压—电流的关系曲线不 是直线,而是曲线。 这条曲线就称为二极管的伏 安特性曲线。

u

二极管的伏安特性曲线可以通过逐点测量字万用表的内阻较大,所以可用电流表外 接法来测量。如图。

mA

V

R

测量时,当 电流变化较大时, 电压间隔应取得 小些。

二极管特性测试 TTL与非门参数测试

二极管特性和TTL与非门特性测试实验电路板

电 源 ╋

电流表

正反向转换开关

短路块 万用表 (电压档)

实验任务:

设计一个测试二极管伏安特性的电路和记录数据 的表格,

拟定测试二极管伏安特性的实验方案,测试二极 管伏安特性,描绘二极管的伏安特性曲线。 注意事项:

实验时应先把电压调到 0 V,然后逐步增大电压。 测试时应根据电压-电流的变化情况,确定测试电 压的间隔。先测正向。 测试最大电流到 5mA。

非线性元件特性曲线

TTL与非门传输特性 的测定

一、实验目的

1.掌握非线性元件特性曲线和门电路主要参数 的测试方法。 2.掌握TTL门电路电压传输特性的测试方法。 3.掌握测试电路的设计与装调。 4.掌握非线性元件二极管伏安特性和门电路的 传输特性。

二、实验原理

1. 二极管伏安特性曲线的测定 电路中元件两端的电压与流过元件的电流服从欧姆定律, 呈线性关系的,这类元件被称为线性元件,如电阻。 如果把电阻两端的电压取为横坐标,电流取为纵坐标,画 出的电压—电流的关系曲线是一条在u-i平面上通过原点的直线, 这条直线称为该元件的伏安特性 。

二输入端与非门设计

二输入端与非门设计

二输入端与非门是一种基本的逻辑门电路,用于将输入的逻辑信号进行反转。

它由两个输入端和一个输出端组成,当两个输入信号中的任意一个为高电平时,输出信号为低电平;只有当两个输入信号都为低电平时,输出信号才会为高电平。

1.原理

在二输入端与非门中,当输入信号的两个输入端之一或者同时为高电平时,输入电阻将会导通,将电流流向负载电阻,并将输出线上的电压拉低,表示低电平。

当输入信号两个输入端都为低电平时,两个输入电阻都截止,负载电阻上没有电流流过,输出线上的电压被拉高,表示高电平。

2.设计

首先,选择一个适合的晶体管,常用的有NPN型和PNP型晶体管。

在这里,我们选择一个NPN型晶体管。

接下来,连接两个输入端。

一个输入端通过电阻接到电源电压(Vcc),另一个输入端通过电阻接到地线,同时这两个输入端也与晶体管的基极连接。

然后,将晶体管的发射极接地,集电极与输出端相连接。

负载电阻连接在输出端到电源电压(Vcc)之间。

最后,根据需要添加外部电路。

例如,可以添加降噪电路、电流限制电路等。

3.工作原理

当输入信号的两个输入端之一或者同时为高电平时,输入电阻导通,晶体管的基极-发射极之间的电压使得晶体管导通,导通时的饱和电压使得输出端电压拉低,表示低电平。

当输入信号的两个输入端都为低电平时,两个输入电阻截止,晶体管的基极-发射极之间的电压使得晶体管截止,输出端上的电压由于负载电阻拉高,表示高电平。

总结:。

用与非门设计的一开关报警控制电路

摘要本次课程设计电路为用与非门设计的一开关报警控制电路,电路有A、B、C三只开关,只有在开关A接通的条件下,开关B才能接通,而开关C则只有在开关B接通的条件下才能接通,违反这一操作规程,则发出报警信号。

除此主要功能外,电路还存在一些拓展功能。

当开关B接电源Vcc且开关C接地时,将开关A接时钟脉冲信号,则电路将会输出与输入时钟脉冲反向的脉冲信号。

关键词:与非门,与门,反相器,声光报警电路。

1.2 非门实验设计电路的非门选用芯片74LS04。

74LS04为六反相器,其逻辑表达式为:L=A 。

其功能表如表1-2所示,其管脚图如图1-2所示,其中1A -6A 为 输入端 ,1Y -6Y 为 输出端。

表1-2 74ls04功能表1.3 与门表1-3 74LS08功能表1.5 蜂鸣器及发光二极管蜂鸣器是一种一体化结构的电子讯响器,采用直流电压供电,广泛应用于计算机、打印机、复印机、报警器、电子玩具、汽车电子设备、机、定时器等电子产品中作发声器件。

发光二极管是半导体二极管的一种,可以把电能转化成光能,常简写为LED。

发光二极管与普通二极管一样是由一个PN结组成,也具有单向导电性。

当给发光二极管加上正向电压后,从P区注入到N区的空穴和由N区注入到P区的电子,在PN结附近数微米分别与N区的电子和P区的空穴复合,产生自发辐射的荧光。

不同的半导体材料中电子和空穴所处的能量状态不同。

当电子和空穴复合时释放出的能量多少不同,释放出的能量越多,则发出的光的波长越短。

常用的是发红光、绿光或黄光的二极管。

发光二极管的反向击穿电压约5伏。

它的正向伏安特性曲线很陡,使用时必须串联限流电阻以控制通过管子的电流。

本实验设计电路选用蜂鸣器及发光二极管共同构成声光报警电路。

2电路的设计根据题要求,用逻辑门来实现电路功能。

首先规定:开关开用逻辑高电平1来表示,开关断用逻辑低电平0来表示。

用Y 来表示报警信号。

当Y=0时表示操作正确,若操作错误W=1即报警。

或门电路

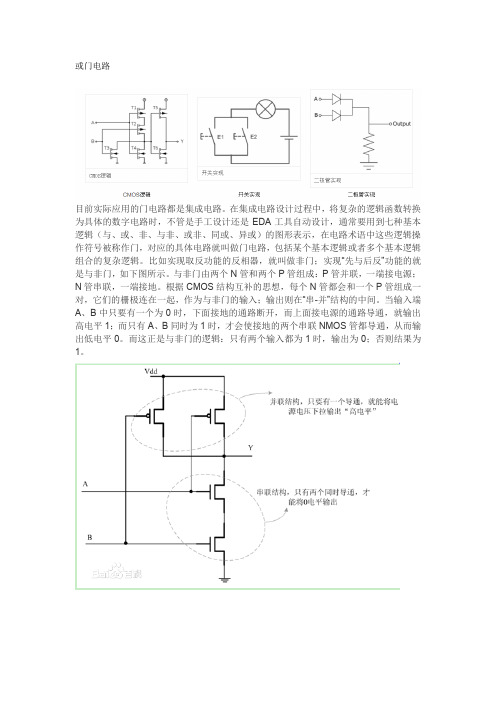

或门电路目前实际应用的门电路都是集成电路。

在集成电路设计过程中,将复杂的逻辑函数转换为具体的数字电路时,不管是手工设计还是EDA工具自动设计,通常要用到七种基本逻辑(与、或、非、与非、或非、同或、异或)的图形表示,在电路术语中这些逻辑操作符号被称作门,对应的具体电路就叫做门电路,包括某个基本逻辑或者多个基本逻辑组合的复杂逻辑。

比如实现取反功能的反相器,就叫做非门;实现“先与后反”功能的就是与非门,如下图所示。

与非门由两个N管和两个P管组成:P管并联,一端接电源;N管串联,一端接地。

根据CMOS结构互补的思想,每个N管都会和一个P管组成一对,它们的栅极连在一起,作为与非门的输入;输出则在“串-并”结构的中间。

当输入端A、B中只要有一个为0时,下面接地的通路断开,而上面接电源的通路导通,就输出高电平1;而只有A、B同时为1时,才会使接地的两个串联NMOS管都导通,从而输出低电平0。

而这正是与非门的逻辑:只有两个输入都为1时,输出为0;否则结果为1。

CMOS逻辑门电路CMOS逻辑门电路是在TTL电路问世之后,所开发出的第二种广泛应用的数字集成器件,从发展趋势来看,由于制造工艺的改进,CMOS电路的性能有可能超越TTL而成为占主导地位的逻辑器件。

CMOS电路的工作速度可与TTL相比较,而它的功耗和抗干扰能力则远优于TTL。

此外,几乎所有的超大规模存储器件,以及PLD器件都采用CMOS艺制造,且费用较低。

早期生产的CMOS门电路为4000系列,随后发展为4000B系列。

当前与TTL兼容的CMO 器件如74HCT系列等可与TTL器件交换使用。

下面首先讨论CMOS反相器,然后介绍其他CMO 逻辑门电路。

MOS管结构图MOS管主要参数:1.开启电压V T·开启电压(又称阈值电压):使得源极S和漏极D之间开始形成导电沟道所需的栅极电压;·标准的N沟道MOS管,V T约为3~6V;·通过工艺上的改进,可以使MOS管的V T值降到2~3V。

电子技术基础(数字部分)第五版答案康华光

第一章数字逻辑习题1.1数字电路与数字信号1.1.2 图形代表的二进制数0101101001.1.4一周期性数字波形如图题所示,试计算:(1)周期;(2)频率;(3)占空比例MSBLSB0 1 2 11 12 (ms)解:因为图题所示为周期性数字波,所以两个相邻的上升沿之间持续的时间为周期,T=10ms 频率为周期的倒数,f=1/T=1/0.01s=100HZ占空比为高电平脉冲宽度与周期的百分比,q=1ms/10ms*100%=10%1.2数制1.2.2将下列十进制数转换为二进制数,八进制数和十六进制数(要求转换误差不大于 42. (2)127 (4)2.718解:(2)(127)D=-1=(10000000)B-1=(1111111)B=(177)O=(7F)H 72(4)(2.718)D=(10.1011)B=(2.54)O=(2.B)H1.4二进制代码1.4.1将下列十进制数转换为8421BCD码:(1)43 (3)254.25解:(43)D=(01000011)BCD1.4.3试用十六进制写书下列字符繁荣ASCⅡ码的表示:P28(1)+ (2)@ (3)you (4)43解:首先查出每个字符所对应的二进制表示的ASCⅡ码,然后将二进制码转换为十六进制数表示。

(1)“+”的ASCⅡ码为0101011,则(00101011)B=(2B)H(2)@的ASCⅡ码为1000000,(01000000)B=(40)H(3)you的ASCⅡ码为本1111001,1101111,1110101,对应的十六进制数分别为79,6F,75(4)43的ASCⅡ码为0110100,0110011,对应的十六紧张数分别为34,331.6逻辑函数及其表示方法1.6.1在图题1. 6.1中,已知输入信号A,B`的波形,画出各门电路输出L的波形。

解: (a)为与非, (b)为同或非,即异或第二章逻辑代数习题解答2.1.1 用真值表证明下列恒等式(3)ABABAB⊕=+(A⊕B)=AB+AB 解:真值表如下ABAB⊕ABABAB⊕AB+AB111111111111由最右边2栏可知,与AB+AB的真值表完全相同。

组合逻辑实验报告

篇一:组合逻辑电路实验报告甘肃政法学院本科生实验报告(组合逻辑电路的设计)姓名: 学院: 专业: 班级:实验课程名称:数字电子技术基础实验日期: 指导教师及职称: 实验成绩: 开课时间:甘肃政法学院实验管理中心印制篇二:组合逻辑电路实验报告课程名称:数字电子技术基础实验指导老师:樊伟敏实验名称:组合逻辑电路实验实验类型:设计类同组学生姓名:__________ 一、实验目的和要求(必填)二、实验内容和原理(必填)三、主要仪器设备(必填)五、实验数据记录和处理七、讨论、心得一.实验目的1.加深理解全加器和奇偶位判断电路等典型组合逻辑电路的工作原理。

2.熟悉74ls00、74ls11、74ls55等基本门电路的功能及其引脚。

3.掌握组合集成电路元件的功能检查方法。

4.掌握组合逻辑电路的功能测试方法及组合逻辑电路的设计方法。

二、主要仪器设备74ls00(与非门) 74ls55(与或非门) 74ls11(与门)导线电源数电综合实验箱三、实验内容和原理及结果四、操作方法和实验步骤六、实验结果与分析(必填)实验报告(一)一位全加器1.1 实验原理:全加器实现一位二进制数的加法,输入有被加数、加数和来自相邻低位的进位;输出有全加和与向高位的进位。

i-1异或门可通过ai ?bi?ab?ab,即一个与非门;(74ls00),一个与或非门(74ls55)来实现。

ci = ai bi +(ai?bi)c再取非,即一个非门(i-1?ai bi +(ai?bi)ci-1,通过一个与或非门ai bi +(ai?bi)ci-1,用与非门)实现。

1.4 仿真与实验电路图:仿真与实验电路图如图 1 所示。

图11实验名称:组合逻辑实验姓名:学号:1.5 实验数据记录以及实验结果全加器实验测试结果满足全加器的功能,真值表:(二)奇偶位判断器2.1 实验原理:数码奇偶位判断电路是用来判别一组代码中含 1 的位数是奇数还是偶数的一种组合电路。

集成电路实验报告 反相器与非门设计

集成电路集中上机实验报告——反相器、与非门设计学院:专业:姓名:学号:一、实验目的(一)全面了解Schematic设计环境,并学会运用(二)掌握与非门、或非门、反相器等电路原理图输入方法(三)掌握逻辑符号创建方法二、实验原理启动Schematic Editor后,在命令解释窗口CIW中,打开任意库与单元中的Schematic视图,浏览Schematic Editing窗口,具体介绍如下:图2.1 Schematic Editing窗口菜单栏中可选菜单有Tool、Design、Window、Edit、Add、Check、Sheet、Options等项。

图标栏内的所有命令都可以在菜单栏实现,图标栏提供使用频率较高的一些菜单为快捷方式,旨在提高设计效率。

在设计过程中,除了可以使用图标快捷方式外,还有盲键(Bindkey)快捷方式。

Cadence系统安装过程中已经设置了通用的盲键,但用户可以根据自己的需要自行设置,在CIW窗口中,选择Options→Bindkeys,可以对所有设置的盲键自定义。

Cadence系统支持3D鼠标,左、中、右分别定义为LMB、MMB、RMB。

LMB用于点击和选择之用,MMB用于辅助编辑,RMB与LMB配合使用,在调查元件属性,局域放大,元件旋转等方面都有应用,在具体实验过程中有详细说明。

在所有元件的添加中,必须定义元件的属性。

最后,为了后续设计中执行仿真,每个元件必须具有物理模型(Model),在lab3中将有实例说明。

三、电路原理图设计的一般流程(一)创建库与视图(二)添加元件:在Schematic Editing窗口中,选择Add→Instance。

(三)添加Pins :在左侧Tool bar图标栏中选择pin icon图标,出现Add form,在Pin names栏中输入。

(四)添加Sources和Ground:选择Add→Instance,在Library column中选择analogLib,再选择vdd并添加到schematic中。

CMOS二输入与非门的设计

CMOS二输入与非门的设计CMOS(Complementary Metal-Oxide-Semiconductor)是一种常用的集成电路技术,它由N型和P型MOS(Metal-Oxide-Semiconductor)晶体管的互补结合构成。

CMOS技术具有功耗低、抗噪声能力强、集成度高等优点,广泛应用于数字逻辑电路设计中。

二输入与非门是最基本的逻辑门之一,它的输出与输入相反。

在CMOS技术中,二输入与非门的设计主要涉及到MOS晶体管的连接方式和输入信号的处理。

首先,我们需要了解CMOS技术中的N型和P型MOS晶体管的特性。

N型MOS 晶体管具有三个端口:栅(G),漏极(D)和源极(S)。

当栅极电压高于阈值电压时,N型MOS晶体管导通;当栅极电压低于阈值电压时,N型MOS晶体管截止。

P 型MOS晶体管也具有类似的特性,但是当栅极电压低于阈值电压时导通。

这种互补关系使得CMOS技术能够实现低功耗和高抗噪声能力。

在二输入与非门的设计中,我们可以使用两个N型MOS晶体管和两个P型MOS 晶体管来实现。

以下是一种常见的二输入与非门的CMOS电路设计:1. 首先,将两个N型MOS晶体管的漏极连接在一起,并与二输入与非门的输出端相连。

这个连接点称为输出节点。

2. 将两个P型MOS晶体管的漏极连接在一起,并与输出节点相连。

3. 一个N型MOS晶体管的栅极连接到输入信号A,另一个N型MOS晶体管的栅极连接到输入信号B。

4. 一个P型MOS晶体管的栅极连接到输入信号A,另一个P型MOS晶体管的栅极连接到输入信号B。

5. 将两个N型MOS晶体管的源极连接到地,将两个P型MOS晶体管的源极连接到电源Vdd。

通过这样的设计,当输入信号A和B都为高电平时,N型MOS晶体管导通,使得输出节点接地,输出低电平。

当输入信号A和B中至少一个为低电平时,N型MOS晶体管截止,P型MOS晶体管导通,使得输出节点连接到电源Vdd,输出高电平。

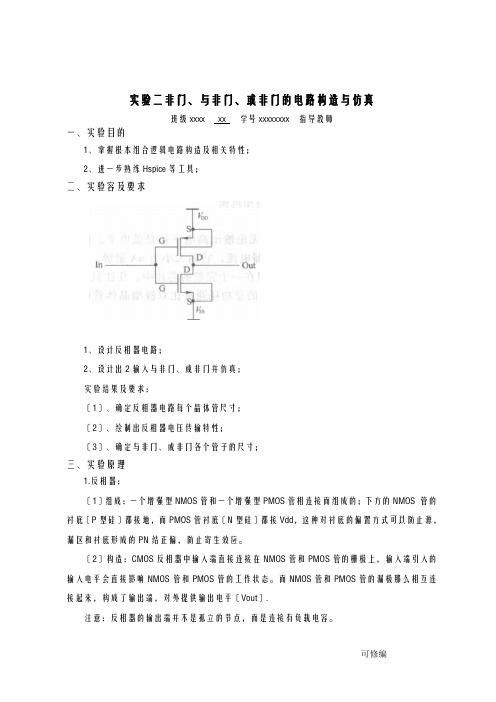

非门,与非门,或非门的电路结构与仿真剖析

实验二非门、与非门、或非门的电路结构与仿真班级xxxx 姓名xx 学号xxxxxxxx 指导老师一、实验目的1、掌握基本组合逻辑电路结构及相关特性;2、进一步熟练Hspice等工具;二、实验内容及要求1、设计反相器电路;2、设计出2输入与非门、或非门并仿真;实验结果及要求:(1)、确定反相器电路每个晶体管尺寸;(2)、绘制出反相器电压传输特性;(3)、确定与非门、或非门各个管子的尺寸;三、实验原理1.反相器:(1)组成:一个增强型NMOS管和一个增强型PMOS管相连接而组成的;下方的NMOS 管的衬底(P型硅)都接地,而PMOS管衬底(N型硅)都接Vdd,这种对衬底的偏置方式可以避免源,漏区和衬底形成的PN结正偏,防止寄生效应。

(2)结构:CMOS反相器中输入端直接连接在NMOS管和PMOS管的栅极上,输入端引入的输入电平会直接影响NMOS管和PMOS管的工作状态。

而NMOS管和PMOS管的漏极则相互连接起来,构成了输出端,对外提供输出电平(Vout).注意:反相器的输出端并不是孤立的节点,而是连接有负载电容。

( 3 )在CMOS反相器中,NMOS管和PMOS管的栅源电压和漏源电压与输入,输出电平的关系为:V(GSN)= V(in);V(DSN)=V(out)V(GSP)=V(in)-V(DD);V(DSP)=V(out)-V(DD);备注:G为栅极,S为源极,D为漏极。

(5)反相器的工作原理:静态工作的CMOS反相器,当输入为逻辑值“0”时(V(in)= 0V),NMOS管的接地端为源极,NMOS管上的栅源电压为0V,而PMOS管接V(DD)的是源极,PMOS管的栅源电压为-V(DD).这就使得NMOS管处于截止状态而PMOS管处于导通状态;通过导通的PMOS管,在电源电压V(DD)与输出端连接的负载电容之间建立起了导电通路。

可以将负载电容充电到V(DD),使得输出的逻辑值变为“1”;当输入为逻辑值“1”时(此时的输入电平为V(DD),即V(in)=V(DD)),由于PMOS管的栅源电压为0V,而NMOS管的栅源电压为V(DD),使得PMOS管处于截止状态而NMOS管处于导通状态,这样就在负载电容与地电极之间通过NMOS管建立起了导电通路,使得负载电容被放电到0V,这就使输出逻辑值变为“0”。

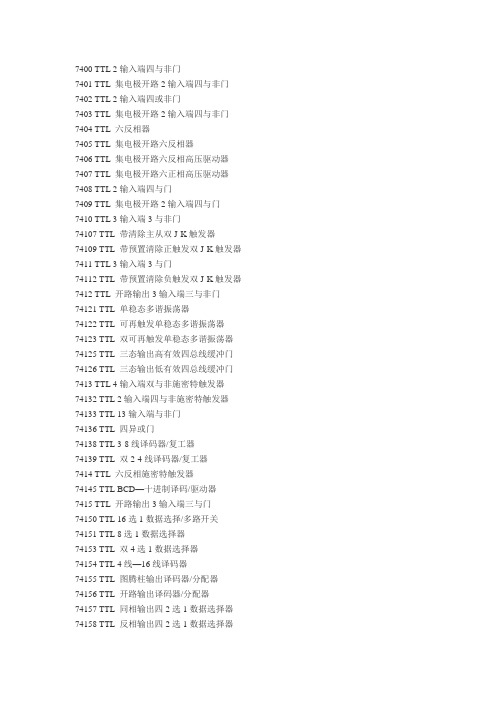

7400 TTL 2输入端四与非门

7400 TTL 2输入端四与非门7401 TTL 集电极开路2输入端四与非门7402 TTL 2输入端四或非门7403 TTL 集电极开路2输入端四与非门7404 TTL 六反相器7405 TTL 集电极开路六反相器7406 TTL 集电极开路六反相高压驱动器7407 TTL 集电极开路六正相高压驱动器7408 TTL 2输入端四与门7409 TTL 集电极开路2输入端四与门7410 TTL 3输入端3与非门74107 TTL 带清除主从双J-K触发器74109 TTL 带预置清除正触发双J-K触发器7411 TTL 3输入端3与门74112 TTL 带预置清除负触发双J-K触发器7412 TTL 开路输出3输入端三与非门74121 TTL 单稳态多谐振荡器74122 TTL 可再触发单稳态多谐振荡器74123 TTL 双可再触发单稳态多谐振荡器74125 TTL 三态输出高有效四总线缓冲门74126 TTL 三态输出低有效四总线缓冲门7413 TTL 4输入端双与非施密特触发器74132 TTL 2输入端四与非施密特触发器74133 TTL 13输入端与非门74136 TTL 四异或门74138 TTL 3-8线译码器/复工器74139 TTL 双2-4线译码器/复工器7414 TTL 六反相施密特触发器74145 TTL BCD—十进制译码/驱动器7415 TTL 开路输出3输入端三与门74150 TTL 16选1数据选择/多路开关74151 TTL 8选1数据选择器74153 TTL 双4选1数据选择器74154 TTL 4线—16线译码器74155 TTL 图腾柱输出译码器/分配器74156 TTL 开路输出译码器/分配器74157 TTL 同相输出四2选1数据选择器74158 TTL 反相输出四2选1数据选择器7416 TTL 开路输出六反相缓冲/驱动器74160 TTL 可预置BCD异步清除计数器74161 TTL 可予制四位二进制异步清除计数器74162 TTL 可预置BCD同步清除计数器74163 TTL 可予制四位二进制同步清除计数器74164 TTL 八位串行入/并行输出移位寄存器74165 TTL 八位并行入/串行输出移位寄存器74166 TTL 八位并入/串出移位寄存器74169 TTL 二进制四位加/减同步计数器7417 TTL 开路输出六同相缓冲/驱动器74170 TTL 开路输出4×4寄存器堆74173 TTL 三态输出四位D型寄存器74174 TTL 带公共时钟和复位六D触发器74175 TTL 带公共时钟和复位四D触发器74180 TTL 9位奇数/偶数发生器/校验器74181 TTL 算术逻辑单元/函数发生器74185 TTL 二进制—BCD代码转换器74190 TTL BCD同步加/减计数器74191 TTL 二进制同步可逆计数器74192 TTL 可预置BCD双时钟可逆计数器74193 TTL 可预置四位二进制双时钟可逆计数器74194 TTL 四位双向通用移位寄存器74195 TTL 四位并行通道移位寄存器74196 TTL 十进制/二-十进制可预置计数锁存器74197 TTL 二进制可预置锁存器/计数器7420 TTL 4输入端双与非门7421 TTL 4输入端双与门7422 TTL 开路输出4输入端双与非门74221 TTL 双/单稳态多谐振荡器74240 TTL 八反相三态缓冲器/线驱动器74241 TTL 八同相三态缓冲器/线驱动器74243 TTL 四同相三态总线收发器74244 TTL 八同相三态缓冲器/线驱动器74245 TTL 八同相三态总线收发器74247 TTL BCD—7段15V输出译码/驱动器74248 TTL BCD—7段译码/升压输出驱动器74249 TTL BCD—7段译码/开路输出驱动器74251 TTL 三态输出8选1数据选择器/复工器74253 TTL 三态输出双4选1数据选择器/复工器74256 TTL 双四位可寻址锁存器74257 TTL 三态原码四2选1数据选择器/复工器74258 TTL 三态反码四2选1数据选择器/复工器74259 TTL 八位可寻址锁存器/3-8线译码器7426 TTL 2输入端高压接口四与非门74260 TTL 5输入端双或非门74266 TTL 2输入端四异或非门7427 TTL 3输入端三或非门74273 TTL 带公共时钟复位八D触发器74279 TTL 四图腾柱输出S-R锁存器7428 TTL 2输入端四或非门缓冲器74283 TTL 4位二进制全加器74290 TTL 二/五分频十进制计数器74293 TTL 二/八分频四位二进制计数器74295 TTL 四位双向通用移位寄存器74298 TTL 四2输入多路带存贮开关74299 TTL 三态输出八位通用移位寄存器7430 TTL 8输入端与非门7432 TTL 2输入端四或门74322 TTL 带符号扩展端八位移位寄存器74323 TTL 三态输出八位双向移位/存贮寄存器7433 TTL 开路输出2输入端四或非缓冲器74347 TTL BCD—7段译码器/驱动器74352 TTL 双4选1数据选择器/复工器74353 TTL 三态输出双4选1数据选择器/复工器74365 TTL 门使能输入三态输出六同相线驱动器74365 TTL 门使能输入三态输出六同相线驱动器74366 TTL 门使能输入三态输出六反相线驱动器74367 TTL 4/2线使能输入三态六同相线驱动器74368 TTL 4/2线使能输入三态六反相线驱动器7437 TTL 开路输出2输入端四与非缓冲器74373 TTL 三态同相八D锁存器74374 TTL 三态反相八D锁存器74375 TTL 4位双稳态锁存器74377 TTL 单边输出公共使能八D锁存器74378 TTL 单边输出公共使能六D锁存器74379 TTL 双边输出公共使能四D锁存器7438 TTL 开路输出2输入端四与非缓冲器74380 TTL 多功能八进制寄存器7439 TTL 开路输出2输入端四与非缓冲器74390 TTL 双十进制计数器74393 TTL 双四位二进制计数器7440 TTL 4输入端双与非缓冲器7442 TTL BCD—十进制代码转换器74352 TTL 双4选1数据选择器/复工器74353 TTL 三态输出双4选1数据选择器/复工器74365 TTL 门使能输入三态输出六同相线驱动器74366 TTL 门使能输入三态输出六反相线驱动器74367 TTL 4/2线使能输入三态六同相线驱动器74368 TTL 4/2线使能输入三态六反相线驱动器7437 TTL 开路输出2输入端四与非缓冲器74373 TTL 三态同相八D锁存器74374 TTL 三态反相八D锁存器74375 TTL 4位双稳态锁存器74377 TTL 单边输出公共使能八D锁存器74378 TTL 单边输出公共使能六D锁存器74379 TTL 双边输出公共使能四D锁存器7438 TTL 开路输出2输入端四与非缓冲器74380 TTL 多功能八进制寄存器7439 TTL 开路输出2输入端四与非缓冲器74390 TTL 双十进制计数器74393 TTL 双四位二进制计数器7440 TTL 4输入端双与非缓冲器7442 TTL BCD—十进制代码转换器74447 TTL BCD—7段译码器/驱动器7445 TTL BCD—十进制代码转换/驱动器74450 TTL 16:1多路转接复用器多工器74451 TTL 双8:1多路转接复用器多工器74453 TTL 四4:1多路转接复用器多工器7446 TTL BCD—7段低有效译码/驱动器74460 TTL 十位比较器74461 TTL 八进制计数器74465 TTL 三态同相2与使能端八总线缓冲器74466 TTL 三态反相2与使能八总线缓冲器74467 TTL 三态同相2使能端八总线缓冲器74468 TTL 三态反相2使能端八总线缓冲器74469 TTL 八位双向计数器7447 TTL BCD—7段高有效译码/驱动7448 TTL BCD—7段译码器/内部上拉输出驱动74490 TTL 双十进制计数器74491 TTL 十位计数器74498 TTL 八进制移位寄存器7450 TTL 2-3/2-2输入端双与或非门74502 TTL 八位逐次逼近寄存器74503 TTL 八位逐次逼近寄存器7451 TTL 2-3/2-2输入端双与或非门74533 TTL 三态反相八D锁存器74534 TTL 三态反相八D锁存器7454 TTL 四路输入与或非门74540 TTL 八位三态反相输出总线缓冲器7455 TTL 4输入端二路输入与或非门74563 TTL 八位三态反相输出触发器74564 TTL 八位三态反相输出D触发器74573 TTL 八位三态输出触发器74574 TTL 八位三态输出D触发器74645 TTL 三态输出八同相总线传送接收器74670 TTL 三态输出4×4寄存器堆7473 TTL 带清除负触发双J-K触发器7474 TTL 带置位复位正触发双D触发器7476 TTL 带预置清除双J-K触发器7483 TTL 四位二进制快速进位全加器7485 TTL 四位数字比较器7486 TTL 2输入端四异或门7490 TTL 可二/五分频十进制计数器7493 TTL 可二/八分频二进制计数器7495 TTL 四位并行输入\输出移位寄存器7497 TTL 6位同步二进制乘法器型号器件名称厂牌备注CD4000 双3输入端或非门+单非门TICD4001 四2输入端或非门HIT/NSC/TI/GOLCD4002 双4输入端或非门NSCCD4006 18位串入/串出移位寄存器NSCCD4007 双互补对加反相器NSCCD4008 4位超前进位全加器NSCCD4009 六反相缓冲/变换器NSCCD4010 六同相缓冲/变换器NSCCD4011 四2输入端与非门HIT/TICD4012 双4输入端与非门NSCCD4013 双主-从D型触发器FSC/NSC/TOSCD4014 8位串入/并入-串出移位寄存器NSCCD4015 双4位串入/并出移位寄存器TICD4016 四传输门FSC/TICD4017 十进制计数/分配器FSC/TI/MOTCD4018 可预制1/N计数器NSC/MOTCD4019 四与或选择器PHICD4020 14级串行二进制计数/分频器FSCCD4021 08位串入/并入-串出移位寄存器PHI/NSCCD4022 八进制计数/分配器NSC/MOT型号器件名称厂牌备注CD4023 三3输入端与非门NSC/MOT/TICD4024 7级二进制串行计数/分频器NSC/MOT/TICD4025 三3输入端或非门NSC/MOT/TICD4026 十进制计数/7段译码器NSC/MOT/TICD4027 双J-K触发器NSC/MOT/TICD4028 BCD码十进制译码器NSC/MOT/TICD4029 可预置可逆计数器NSC/MOT/TICD4030 四异或门NSC/MOT/TI/GOLCD4031 64位串入/串出移位存储器NSC/MOT/TICD4032 三串行加法器NSC/TICD4033 十进制计数/7段译码器NSC/TICD4034 8位通用总线寄存器NSC/MOT/TICD4035 4位并入/串入-并出/串出移位寄存NSC/MOT/TI CD4038 三串行加法器NSC/TICD4040 12级二进制串行计数/分频器NSC/MOT/TICD4041 四同相/反相缓冲器NSC/MOT/TICD4042 四锁存D型触发器NSC/MOT/TICD4043 4三态R-S锁存触发器("1"触发) NSC/MOT/TI CD4044 四三态R-S锁存触发器("0"触发) NSC/MOT/TICD4046 锁相环NSC/MOT/TI/PHICD4047 无稳态/单稳态多谐振荡器NSC/MOT/TI型号器件名称厂牌备注CD4048 4输入端可扩展多功能门NSC/HIT/TICD4049 六反相缓冲/变换器NSC/HIT/TICD4050 六同相缓冲/变换器NSC/MOT/TICD4051 八选一模拟开关NSC/MOT/TICD4052 双4选1模拟开关NSC/MOT/TICD4053 三组二路模拟开关NSC/MOT/TICD4054 液晶显示驱动器NSC/HIT/TICD4055 BCD-7段译码/液晶驱动器NSC/HIT/TI CD4056 液晶显示驱动器NSC/HIT/TICD4059 “N”分频计数器NSC/TICD4060 14级二进制串行计数/分频器NSC/TI/MOT CD4063 四位数字比较器NSC/HIT/TICD4066 四传输门NSC/TI/MOTCD4067 16选1模拟开关NSC/TICD4068 八输入端与非门/与门NSC/HIT/TICD4069 六反相器NSC/HIT/TICD4070 四异或门NSC/HIT/TICD4071 四2输入端或门NSC/TICD4072 双4输入端或门NSC/TICD4073 三3输入端与门NSC/TICD4075 三3输入端或门NSC/TI型号器件名称厂牌备注CD4076 四D寄存器CD4077 四2输入端异或非门HITCD4078 8输入端或非门/或门CD4081 四2输入端与门NSC/HIT/TICD4082 双4输入端与门NSC/HIT/TICD4085 双2路2输入端与或非门CD4086 四2输入端可扩展与或非门CD4089 二进制比例乘法器CD4093 四2输入端施密特触发器NSC/MOT/ST CD4094 8位移位存储总线寄存器NSC/TI/PHICD4095 3输入端J-K触发器CD4096 3输入端J-K触发器CD4097 双路八选一模拟开关CD4098 双单稳态触发器NSC/MOT/TICD4099 8位可寻址锁存器NSC/MOT/STCD40100 32位左/右移位寄存器CD40101 9位奇偶较验器CD40102 8位可预置同步BCD减法计数器CD40103 8位可预置同步二进制减法计数器CD40104 4位双向移位寄存器CD40105 先入先出FI-FD寄存器型号器件名称厂牌备注CD40106 六施密特触发器NSC\TICD40107 双2输入端与非缓冲/驱动器HAR\TICD40108 4字×4位多通道寄存器CD40109 四低-高电平位移器CD40110 十进制加/减,计数,锁存,译码驱动STCD40147 10-4线编码器NSC\MOTCD40160 可预置BCD加计数器NSC\MOTCD40161 可预置4位二进制加计数器NSC\MOTCD40162 BCD加法计数器NSC\MOTCD40163 4位二进制同步计数器NSC\MOTCD40174 六锁存D型触发器NSC\TI\MOTCD40175 四D型触发器NSC\TI\MOTCD40181 4位算术逻辑单元/函数发生器CD40182 超前位发生器CD40192 可预置BCD加/减计数器(双时钟) NSC\TI CD40193 可预置4位二进制加/减计数器NSC\TICD40194 4位并入/串入-并出/串出移位寄存NSC\MOT CD40195 4位并入/串入-并出/串出移位寄存NSC\MOT CD40208 4×4多端口寄存器型号器件名称厂牌备注CD4501 4输入端双与门及2输入端或非门CD4502 可选通三态输出六反相/缓冲器CD4503 六同相三态缓冲器CD4504 六电压转换器CD4506 双二组2输入可扩展或非门CD4508 双4位锁存D型触发器CD4510 可预置BCD码加/减计数器CD4511 BCD锁存,7段译码,驱动器CD4512 八路数据选择器CD4513 BCD锁存,7段译码,驱动器(消隐) CD4514 4位锁存,4线-16线译码器CD4515 4位锁存,4线-16线译码器CD4516 可预置4位二进制加/减计数器CD4517 双64位静态移位寄存器CD4518 双BCD同步加计数器CD4519 四位与或选择器CD4520 双4位二进制同步加计数器CD4521 24级分频器CD4522 可预置BCD同步1/N计数器CD4526 可预置4位二进制同步1/N计数器CD4527 BCD比例乘法器型号器件名称厂牌备注CD4528 双单稳态触发器CD4529 双四路/单八路模拟开关CD4530 双5输入端优势逻辑门CD4531 12位奇偶校验器CD4532 8位优先编码器CD4536 可编程定时器CD4538 精密双单稳CD4539 双四路数据选择器CD4541 可编程序振荡/计时器CD4543 BCD七段锁存译码,驱动器CD4544 BCD七段锁存译码,驱动器CD4547 BCD七段译码/大电流驱动器CD4549 函数近似寄存器CD4551 四2通道模拟开关CD4553 三位BCD计数器CD4555 双二进制四选一译码器/分离器CD4556 双二进制四选一译码器/分离器CD4558 BCD八段译码器CD4560 "N"BCD加法器CD4561 "9"求补器CD4573 四可编程运算放大器CD4574 四可编程电压比较器CD4575 双可编程运放/比较器CD4583 双施密特触发器CD4584 六施密特触发器CD4585 4位数值比较器CD4599 8位可寻址锁存器CD22100 4×4×1交叉点开关。

采用二输入与非门制作四人表决器

四人表决器的设计一、实验目的1、了解和初步掌握EWB软件的基本操作方法以及练习做板。

2、通过实验,加深电路设计的概念以及了解计算机辅助设计分析的过程。

3、培养学生的创新能力以及理论知识的应用能力。

二、实验器材+5V直流电源,8脚拨码开关2个、100Ω电阻1个、10KΩ电阻4个、1K Ω电阻1个、74LS00 2个、发光二极管1个、万能板1个、导线若干等。

三、实验内容及步骤实验内容:本实验要求利用EWB软件完成对四人表决器的设计及仿真,表决规则是:多数胜少数负。

此次仿真应有四个输入端口,一个输出端口。

分别设置其A,B,C,D 为输入端口,Y为输出端口。

A,B,C,D全为‘1’时则全票通过;A,B,C为‘1’,D为0时Y为‘1’;A,B,D为‘1’,C为‘0’时Y为‘1’;A,C,D为‘1’,B 为‘0’时Y为‘0’;B,C,D为‘1’,A为‘0’时输出Y为‘1’;当A,B,C,D 全为‘1’时,则Y=‘1’。

实验步骤:1、分析可知其真值表如下所示:根据卡诺图可分析:无人中任意三人或者四人通过则表决可以通过,故得到其逻辑表达式为Y=ABCD’+ABC’D+AB’CD+A’ BCD+ ABCD=ABD+ACD+ABC+BCD=((AB+AC)D)+(B(AC+CD))=(((AB)’(AC)’)’D)+(B((AC)’(CD)’)’)=((((AB)’(AC)’)’D)’(B((AC)’(CD)’)’)’)’2、打开EWB软件,新建一个项目。

3、在新建立的项目的基础上新建一个原理图文件。

用软件绘制原理图如下所示:图2:四人表决器原理图用EWB软件进行模拟,使A,B,C,D开关分别按照真值表进行开关,观察发光二极管的发光情况。

模拟成功后再根据实验原理图连接实线,焊接的时候注意不要短路,根据实验要求控制逻辑开关,并记录发光二极管的发光情况,与理论的结果进行比较。

四、实验结果分析1、根据图2进行仿真模拟时发现当分别置A,B,C,D全为接通时则发光二极管处于发光状态;A,B,C接通,D为断开时发光二极管处于发光状态;A,B,D为接通,C为断开时Y为发光状态;A,C,D为接通,B为断开时Y为发光状态;B,C,D为接通,A为断开时输出Y为发光状态;当有2个或2个以上开关打开时,发光二极管熄灭。

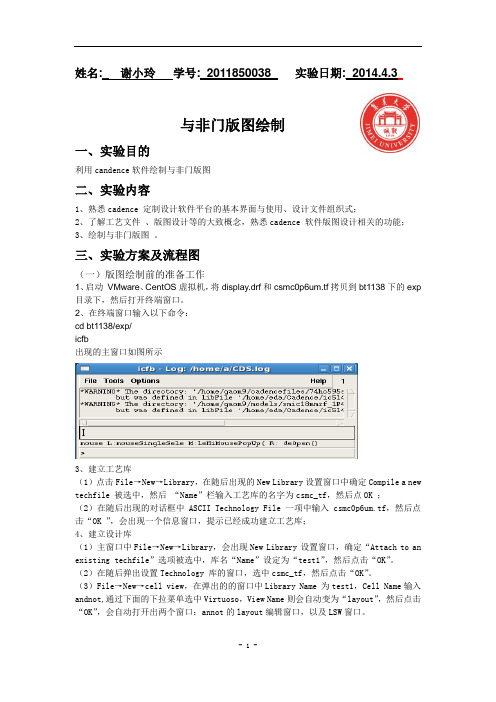

实验二 二输入与非门版图绘制

姓名:_ 谢小玲学号:_2011850038_ 实验日期:_2014.4.3与非门版图绘制一、实验目的利用candence软件绘制与非门版图二、实验内容1、熟悉cadence 定制设计软件平台的基本界面与使用、设计文件组织式;2、了解工艺文件、版图设计等的大致概念,熟悉cadence 软件版图设计相关的功能;3、绘制与非门版图。

三、实验方案及流程图(一)版图绘制前的准备工作1、启动VMware、CentOS虚拟机,将display.drf和csmc0p6um.tf拷贝到bt1138下的exp 目录下,然后打开终端窗口。

2、在终端窗口输入以下命令:cd bt1138/exp/icfb出现的主窗口如图所示3、建立工艺库(1)点击File→New→Library,在随后出现的New Library设置窗口中确定Compile a new techfile 被选中,然后“Name”栏输入工艺库的名字为csmc_tf,然后点OK ;(2)在随后出现的对话框中ASCII Technology File 一项中输入 csmc0p6um.tf,然后点击“OK ”,会出现一个信息窗口,提示已经成功建立工艺库;4、建立设计库(1)主窗口中File→New→Library,会出现New Library 设置窗口,确定“Attach to an existing techfile”选项被选中,库名“Name”设定为“test1”,然后点击“OK”。

(2)在随后弹出设置Technology 库的窗口,选中csmc_tf,然后点击“OK”。

(3)File→New→cell view,在弹出的的窗口中Library Name 为test1,Cell Name输入andnot,通过下面的下拉菜单选中Virtuoso,View Name则会自动变为“layout”,然后点击“OK”,会自动打开出两个窗口:annot的layout编辑窗口,以及LSW窗口。

1.2基本门电路设计-版图绘制

集成电路设计实习Integrated Circuits Design LabsI t t d Ci it D i L b单元实验一(第二次课)基本门电路设计--版图设计2006-2007 Institute of Microelectronics Peking University实验目的及时间安排z内容一:z掌握基本门电路的版图设计z熟悉Cadence版图设计、版图验证工具的使用z内容二:z完成2与非门的设计,包括原理图输入、电路仿真、版图设计、版图验证Institute of Microelectronics, Peking University集成电路设计实习-单元实验一Page21. 版图图层z本课程中使用CSMC双硅三铝混合信号工艺,主要的设计层包括z TB:tub,n阱,作为pmos器件衬底z TO:Thin Oxide,有源区,作为mos的源漏区Thin Oxidez GT:gate,多晶硅1,作为mos栅极z SP:P+注入区z SN:N+注入区z W1:接触孔,金属1到多晶硅和有源区的接触孔z A1:铝1,第一层金属z W2:通孔1,金属1和金属2的接触孔z A2:铝2,第二层金属z W3:通孔2,金属2和金属3的接触孔z CP:bond pad,pad开孔z IM:第二层多晶硅电阻阻挡层z PC:poly Cap,用作多晶硅电容上极板和多晶硅电阻的第二层多晶硅l Cz PT:p tub,p阱,作为nmos器件衬底z详细的工艺信息请参考设计规则(在CSMC05MS/docs目录下)Institute of Microelectronics, Peking University集成电路设计实习-单元实验一Page32. 由电路图产生初始版图z VirtuosoXL为cadence的连接关系驱动定制版图设计工具z启动Virtuoso XLz第一步:打开inv的schematic viewz第二步:Schematic窗口:Tools->Design Synthesis->Layout XLz Create Newz OKz OK,弹出Virtuoso XL窗口Vi t XLz在Virtuoso XL窗口中,Design->GenFrom Source Layout,弹出yGeneration Options对话框(下页)Institute of Microelectronics, Peking University集成电路设计实习-单元实验一Page4z Layout Generation部分z选中I/O Pins,Instances,Transistor Chaining,TransistorTransistor Chaining TransistorFoldingz I/O Pins部分z DefaultsD f lz Layer/Master选择A1层z选中Createz Applyz Pin Label Shapez点击Pin Label Options,在弹出的对话框中选中Layer Name后面的SameLayer Name SameAs Pinz点击OK后出现下页图,按照前面的设计要求进行版图设计Institute of Microelectronics, Peking University集成电路设计实习-单元实验一Page5Inv的版图设计z在此基础上添加电源线vdd,地线gnd(可参考下页快捷键)z按照电路图用相应的层把mos管的各端连线画出来z把vdd和N阱相连(用CSMC05MS库中的ntap),把gnd和衬底相连(用tCSMC05MS库中的ptap )z按照标准单元的画法,单元有统一的高度(这里是24um),统一的vdd和gnd走线宽度(2um)和位置(vdd走线在单元的最上端,gnd在最下端)Institute of Microelectronics, Peking University集成电路设计实习-单元实验一Page6Virtuoso Layout Editor常用操作z Instance(添加元件,快捷键i)g(画矩形,快捷键),yg(画多边形,快捷键z Rectangle r PolygonP),Path(画长连线,快捷键p)pyz Copy(c),Move(m),Stretch(s)z Merge(把多个相互重叠的图形合并成一块,M)Create Ruler Clear All Rulersz Create Ruler(添加标尺,快捷键k),Clear All Rulers(K)z Descend(X),Return(B)z Zoom in by 2(^z),Zoom out by 2(Z),Fit(f)z Option->Display(e)中可以设置一些参数z在命令过程中可以利用F3键打开该命令相关的选项,帮助我们调整命令参数(很有帮助!)Institute of Microelectronics, Peking University集成电路设计实习-单元实验一Page73. 版图的验证DRCz在Layout窗口中,Verify->DRCz在Rules File一项中,填入divaDRC.rul,若该文件不在启动目录下,还应写上路径z取消Rules Library选项Rules Libraryz OKz在CIW中可以看到DRC的结果,按说明改掉图中的error,直到Total errors found为0Institute of Microelectronics, Peking University集成电路设计实习-单元实验一Page84. 版图的器件提取和LVS检查z在做LVS之前,要把版图中的管子信息和pin的信息提取出来,这就是Extractz在Layout窗口中,Verify->Extractz Rules File一项中,填入在Rules FiledivaEXT.rul,若该文件不在启动目录下,还应写上路径z取消Rules Library选项Rules Libraryz OK在中可以看到是否成z CIW Extract功,一般情况下Total errorsfound都为0z执行的结果是cell inv产生了一个extracted viewInstitute of Microelectronics, Peking University集成电路设计实习-单元实验一Page9LVSz在Layout窗口中,Verify->LVSz Library和Cell中分别填入库名字design03和单元名字inv,View中对应于schematic的填入schematic,对应于extracted的填入extracted(这些信息也可以通过Browse或者BSel by Cursor得到)在一项中,填入z Rules FiledivaLVS.rul,若该文件不在启动目录下,还应写上路径z点击Run,运行几秒后会出现“Analysis Job Succeeded”的提示z点击Output,观看结果。

非门,与非门,或非门的电路结构与仿真

实验二非门、与非门、或非门的电路构造与仿真班级xxxx xx 学号xxxxxxxx 指导教师一、实验目的1、掌握根本组合逻辑电路构造及相关特性;2、进一步熟练Hspice等工具;二、实验容及要求1、设计反相器电路;2、设计出2输入与非门、或非门并仿真;实验结果及要求:〔1〕、确定反相器电路每个晶体管尺寸;〔2〕、绘制出反相器电压传输特性;〔3〕、确定与非门、或非门各个管子的尺寸;三、实验原理1.反相器:〔1〕组成:一个增强型NMOS管和一个增强型PMOS管相连接而组成的;下方的NMOS 管的衬底〔P型硅〕都接地,而PMOS管衬底〔N型硅〕都接Vdd,这种对衬底的偏置方式可以防止源,漏区和衬底形成的PN结正偏,防止寄生效应。

〔2〕构造:CMOS反相器中输入端直接连接在NMOS管和PMOS管的栅极上,输入端引入的输入电平会直接影响NMOS管和PMOS管的工作状态。

而NMOS管和PMOS管的漏极那么相互连接起来,构成了输出端,对外提供输出电平〔Vout〕.注意:反相器的输出端并不是孤立的节点,而是连接有负载电容。

( 3 )在CMOS反相器中,NMOS管和PMOS管的栅源电压和漏源电压与输入,输出电平的关系为:V(GSN)= V(in);V(DSN)=V(out)V(GSP)=V(in)-V(DD);V(DSP)=V(out)-V(DD);备注:G为栅极,S为源极,D为漏极。

(5)反相器的工作原理:静态工作的CMOS反相器,当输入为逻辑值“0〞时〔V〔in〕= 0V〕,NMOS管的接地端为源极,NMOS 管上的栅源电压为0V,而PMOS管接V〔DD〕的是源极,PMOS管的栅源电压为-V(DD).这就使得NMOS 管处于截止状态而PMOS管处于导通状态;通过导通的PMOS管,在电源电压V(DD)与输出端连接的负载电容之间建立起了导电通路。

可以将负载电容充电到V〔DD〕,使得输出的逻辑值变为“1〞;当输入为逻辑值“1〞时〔此时的输入电平为V〔DD〕,即V(in)=V(DD)〕,由于PMOS管的栅源电压为0V,而NMOS管的栅源电压为V(DD),使得PMOS管处于截止状态而NMOS管处于导通状态,这样就在负载电容与地电极之间通过NMOS管建立起了导电通路,使得负载电容被放电到0V,这就使输出逻辑值变为“0〞。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

(14) 创建电路包含文件:选取窗口菜单→ ,产生 用来代表目前所设计电路的2文件,供其他编译时使用, 如图5-3所示。

(15) 时间分析:选取窗口菜单→ ,再选取窗口菜 单→ ,可以产来自如图5-4所示的时间分析结果。

NAND2

AA

C

C

B

B

图5-2 2输入端与非门的电路符号

FUNCTION nand2 (a,b) RETURNS (c);

表5-1 2输入端与非门的真值表

输入端

A

B

0

0

0

1

1

0

1

1

输出端 C 1 1 1 0

2.原理图输入 与非门原理图输入法的操作步骤介绍如下。 (1) 建立新文件:选取窗口菜单→,出现对话框, 选择 选项,单击按钮,进入图形编辑画面。 (2) 保存:选取窗口菜单→,出现对话框,键入文 件名2,单击按钮。

基本门电路的设计

基本门电路的设计

基本门电路主要用来实现基本的输入/输出之间的 逻辑关系,包括与门、非门、或门、与非门、或非门、 异或门、同或门等,下面以2输入端与非门为例讲解基 本门电路的设计。

1.实验原理 表5-1 2输入端与非门的真值表 2输入端与非门是组合逻辑电路中的基本逻辑器件, 有2个输入端A、B和1个输出端C。其真值表如表5-1所 示。2输入端与非门应具备的脚位: 输入端:A、B; 输出端:C。

(3) 指定项目名称,要求与文件名相同:选取窗口 菜单→→,键入文件名2,单击按钮。

(4) 确定对象的输入位置:在图形窗口内单击鼠标 左键。

(5) 引入逻辑门:选取窗口菜单→ ,在\2\2\处双击, 在 菜单中选取2逻辑门,单击按钮。

(6) 引入输入和输出脚:按步骤(5)选出2个输入脚 和1个输出脚。

图5-3 2输入端与非门的电路包含文件

A B s o u r c e

Delay Matrix

Destination C

7.5 ns 7.3 ns

图5-4 2输入端与非门的时间分析

3.文本输入 (1) 建立新文件:选取窗口菜单→,出现对话框, 选择 选项,单击按钮,进入文本编辑画面。

(2) 保存:选取窗口菜单→,出现对话框,键入文 件名2,单击按钮。

图5-5 2输入端与非门的波形图

5.硬件仿真 1) 下载实验验证 (1) 选择器件:打开Ⅱ,选取窗口菜单→,出现对 话框,选择1K系列的1K30144-1,如图5-6所示。

图5-6 选择器件

(2) 锁定引脚:选取窗口菜单→,出现对话框, 在 中分别键入引脚名称A、B、C,在中键入引脚编号 68、67、17。引脚68对应1,信号灯为1;引脚67对应2, 信号灯为2;引脚17对应1。锁定引脚的界面如图5-7所 示。

A B

N A N D 2 IN PU T

V CC IN PU T V CC 20

O U TPU T 23

Y

图5-1 2输入端与非门的原理图

(11) 修改错误:针对窗口所提供的信息修改电路设 计,直到没有错误为止。

(12) 保存并编译:选取窗口菜单→→ ,即可进行 编译,产生2烧写文件。

(13) 创建电路符号:选取窗口菜单→ ,可以产生 2文件,代表现在所设计的电路符号。选取→ ,进入 画面,2输入端与非门的电路符号如图5-2所示。

(3) 指定项目名称,要求与文件名相同:选取窗口 菜单→→, 键入文件名2,单击按钮。

(4) 选择实际编程器件型号:选取窗口菜单→,出 现对话框,选择1K系列的1K30144-1。

(5) 输入源程序:

2

(A, B:

;

C:

);

2;

a2

C<= (A B); a;

(6) 保存并查错:选取窗口菜单→→,即可针对电路 文件进行检查。

(3) 设定时钟的周期:选取窗口菜单→ ,出现对 话框,设定 为50 ,单击按钮。

(4) 设定初始值并保存:设定初始值,选取窗口菜 单→,出现对话框,单击按钮。

(5) 仿真:选取窗口菜单Ⅱ→,出现 对话框,单击 按钮,出现对话框,单击“确定”按钮,出现2输入端 与非门的波形图,如图5-5所示。

(6) 观察输入结果的正确性:单击 按钮,可以 在时序图中写字,并验证仿真结果的正确性。

表5-2 与非门的实验结果

LED_KEY2(B) 灭 灭 亮 亮

LED_KEY1(A) 灭 亮 灭 亮

LED1(C) 亮 亮 亮 灭

(7) 修改错误:针对窗口所提供的信息修改电路文 件,直到没有错误为止。

(8) 保存并编译:选取窗口菜单→→,即可进行编 译,产生2烧写文件。

(9) 创建电路符号:选取窗口菜单→ ,可以产生2 文件,代表现在所设计的电路符号。选取→ ,进入 画 面。

(10) 创建电路包含文件:选取窗口菜单→ ,产 生代表现在所设计电路的2 文件,供其他编译时使用。

(11) 时间分析:选取窗口菜单→ ,再选取窗口菜 单→ ,产生时间分析结果。

4.软件仿真 (1) 进入波形编辑窗口:选取窗口菜单Ⅱ→ ,进 入波形编辑窗口。

(2) 引入输入/输出脚:选取窗口菜单→ ,出现对 话框,单击按钮,选择 中的输入与输出,按“=>”键 将A、B、C移至右边,单击按钮进行波形编辑。

(3) 编译:选取窗口菜单→→ ,即可进行编译,编 译完成后的提示信息如图5-8所示。

(4) 烧写:选取窗口菜单→进行烧写,如图5-9所示。

图5-7 锁定引脚

图5-8 编译完成后的提示信息

图5-9 烧写

2) 实验结果 设定输入信号为键按下时输入“1”信号,此时信 号灯亮,否则输入“0”信号,信号灯灭。输出信号为 信号灯亮时为“1”,信号灯灭时为“0”。 按表5-2所示,按下1、2键,观察输出1的结果。

(7) 更改输入和输出脚的脚位名称:在处双击鼠 标左键,进行更名,输入脚为A、B,输出脚为C。

(8) 连接:将A、B脚连接到与非门的输入端,C 脚连接到与非门的输出端,如图5-1所示。

(9) 选择实际编程器件型号:选取窗口菜单→, 出 现对话框,选择1K系列的1K30144-1。

(10) 保存并查错:选取窗口菜单→→,即可针对 电路文件进行检查。