外延及CVD工艺

【2024版】外延工艺培训课件

(3)升温(两步)(4)HCl排空、抛光(5)H2清洗(6)外延生长(7)H2清洗-降低自掺杂效应(8)降温(9)N2清洗

反应物和载气(如H2)一起被引入反应器中,而晶片一般维持在650℃到850℃的范围。必须有足够的砷的过蒸汽压,以防止衬底和生长层的热分解。

3.7.1 外延生长原理1 气相外延外延是指在单晶衬底上生长一层新单晶的技术,新单晶的晶向取决于衬底,由衬底向外外延而成。外延方法很多,硅半导体器件中通常采用硅的气相外延法。其过程是:四氯化硅(SiCl4)或硅烷(SiH4),在加热的硅衬底表面与氢发生反应或自身发生热分解,还原成硅,并以单晶形式沉积在硅衬底表面。

2外延生长设备

外延系统应满足如下要求:(1)气密性好(2)温度均匀且精确可控,能保证衬底均匀地升温与降温;(3)气流均匀分布(4)反应剂与掺杂计的浓度及流量精确可控(5)管道、阀门用不锈钢制造,并保证连接可靠。(6)要使用多个流量计使反应剂与掺杂计的浓度及流量精确可控。(7)石墨基座由高纯墨制成。加热采用射频感应加热方式。

1、Genius only means hard-working all one's life. (Mendeleyer, Russian Chemist) 天才只意味着终身不懈的努力。21.5.265.26.202108:3008:30:57May-2108:302、Our destiny offers not only the cup of despair, but the chalice of opportunity. (Richard Nixon, American President )命运给予我们的不是失望之酒,而是机会之杯。二〇二一年五月二十六日2021年5月26日星期三3、Patience is bitter, but its fruit is sweet. (Jean Jacques Rousseau , French thinker)忍耐是痛苦的,但它的果实是甜蜜的。08:305.26.202108:305.26.202108:3008:30:575.26.202108:305.26.20214、All that you do, do with your might; things done by halves are never done right. ----R.H. Stoddard, American poet做一切事都应尽力而为,半途而废永远不行5.26.20215.26.202108:3008:3008:30:5708:30:575、You have to believe in yourself. That's the secret of success. ----Charles Chaplin人必须相信自己,这是成功的秘诀。-Wednesday, May 26, 2021May 21Wednesday, May 26, 20215/26/2021

外延及CVD工艺教材

三. 外延中的掺杂

掺杂剂 氢化物 : PH3, AsH3,BBr3,B2H6 氯化物: POCl3,AsCl3

2019/4/6 13

在外延层的电阻率还会受到下 列三种因素的干扰

重掺杂衬底重的大量杂质通过热扩散方

式进入外延层,称为杂质外扩散。 衬底中的杂质因挥发等而进入气流,然 后重新返回外延层,称为气相自掺杂。 气源或外延系统中的污染杂质进入外延, 称为系统污染。

2019/4/6 21

3.参数测量

参数内容

外延层厚度

常用测量方法

磨角染色法 层错法 红外椭圆偏振仪法 红外反射干涉法 四探针法 三探针法 C-V 法 扩展电阻法 脉冲 MOS 电容法 C-V 法 扩展电阻法 微分电导和霍尔效应 放射性元素示踪分析 卢瑟福背散射 光学显微镜观测 自动激光扫描仪

电阻率

2019/4/6 3

二.硅气相外延工艺

1. 外延原理

氢还原反应

SiCl4 2H2 Si 4HCl

1000 C

SiCl4 Si(固) 2SiCl2

硅烷热分解

SiH4 Si 2H 2

2019/4/6

600 C

4

2. 生长速率

影响外延生长速率的主要因素:

少子寿命

杂质分布

缺陷密度

2019/4/6

22

五.外延的用途

双极电路:

利用n/n+硅外延,将双极型高频功率晶体

管制作在n型外延层内,n+硅用作机械支 撑层和导电层,降低了集电极的串联电 阻。 采用n/p外延片,通过简单的p型杂质隔离 扩散,便能实现双极集成电路元器件间 的隔离。

SIC外延生长法的工艺流程

SIC外延生长法的工艺流程SIC外延生长法的工艺流程序号:1SIC外延生长法是一种重要的半导体材料生长技术,被广泛应用于功率电子、射频器件和光电子器件等领域。

它通过在SIC衬底上连续沉积SiC晶体层,实现了对SiC材料的高质量控制和大面积生长。

在本文中,我们将深入探讨SIC外延生长法的工艺流程,以帮助读者更好地理解和学习该技术。

序号:2SIC外延生长法的基本原理是在惰性气体气氛中,通过化学气相沉积(CVD)的方法,将硅和碳源气体分解成SiC气体,然后在SIC衬底上沉积成SIC晶体层。

在整个工艺过程中,需要控制好气氛、温度和气体流量等参数,以保证SIC晶体层的质量和厚度的一致性。

序号:3具体而言,SIC外延生长法的工艺流程可以分为以下几个关键步骤:a. 衬底准备:选择合适的SIC衬底,并进行表面处理,以去除杂质和缺陷。

通常使用化学气相沉积(CVD)或物理气相沉积(PVD)等方法来制备合适的SIC衬底。

b. 热解预处理:将SIC衬底放置在高温炉中,通过热解预处理,去除表面的氧化物和其它杂质。

这一步骤也有助于提高SIC晶体层的生长质量。

c. 生长条件控制:在热解预处理后,将SIC衬底放置在CVD反应室中。

控制好反应温度、压力和气体流量等参数,以实现SiC晶体层的均匀和连续生长。

通常,选择适当的碳源和硅源气体,如甲烷(CH4)和四氯化硅(SiCl4),作为SIC生长的原料气体。

d. 控制生长时间:根据所需的SIC晶体层厚度和生长速率,控制生长时间。

通过调整反应室中的反应气体流量和温度,可以有效控制SIC晶体层的生长速率。

e. 冷却和退火:在SIC晶体层生长完成后,将SIC衬底从反应室中取出,并进行冷却和退火处理。

这一步骤有助于提高晶体层的结晶质量、降低残余应力,并改善界面的质量。

序号:4总结回顾:SIC外延生长法是一种关键的半导体材料生长技术,其工艺流程包括衬底准备、热解预处理、生长条件控制、控制生长时间以及冷却和退火等关键步骤。

分子束外延和cvd

分子束外延和cvd

分子束外延(MBE)和化学气相沉积(CVD)都是用于生长薄膜

和纳米结构的技术,它们在材料科学和纳米技术领域具有重要意义。

首先,让我们来看看分子束外延(MBE)。

MBE是一种通过逐层

沉积原子或分子来生长薄膜的技术。

在MBE中,固体源中的原子或

分子被加热,产生蒸汽或分子束,然后通过真空腔室中的激光或热

电子束来定向沉积在衬底表面上。

这种技术可以精确地控制沉积速

率和成分,因此适用于制备复杂的多层结构和纳米器件。

MBE通常

用于生长III-V族化合物半导体材料,如氮化镓、砷化镓等,以及

其他复杂的材料体系。

其次,让我们来看看化学气相沉积(CVD)。

CVD是一种利用气

态前体分子在表面化学反应生成固体薄膜的技术。

在CVD过程中,

气态前体分子通过化学反应在衬底表面上沉积形成固体薄膜。

CVD

技术可以通过控制气相前体的浓度、温度和压力来调控沉积速率和

薄膜成分,因此在生长大面积均匀薄膜方面具有优势。

CVD广泛应

用于生长金属薄膜、氧化物薄膜、碳纳米管和石墨烯等材料。

从使用角度来看,MBE通常用于研究实验室和半导体器件制备,

因为它能够精确地控制材料的结构和成分,适用于制备高质量的纳米结构和器件。

而CVD则更适用于工业生产,因为它可以在较大的衬底上实现均匀的薄膜生长,且设备成本相对较低。

总的来说,MBE和CVD都是重要的薄膜生长技术,它们各自具有特定的优势和适用范围,对于材料科学和纳米技术的发展都具有重要意义。

以单晶硅为例,简述如何通过CVD技术实现半导体材料的外延生长

通过CVD技术实现半导体材料外延生长一.气相外延的作用(1).提高硅材料的完美性(2).提高集成度(3).提高少子的寿命,减少储存单元的漏电流(4)提高电路的速度(5)改变电路的功率特性以及频率特性(6)解决CMOS电路的锁定(7)实现各种材质的多种薄膜外延二、单晶硅的气相外延生长方法,属于半导体制造领域,包括以下步骤:a、提供可供预处理的基底;b、清洗;c、提供可供单晶硅外延生长的腔体,腔体内设有基底储放装置,并将基底放置于基底储放装置上;d、向腔体内通入还原性气体,并将腔体内压强和温度调至所需压强和温度;e、向腔体内通入气态硅源,在基底表面生成预设厚度的牺牲层;f、在牺牲层上方形成单晶硅层;g、将单晶硅层和牺牲层的连接体与基底分离。

化学气相沉积(CVD)是半导体工业中应用最为广泛的用来沉积多种材料的技术,包括大范围的绝缘材料,大多数金属材料和金属合金材料。

从理论上来说,它是很简单的:两种或两种以上的气态原材料导入到一个反应室内,然后他们相互之间发生化学反应,形成一种新的材料,沉积到晶片表面上。

淀积氮化硅膜(Si3N4)就是一个很好的例子,它是由硅烷和氮反应形成的。

然而,实际上,反应室中的反应是很复杂的,有很多必须考虑的因素,沉积参数的变化范围是很宽的:反应室内的压力、晶片的温度、气体的流动速率、气体通过晶片的路程(如图所示)、气体的化学成份、一种气体相对于另一种气体的比率、反应的中间产品起的作用、以及是否需要其它反应室外的外部能量来源加速或诱发想得到的反应等。

额外能量来源诸如等离子体能量,当然会产生一整套新变数,如离子与中性气流的比率,离子能和晶片上的射频偏压等。

然后,考虑沉积薄膜中的变数:如在整个晶片内厚度的均匀性和在图形上的覆盖特性(后者指跨图形台阶的覆盖),薄膜的化学配比(化学成份和分布状态),结晶晶向和缺陷密度等。

当然,沉积速率也是一个重要的因素,因为它决定着反应室的产出量,高的沉积速率常常要和薄膜的高质量折中考虑。

碳化硅外延cvd法-概述说明以及解释

碳化硅外延cvd法-概述说明以及解释1.引言1.1 概述概述碳化硅外延化学气相沉积法(Chemical Vapor Deposition,CVD)是一种常用的制备高质量碳化硅薄膜的技术。

该方法通过在高温下将气态前驱体降解分解,使其原子重新组合并在基底表面形成固态薄膜。

碳化硅具有优异的热导性、尺寸稳定性和化学稳定性,在高温、高功率及特殊工况下具有广泛的应用前景。

本文将介绍碳化硅外延CVD法的原理、工艺和应用。

首先,将对CVD 法的基本原理进行阐述,包括分解反应机理、气相热化学反应和沉积动力学等方面。

其次,会详细介绍碳化硅外延CVD法在制备晶态碳化硅薄膜方面的应用,包括各种衬底材料的使用、反应温度和气氛的选择,以及前驱体选择等方面的优化。

最后,我们将对碳化硅外延CVD法的优势进行总结,并展望其在未来的发展前景。

通过本文的阐述,读者可以全面了解碳化硅外延CVD法的研究现状和应用前景,以及该技术在能源、光电子、半导体和化学等领域的潜在应用价值。

同时,本文还将提供一些可供参考的研究方向和问题,以促进碳化硅外延CVD法的进一步发展和应用。

1.2文章结构1.2 文章结构本文主要介绍了碳化硅外延CVD法的技术和应用。

具体内容包括以下几个方面:第二部分将详细介绍碳化硅外延技术。

首先会对碳化硅外延的基本概念进行解释,并介绍其在半导体工业中的重要性。

然后会介绍CVD法在碳化硅外延中的应用,包括其原理、工艺流程和实验设备等。

第三部分将对碳化硅外延CVD法的优势进行总结。

这一部分将重点探讨CVD法在碳化硅外延制备中的优点,如高晶体质量、可控性和制备效率等。

最后,第四部分将展望碳化硅外延CVD法在未来的发展前景。

这一部分将分析当前碳化硅外延CVD法存在的挑战和问题,并提出改进和发展思路,以期实现碳化硅外延技术的进一步发展和应用。

通过对碳化硅外延CVD法的全面介绍和分析,本文旨在为读者提供全面了解碳化硅外延CVD法的基础知识,以及认识和认识碳化硅外延技术在半导体工业中的应用前景。

化学气相沉积法CVD

外延工艺的主要分类

气相外延工艺(Vapor-Phase Epitaxy,VPE)

液相外延工艺(LPE)

CVD

其他:RTCVD、UHVCVD

在层状-岛状生长模式中,在最开始一两个原子层厚度的层 状生长之后,生长模式转化为岛状模式。导致这种模式转变的物 理机制比较复杂,原因是由于薄膜生长过程中各种能量的相互消 长。

导致生长模式转变的物理机制

1、虽然开始时的生长是外延式的层状生长,但是由于薄膜与衬底之 间晶格常数不匹配,因而随着沉积原子层的增加,应变能(应力) 逐渐增加。为了松弛这部分能量,薄膜在生长到一定厚度之后, 生长模式转化为岛状模式。

MOCVD设备

MOCVD 系统

气体处理 系统

反应腔

计算机控制

真空及排气 系统

气体处理系统

气体处理系统的功能是混合与测量进入反应室的 气体。调节进入反应室气体的速率与成分将决定 外延层的结构。

气路的密封性至关重要。 阀门的快速转换对薄膜和突变界面结构的生长很

重要。 流速,压强和温度的精确控制能保证生长薄膜的

(e)生成物与反应物进入主气流里,并离开系统

输送现象

以化学工程的角度来看,任何流体的传递或输送现象,都会涉及 到热能的传递(传导、辐射、对流)、动量的传递及质量的传递 等三大传递现象。

(1)热量传递-热传导

热传导是固体中热传递的主要方式

(1)热量传递-热辐射

物体因自身温度而具有向外发射能量的本领,这种热传递的方式叫 做热辐射。热辐射能不依靠媒介把热量直接从一个系统传到另一个 系统。

分子束外延和cvd

分子束外延和cvd分子束外延(MBE)和化学气相沉积(CVD)是两种常用的制备薄膜材料的方法。

它们在材料科学和工程领域有着广泛的应用。

本文将从人类的视角出发,介绍这两种方法的原理和特点。

一、分子束外延(MBE)分子束外延是一种基于物理气相沉积的方法,通过在真空环境下将原子或分子束束缚在一束高能束流中,使其沉积在衬底表面。

这种方法可以在原子级别上控制材料的生长,因此薄膜的质量和结晶性能很高。

分子束外延通常使用高真空系统来实现,其中包括真空室、热蒸发源、衬底和探测器等组件。

在生长过程中,原子或分子束从热蒸发源中蒸发出来,经过激励和聚焦后,沉积在衬底表面上。

通过控制衬底的温度和束流的能量,可以调节薄膜的生长速率和结晶度。

分子束外延具有很高的生长速率和优秀的晶体质量,尤其适用于生长半导体材料和量子结构。

它可以精确控制材料的厚度和成分,并能够在不同的衬底上生长多层结构。

这使得它在微电子器件、光电子器件和纳米器件等领域有着广泛的应用。

二、化学气相沉积(CVD)化学气相沉积是一种在气相中通过化学反应生成材料的方法。

它利用气态前驱体在表面上发生化学反应,形成固态薄膜。

CVD可以分为热CVD和低温CVD两种方式。

热CVD是通过在高温下使气态前驱体分解并沉积在衬底表面上。

这种方法适用于生长高质量的单晶薄膜,但需要高温条件和较长的生长时间。

低温CVD是在较低温度下实现材料的生长,通常在300-900摄氏度之间。

它可以通过增加反应气体的活性来降低生长温度,从而适用于热敏性衬底和复杂结构的生长。

化学气相沉积具有生长速度快、成本低廉和生长均匀性好的特点。

它可以生长多种材料,如金属、半导体和氧化物等。

因此,在光电子、能源和化学传感器等领域有着广泛的应用。

总结:分子束外延和化学气相沉积是两种常用的制备薄膜材料的方法。

它们在材料科学和工程中发挥着重要的作用。

分子束外延通过物理气相沉积的方式实现高质量薄膜的生长,而化学气相沉积则通过化学反应在气相中生成材料。

CVD的原理与工艺

CVD的原理与工艺CVD是化学气相沉积的缩写,是一种重要的薄膜制备工艺。

其原理是通过化学反应在基板表面沉积出所需的薄膜。

CVD工艺具有高温、通用性、高产率等优点,被广泛应用于半导体、光电子、材料科学等领域。

CVD工艺的原理主要涉及三个基本过程:传输过程、反应过程和沉积过程。

传输过程是指气相中物质在反应室中的输送和混合过程。

反应过程是指气相中物质发生化学反应的过程。

沉积过程是指反应生成物在基板表面的吸附和成膜过程。

CVD工艺的实施基础是高温条件下反应气体中的化学反应。

通常,CVD工艺需要在几百摄氏度到几千摄氏度的高温下进行。

高温条件下,反应气体中的分子活性增加,促使反应发生。

此外,高温条件下也有利于沉积物的生长和晶格匹配。

CVD工艺中常用的气体有两种类型:反应物气体和载体气体。

反应物气体是指与基板表面发生化学反应的气体,可以是纯净气体或有机金属(如金属有机化合物)。

载体气体是指将反应物气体输送到反应室中,并稀释以便控制反应速率和成膜均匀性的气体。

常用的载体气体有氢气、氮气、氩气等。

具体而言,CVD工艺的实施过程可以分为以下几个步骤:1.反应物气体输送:反应物气体通常通过质量流控制器控制流量,并由气体输送系统输送到反应室中。

2.传输与混合:反应物气体进入反应室后,通过传输与混合过程,与载体气体充分混合,形成气相反应体系。

3.化学反应:在高温条件下,混合的反应气体在反应器中发生化学反应。

这些化学反应通常是复杂的多步骤反应,生成物在气相中。

4.吸附与扩散:生成物与基板表面发生吸附和扩散,使得沉积物开始形成。

5.成膜和生长:沉积物在基板表面不断生长,并形成所需的薄膜。

CVD工艺的成功实施需要考虑许多因素。

其中,关键的因素包括:反应温度、反应气体浓度、反应压力、基板表面状态等。

这些因素直接影响了沉积物的结构、性能和均匀性。

为了实现理想的薄膜沉积,CVD工艺还需要进行流程优化和参数调控。

通过控制反应条件、改变反应气体浓度和流量,以及调整基板表面状态,可以实现不同结构和性能的沉积物。

分子束外延和cvd

分子束外延和cvd分子束外延和化学气相沉积(CVD)是两种常用的薄膜生长技术,它们在材料科学和工程领域有着广泛的应用。

本文将从人类的视角出发,详细介绍这两种技术的原理、应用和优缺点,以及它们对人类社会的贡献和影响。

一、分子束外延(MBE)分子束外延是一种通过在真空中控制分子束来生长薄膜的技术。

在MBE过程中,采用气体源将原子或分子转化为分子束,然后将其瞄准到待生长表面上。

通过控制分子束的能量和角度,可以实现对薄膜生长的精确控制。

MBE技术在半导体器件、光电子器件和纳米材料等领域有着重要的应用。

MBE技术的优点在于其生长速率较慢,能够实现高质量的薄膜生长。

由于在真空环境下进行,可以避免氧化和杂质的污染,从而得到更纯净的材料。

此外,MBE技术可以实现单层薄膜的生长和原子级别的控制,有利于制备纳米器件和量子结构。

然而,MBE技术也存在一些限制。

首先,由于薄膜生长速率较慢,生产效率较低,不适合大规模工业生产。

其次,MBE设备复杂,操作难度较大,需要高度专业化的技术人员进行操作和维护。

此外,MBE技术对材料的选择性较强,只能用于某些特定的材料。

二、化学气相沉积(CVD)化学气相沉积是一种通过化学反应在固体表面上生长薄膜的技术。

在CVD过程中,将气体源中的反应物输送到待生长表面上,通过化学反应生成固态产物。

CVD技术具有生长速度快、适用范围广的特点,广泛应用于半导体、涂层和薄膜材料等领域。

CVD技术的优点在于其生长速度快,适用于大面积薄膜的生长。

同时,CVD技术可以实现复杂结构的薄膜生长,如多层薄膜、异质结构等。

此外,CVD技术的设备相对简单,操作和维护较为方便。

然而,CVD技术也存在一些问题。

首先,由于化学反应涉及到多种气体和反应物,需要严格控制反应条件,如温度、压力和气体流量等,以保证薄膜的质量和均匀性。

其次,CVD过程中会产生大量的废气和有害物质,需要进行处理和排放,对环境造成一定的影响。

总的来说,分子束外延和化学气相沉积是两种重要的薄膜生长技术,它们在材料科学和工程领域有着广泛的应用。

《外延及CVD工艺》课件

01

外延及CVD工艺 在LED中的应用

外延及CVD工艺在GaN基LED中的应用

总结词

广泛使用、技术成熟

详细描述

GaN基LED是当前应用最广泛的LED类型之一,外延及CVD工艺在GaN基LED中 得到了广泛的应用。通过精确控制外延层的生长条件,可以获得高质量的GaN基 材料,进而提高LED的光效和可靠性。

总结词

高温工作、高频率

详细描述

SiC基LED具有高温工作、高频率等优点,被应用于高温、高频和高功率电子器件领域。外延及CVD工艺在SiC基 LED中同样占据重要地位,通过优化生长条件可以获得高质量的SiC材料,提高LED的稳定性和可靠性。

01

外延及CVD工艺 的发展前景与挑战

外延及CVD工艺的发展前景

光学镀膜

用于制造光学镜头、眼 镜片、太阳能集热管等

。

陶瓷材料

用于制造陶瓷轴承、密 封件、热敏电阻等。

金属表面处理

用于提高金属表面的耐 磨性、耐腐蚀性和抗疲

劳性能等。

01

外延及CVD工艺 在太阳能电池中的

应用

外延及CVD工艺在硅基太阳能电池中的应用

总结词

硅基太阳能电池是当前光伏市场的主流产品,外延及CVD工艺在硅基太阳能电池制造中起到关键作用 。

详细描述

外延及CVD工艺在硅基太阳能电池制造中主要用于形成高质量的硅薄膜,控制薄膜的晶体结构和缺陷 密度,提高电池的光电转换效率。通过精确控制反应气体流量、温度、压力等参数,可以获得具有优 良性能的硅薄膜,进一步优化太阳能电池的性能。

外延及CVD工艺在薄膜太阳能电池中的应用

总结词

薄膜太阳能电池是下一代太阳能电池的 重要发展方向,外延及CVD工艺在薄膜 太阳能电池制备中具有广阔的应用前景 。

外延

选择性生长的用途之一是在 SiO2 层上开的接触孔内填硅, 以降低接触孔的深宽比,使接触孔平坦化。

6 卤化物输运 GaAs 气相外延

当采用气相外延生长 GaAs 薄膜时,可以用气态的 AsH3 作 为砷源。但镓不能形成稳定的氢化物。可让经氢气稀释的 HCl 气体流过加热的固态镓,生成气态的 GaCl 作为镓源。这就是 卤化物输运 GaAs 气相外延。也可以让氢气流过加热的固态砷, 生成气态的 AsH3 作为砷源。

液态源可放在起泡器中,让携带气体鼓泡带走。各种液态 源的蒸汽压差别很大,为获得适当的蒸汽压,有的需要加热, 有的则需要冷却。

GaAs 的 MOCVD 通常在中温区进行,生长速率取决于反 应气体的输运,对气流的要求非常高,必须是严格的层流,而 不能有任何湍流或环流。早期的 MOCVD 系统是常压的,现在 大多是低压的。

CS 2

1

erf

2

x DSt

当在本征衬底上生长掺杂浓度为 CE 的外延层时,外延层

的杂质浓度分布为

CE (x)

CE 2

1 erf

2

x DEt

当衬底和外延层都掺杂时,外延层的杂质erf

2

x DSt

CE 2

1

erf

2

x DEt

上式中,“+” 号对应于衬底和外延层的掺杂类型相同时; “-” 号对应于衬底和外延层的掺杂类型相反时。

硅的气相外延多利用硅氯化物 SiHxCl4-x ( x = 0、1、2、3 ) 与 H2 的反应来淀积单晶硅。反应气体分子中氯原子数越少, 所需的化学反应激活能就越小,反应温度就越低。最早使用的 是 SiCl4 ,激活能为 1.6 ~1.7 eV,反应温度在 1150oC 以上。现 在普遍使用的是 SiH2Cl2 ,激活能为 0.3 ~ 0.6 eV。

外延及CVD工艺

2010-10-1

28

工艺多样化: 工艺多样化:

具有相反导电类型的外延层,在器件工 艺中可形成结和隔离区; 薄层外延供器件发展等平面隔离和高速 电路; 选择外延可取代等平面隔离工艺来发展 平面隔离; 绝缘衬底上的多层外延工艺可以发展三 维空间电路

2010-10-1 29

2010-10-1 12

三. 外延中的掺杂

掺杂剂 氢化物: PH3, AsH3,BBr3,B2H6 氯化物: POCl3,AsCl3

2010-10-1 13

在外延层的电阻率还会受到下 列三种因素的干扰

重掺杂衬底重的大量杂质通过热扩散方 式进入外延层,称为杂质外扩散。 衬底中的杂质因挥发等而进入气流,然 后重新返回外延层,称为气相自掺杂。 气源或外延系统中的污染杂质进入外延, 称为系统污染。

2010-10-1

25

软误差

从封装材料中辐射出的α粒子进入衬 底产生大量(约106量级)电子-空穴对, 在低掺杂MOS衬底中,电子-空穴对 可以扩散50μm,易受电场作用进入 有源区,引起器件误动作,这就是 软误差。 采用低阻衬底上外延高阻层的外延片, 则电子-空穴对先进入衬底低阻层,其扩 散长度仅1μm,易被复合,它使软误差 率减少到原来的1/10。

2010-10-1 3

二.硅气相外延工艺 外延工艺

1. 外延原理

氢还原反应

SiCl

SiCl 4 + 2 H 2 ← → Si + 4 HCl

4

>1000ο C

↓

↑

+ Si ( 固 ) ← → 2 SiCl

> 600 ο C ↓ ↑

2

硅烷热分解

SiH

2010-10-1

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

电阻率

少子寿命

杂质分布

缺陷密度

2010-10-1

22

五.外延的用途 .

双极电路: 双极电路: 利用n/n+硅外延,将双极型高频功率晶体 管制作在n型外延层内,n+硅用作机械支 撑层和导电层,降低了集电极的串联电 阻。 采用n/p外延片,通过简单的p型杂质隔离 扩散,便能实现双极集成电路元器件间 的隔离。

2010-10-1

16

2010-10-1

17

2010-10-1

18

2010-10-1

19

2.埋层图形的漂移与畸变 埋层图形的漂移与畸变2. 埋层图形的漂移与畸变

2010-10-1

20

漂移规律

{111}面上严重,偏离2~4度,漂移显著减小, 常用偏离3度. 外延层越厚,偏移越大 , 温度越高,偏移越小 生长速率越小,偏移越小 SiCl4 SiH2Cl2 SiH4 硅生长---腐蚀速率的各向异型是发生漂移 的根本原因.

2010-10-1

25

软误差

从封装材料中辐射出的α粒子进入衬 底产生大量(约106量级)电子-空穴对, 在低掺杂MOS衬底中,电子-空穴对 可以扩散50μm,易受电场作用进入 有源区,引起器件误动作,这就是 软误差。 采用低阻衬底上外延高阻层的外延片, 则电子-空穴对先进入衬底低阻层,其扩 散长度仅1μm,易被复合,它使软误差 率减少到原来的1/10。

等气压线

2010-10-1

8

3.系统与工艺流程 3.系统与工艺流程

系统示意图

2010-10-1

9

工艺流程

. 基座的 HCl 腐蚀去硅程序 ( 去除前次外 延后基座上的硅) N2预冲洗 260L/min 4min H2预冲洗 260L/min 5min 升温1 850C 5min 升温2 1170C 5min HCl排空 1.3L/min 1min

2010-10-1 10

HCl腐蚀 H2冲洗 降温 N2冲洗

10L/min 10min 260L/min 1min 6min

2010-10-1

11

外延生长程序

(1)N2 预冲洗 260L/min 4min 260L/min 5min (2)H2 预冲洗 (3)升温 1 850C 5min (4)升温 2 1170C 6min (5)HCl 排空 1.3L/min 1min (6)HCl 抛光 1.3L/min 3min (7)H2 冲洗(附面层) 260L/min 1min (8)外延生长: H2: 260L/min SiCl4: 6.4~7g/min PH3: 100PPM; 0.15~0.18L/min T: 1160~1190C; 时间随品种而定 1170C 1min (9)H2 冲洗 (10)降温 6min (11)N2 冲洗 4min

4

2. 生长速率

影响外延生长速率的主要因素: 影响外延生长速率的主要因素

反应剂浓度

2010-10-1

5

温度:B区高温区(常选用),A区低温区

2010-10-1

6

气体流速 :气体流速大生长加快

2010-10-1

7

生长速率还与反应腔横截面形状和衬底 取向有关

矩形腔的均匀性较圆形腔好。晶面间的共 价键数目越多,生长速率越慢。

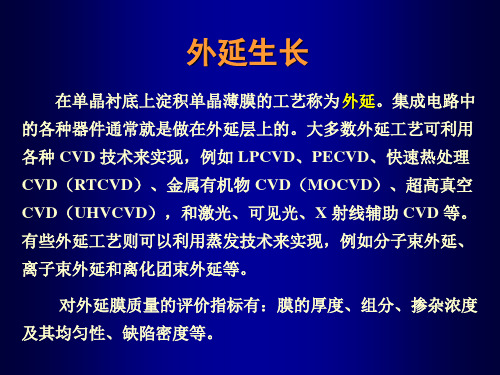

第二章 外延及CVD工艺 外延及CVD工艺 CVD

§1 外延工艺

一.外延工艺概述

定义:外延(epitaxy)是在单晶衬底上生长

一层单晶膜的技术。新生单晶层按衬底 晶相延伸生长,并称此为外延层。长了 外延层的衬底称为外延片。

2010-10-1 1

CVD:Chemical Vapor Deposition

2010-10-1 23

外延层和衬底中不同类型的掺杂形成的 p--n结,它不是通过杂质补偿作用形成的, 其杂质分布可接近理想的突变结。

2010-10-1

24

外延改善NMOS存储器电路特性

(1)提高器件的抗软误差能力 (2)采用低阻上外延高阻层,可降低源、 漏n+ 区耗尽层寄生电容,并提高器件对 衬底中杂散电荷噪声的抗扰度 (3)硅外延片可提供比体硅高的载流子寿 命,使半导体存储器的电荷保持性能提 高。

2010-10-1

28

工艺多样化: 工艺多样化:

具有相反导电类型的外延层,在器件工 艺中可形成结和隔离区; 薄层外延供器件发展等平面隔离和高速 电路; 选择外延可取代等平面隔离工艺来发展 平面隔离; 绝缘衬底上的多层外延工艺可以发展三 维空间电路

2010-10-1 29

2010-10-1 3

二.硅气相外延工艺 外延工艺

1. 外延原理

氢还原反应

SiCl

SiCl 4 + 2 H 2 ← → Si + 4 HCl

4

>1000ο C

↓

↑

+ Si ( 固 ) ← → 2 SiCl

> 600 ο C ↓ ↑

2

硅烷热分解

SiH

2010-10-1

4

→ Si + 2 H 2

2010-10-1

14

同型杂质

异型杂质

2010-10-1

15

四. 外延层中的缺陷与检测

1. 缺陷种类 缺陷种类:

a.存在与衬底中并连续延伸到外延层中的位错 b .衬底表面的析出杂质或残留的氧化物,吸附 的碳氧化物导致的层错; c . 外延工艺引起的外延层中析出杂质; d .与工艺或与表面加工(抛光面划痕、损伤), 碳沾污等有关,形成的表面锥体缺陷(如角锥 体、圆锥体、三棱锥体、小丘); e . 衬底堆垛层错的延伸;

2010-10-1 26

CMOS电路采用外延片可使

电路的寄生闸流管效应有数 量级的改善。 量级的改善。

Latch-up

2010-10-1

27

器件微型化: 器件微型化:

提高器件的性能和集成度要求按比例 缩小器件的横向和纵向尺寸。其中,外 延层厚和掺杂浓度的控制是纵向微细加 工的重要组成部分;薄层外延能使p-n结 隔离或氧化物隔离的横向扩展尺寸大为 减小。

晶体结构良好 掺入的杂质浓度易控制 可形成接近突变p—n结 p—n

外延分类: 外延分类 气相外延(VPE)--常用

. .

2010-10-1

液相外延(LPE)--ⅢⅤ ⅢⅤ 固相外延(SPE)--熔融在结晶 分子束外延(MBE)--超薄 化学气相淀积(CVD)----低温,非晶 2

材料异同

同质结 Si-Si 异质结GaAs--AlxGa(1-x) As 温度:高温1000℃以上 低温1000℃以下 CVD(低温)

2010-10-1 21

3.参数测量 参数测量

参数内容

外延层厚度

常用测量方法

磨角染色法 层错法 红外椭圆偏振仪法 红外反射干涉法 四探针法 三探针法 C-V 法 扩展电阻法 脉冲 MOS 电容法 C-V 法 扩展电阻法 微分电导和霍尔效应 放射性元素示踪分析 卢瑟福背散射 光学显微镜观测 自动激光扫描仪

2010-10-1 12

三. 外延中的掺杂

掺杂剂 氢化物: PH3, AsH3,BBr3,B2H6 氯化物: POCl3,AsCl3

2010-10-1 13

在外延层的电阻率还会受到下 列三种因素的干扰

重掺杂衬底重的大量杂质通过热扩散方 式进入外延层,称为杂质外扩散。 衬底中的杂质因挥发等而进入气流,然 后重新返回外延层,称为气相自掺杂。 气源或外延系统中的污染杂质进入外延, 称为系统污染。