七段数码显示译码器设计

EDA实验报告

EDA实验报告班级:姓名:目录实验一:七段数码显示译码器设计 (1)摘要 (1)实验原理 (1)实验方案及仿真 (1)引脚下载 (2)实验结果与分析 (3)附录 (3)实验二:序列检测器设计 (6)摘要 (6)实验原理 (6)实现方案及仿真 (6)引脚下载 (7)实验结果与分析 (8)实验三:数控分频器的设计 (11)摘要 (11)实验原理 (11)方案的实现与仿真 (11)引脚下载 (12)实验结果及总结 (12)附录 (12)实验四:正弦信号发生器 (14)摘要 (14)实验原理 (14)实现方案与仿真 (14)嵌入式逻辑分析及管脚下载 (16)实验结果与分析 (17)附录 (18)实验一:七段数码显示译码器设计摘要:七段译码器是一种简单的组合电路,利用QuartusII的VHDL语言十分方便的设计出七段数码显示译码器。

将其生成原理图,再与四位二进制计数器组合而成的一个用数码管显示的十六位计数器。

整个设计过程完整的学习了QuartusII的整个设计流程。

实验原理:七段数码是纯组合电路,通常的小规模专用IC,如74或4000系列的器件只能作十进制BCD码译码,然而数字系统中的数据处理和运算都是2进制的,所以输出表达都是16进制的,为了满足16进制数的译码显示,最方便的方法就是利用译码程序在FPGA\CPLD中来实现。

本实验作为7段译码器,输出信号LED7S的7位分别是g、f、e、d、c、b、a,高位在左,低位在右。

例如当LED7S 输出为“1101101”时,数码管的7个段g、f、e、d、c、b、a分别为1、1、0、1、1、1、0、1。

接有高电平段发亮,于是数码管显示“5”。

实验方案及仿真:I、七段数码显示管的设计实现利用VHDL描述语言进行FPGA上的编译实现七段数码显示译码器的设计。

运行QuartusII在G:\QuartusII\LED7S\下新建一个工程文件。

新建一个vhdl语言编译文件,编写七段数码显示管的程序见附录1-1。

十六进制7段数码显示译码器设计实验报告

实验名称:十六进制7段数码显示译码器设计实验目的:1.设计七段显示译码器2.学习Verilog HDL文本文件进行逻辑设计输入;3.学习设计仿真工具的使用方法;工作原理:7段数码是纯组合电路,通常的小规模专用IC,如74或4000系列的器件只能作十进制BCD码译码,然而数字系统中的数据处理和运算都是二进制的,所以输出表达都是十六进制的,为了满足十六进制数的译码显示,最方便的方法就是利用译码程序在FPGA/CPLD中来实现。

例如6-18作为7段译码器,输出信号LED7S 的7位分别接图6-17数码管的7个段,高位在左,低位在右。

例如当LED7S输出为“1101101”时,数码管的7个段g,f,e,d,c,b,a分别接1,1,0,1,1,0,1;接有高电平的段发亮,于是数码管显示“5”。

注意,这里没有考虑表示小数点的发光管,如果要考虑,需要增加段h,例6-18中的LED7S:OUT STD_LOGIC_VECTOR(6 DOWNTO 0)应改为…(7 DOWNTO 0)。

实验内容1:将设计好的VHDL译码器程序在Quartus II上进行编辑、编译、综合、适配、仿真,给出其所有信号的时序仿真波形。

实验步骤:步骤1:新建一个文件夹击打开vhdl文件;步骤2:编写源程序并保存步骤3:新建一个工程及进行工程设置步骤4:调试程序至无误;步骤5:接着新建一个VECTOR WAVEFOM文件及展出仿真波形设置步骤6:输入数据并输出结果(时序仿真图)步骤7:设置好这个模式步骤8:生成RTL原理图步骤9:引脚锁定及源代码LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY DECL7S ISPORT(A :IN STD_LOGIC_VECTOR(3 DOWNTO 0);LED7S:OUT STD_LOGIC_VECTOR(6 DOWNTO 0)); END;ARCHITECTURE one OF DECL7S ISBEGINPROCESS(A)BEGINCASE A ISWHEN"0000"=> LED7S<="0111111";WHEN"0001"=> LED7S<="0000110";WHEN"0010"=> LED7S<="1011011";WHEN"0011"=> LED7S<="1001111";WHEN"0100"=> LED7S<="1100110";WHEN"0101"=> LED7S<="1101101";WHEN"0110"=> LED7S<="1111101";WHEN"0111"=> LED7S<="0000111";WHEN"1000"=> LED7S<="1111111";WHEN"1001"=> LED7S<="1101111";WHEN"1010"=> LED7S<="1110111";WHEN"1011"=> LED7S<="1111100";WHEN"1100"=> LED7S<="0111001";WHEN"1101"=> LED7S<="1011110";WHEN"1110"=> LED7S<="1111001";WHEN"1111"=> LED7S<="1110001";WHEN OTHERS =>NULL;END CASE;END PROCESS;END;实验内容二:1、硬件测试。

十六进制7段数码显示译码器设计实验报告

十六进制7段数码显示译码器设计实验报告实验报告:十六进制7段数码显示译码器设计一、实验目的本实验的主要目的是设计一种用于将十六进制数码转化为七段显示的译码器电路。

通过这个实验,我们可以学习和了解数字电路的工作原理、数码管的控制方式以及七段数码的译码方法。

二、实验原理本实验所用到的数码管为共阳数码管,它由7个发光二极管组成,其中的每一个发光二极管称为一个段。

这七个段依次为a、b、c、d、e、f和g,它们分别对应数码管上的abcdefg七个引脚。

当一些引脚输出高电平时,相应的段就会被点亮,从而显示出特定的字符。

为了实现将十六进制数码转化为七段显示的功能,我们需要设计一个译码器电路。

译码器电路的输入为十六进制数码,输出为七段信号,用于控制数码管的每个段的亮灭情况。

为了简化设计,我们可以采用CMOS数字集成电路74LS47来实现译码器电路。

该集成电路内部集成了BCD转七段译码器,可以将二进制代码转化为七段数码显示所需要的信号。

它的输入为四个二进制输入端口A、B、C和D,输出为七个段芯片(a、b、c、d、e、f和g)的控制信号。

三、实验步骤1.首先,根据74LS47的真值表,确定译码器的输入和输出。

2.根据真值表,画出逻辑图,确定硬件电路的连接方式。

3.按照逻辑图和电路连接方式,进行硬件电路的布线。

4.按照实验仪器的操作说明,对电路进行调试和测试。

5.将输入端口连接至外部的十六进制信号源,观察输出端口的数据是否正确。

6.验证电路的正确性和稳定性,如果出现问题,进行排除和修复。

四、实验结果经过实验,我们成功地设计并实现了一个十六进制7段数码显示译码器电路。

当输入端口接收到一个十六进制信号时,通过电路的处理和转换,将其转化为了相应的七段信号,用于控制数码管的每个段的亮灭情况。

通过实验观察,我们发现电路的输出结果与预期一致,且工作稳定。

五、实验总结通过这个实验,我们对于数字电路的工作原理和数码管的控制方式有了更深的了解。

实验二 7 段数码管静态显示译码器

实验二7 段数码管静态显示译码器1.实验目的学习quartusii 和modelsim的使用方法;学习原理图和veriloghdl混合输入设计方法;掌握7 段数码管静态显示译码器的设计及仿真方法。

2.实验原理根据下面电路图,设计7 段数码管静态显示译码器电路,在kx3c10F+开发板上实现该电路,并作仿真。

3.实验设备kx3c10F+开发板,电脑。

4.实验步骤4.1编译4.1.1七段数码管代码module segled(out1,a); //定义模块名和输入输出端口input [3:0]a; //输入一个3位矢量output [6:0]out1; //输出一个6位矢量reg [6:0]out1; //reg型变量用于always语句always@(a) //敏感信号啊begincase(a) //case语句用于选择输出4'b0000:out1<=7'b1000000;4'b0001:out1<=7'b1001111;4'b0010:out1<=7'b0100100;4'b0011:out1<=7'b0110000;4'b0100:out1<=7'b0011001;4'b0101:out1<=7'b0010010;4'b0110:out1<=7'b0000011;4'b0111:out1<=7'b1111000;4'b1000:out1<=7'b0000000;4'b1001:out1<=7'b0011000;4'b1010:out1<=7'b0001000;4'b1011:out1<=7'b0011100;4'b1100:out1<=7'b1000111;4'b1101:out1<=7'b0100011;4'b1110:out1<=7'b0000110;4'b1111:out1<=7'b0001110;endcaseendendmodule //模块结束效果图:4.1.2综合模块代码// Copyright (C) 1991-2013 Altera Corporation// Your use of Altera Corporation's design tools, logic functions // and other software and tools, and its AMPP partner logic// functions, and any output files from any of the foregoing// (including device programming or simulation files), and any// associated documentation or information are expressly subject // to the terms and conditions of the Altera Program License// Subscription Agreement, Altera MegaCore Function License// Agreement, or other applicable license agreement, including,// without limitation, that your use is for the sole purpose of// programming logic devices manufactured by Altera and sold by// Altera or its authorized distributors. Please refer to the// applicable agreement for further details.// PROGRAM "Quartus II 64-Bit"// VERSION "Version 13.1.0 Build 162 10/23/2013 SJ Web Edition" // CREATED "Mon Mar 27 15:23:18 2017"module Blok(a,out1);input wire [3:0] a;output wire [6:0] out1;segled b2v_inst(.a(a),.out1(out1));endmodule效果图:4.1.3编辑结果截图编译解释:在这个报告中,我们可以看到如下信息:Total logic elements 7/5136(<1%): 该芯片中共有5136个LE资源,其中的7个在这个工程的这次编译中得到了使用。

7段数码显示译码器设计

7段数码显示译码器设计数码显示译码器是一种可以将二进制代码转换为数码形式输出的电子装置。

它是数字电路中常见且重要的组成部分,用于将二进制数据转换为人们可以直接阅读和理解的数码显示。

本文将介绍一个基于74LS47芯片的7段数码显示译码器的设计。

一、设计目标设计一个能够接受4位二进制代码输入,并将其转换为对应的七段数码形式输出的译码器电路。

二、74LS47芯片介绍74LS47是一种四位BCD-7段数码译码器/驱动器芯片,它能够将4位BCD代码转换为对应的七段数码输出。

该芯片具有以下特点:1.输入:4位BCD代码(A,B,C和D)2.输出:共阳极(共阳)显示器的七个引脚(a,b,c,d,e,f和g)3.功能:将BCD代码转换为七段数码形式输出,用于显示三、电路设计1.将74LS47芯片的引脚连接至7段数码显示器的a,b,c,d,e,f和g引脚。

这些引脚负责控制七段数码的每个段。

2.A,B,C和D引脚接收4位二进制代码输入。

3. 第一个74LS47芯片的Vcc引脚连接到正电源,GND引脚连接到地。

4. 还需将每个74LS47芯片的GA和GB引脚连接在一起,形成一个输入信号的链。

GA和GB引脚连接到Vcc电源端。

5.在接有显示器的七段段引脚(a,b,c,d,e,f,g)和段选择(a-g`)之间插入电阻。

这些电阻可用于限流,避免过高电流对显示器和芯片造成损坏。

6.确保芯片和显示器之间的信号传输有效,没有短路或脱离接地。

四、工作原理1.输入:通过A、B、C和D四个引脚接收4位BCD代码,一共有16个可能的输入组合。

2.输出:将四位BCD代码转换为相应的七段数码输出,用于显示。

例如,输入“0000”将转换为“0”的数码形式。

3.七段显示器共阳极(共阳):对于共阳极的显示器,七个段引脚(a,b,c,d,e,f和g)的高电平将被激活,且通过公共引脚控制显示的数码部分。

4.区分位和段:每个数码位由七个段组成,通过该段的点亮和熄灭来表示所需显示的数字。

(完整word版)7段数码显示译码器设计

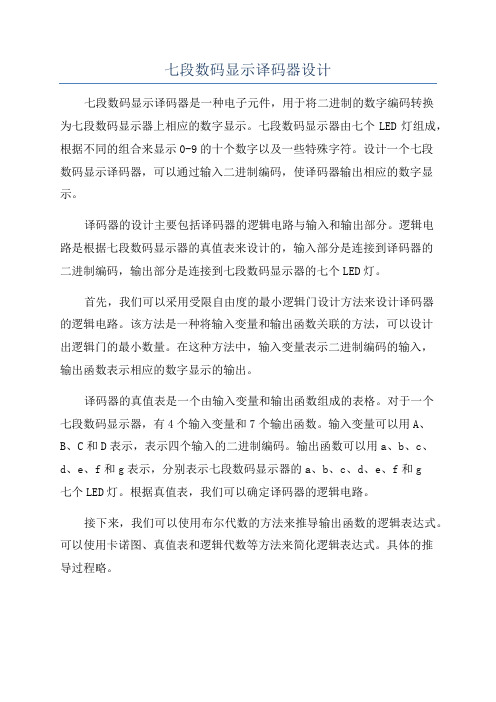

广州大学学生实验报告实验室: 电子信息楼 317EDA 2017 年10 月 16 日一 实验目的a) 学习7段数码显示译码器设计;学习VHDL 的多层次设计方法二 实验原理a) 如图是共阴极数码管。

b) 七段数码管是纯组合电路,通常小规模专用IC ,如74或4000系列的器件只能做十进制BCD 译码。

然而.数字系统中的数据都是2vhdl 译码程序在FPGA 中来实现,4位码为A[3:0],输出控制77位数据为LED7S[6:0]。

输出信号LED7S 的7位7个端,高位在左,低位在右。

例如当LED7S ”时,数码管的7个段g,f,e,d,c,b,a 分别接1,5,如果要考虑小dp ,这里不考虑小数点。

三实验设备a)FPGA实验箱,Cyclone III EP3C40Q24C08四实验内容和结果a)10进制译码器VHDL代码设计根据实验原理,输入7段数码管译码程序,如图所示:b)波形仿真显然,仿真结果和共阴数码管真值表结果相同,说明设计是正确的,能实现正常10进制译码c)引脚锁定和硬件验证如图所示:实验电路模式6,用数码8显示译码输出(PIO46-PIO40),键8/7/6/5四位控制输入硬件验证的结果也和仿真的结果一致,通过按键控制4位输入控制10进制数字,从数码管读出译码值。

发现电路是可行的,说明设计没有错误。

d)16进制译码器VHDL设计i.根据实验原理,输入7段数码管译码程序,如图所示,红色方框为添加了的程序代码,将10进制延伸到16进制,新增加了6个数据点。

ii.波形仿真,可以看到,输出可以对16个数据进行译码输出,遂可以知道该VHDL程序能实现16进制的译码,译码输出可以接数码管。

iii.引脚锁定和硬件仿真实验电路模式6,用数码8显示译码输出(PIO46-PIO40),键8/7/6/5四位控制输入硬件验证的结果也和仿真的结果一致,通过按键控制4位输入控制16进制数字,从数码管读出译码值。

EDA7段数码显示译码器设计(精)

EDA技术实验报告实验项目名称:7段数码显示译码器设计实验日期:2012.06.04实验成绩:实验评定标准:1)实验程序是否正确2)实验仿真、结果及分析是否合理3)实验报告是否按照规定格式实验目的实验器材学习7段数码显示译码器设计,学习VHDL的CASE语句应用及多层次设计方法。

Quartusll7.2 软件三、实验内容(实验过程)1、首先设计一个2选1的数据选择器(1)打开软件,选择菜单file —>new,在弹出的new对话框中选择Device Design Files 的VHDL File项,按OK键后进入VHDL文本编辑方式。

根据7段数码显示译码器的功能编辑相应的源程序。

如下: library ieee;use ieee.std」o gic_1164.all;en tity decl7s isport (a:i n std_logic_vector(3 dow nto 0; led7s:out std」o gic_vector(6 dow nto 0; end decl7s;architecture one of decl7s isbeg inprocess(abeg incase a iswhe n"0000"=>led7s<="0111111";whe n"0001"=>led7s<="0000110";whe n"0010"=>led7s<="1011011";whe n"0011"=>led7s<="1001111";whe n"0100"=>led7s<="1100110";whe n"0101"=>led7s<="1101101";whe n"0110"=>led7s<="1111101";whe n"0111"=>led7s<="0000111";whe n"1000"=>led7s<="1111111";whe n"1001"=>led7s<="1101111";whe n"1010"=>led7s<="1110111";whe n"1011"=>led7s<="1111100";whe n"1100"=>led7s<="0111001";whe n"1101"=>led7s<="1011110";whe n"1110"=>led7s<="1111001";whe n"1111"=>led7s<="1111001";whe n others =>nu II;end case;end process;end one;2、对该VHDL语言进行编辑后,无误后进行仿真。

(整理)七段显示译码器电路设计.

题目:七段显示译码器电路设计专业:生产过程自动化专业班级:生产过程0901 姓名:学号:指导老师:杨旭目录第一节绪论……………………………………………………………………………..1.1本设计的任务和主要内容………………………………………………………………..1.2基本工作原理及原理框图………………………………………………………………...第二节硬件电路的设计…………………………………………………………………2.1BCD译码器选择与设计…………………………………………………………………….2.2LED显示器的设计……………………………………………………………………………2.3总的设计……………………………………………………………………………………第四节设计总结…………………………………………………………………………第一节绪论本课程设计的七段译码器主要以BCD译码器或LED显示器为主要部件,应用集成门电路组成的一个具有译码和显示的装置。

其中BCD 译码器采用8421BCD译码器,即----七段显示译码器(74LS48)型。

LED显示器是由发光二极管组成的,LED显示器分共阴极和共阳极两种型号,共阴极LED显示器的发光二级管阴极接地,共阳极LED显示器的发光二极管阳极并联。

最后把BCD译码器或LED显示器组成了的装置就具有了显示和译码的功能。

此七段译码器也就成功了。

1.1设计的任务和本主要内容1)运用LED显示器或BCD译码器实现一定的功能2)写出详细的实验报告1.2基本工作原理及原理框图基本工作原理及原理框图如下:第二节硬件的设计BCD译码器选择与设计发光二极管(LED)由特殊的半导体材料砷化镓、磷砷化镓等制成,可以单独使用,也可以组装成分段式或点阵式LED显示器件(半导体显示器)。

分段式显示器(LED数码管)由7条线段围成字型,每一段包含一个发光二极管。

外加正向电压时二极管导通,发出清晰的光,有红、黄、绿等色。

EDA实验二_VHDL七段数码管显示译码

EDA实验二七段数码管显示译码的设计一、实验目的1、掌握七段数码管译码器的工作原理;2、学会运用波形仿真测试检验程序的正确性;3、学会运用波形仿真测试检验程序的正确性。

二、实验设备ZYE1502C型实验箱三、内容要求1、用拨位开关输入8421BCD码,七段数码管显示“0-F”16个16进制的数字。

2、观察字符亮度和显示刷新的效果:(1)在8个七段数码管上同时显示某一数字;(2)在8个七段数码管上动态显示某一数字。

3、扩展内容:(1)动态显示时,能即时改变显示的顺序;(2)动态显示时,实现显示数字从0~F的循环显示。

四、实验步骤1、输入:设计部分采用VHDL语言完成;2、编译;3、仿真;4、下载;5、连线。

(1)四个拨位开关(在P1、P2处选择)连接D3、D2、D1、D0信号所对应的管脚。

时钟CLK所对应的管脚同实验箱上的时钟源相连。

(2)扫描片选信号DIG(0 TO 3)的管脚同七段数码管(共阴)相连;(3)七段数码管驱动信号A,B,C,D,E,F,G的管脚分别同扫描数码管的段输入PCLK处的连接线孔A,B,C,D,E,F,G相连。

五、实验报告1、论述实验过程和步骤;2、填写正确的实验结果。

(1)通过两种显示效果分析:字符显示亮度同扫描频率的关系,且让人眼感觉不出光闪烁现象的最低扫描频率是多少?答:扫描频率越高,显示亮度越低。

人眼看是否闪烁与所用的时钟和分频方式有关,在频率稳定和分频均匀的情况下,最低扫描频率为256Hz,若分频不均匀或频率不稳定,则需更高频率。

(2)字形编码的种类,即一个7段数码管可产生多少种字符,产生所有字符需要多少根被译码信号线?答:一个7段数码管可产生2^7=128种字符,产生所有字符至少需要7根被译码信号线。

但假如只编译0-F,16个字符,则至少只需要4根被译码信号线。

六、实验小结。

答:1、不同控制端需要预先分配控制优先级,否则编写的时候会出现很多问题。

优先级分为普通和特殊,一般错误情况可以跨越权限显示出来。

基于FPGA的七段数码显示译码器的设计

基于FPGA的七段数码显示译码器的设计七段数码显示器是一种常见的显示设备,用于显示数字和一些字母字符。

在FPGA(Field Programmable Gate Array)上设计七段数码显示译码器可以实现数字输入到七段数码显示器的转换,并将对应的控制信号输出到相应的段。

FPGA是一种可编程逻辑设备,具有可重构性和可编程性,因此它可以用来设计各种数字逻辑电路,包括数码显示译码器。

设计一个基于FPGA的七段数码显示译码器需要以下步骤:

1.确定输入和输出:七段数码显示译码器的输入为数字(0-9),输出为七段数码显示器的段控制信号。

2.确定数码管的显示编码:七段数码管的每个段都有对应的编号,常用的编码方式有共阴极和共阳极两种。

确定使用哪种编码方式,决定了段控制信号的输出方式。

3.设计逻辑电路:根据数码管的显示编码和输入数字,设计逻辑电路来生成对应的段控制信号。

可以使用逻辑门、触发器和其他数字逻辑电路组合实现。

4. 编写HDL代码:使用硬件描述语言(如Verilog、VHDL等)编写逻辑电路的描述代码。

代码应包括输入端口、输出端口以及逻辑电路的实现。

5.进行仿真:使用仿真工具对编写的HDL代码进行仿真验证,确保逻辑电路的正确性。

6.确定FPGA芯片:选择适合需求的FPGA芯片,考虑输入输出端口数量、资源利用率以及时钟频率等因素。

7.进行综合:使用综合工具将编写的HDL代码综合为FPGA芯片可识别的级联逻辑门。

8.进行布局布线:使用布局布线工具将综合结果映射到FPGA芯片上的逻辑单元和连线。

9.进行时序分析:使用时序分析工具分析电路中的时序约束,如时钟频率,以确保电路工作正常。

7段显示译码器设计实验报告

数字钟实验报告学生专业:电子信息工程学生班级:151143C学生学号:*********学生姓名:***7段显示译码器设计151143324 ***一、实验目的:学习七段数码显示译码器设计,多层次设计方法和总线数据输入方式的仿真。

二、实验原理:7段BCD码译码器的设计,输出信号Segmentout的7位分别接数码管的7个段,高位在左,低位在右。

例如当Segmentout输出为“1101101”时,数码管的7个段:g、f、e、d、c、b、a分别接1、1、0、1、1、0、1,接有高电平的段发亮,于是数码管显示数字“5”。

如果是共阳极的数码显示器,则8段输出应取反,段显码为“10010010”,使用时要注意数码管的接法。

实际产品设计中,一般会用到多个数码管,显示几位数字。

4位数的7段数码管,4位数字共用同样的段输出。

若只想让第一个位显示,其他的位不显示,那么可以只给第一位数字供电,其他的断电,用4LED来控制的,4LED输出0001即可,若只让第二位显示则4LED输出0010即可。

这里的4LED选择控制要显示的位,称为位选。

三、实验内容:module BCD_Segment7(BCDin,Segmentout,Select);input[3:0]BCDin;output Select;output [6:0]Segmentout;reg[6:0]Segmentout;always@(BCDin)begincase(BCDin)4'h0:Segmentout=7'b1000000;4'h1:Segmentout=7'b1111001;4'h2:Segmentout=7'b0100100;4'h3:Segmentout=7'b0110000;4'h4:Segmentout=7'b0011001;4'h5:Segmentout=7'b0010010;4'h6:Segmentout=7'b0000010;4'h7:Segmentout=7'b1111000;4'h8:Segmentout=7'b0000000;4'h9:Segmentout=7'b0010000;4'hA:Segmentout=7'b0001000;4'hB:Segmentout=7'b0000011;4'hC:Segmentout=7'b1000110;4'hD:Segmentout=7'b0100001;4'hE:Segmentout=7'b0000110;4'hF:Segmentout=7'b0001110;default:Segmentout=7'bxxxxxxx;endcaseendassign Select=1'b0;endmodule四、时序仿真波形:引脚设定时序仿真波形参考设置:1、设置仿真时间。

七段显示译码器电路设计

七段显示译码器电路设计七段显示译码器是一种重要的数字电路,用于将二进制码转换为七段显示器上的对应数字或字母。

它通常由四个输入引脚和七个输出引脚组成,其中四个输入引脚表示二进制数的四位码,而七个输出引脚控制七段显示器中的各个段是否点亮。

下面是一个简单的七段显示译码器电路设计,它能够将四位二进制码转换为七段显示器所需的控制信号。

首先,我们需要定义一个真值表来描述七段显示器的每个数字或字母的显示信号。

下面是一个常用的真值表示例:输入编号,a,b,c,d,e,f,g--------,-,-,-,-,-,-,-0,1,1,1,1,1,1,01,0,1,1,0,0,0,02,1,1,0,1,1,0,13,1,1,1,1,0,0,14,0,1,1,0,0,1,15,1,0,1,1,0,1,16,1,0,1,1,1,1,17,1,1,1,0,0,0,08,1,1,1,1,1,1,19,1,1,1,1,0,1,1A,1,1,1,0,1,1,1B,0,0,1,1,1,1,1C,1,0,0,1,1,1,0D,0,1,1,1,1,0,1E,1,0,0,1,1,1,1F,1,0,0,0,1,1,1接下来,我们可以根据这个真值表来设计七段显示译码器的逻辑电路。

一个常见的方法是使用四个二-四译码器和一些逻辑门。

每个二-四译码器都有两个输入引脚和四个输出引脚,它将两个二进制数的每一位作为输入,将输出引脚的一些组合置高来实现对应输出数的逻辑。

在我们的设计中,我们可以将四个输入引脚分别连接到四个二-四译码器的输入引脚上,然后将四个输出引脚通过逻辑门连接到七个段的输入引脚上。

最后,我们需要选择适当的逻辑门来实现所需的逻辑。

常见的选择是使用与门和反相器。

与门用于实现多个输入引脚同时为高时将输出引脚置高的逻辑。

反相器则用于将逻辑信号进行反相。

例如,我们可以使用四个与门来实现输入二进制数为0、1、2和3时,对应输出引脚的逻辑。

然后,我们可以使用反相器来实现其他输出引脚的逻辑。

七段数码显示译码器设计

七段数码显示译码器设计七段数码显示译码器是一种电子元件,用于将二进制的数字编码转换为七段数码显示器上相应的数字显示。

七段数码显示器由七个LED灯组成,根据不同的组合来显示0-9的十个数字以及一些特殊字符。

设计一个七段数码显示译码器,可以通过输入二进制编码,使译码器输出相应的数字显示。

译码器的设计主要包括译码器的逻辑电路与输入和输出部分。

逻辑电路是根据七段数码显示器的真值表来设计的,输入部分是连接到译码器的二进制编码,输出部分是连接到七段数码显示器的七个LED灯。

首先,我们可以采用受限自由度的最小逻辑门设计方法来设计译码器的逻辑电路。

该方法是一种将输入变量和输出函数关联的方法,可以设计出逻辑门的最小数量。

在这种方法中,输入变量表示二进制编码的输入,输出函数表示相应的数字显示的输出。

译码器的真值表是一个由输入变量和输出函数组成的表格。

对于一个七段数码显示器,有4个输入变量和7个输出函数。

输入变量可以用A、B、C和D表示,表示四个输入的二进制编码。

输出函数可以用a、b、c、d、e、f和g表示,分别表示七段数码显示器的a、b、c、d、e、f和g七个LED灯。

根据真值表,我们可以确定译码器的逻辑电路。

接下来,我们可以使用布尔代数的方法来推导输出函数的逻辑表达式。

可以使用卡诺图、真值表和逻辑代数等方法来简化逻辑表达式。

具体的推导过程略。

最后,我们可以根据逻辑表达式设计译码器的逻辑电路。

可以使用逻辑门来实现逻辑函数,如与门、或门和非门等。

对于一个有7个输出函数的译码器,需要使用足够数量的逻辑门来实现逻辑函数。

在设计完逻辑电路之后,我们需要将输入和输出部分与逻辑电路连接起来。

输入部分是连接到译码器的二进制编码,输出部分是连接到七段数码显示器的七个LED灯。

可以使用连接器、导线和电阻等元件来完成连接。

综上所述,设计一个七段数码显示译码器需要进行以下几个步骤:确定逻辑电路的真值表,推导输出函数的逻辑表达式,设计逻辑电路,连接输入和输出部分。

七段译码器设计(含程序)

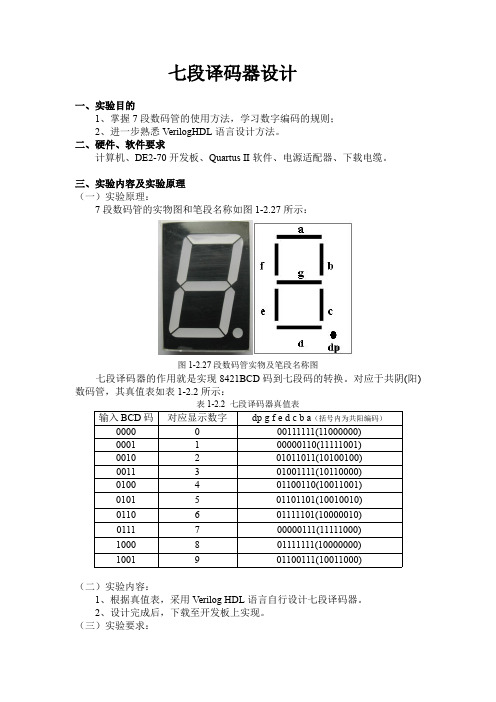

七段译码器设计一、实验目的1、掌握7段数码管的使用方法,学习数字编码的规则;2、进一步熟悉VerilogHDL语言设计方法。

二、硬件、软件要求计算机、DE2-70开发板、Quartus II软件、电源适配器、下载电缆。

三、实验内容及实验原理(一)实验原理:7段数码管的实物图和笔段名称如图1-2.27所示:图1-2.27段数码管实物及笔段名称图七段译码器的作用就是实现8421BCD码到七段码的转换。

对应于共阴(阳)数码管,其真值表如表1-2.2所示:表1-2.2七段译码器真值表输入BCD码对应显示数字dp g f e d c b a(括号内为共阳编码)0000000111111(11000000)0001100000110(11111001)0010201011011(10100100)0011301001111(10110000)0100401100110(10011001)0101501101101(10010010)0110601111101(10000010)0111700000111(11111000)1000801111111(10000000)1001901100111(10011000)(二)实验内容:1、根据真值表,采用Verilog HDL语言自行设计七段译码器。

2、设计完成后,下载至开发板上实现。

(三)实验要求:1、采用Verilog HDL语言设计方法完成七段译码器设计,写出Verilog程序;2、对程序进行功能仿真,仿真无误后进行管脚分配(输入8421BCD码:SW0-SW3,输出七段码:HEX0_D[0]-HEX0_D[6]),编译后将编程文件下载到DE2-70开发板,进行功能验证,并观察实验结果。

程序设计如下:module decoder7(data_in,data_out);input[3:0]data_in;output[7:0]data_out;reg[7:0]data_out;always@(data_in)begincase(data_in)4'b0000:data_out=8'b01000000;4'b0001:data_out=8'b01111001;4'b0010:data_out=8'b00100100;4'b0011:data_out=8'b00110000;4'b0100:data_out=8'b00011001;4'b0101:data_out=8'b00010010;4'b0110:data_out=8'b00000011;4'b0111:data_out=8'b01111000;4'b1000:data_out=8'b00000000;4'b1001:data_out=8'b00011000;default:data_out=8'b01111111;endcaseend endmodule。

实验六 BCD七段显示译码器的设计

浙江大学城市学院实验报告纸一.实验目的(1)学习利用VHDL语言设计BCD七段显示译码器的方法,掌握BCD 七段显示译码器的设计思路;(2)掌握软件工具的使用方法。

二.实验原理根据BCD七段显示译码器的真值表原理进行实验,如表2—3所示。

三.实验内容用VHDL语言设计BCD七段显示译码器,进行编译、波形仿真及器件编程,并自行用VHDL语言设计3线-8线译码器。

四.源程序清单library ieee;use ieee.std_logic_1164.all;entity gaoqianyi isport (a:in std_logic_vector (3 downto 0);y:out std_logic_vector (6 downto 0));end gaoqianyi;architecture zhang of gaoqianyi isbeginprocess(a)begincase a iswhen"0000"=>y<="0111111"; --0的BCD七段码when"0001"=>y<="0000110"; --1的BCD七段码when"0010"=>y<="1011011"; --2的BCD七段码when"0011"=>y<="1001111"; --3的BCD七段码when"0100"=>y<="1100110"; --4的BCD七段码when"0101"=>y<="1101101"; --5的BCD七段码when"0110"=>y<="1111101"; --6的BCD七段码when"0111"=>y<="0100111"; --7的BCD七段码when"1000"=>y<="1111111"; --8的BCD七段码when"1001"=>y<="1101111"; --9的BCD七段码when"1010"=>y<="1110111"; --A的BCD七段码when"1011"=>y<="1111100"; --B的BCD七段码when"1100"=>y<="0111001"; --C的BCD七段码when"1101"=>y<="1011110"; --D的BCD七段码when"1110"=>y<="1111001"; --E的BCD七段码when others=>y<="1110001"; --F的BCD七段码end case; end process; end zhang;附加:3线-8线译码器表2-4 3线-8线译码器真值表不带使能端library ieee;use ieee.std_logic_1164.all;entity gaoqianyi11 isport (a:in std_logic_vector (2 downto 0);y:out std_logic_vector (7 downto 0)); end gaoqianyi11;architecture zhang of gaoqianyi11 isbeginwith a selecty<="11111110"when"000","11111101"when"001","11111011"when"010","11110111"when"011","11101111"when"100","11011111"when"101","10111111"when"110","01111111"when"111","11111111"when others;end zhang;带使能端library IEEE;use IEEE.std_logic_1164.all;entity gaoqianyi111 isport (A : in std_logic_vector (2 downto 0);S1,S2,S3 : in std_logic;Y : out std_logic_vector (7 downto 0));end entity;architecture gaoqianyi111_arch of gaoqianyi111 is signal s : std_logic_vector(2 downto 0);beginS <= S1&S2&S3;process(A, S)beginY <= (others => '1');if S="100" thencase A iswhen "000" =>y<= "11111110";when "001" =>y<= "11111101";when "010" =>y<= "11111011";when "011" =>y<= "11110111";when "100" =>y<= "11101111";when "101" =>y<= "11011111";when "110" =>y<= "10111111";when "111" =>y<= "01111111";when others => NULL;end case;end if;end process;end architecture;五.实验总结我学会了利用VHDL 语言设计BCD 七段显示译码器的方法和自己编写类似的程序。

七段数码显示译码器设计

实验一七段数码显示译码器设计一、实验目的:1.完成七段数码显示译码器的设计,学习组合电路设计;2.学习多层次设计方法。

3.锻炼使用Verilog HDL 语言编程的能力。

二、实验原理:1.七段译码电路时一宗纯组合的逻辑电路,通常是由小型专用的IC门电路组成。

2.七段码输入与输出的原理与真值表关系。

a)输入:七段码输入为四个输入信号,用来表示0000—1111,即表示为十六进制的“0”到“F”。

b)输出:七段码输出为七个输出信号,分别用a,b, c,d,e,f,g七个符号来表示。

一般规定,输出信号为“1”时,它所控制的发光二极管为点亮状态,输出信号为“0”时,它所控制的发光二极管为熄灭状态。

本实验使用的七段数码为共阴极,其电路图如图1所示。

图1 共阴数码管及其电路c)输入与输出关系用思维二进制代码组成十六进制代码,将其用代码显示,表2-1 七段字符显示真值表数码A3 A2 A1 A0 A B C D E F G 对应码(h)0 0 0 0 0 1 1 1 1 1 1 0 7E1 0 0 0 1 0 1 1 0 0 0 0 302 0 0 1 0 1 1 0 1 1 0 1 6D3 0 0 1 1 1 1 1 1 0 0 1 794 0 1 0 0 0 1 1 0 0 1 1 335 0 1 0 1 1 0 1 1 0 1 1 5B6 0 1 1 0 1 0 1 1 1 1 1 5F7 0 1 1 1 1 1 1 0 0 0 0 708 1 0 0 0 1 1 1 1 1 1 1 7F9 1 0 0 1 1 1 1 1 0 1 1 7BA 1 0 1 0 1 1 1 0 1 1 1 77上,需要进行引脚分配。

一、实验步骤:(1) 创建工程文件(2) 创建原理图设计文档(3) 利用ESC绘制电路图进行功能设计(4) 执行综合(5) 设计测试平台文件(6) 执行功能仿真(7) 执行实现、添加约束文件(8) 执行时序仿真(9) 生产位流文件,配置目标芯片Verilog HDL程序:`timescale 1ns / 1ps//////////////////////////////////////////////////////////////////////////////////// Company:// Engineer://// Create Date: 18:47:07 03/10/2013// Design Name:// Module Name: ssss// Project Name:// Target Devices:// Tool versions:// Description://// Dependencies://// Revision:// Revision 0.01 - File Created// Additional Comments:////////////////////////////////////////////////////////////////////////////////////module decode_7(a, b, c, d, en, sega, segb, segc, segd,sege,segf,segg );input a, b, c, d, en;output reg sega, segb, segc, segd,sege,segf,segg;reg [1:7] segs;always @(a or b or c or d or en) beginif (en)case ({d, c, b, a})0:segs = 7'b1111110; //01:segs = 7'b0110000;2:segs = 7'b1101101;3:segs = 7'b1111001;4:segs = 7'b0110011;5:segs = 7'b1011011;6:segs = 7'b0011111;7:segs = 7'b1110000;8:segs = 7'b1111111;9:segs = 7'b1110011; //910:segs = 7'b1110111;//1011:segs = 7'b0011111;12:segs = 7'b1001110;13:segs = 7'b0111101;4:segs = 7'b10011111;15:segs = 7'b1000111;15default segs = 7'bx;endcaseelsesegs = 7'b0;{sega, segb, segc, segd,sege,segf,segg} = segs; endEndmodule实验过程中得到的图片:实验体会:本次实验通过对FPGA实验平台的使用,Verilog HDL语言有了一定的理解与认识,但在很多地方没有很好的熟练度,在以后的学习中还要好好的熟悉之。

BCD七段显示译码器的设计报告

实验二、BCD七段显示译码器的设计一、实验目的学习利用VHDL语言设计BCD七段显示译码器的方法,掌握BCD七段显示译码器的设计思路:掌握软件工具的使用方法。

二、实验原理三、实验内容1.用VHDL语言设计BCD七段显示译码器,进行编译、波形仿真及器件编程。

(代码一详见附录)产生仿真波形如下:BCD七段显示译码器仿真1分析:问:给定的代码驱动的是共阴极还是共阳极的七段数码管显示器?由BCD七段显示译码器真值表可知是共阴极七段数码管显示器。

2.用VHDL语言设计3-8译码器,进行编译、波形仿真及器件编程。

(代码二详见附录)产生仿真波形如下:3-8译码器仿真1四、实验心得在实验中,通过BCD七段显示译码器真值表真值表得到BCD七段显示译码器case 代码。

同理通过8-3译码器真值表修改BCD七段显示译码器case代码得到8-3译码器case代码。

附录代码一(BCD七段显示译码器代码):library ieee;use ieee.std_logic_1164.all;entity bcdym isport (a:in std_logic_vector(3 downto 0);y:out std_logic_vector(6 downto 0));end bcdym;architecture zhang of bcdym isbeginprocess(a)begincase a iswhen"0000"=>y<="0111111";when"0001"=>y<="0000110";when"0010"=>y<="1011011"; when"0011"=>y<="1001111"; when"0100"=>y<="1100110"; when"0101"=>y<="1101101"; when"0110"=>y<="1111101"; when"0111"=>y<="0100111"; when"1000"=>y<="1111111"; when"1001"=>y<="1101111"; when"1010"=>y<="1110111"; when"1011"=>y<="1111100"; when"1100"=>y<="0111001"; when"1101"=>y<="1011110"; when"1110"=>y<="1111001";when others=>y<="1110001";end case;end process;end zhang;代码二(8-3译码器代码):library ieee; use ieee.std_logic_1164.all;entity bm3_8 isport(a:in std_logic_vector(0 to 2);b:out std_logic_vector(0 to 7)); end bm3_8;architecture zhang of bm3_8 isbeginprocess(a)begincase a iswhen"000"=>b<="00000001";when"001"=>b<="00000010";when"010"=>b<="00000100";when"011"=>b<="00001000";when"100"=>b<="00010000";when"101"=>b<="00100000";when"110"=>b<="01000000";when others =>b<="10000000"; end case;end process;end zhang;。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

七段数码显示译码器设计

一、

实验目的:

学习7段数码显示译码器设计,学习VHDL 的多层次设计方法。

二、实验原理:

七段数码管由8个(a,b,c,d,e,f,g,dp )按照一定位置排列的发光二极管构

成,通常采取共阴极或者共阳极的设计,将8个二极管的同一极接在一起,通过分别控制另外的8个电极的电平,使二极管导通(发光)或截止(不发光)。

七段数码显示译码器的功能就是根据需要显示的字符,输出能够控制七段数

码管显示出该字符的编码。

三、

实验内容 :

1)用VHDL 设计7段数码管显示译码电路,并在VHDL 描述的测试平台下对译码器进行功能仿真,给出仿真的波形。

---------------------------------------------------------------------

程序: LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL; ENTITY SMG IS

PORT(A:IN STD_LOGIC_VECTOR(3 DOWNTO 0); LED7S:OUT STD_LOGIC_VECTOR(6 DOWNTO 0)); END;

ARCHITECTURE ONE OF SMG IS BEGIN

PROCESS(A)

BEGIN

CASE A IS

WHEN"0000"=>LED7S<="0111111"; WHEN"0001"=>LED7S<="0000110"; WHEN"0010"=>LED7S<="1011011"; WHEN"0011"=>LED7S<="1001111"; WHEN"0100"=>LED7S<="1100110"; WHEN"0101"=>LED7S<="1101101"; WHEN"0110"=>LED7S<="1111101"; WHEN"0111"=>LED7S<="0000111"; WHEN"1000"=>LED7S<="1111111"; WHEN"1001"=>LED7S<="1101111"; WHEN"1010"=>LED7S<="1110111"; WHEN"1011"=>LED7S<="1111100"; WHEN"1100"=>LED7S<="0111001"; WHEN"1101"=>LED7S<="1011110"; WHEN"1110"=>LED7S<="1111001"; WHEN"1111"=>LED7S<="1110001"; WHEN OTHERS=>NULL;

END CASE;

仿真波形:

2)数码管显示电路设计

利用以上设计的译码器模块,设计一个8位的显示电路。

利用时分复用的方式快速轮流点亮8个数码管,在视觉上形成8个数码管同时显示的效果(尽管实际上同一时间只有一个数码管被点亮)。

要实现以上功能,就必须按照一定时钟节拍,轮流使译码器输出所需要字符的编码;同时控制数码管的公共电极电平,轮流点亮数码管。

备注:在新试验箱中可酌情减少位数实现,新试验箱中管脚查阅教材中附录。

程序:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY VHDL42 IS

PORT(CLK:IN STD_LOGIC;

S:OUT STD_LOGIC_VECTOR(2 DOWNTO 0);

D:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

A:OUT STD_LOGIC_VECTOR(6 DOWNTO 0));

END VHDL42;

ARCHITECTURE ONE OF VHDL42 IS

SIGNAL C:STD_LOGIC_VECTOR(2 DOWNTO 0);

BEGIN

P1:PROCESS(CLK)

BEGIN

IF CLK'EVENT AND CLK='1'THEN

IF C<"111"THEN C<=C+1;ELSE C<="000";

END IF;

END IF;

S<=C;

END PROCESS P1;

P2:PROCESS(D)

BEGIN

CASE D IS

WHEN "0000"=> A<="0111111";WHEN "0001"=> A<="0000110"; WHEN "0010"=> A<="1011011";WHEN "0011"=> A<="1001111"; WHEN "0100"=> A<="1100110";WHEN "0101"=> A<="1101101"; WHEN "0110"=> A<="1111101";WHEN "0111"=> A<="0000111"; WHEN "1000"=> A<="1111111";WHEN "1001"=> A<="1101111"; WHEN "1010"=> A<="1110111";WHEN "1011"=> A<="1111100"; WHEN "1100"=> A<="0111001";WHEN "1101"=> A<="1011110"; WHEN "1110"=> A<="1111001";WHEN "1111"=> A<="1110001"; WHEN OTHERS=> NULL;

END CASE;

END PROCESS P2;

END;

仿真波形:

管脚锁定:

信号旧试验箱新试验箱No.2

管脚号连接的器件管脚号连接的器件clk 43 Clk1 153 CLK2

rst 35 开关2 234 键2

ena 30 开关1 233 键1

A(6) 11 SEG g167 SEG g

A(5) 10 SEG f166 SEG f

A(4) 9 SEG e165 SEG e

A(3) 8 SEG d164 SEG d

A(2) 7 SEG c163 SEG c

A(1) 6 SEG b162 SEG b

A(0) 5 SEG a 161 SEG a

S(2) 80 三-八译码器

的控制输入端

S(1) 79

S(0) 78。