TI KeyStone存储器架构

单片机程序固件加密的另一种思路

0引言:MCU 的发展过程和固件加密重要性随着大规模集成电路的出现和发展,单片机(MCU )将原有计算机上的CPU 、RAM 、ROM 、定时计数器和多种I/O 接口集成到一个芯片,从而形成芯片级的计算机。

这也是TI 工程师的Gary Boone 和Michael Cochran 发明的全球第一颗微控制器(MCU )———TMS 1000系列(图1)的雏形。

之后,日本电子厂商开始生产汽车用微控制器,包括用于车内娱乐、自动雨刷、电子锁和仪表盘的4位MCU ,以及用于发动机控制的8位MCU 。

时至今日,单片机除了传统的玩具市场、工业控制、汽车电子、白家电等,在物联网以及智能化浪潮来临以后,单片机更加成为产品设备的核心部件,一方面设备需要进行实时性高效智能的信息,另一方面还要能与其他设备进行信息互换,这些需求都需要由单片机来完成。

而中国拥有最为广泛的消费群体和应用场景,单片机在国内的发展优势也更为明显。

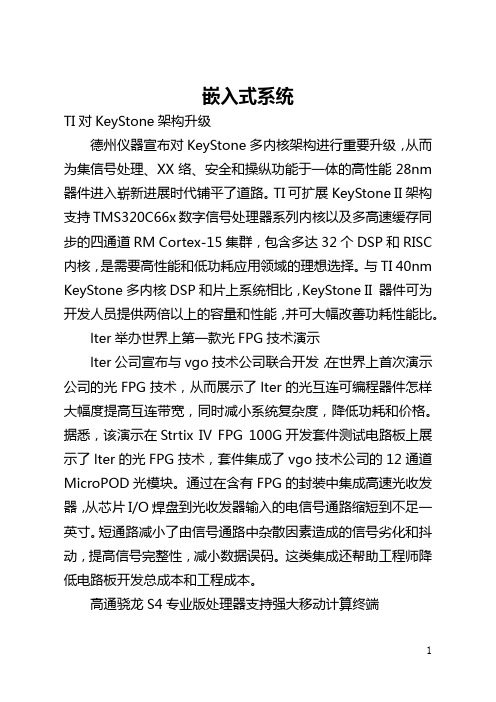

从图2所示,预计到2022年,中国MCU 市场规模将突破300亿元大关,预计达到319亿元!可以说,单片机因应用而生,除了芯片本身硬件性能,与应用相关的程序固件越发显得重要,固件安全的需求也就越来越受到关注!1单片机的信息安全首先,广义上的“安全”,也可视作为“信息安全”,它具有三个重要的特点:1)保密性:需要确保信息不为其它未授权的个人或团体所获得。

2)完整性:维持和确保信息的完整,不被未授权的篡改。

3)可行性:被授权访问信息的主体,在需要信单片机程序固件加密的另一种思路丘宁冰创芯工坊科技(深圳)有限公司图1TI 的TMS 1000系列MCU图2中国MCU 市场规模增长与预测息的时候能及时访问并获取。

保密性Confidentiality,Integrity完整性和可行性Availability,简称:CIA。

从以上特征描述,引申出处理信息安全的三种常用工具:标识、认证以及授权,也简称为:IAA。

1)标识:Identity首先,信息访问者标明主体身份,但是不确定该主体确实可访问该信息?所以,得验证其真假;2)认证:Authentication身份认证也就是核实主体声称的内容是否属实?以便在主体身份核实后,进行更细化的动作3)授权:Authorization作为更精细的信息处理,需要解决的问题包括:确保哪些信息可被授权人查看?被查看的信息是否保持完整,未被未授权的修改?以及被授权人可以随时方便的访问可查看的信息。

固态硬盘SSD内部结构是怎样的

固态硬盘SSD内部结构是怎样的固态硬盘(Solid State Drive),简称SSD(固盘),是用固态电子存储芯片阵列而制成的硬盘,由控制单元和存储单元(FLASH芯片、DRAM芯片)以及缓存单元组成,现在很多用户都在使用,容量大,读取和存储速度又快,那么内部结构组成是怎样的呢,如果你有兴趣的话,可以看看小编给大家科普的固态硬盘内部结构知识。

固态硬盘内部结构详解下面我们简单的聊了聊关于固态硬盘的发展历程,以及固态硬盘行业当下的市场格局,而这些都是比较大比较宏观的东西。

今天,将从微观出发,从固态硬盘本身出发,简单剖析固态硬盘的内外构造,让更多的人知道固态硬盘究竟长什么样子。

SSD主要由电子芯片及电路板组成:根据固态硬盘的定义,我们可以知道固态硬盘的内部结构,其实就是由三大块主控芯片、闪存颗粒、缓存单元构成,那么接下来,我们逐一来看。

1、固态硬盘大脑:主控芯片正如同CPU之于PC一样,主控芯片其实也和CPU一样,是整个固态硬盘的核心器件,其作用一是合理调配数据在各个闪存芯片上的负荷,二则是承担了整个数据中转,连接闪存芯片和外部SATA接口。

不同的主控之间能力相差非常大,在数据处理能力、算法上,对闪存芯片的读取写入控制上会有非常大的不同,直接会导致固态硬盘产品在性能上产生很大的差距。

慧荣主控当前主流的主控芯片厂商有marvell 迈威(俗称“马牌”)、SandForce、siliconmotion慧荣、phison群联、jmicron智微等。

而这几大主控厂商,又都有着自己的相应特点,应用于不同层级的固态产品。

以台系厂商siliconmotion慧荣为例,此款主控芯片主要特点在于能够为固态硬盘厂商提供包括软件和硬件在内的一体化主控方案,包括主控芯片、电路板以及存储单元,能够极大的提升产品的更新速度和使用寿命,并且不存在兼容等问题。

2、核心器件:闪存颗粒单元作为硬盘,存储单元绝对是核心器件。

在固态硬盘里面,闪存颗粒则替代了机械磁盘成为了存储单元。

DSP在雷达方面的应用

DSP在雷达方面的应用摘要:DSP是一种基于精简指令集的可编程数学计算芯片,可以对数字信号进行时频域变换、频谱分析、滤波、估值、增强、压缩等处理,广泛应用于家用电器、多媒体系统、雷达、卫星系统、移动通信、网络会议、医学仪器、实时图像识别与处理、语音处理、自适应制导控制、模式识别、定位、导航、联合战术无线电系统和智能基站等领域。

本文重点介绍通用DSP在雷达信号处理系统中的典型应用,以及研制基于DSP的雷达信号处理系统的关键技术。

关键词:DSP,军事,雷达;一、多核DSP在军事应用随着无人机(UAV)、声纳、雷达、信号情报(SIGINT)以及软件定义无线电(SDR) 等波形密集型应用中的信号处理需求不断攀升,多个数字信号处理器(DSP)内核的使用已成为重要的实现手段。

多核功能与不断丰富的IP内核及开发工具相结合可实现优异的系统架构。

所有这些应用都需要多核DSP来满足关键任务行业的各种需求,其中包括更强大的功能性(更快的处理速度)、更精细的分辨率以及更高的精度。

过去,处理器性能的改善是通过工艺节点升级及提高运行时钟频率来实现的。

然而,发展小型工艺节点和提高时钟频率并不是提高性能的低功耗捷径。

在单个裸片中集成多核的这个方法可在更低的时钟频率及功耗下实现所需的高性能。

当前的多核器件或采用同质内核,即所有处理内核都是相同的;或采用异质内核,即器件由不同类型的内核组成。

几乎所有应用都需要混合搭配的处理功能来满足行业需求。

从开发人员角度看,重点是支持同质内核,因为异质系统架构可通过同质器件创建。

反之,如果不牺牲性能就很难实现。

图1(下图)是作为异质多核架构实例的德州仪器 (TI) KeyStone 多核架构。

图1:德州仪器KeyStone多核架构TI KeyStone多内核架构拥有高度的灵活性,可同时集成定点与浮点运算、定向协处理与硬件加速,以及优化的内核间/组件间通信。

此架构包括多个 C66x DSP 内核,能够支持高达 256 GMAC 的定点运算性能以及 128GFLOP 的浮点运算性能。

第五章c66xcorepac

第五章C66x CorePacC66x CorePac的组成:●C66x DSP和相关C66x CorePac核;●一级和二级存储器(L1P,L1D,L2)●数据跟踪格式程序(data trace formatter, DTF)●内嵌跟踪缓冲器(embedded trace buffer)●中断控制●Power down controller●外部存储器控制●扩展存储器控制●专用上电/休眠控制C66x CorePac提供存储器保护,位宽控制及地址扩展。

图5.1所示为C66x CorePac示意图:5.1 存储器结构每个TMS320C6678器件的C66x CorePac都包含一个512KB二级存储器(L2),一个32KB一级程序存储器(L1P)和一个32KB数据存储器(L1D),该器件还包含一个4096KB的多核共享存储空间。

在C6678上的所有存储器在存储空间上都有相应的地址。

L1P和L1D缓冲器可以通过软件来设置。

L1P配置寄存器(L1PCFG)的L1PMODE 字段可以配置L1P,L1D配置寄存器(L1DCFG)的L1DMODE字段可以配置L1D。

5.1.1 L1P存储器●区域0是0K bytes,禁止●区域1是32Kbytes,没有等待状态5.1.2 L1D 存储器区域0是0K bytes ,禁止;区域1是32K bytes,没有等待状态;5.1.3 L2存储器●存储器的总小为4096KB●每个核有512KB●在每个核中的本地起始地址为0x00800000hL2存储器可以配置成全SRAM,全4通道相关联存储器,或者两者的结合。

L2可配置位缓冲的存储空间的大小是通过L2配置寄存器的L2MODE字段来控制的。

图5-4所示位L2配置成SRAM/缓冲可选方式。

器件复位后L2默认配置位全SRAM。

在系统中所有的主处理器核都可以全局寻址。

此外,局部存储器可以由协处理器通过“别名地址”(aliased addresses)直接访问,其中MSBs都置为0。

TI DSP选型

C6000™ 经过功耗优化的 DSP:

C6000™ DSP 平台提供行业最高性能的定点和浮点DSP,其中包括运行速度高达 1.2GHz 的最快定点DSP。

它是高性能音频、视频、影像和宽带基础设施

应用的理想选择。

系列的主要特点是低功耗,所以最适合个人与便携式上网以及无线通信应用,如手机、PDA、GPS等应用。

处理速度在80MIPS-PI并行接口、定时器、DMA 等外设。

值得注意的是C55XX 提供了EMIF 外部存储器扩展接口,可以直接使用SDRAM,而C54XX则,C28x该系芯片具有大量外设资源,如:A/D、定时器、各种串口(同步和异步),WATCHDOG、CAN 总线/PWM 发生器、数字IO C2000 有FLASH,也只有该系列有异步串口可以和PC 的UART 相连。

适合宽带网络和数字影像应用。

32bit,其中:C62XX 和C64X 是定点系列,C67XX是浮点系列。

该系列提供EMIF扩展存储器接同为浮点系列的C3X 中的VC33现在虽非主流产品,但也仍在广泛使用,但其速度较低,最高在150MIPS。

还提供DSP 的低功耗实时信号处理能力,最适合移动上网设备和多媒体家电。

其他系列的DSP 曾经有过风光,但现在都非TI X 的浮点系列:C30,C31,C32 C2X 和C5X 系列:C20,C25,C50每个系列的DSP 都有其主要应用领域。

keystone架构分析

Keystone基本概念介绍1. UserUser即用户,他们代表可以通过keystone进行访问的人或程序。

Users通过认证信息(credentials,如密码、API Keys等)进行验证。

2. TenantTenant即租户,它是各个服务中的一些可以访问的资源集合。

例如,在Nova 中一个tenant可以是一些机器,在Swift和Glance中一个tenant可以是一些镜像存储,在Quantum中一个tenant可以是一些网络资源。

Users默认的总是绑定到某些tenant上。

3. RoleRole即角色,Roles代表一组用户可以访问的资源权限,例如Nova中的虚拟机、Glance中的镜像。

Users可以被添加到任意一个全局的或租户内的角色中。

在全局的role中,用户的role权限作用于所有的租户,即可以对所有的租户执行role规定的权限;在租户内的role中,用户仅能在当前租户内执行role 规定的权限。

4. ServiceService即服务,如Nova、Glance、Swift。

根据前三个概念(User,Tenant 和Role)一个服务可以确认当前用户是否具有访问其资源的权限。

但是当一个user尝试着访问其租户内的service时,他必须知道这个service是否存在以及如何访问这个service,这里通常使用一些不同的名称表示不同的服务。

在上文中谈到的Role,实际上也是可以绑定到某个service的。

例如,当swift需要一个管理员权限的访问进行对象创建时,对于相同的role我们并不一定也需要对nova进行管理员权限的访问。

为了实现这个目标,我们应该创建两个独立的管理员role,一个绑定到swift,另一个绑定到nova,从而实现对swift进行管理员权限访问不会影响到Nova或其他服务。

5. EndpointEndpoint,翻译为“端点”,我们可以理解它是一个服务暴露出来的访问点,如果需要访问一个服务,则必须知道他的endpoint。

基于TMS320C667x和VPX的雷达处理系统设计及应用

基于TMS320C667x和VPX的雷达处理系统设计及应用宋玉霞;李贵;甘峰;邵江雨【摘要】针对基于CPCI或VME构建的雷达信号处理系统数传和处理能力的瓶颈,提出了一种以TI公司多核DSP TMS320C667x为核心处理器、基于VPX架构的高端高速雷达实时信号处理系统,介绍了系统的软硬件架构设计、电气结构设计、背板拓扑结构设计以及在雷达SAR成像处理模式、单脉冲处理模式的应用软件设计。

工程应用中的测试结果表明,该系统具有比传统信号处理系统更高的处理性能和与高性能相匹配的高速数传网络,应用前景广阔。

%For radar processing systems based on CPCI or VME,the data transmission and processing capability is a bottleneck.To address this issue,the design of a highlyreal⁃time processor based on multi⁃core DSP TMS320C667x from TI and VPX is presented,the design of software,hardware,electric structure and backplane topological structure is introduced,and the applications in SAR imaging and monopulse processing are proposed. The testing results in engineering application shown that this system has a better processing performance than traditional signal processor and a high⁃speed data transmission network matching with its high performance,and it has a good prospect of application.【期刊名称】《无线电工程》【年(卷),期】2016(046)011【总页数】4页(P71-74)【关键词】处理系统;TMS320C667x;VPX;SAR成像处理;单脉冲处理【作者】宋玉霞;李贵;甘峰;邵江雨【作者单位】中国西南电子技术研究所,四川成都610036;中国西南电子技术研究所,四川成都610036;中国西南电子技术研究所,四川成都610036;中国西南电子技术研究所,四川成都610036【正文语种】中文【中图分类】TN958.94过去10多年,雷达信号处理系统常采用TigerSHARC系列DSP或PowerPC系列CPU基于CPCI或VME总线进行构建。

先进半导体存储器-结构、设计与应用__概述说明

先进半导体存储器-结构、设计与应用概述说明1. 引言1.1 概述随着信息技术的快速发展,存储器设备在计算机和移动设备等领域中扮演着至关重要的角色。

在过去的几十年里,人们开发了各种类型的存储器,其中最为先进和广泛应用的是半导体存储器。

半导体存储器以其快速读写操作、高密度数据存储和较低功耗的优势成为主流技术。

1.2 文章结构本文将对先进半导体存储器的结构、设计与应用进行全面深入地探讨。

首先,我们将介绍先进半导体存储器的基本原理和发展历程,包括其在计算机系统中的主要类别和性能指标。

然后,我们将重点探讨先进半导体存储器在计算机系统中主存和缓存系统中的应用以及其在移动设备和云计算中的应用。

此外,我们还将探讨未来先进半导体存储器发展方向及挑战,并分析微细加工技术对其造成的影响与挑战。

最后,在结论部分对该论题进行总结,并展望先进半导体存储器的未来发展方向和挑战。

1.3 目的本文旨在通过对先进半导体存储器的结构、设计与应用进行全面分析,帮助读者深入了解该领域的最新进展和技术趋势。

文章将从基础原理入手,详细介绍各种先进半导体存储器的类型、特点和性能指标,并探讨其在计算机系统中的广泛应用。

此外,文章还将关注微细加工技术对先进半导体存储器的影响和挑战,并展望该技术领域的未来发展方向。

通过阅读本文,读者将深入了解现代存储器技术的发展趋势,为相关研究和应用提供参考依据。

2. 先进半导体存储器的结构与设计2.1 先进半导体存储器的基本原理先进半导体存储器是一种利用电子场效应管和电容来实现数据存储的半导体器件。

它通常由晶体管和电容构成,其中晶体管用于控制电荷在电容中的流动以实现数据的存取。

基本存储单元包括位线、字线、感应线和电容,通过调整位线、字线和感应线上的电势,并利用晶体管对数据进行读写操作。

2.2 先进半导体存储器的发展历程先进半导体存储器起源于上世纪60年代,经历了多个阶段的技术演进。

最初的静态随机访问存储器(SRAM)采用双稳态触发器作为基本单元,具有快速读写速度和较高可靠性。

嵌入式系统(全文)

嵌入式系统TI对KeyStone架构升级德州仪器宣布对KeyStone多内核架构进行重要升级,从而为集信号处理、XX络、安全和操纵功能于一体的高性能28nm 器件进入崭新进展时代铺平了道路。

TI可扩展KeyStone II架构支持TMS320C66x数字信号处理器系列内核以及多高速缓存同步的四通道RM Cortex-15集群,包含多达32个DSP和RISC 内核,是需要高性能和低功耗应用领域的理想选择。

与TI 40nm KeyStone多内核DSP和片上系统相比,KeyStone II 器件可为开发人员提供两倍以上的容量和性能,并可大幅改善功耗性能比。

lter举办世界上第一款光FPG技术演示lter公司宣布与vgo技术公司联合开发,在世界上首次演示公司的光FPG技术,从而展示了lter的光互连可编程器件怎样大幅度提高互连带宽,同时减小系统复杂度,降低功耗和价格。

据悉,该演示在Strtix IV FPG 100G开发套件测试电路板上展示了lter的光FPG技术,套件集成了vgo技术公司的12通道MicroPOD光模块。

通过在含有FPG的封装中集成高速光收发器,从芯片I/O焊盘到光收发器输入的电信号通路缩短到不足一英寸。

短通路减小了由信号通路中杂散因素造成的信号劣化和抖动,提高信号完整性,减小数据误码。

这类集成还帮助工程师降低电路板开发总成本和工程成本。

高通骁龙S4专业版处理器支持强大移动计算终端高通推出Snpdrgon骁龙S4 MSM8960专业版处理器,以支持功能更强大的移动计算终端。

S4专业版处理器采纳dreno 320图形处理器,支持更高分辨率的显示器,与S4系列产品在硬件和软件上兼容。

d r e n o 320为S4专业版处理器注入了新的多媒体功能,包括计算型照相机。

通过OpenCL 等应用程序接口直接利用dreno 320图形处理器的计算功能,以支持下一代照相方式。

为支持下一代3D图形应用程序接口,dreno 320将从硬件方面增加实例化、遮挡查询和多渲染目标等高级渲染功能,以实现更逼真的3D图形效果。

KeyStone内存架构

KeyStone内存架构Chunhua Hu;David Bell【期刊名称】《电子与电脑》【年(卷),期】2011(000)012【摘要】序言随着全球大量的资料强烈冲击无线和有线网络,营运商面临着严峻的挑战,需要不断推出能满足当前与未来需求的网络.因此,通信基础建设设备制造商致力于降低每bit成本和功耗的同时,也不断寻求能够满足当前及未来需求的核心技术.TI最新推出的新型KeyStone多核心SoC架构即能满足这些挑战.基于新型KeyStone多核心SoC架构的装置包含了多达8个TMS320C66x DSP CorePac,能够实现无与伦比的定点与浮点处理能力.KeyStone架构是一款精心设计且效率极高的多核心内存架构,能在执行任务的同时,允许所有的CorePac实现全速处理.本文探讨KeyStone内存层级,以及如何连结至SoC架构的其他部件,以实现多核心全速处理.KeyStone内存架构TI积极创新以面对多核心SoC技术挑战.TI KeyStone 架构包含全新的C66x定点和浮点DSP核心、针对基于标准的优化功能和接口的可配置协处理器、层级内存架构、TeraNet切换结构以及可将上述各部件连结在一起的多核心导航器.KeyStone架构具备3种内存阶级:每个C66xCorePac均拥有自己的一级程序(L1P)和一级数据(L1D)内存.另外,每个CorePac 还拥有本地(local)的二级统一内存.每个本地内存均能独立配置成内存映像的SRAM、快速缓冲贮存区,或是两者的组合.【总页数】5页(P71-75)【作者】Chunhua Hu;David Bell【作者单位】【正文语种】中文【相关文献】1.KeyStone架构的多核DSP中断路由机制及其实现方法 [J], 沙海珍;魏利卓2.基于新型非易失存储器的混合内存架构的内存管理机制 [J], 李琪;钟将;李雪;李青3.一种显示控制器和二维图形处理器通过同一个内存控制器访问内存的架构设计方法 [J], 张慧明; 秦奎4.基于FPGA的并行可配置Keystone实时处理架构设计 [J], 孙健;凌元;韩文俊5.德州仪器KeyStone Ⅱ架构助力多内核技术发展 [J],因版权原因,仅展示原文概要,查看原文内容请购买。

基于TMS320C6678的国产DSP操作系统引导程序设计

BOOTMODE[I2:0]用 于 引 导 方 式 的 设 置 。 上 的高 性 能 国产 基 础 软 件 解 决 方 案 , 其 内 核 完 全

电后 ,内核 0执行 RBL代码 ,并采样这 13个 自主 设 计 ,并 针对 TI公 司 TMS320C6678芯

引 脚 的 状 态 , 决 定 采 用 哪 种 引 导 方 式 。 管脚 配 片 进 行 了系 统 优 化 。

启 动 其 它 DSP节 点 是 一 种 非 常 高 效 的 引 导 方

本 文 的 引 导 是 针 对 于 带 有 操 作 系 统 的 镜

式 。

像 ,操 作系 统选用 国产 的锐 华 DSP实时操 作

TMS320C6678芯 片 有 13个 外 部 引 脚 系 统,该操 作系统提 供 了面 向主 流 DSP芯片

2 DSP启 动 方 式

RBL是 固化 在 DSP内 部 的 一 段 程 序 ,非 常精简 ,但是 无法直 接对 ELF格 式 的文件进 行解析 。为 了实现镜 像 的加载 ,必须通 过 TI 提 供 的一系列 的工 具将 ELF文件 转换 成特定 的格式,而 且不同接 口转换后 的格 式也不尽相 同 , 例 如 通 过 网 络 、SPI、 I2C、EMIF等 加 载 必须通过不同的方法完成转换 ,通用性极差 。

基于TI KeyStone C66x多核DSP TMS320C6678 + Xilinx Kintex-7 FPGA的高性能信号处理器简介

1 开发板简介

基于 TI KeyStone C66x 多核定点/浮点 DSP TMS320C6678 + Xilinx Kintex-7 FPGA 的高 性能信号处理器;

TI TMS320C6678 集成 8 核 C66x,每核主频 1.0/1.25GHz,每核运算能力高达 40GMACS 和 20GFLOPS,每核心 32KByte L1P、32KByte L1D、512KByte L2,4MByte 多核共享内 存,8192 个多用途硬件队列,支持 DMA 传输;

创龙不仅提供丰富的 Demo 程序,还提供 DSP 核间通信、DSP 与 FPGA 间通讯开发教 程以及技术支持,协助客户进行底板设计和调试以及多核软件开发。

2 典型运用领域

视频通信系统 电力采集 雷达声纳 光缆普查仪 医用仪器 机器视觉

3 软硬件参数

硬件框图

硬件参数

BOOT SET

1x 5bit 拨码开关

SWITCH

1x 电源开关

POWER

1x 12V 5A 直流输入 DC005 电源接口,外径 5.5mm,内径 2.1mm

FPGA ROM RAM SENSOR LED KEY

IO

表 2 FPGA 端硬件参数 Xilinx Kintex-7 XC7K325T-2FFG676I,兼容 XC7K160T/410T-2FFG676I 256Mbit SPI NOR FLASH 512M/1GByte DDR3 1x TMP102AIDRLT,核心板温度传感器,I2C 接口 5x 用户指示灯(核心板 2 个,底板 3 个) 3x 用户按键 1x 48pin 欧式连接器,GPIO 拓展 2x 400pin FMC 连接器,LPC 标准

一种基于嵌入式磁旋存储芯片的固态硬盘控制器芯片架构

一种基于嵌入式磁旋存储芯片的固态硬盘控制器芯片架构李炜【摘要】传统企业级固态硬盘存储芯片采用外接DRAM(Dynamic Random Access Memory)颗粒的方式来存储闪存地址转换映射表,不仅成本高,占用面积大,还需要设计复杂的掉电保护流程和额外的备电保持电容.利用新型磁旋存储芯片的掉电非易失特性,以及密度高、速度快、功耗低、数据保持时间长、可擦写次数无限等特点,提出了一种基于嵌入式磁旋存储芯片的固态硬盘控制器架构方案,能够大大简化控制器芯片的掉电异常流程和备电设计,节省固态硬盘内部的备电电容成本,有效支撑固态硬盘的容量提升.【期刊名称】《微型机与应用》【年(卷),期】2017(036)001【总页数】3页(P29-31)【关键词】磁旋存储芯片;固态硬盘;芯片架构;嵌入式【作者】李炜【作者单位】中电海康集团有限公司,浙江杭州311121【正文语种】中文【中图分类】TN492随着大数据和云计算的发展,大量的数据需要进行存储,另一方面,随着NAND 闪存(NAND Flash)工艺的进步和良率的提升,固态硬盘(Solid State Disk,SSD)的成本已经下降至接近企业级机械硬盘(Hard Disk Drive)相当的水平,SSD在服务器、数据中心以及存储系统中的应用越来越广泛。

传统的企业级SSD控制器大多采用基于DRAM方案的数据和表项存储方案,不仅设计难度大,掉电异常流程复杂,而且在SSD盘内需要占用大量的空间用来摆放备电钽电容,既增加了成本又制约了盘内利用空间,无法做到SSD的容量提升。

本文将嵌入式磁旋存储芯片(Spin-Transfer-Torque Magnetic Random Access Memory, STT-MRAM)应用于SSD控制器芯片架构设计中,能够简化掉电异常流程,节省SSD盘内备电电容,并可以提升硬盘容量达30%以上。

图1为当前主流企业级固态硬盘架构方案示意图。

冲向云端,TI最新KeyStone II多核SoC为您提供更好的云技术发展道路

冲向云端,TI最新KeyStone II多核SoC为您提供更好的云技术发展道路近几年,云概念不断升温,云技术确实给市场带来了很多机遇。

虽然针对云应用的产品层出不穷,但往往被性能、可扩展性、网络及功耗所限制。

为此,德州仪器(TI)寻求为云技术的发展创造更好的途径,最新Keystone II 多核SoC就应运而生了,它们特别是针对专用服务器、企业与工业应用以及电源网络这三大领域。

TI多核DSP中国市场开发经理蒋亚坚先生这样描述新产品的核心价值:“高密度运算+管理。

”听上去好像简单,但是要实现却不是那么容易。

TI多核DSP中国市场开发经理蒋亚坚更好的云技术发展道路TI最新推出的6 款28 nm多核SoC包括66AK2E02、66AK2E05、66AK2H06、66AK2H12、AM5K2E02 以及AM5K2E04,它们都建立在KeyStone II多核架构基础之上,并整合了ARM Cortex-A15 处理器、C66x DSP、数据包处理、安全处理以及以太网交换,可将实时云转变为优化的高性能低功耗处理平台。

其实今年3月TI推出的TC16612/4/6 SoC就集成了ARM Cortex-A15和C66x DSP,它们主要针对小型蜂窝基站的应用。

然而,如此卓越的架构应该服务于更多领域,此次,TI 就把它延伸到了云端,为云应用注入了新的活力。

6 款最新SoC 有2~12个核,总计15 GHz,速度范围为800 MHz~1.4 GHz,而功耗却只有6 W~13 W。

光看这几个指标就知道,这6款SoC能突破目前云应用中的诸多瓶颈。

与市面上其他多核ARM处理器不同,KeyStone II SoC具有全面的多核优势:其将互联带宽提高了1倍;数据通道从126 bit提高到256 bit;接口时钟速率也提高了1倍,这样可以让多核中每个处理器的性能都能得到释放,实现1+1大于或等于2。

TI DSP硬件平台方案选型

TI DSP硬件平台方案选型By ITSPY Q:514704465目 录1 引言 (1)1.1 目的 (1)2 TI DSP硬件平台 (1)2.1 KeyStone多核DSP +ARM处理器 (1)2.2 KeyStone多核处理器 (2)2.3 C6000™高性能多核 DSP (2)2.4 C6000™高性能 DSP (2)2.5 DaVinci™数字媒体处理器 (3)3 几种实现方案 (5)3.1 集成多个DM8168方案 (5)3.2 单个或集成多个C6678方案 (5)3.3 DM8168+C6678方案 (6)3.4 C6678 + ARM方案 (6)3.5 KeyStone多核+ARM SOC方案 (6)3.6 多核C66X + X86方案 (7)4 TI的多核DSP软件开发模型 (8)4.1 基于SYS/BIOS的开发模型 (8)4.2 基于Linux + SYS/BIOS的开发模型 (8)5 总结 (9)1引言1.1目的编写本需求的目的是对TI DSP硬件平台选型进行评估,根据项目具体要求和产品功能需求来确立产品开发平台,为硬件平台选型提供参考。

2TI DSP硬件平台TI的DSP目前为业界领先的DSP供应商。

C6000系列DSP目前为TI处理能力最高的一个系列,C6000针对应用的不同,其主要有以下各不同构架及性能的DSP:KeyStone 多核 ARM 处理器KeyStone 多核 DSPKeyStone™多核 DSP + ARM®C6000™高性能多核 DSPC6000™高性能 DSPDaVinci™数字视频处理器2.1 KeyStone多核DSP +ARM处理器包括各种器件选择,这些器件以最低的功率级别和成本提供最高的性能。

TI 的KeyStone 平台以低于多芯片解决方案的功耗,提供高达 5.6GHz 的 ARM 和 11.2GHz 的DSP 处理能力,因此适用于嵌入式基础设施应用,例如云计算、媒体处理、高性能计算、转码、安全、游戏、分析和虚拟桌面。

基于DSP6678实现多任务以太网络数据传输

基于DSP6678实现多任务以太网络数据传输王谦;田欢【摘要】The paper realizes the multi process Ethernet transceiver function based on the TMS320C6678 DSP and SYS/BIOS system.This paper firstly introduces the characteristics and architecture of TMS320C6678, and the software environment for network development: V5 SYS/BIOS, CCS 6 and NDK, and ifnally focuses on the implementation method of multi task Ethernet data transmission.%文章基于DSP TMS320C6678和SYS/BIOS系统实现多进程以太网络收发功能。

文章首先介绍了TMS320C6678的特性和架构,实现网络开发所需要的软件环境:CCS V5,SYS/BIOS 6和NDK,最后重点介绍多任务以太网数据传输的实现方法。

【期刊名称】《无线互联科技》【年(卷),期】2016(000)014【总页数】2页(P44-45)【关键词】DSP6678;以太网;SYS/BIOS;NDK;UDP【作者】王谦;田欢【作者单位】西安电子工程研究所,陕西西安 710100;西安电子工程研究所,陕西西安 710100【正文语种】中文在某型号雷达系统中信号处理板与多个分系统进行通信采用以太网络进行数据传输,一般信处板上的可编程器件如DSP或者FPGA不易实现这种多线程功能,传统的解决方法是另配一个单板机来完成此功能。

这种方法缺点有2个:一是提高了近1倍的硬件成本;二是增加了系统复杂程度,降低了可调试性和可靠度。

TI扩展KeyStone多核架构 提供空前大容量支持

TI 扩展KeyStone 多核架构提供空前大容量支持日前,德州仪器(TI) 宣布扩展其面向新兴云无线接入网络(C-RAN) 应用与网络服务器开发人员的KeyStone 多核架构,确保其市场领先基站片上系统(SoC) 解决方案继续在无线产业中保持领先地位。

具体而言,TI 正在为新兴C-RAN 基站模式扩展KeyStone 架构,其可为制造商开发极高性能的低功耗C-RAN 基站群集创建支持极大容量的器件池。

群集基站功能可集中处理容量,减少现场设备数量,为运营商降低运营成本提供一个创新方案。

TI 通过扩展KeyStone 架构,可为C-RAN 提供功能强大的低成本途径,帮助开发人员在小型蜂窝或宏蜂窝基站中使用KeyStone 器件的同时,保护其软件投资。

Yankee Group 移动基础设施首席分析师Ken Rehbehn 指出:TI 正在为功能强大的低成本云RAN 解决方案提供重要的支持技术。

扩展TI 高灵活KeyStone 架构以满足C-RAN 网络拓扑需求,就意味着无线系统创新人员可获得一体化架构从小型蜂窝扩展至大型C-RAN 处理池。

这些增强功能可在不显著增加成本的同时,提供重要的设计高灵活性,加快产品上市进程。

C-RAN 是无线领域除小型蜂窝、分布式天线系统(DAS)、有源天线阵列(AAA) 以及远程无线头端(RRH) 之外的又一款新兴拓扑工具,其部署可满足从站点采集到覆盖范围与容量改进,乃至环境管理(绿色环保基站)等各种日益严峻的挑战要求。

KeyStone 是首款多核基础设施架构,可为基站开发人员提供一款综合而全面的可扩展平台。

TI 针对C-RAN 的KeyStone 增强功能包括Multicore Navigator 不断扩展的Queue Manager,可提供超过16K 的队列以及100 万个描述符。

此外,TI 超链接芯片间接口可通过双端口运行扩展至100Gbps,。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

序言 随着全球范围内的海量数据对无线和有线网络的强大冲击,运营商面临着严峻的挑战,他们需要不断推出既能满足当前需求也能满足未来需求的网络。因此,通信基础局端设备制造商在致力于降低每比特成本和功耗的同时,也在不断寻求能够满足当前及至未来需求的核心技术。TI最新推出的新型 KeyStone 多内核 SoC 架构能够游刃有余地满足这些挑战。 基于新型 KeyStone 多内核 SoC 架构的器件集成了多达 8 个TMS320C66x DSP CorePac,能够实现无与伦比的定点与浮点处理能力。KeyStone 架构经精心设计,是一款效率极高的多内核存储器架构,允许并行执行任务的同时,还能使所有的 CorePac实现全速处理。本文探讨了 KeyStone 存储器的层级结构,及其将如何与 SoC架构的其他组件进行连接以实现多内核全速处理。 KeyStone存储器架构 德州仪器 (TI) 积极创新,努力迎接多内核 SoC 技术带来的挑战。TI KeyStone 架构拥有众多组件,其中包含全新的 C66x 定点和浮点 DSP 内核、可实现基于标准的优化功能和接口的可配置协处理器、层级存储器架构、TeraNet 交换结构以及可将上述各组件连结在一起的多内核导航器。KeyStone 架构具备三个存储等级。每个 C66xCorePac 均拥有自己的一级程序 (L1P) 和一级数据 (L1D) 存储器。另外,每个 CorePac 还拥有局域的二级统一存储器。每个局域存储器均能独立配置成存储器映射的SRAM、高速缓存,或是两者的组合。 KeyStone 架构包含共享的存储器子系统,其由通过多内核共享存储器控制器 (MSMC) 连接的内部和外部存储器组成。MSMC 允许CorePac动态地分享程序和数据的内外部存储器。 图 1 - KeyStone 器件方框图 - TMS320TCI6616 MSMC 的内部 RAM 允许各部分被配置成共享的二级 RAM 或者共享三级 (SL3) RAM,从而可为程序员提供高度的灵活性。SL2 RAM 仅能够在局域 L1P 和 L1D 高速缓存中缓存,而 SL3另外还可在局域 L2 高速缓存中进行缓存。 为向软件执行提供快速通道,外部存储器同内部共享存储器一样,通过同一存储器控制器进行连接,而并非像在嵌入式处理器架构上所进行的传统做法那样,与芯片系统实现互通互连。外部存储器始终被看作是 SL3 存储器,并可在 L1 和 L2 中缓存。接下来的我们将探讨在KeyStone 架构中实现的各种性能增强。 存储性能增强 C66x CorePac 的内部存储器架构与此前 C6000™ DSP 系列产品相比,主要在四个方面实现了增强,而这突出体现在性能指标和实用性方面。这些改进旨在实现如下优势:1) 无论多个内核和数据 I/O 是否处于高度繁忙状态,都能提高存储器各级的执行效率;2) 更轻松便捷地管理多个内核和数据 I/O 之间的缓存一致性;3) 存储器的保护与地址扩展,以及;4) 将对软错误的保护进一步扩展至较高级别的存储器。执行效率 —— C66x CorePac 的存储器子系统在功能上与最新的 C64x+™ 和C67x™ 系列 DSP 系列 C64x+™ 和 C67x™ 的相当。每个局域 L1存储器均为 32KB,并能够配置成全速缓存(默认)、全存储器映射 SRAM,或是 4、8 或 16KB 高速缓存选项的组合。L1P 始终为直接映射,而 L1D 则始终为双向集关联 (two-way set-associative)。 图2 – CorePac 存储器增强 相应地,局域 L2 存储器是高达 1MB 的统一存储器(最初宣布推出的器件为 512KB 或 1MB)。此外,该存储器也可配置为全高速缓存、全存储器映射 SRAM(默认),或是 32、64、128、256 或 512KB 四路集关联高速缓存选项的组合。 至共享存储器子系统的存取路径经过精心的重新设计,能够显著降低至较高级存储器的时延,无论所有CorePac和数据 I/O 是否处于繁忙状态,均能维持相同的效率。 二级存储器效率 —— 与之前的系列产品相比,LL2 存储器器件和控制器的时钟运行速率更高。C66x LL2 存储器以等同于 CPU 时钟的时钟速率运行。更高的时钟频率可实现更快的访问时间,从而减少了因 L1 高速缓存失效造成的停滞,在此情况下必须从 LL2 高速缓存或 SRAM 获取存储器)。光这一项改进就自动使得从 C64X+ 或 C67X 器件进行应用升级实现了很大的速度提升,而且无需为 C66x 指令集进行重新编译。 此外,无论是对用户隐藏的还是由软件命令驱动的高速缓存一致性操作都会变得更高效,而且需要执行的周期数也更少。反之,这也意味着自动的高速缓存一致性操作(例如检测、数据移出)对处理器的干扰更小,因而停滞周期数也更少。手动的高速缓存一致性操作(例如全局或模块回写和/或无效)占用较少的周期即可完成,这就意味着在为共享存储器判优的过程中,实现CorePac 之间或 CorePac 与 DMA 主系统的同步将需要更短的等待时间。 共享存储器效率 —— 为进一步提高共享存储器的执行效率,在 CorePac 内置了扩展存储器控制器 (XMC)。对共享内部存储器 (SL2/SL3) 和外部存储器 (DDR3 SRAM) 来说,XMC 是通向 MSMC 的通道,且架构的构建基础实施在此前具有共享二级(SL2)存储器(比如TMS320C6472 DSP)的器件之上。 图 3 - 共享存储器架构 在以前具有 SL2 存储器的器件上,通向 SL2 的存取路径与通向 LL2的存取路径一样,在邻近内部接口处均有一个预取缓冲器。预取功能可隐藏对共享 RAM 库的访问时延,并可优化代码执行及对只读数据的存取(全面支持写操作)。XMC 虽然也遵循相同的目标,但是却进一步扩展添加了强大得多的预取功能,从而对程序执行和 R/W 数据获取提供了可与 LL2 相媲美的最佳性能。预取功能不仅能在访问存储器之前通过拉近存储器和 C66x DSP 内核之间的距离来降低存取时延,而且பைடு நூலகம்能缓解其他 CorePac 和数据 I/O 通过 MSMC 争夺同一存储器资源的竞争局面。 MSMC 通过 256 位宽的总线与 XMC 相连,而 XMC 则可直接连接至用于内部 SL2/SL3 RAM 的 4 个宽 1024 位存储器组。内部存储器组使 XMC 中的预取逻辑功能能够在未来每次请求访问物理 RAM 之前获取程序和数据,从而避免后续访问停滞在 XMC。MSMC 可通过另一 256 位接口与外部存储器接口控制器直接相连,进一步将 CorePac 的高带宽接口一直扩展到外部存储器。 对于外部存储器而言,KeyStone架构可通过与共享内部存储器相同的通道进行访问,从而较之前的架构实现了显著的增强。该通道的宽度是之前器件的两倍,而速度则为一半,从而大幅降低了到达外部 DDR3 存储器控制器(通过 XMC 和 MSMC)的时延。在此前的 C6000 DSP 中以及众多的嵌入式处理器架构中,外部 CPU 和高速缓存访问是通过芯片级互连进行发布的,而 XMC 则可提供更为直接的最优通道。当从外部存储器执行程序时,其可大幅提高 L1/L2 高速缓存效率,并在多个内核与数据 I/O 对外部存储器并行判优时能够显著降低所带来的迟滞。 对于内部和外部存储器,所有的数据 I/O 流量都可通过多条直接通道进入 MSMC 到达芯片,而不是通过 CorePac 存储器控制器,从而在当数据 I/O 要访问 CorePacs 当前没有访问(例如,当 CorePac 从 SL2 执行,而数据 I/O往返于 DDR3 时)的存储器端点时,能使两者处于完全正交的状态;而且在 XMC 预取缓冲器后可提供判优以对 CorePacs 隐藏存储器组之间的冲突。 此外,XMC 还为数据和程序预取嵌入了多流预取缓冲器。程序预取缓冲器可为来自 L1P 和 L2 的读取请求提供服务,从而使其能够在 CPU 需要之前预取高达 128 字节的程序数据。数据预取缓冲器可为来自 L1D 和 L2 的读取请求提供服务。数据预取单元能够支持 8 个预取流,且每个流都能独立地从地址增加方向或地址减少方向预取数据。针对进入 DSP 内核的数据流,预取功能能够有助于减少强制失效损失。在多内核环境中,预取功能还能通过分散带宽峰值来提升性能。为在不增加负面影响的情况下利用预取实现性能提升,可在 16MB 范围内将存储器配置为启用或禁用预取属性。 外部存储器效率——除了将外部存储器连接到 MSMC 所带来的优势,KeyStone 外部存储器还包含了对外部存储器控制器 (EMIF) 的显著改进。KeyStone 架构能够以 1333MT/s以上的速率支持高性能 DDR3 SDRAM 存储器。虽然总线能配置成 16 或 32 位(为节省面板空间和功耗),但其实际支持的总线宽高达 64 位数据宽度。该架构相对于之前的架构具有更大的宽度以及更快的速度,从而允许集成多个更高性能的内核、加速器和数据 I/O。 高速缓存一致性控制——通常在多内核器件以及多器件系统内,数据作为处理的一部分在内核之间共享。KeyStone 架构可提供一些改进措施,以简化共享内部与外部存储器的一致性管理操作。 在 KeyStone 架构中,LL2 存储器始终与 L1D 高速缓存保持一致,所以不需要对一致性管理进行特殊的配置(虽然利用 L1D 一致性命令可实现一些性能优化)。SL2 和 SL3 这两种共享存储器不能由硬件来保障与 L1 和 L2 高速缓存的同步。因此需要软件控制往返于数据 I/O 页面的传输,以及对多内核之间共享缓冲器的访问。 为简化该过程,已将 fence 操作作为新的 MFENCE 指令添加到 CorePac 中。当与简单的 CPU 环路组合使用时,能将 MFENCE 用于实施 fence 操作,以保障读/写访问群组之间的序列一致性。能将其用于对可能从不同路径到达的特定端点的存储器请求进行同步。此外,对于多处理器算法,还可将其用于以特定顺序实现对存储器的存取,而这-顺序从所有 CPU 角度来看都一样。这可大幅简化共享数据段所需的一致性协议。 共享存储器保护与地址扩展 — C64x+ 和 C67x DSP 架构均将存储器保护作为内部存储器设计(L1、L2、SL2)的一部分。KeyStone 架构将存储器保护扩展至外部存储器,同时还增强了对内部存储器进行保护的灵活性。另外,MSMC 允许将外部存储器的地址空间从 32 位扩展至 36 位。 可为每个 C66x DSP 分配唯一的权限 ID (PrivlD) 值。可为数据 I/O 主系统分配一个 PrivID,EDMA 则例外,但它可以继承为每次传输进行配置的主系统的 PrivID 值。KeyStone 器件总共可支持 16 个 PrivID 值。存储器保护属性分别为管理员用户和普通用户分配了读/写/执行访问权限。 局域存储器的存储保护 —— C66x CorePac可提供由软件控制的请求者到存储器映射的灵活性,从而进一步扩展了此前 C6000 架构的存储器保护协议。所有存储器请求者(C66x CPU、EDMA、导航器、PCIe、SRIO 等)均拥有相关联的特权 ID。内部存储器控制器可以区分多达 6 个不同的请求者,并配置所有其他请求者。由于 KeyStone 器件集成了更多的内核以及更多的 DMA 主系统(I/O 和加速器),这一数目已不够用。KeyStone CorePac 允许将系统主控器的 ID 映射到保护逻辑中使用的 ID,以使应用能够获得量身打造的强大保护功能。 图 4 - 存储器保护属性 共享存储器的存储器保护 —— 共享存储器拥有多个存储器保护和地址扩展 (MPAX) 单元。C66x DSP 可通过 XMC 中的局域 MPAX 访问 MSMC 通道,而数据 I/O 则通过 MSMC 中的MPAX 逻辑访问 MSMC,并分别对内部共享存储器和外部存储器进行控制。 MPAX 单元将存储器保护和地址扩展结合成一步完成。正如对局域存储器的访问一样,MPAX 的运行基础为每个交易事务承载的特权 ID,用以代表存储器的请求者。对于每个 PrivID,相关联的 MPAX 单元在内部共享存储器和外部存储器中均支持最多 16 个存储段的定义。每个存储段均独立配置,并提供各自的存储器保护地址扩展属性。每个存储段的大小可以是2 的任意次方,范围介于 4KB 到 4GB 之间。地址扩展功能可将外部存储空间从 32 位地址扩展至 36 位。 图 5 – MSMC 地址扩展 存储器段的地址区间定义非常灵活,而且能够重叠以创建尺寸为非 2 的指数次方大小的段以及附加的存储器区域。 地址扩展功能可将 32 位地址重新映射到 36 位,从而支持更大的外部存储器。地址扩展能将 DSP 内核中相同的虚拟地址映射到不同的物理地址,并将多个虚拟地址映射到同一物理地址,这对于同一个存储器来说具有不同的语义。MPAX 单元可将运行在不同 DSP 内核之上的操作系统和应用进行隔离,并能轻松支持共享程序。 图 6 显示了如何在 KeyStone 架构内使用 MPAX 来构建多内核虚拟存储器的实例。假定所有内核均运行同一应用,则可将该共享程序和静态数据加载至共享的内部和外部存储器区域中。私有变量(如数据 1)可以使用各个内核中的同一虚拟地址,同时 MPAX 将其映射至不同的物理存储器地址。软件在运行时无需重新进行任何地址映射即可使相同的代码映像在多个内核上执行。 错误检测与校正 —— 专用于基础局端系统的数代 C6000 器件系列,内部存储空间中包含了软错误校正功能。KeyStone 系列器件以该技术为构建基础,能够进一步将软错误保护扩展至存储器的所有层级。 图 6 - 多内核虚拟存储器 层级系统中的存储器控制器可支持多级保护,并可用于实现对代码段进行全面校正,并对数据空间进行错误检测。L1P、L2 和 SL2(或 SL3 内部 RAM)均包含可用于检测和校正 128 位或 256 位存储器段内单个位错误的奇偶校验信息。另外,我们还将能检测到同一访问中的两个位错误并触发访问 CorePac 产生异常。对于数据存取,仅能检测到位误差,并触发异常。无论发生检测还是校正事件,信息均被存储在错误访问的存储器控制器中,以便为应用和/或主机恢复提供信息援助。 通过 ECC 逻辑可将软错误保护进一步扩展至外部存储器空间。每 64 位数据有一个 8 位 ECC 码,根据选项可配置成支持 32 位和 64 位数据宽度。添加 ECC 需要支持 32 位数据宽度的额外 4 位 DDR3 IC(实现 36 位接口),或额外的 8 位 DDR3 IC(实现 72 位接口)以存放与整个外部数据空间相关的 ECC 值。 总结 新型 KeyStone 架构在存储器架构方面具备各种优势,意味着无论在单内核还是在多内核 SoC 执行环境中都能够直接实现显著的性能提升。与此前的产品系列相比,这些性能提升涉及各级存储器,如局域 L2、共享 L2/L3,以及外部存储器等。通过高效判优和预取机制,性能改进也体现在多内核、加速器以及数据 I/O 的并行访问方面。 针对内核之间以及内核与数据 I/O 之间的共享数据页面,缓存一致性控制的改进可实现更简单的判优。 实施存储器保护和地址扩展可实现高度灵活的编程模型、更大范围的地址搜索并为错误访问提供保护。 针对各级存储器的软错误保护可确保运行时执行不受随机软错误事件的影响,而这一事件会对所有嵌入式处理器造成影响。 Keystone 架构在存储器性能、易操作性以及灵活性方面实现的改进可确保程序员能够实现由功能强大的新型C66X DSP系列提供的全速性能优势。该架构具有卓越的可扩展性,其为具有各种数量的内核、加速器和数据 I/O 的 SoC 系列奠定了坚实基础。