数电课件第9次课

合集下载

数电课件Lecture 9

Parallel inputs Serial outputs

13

Figure 9–12 A 4-bit parallel in/serial out shift register.

14

Example: Show the data-output waveform for a 4-bit register with the parallel input data and the clock and other control signal.

30

Summary

The concept of shift register Some kinds of shift register

Serial In/Serial Out Serial In/parallel Out Parallel In/Serial Out Parallel In/Parallel Out Bidirectional Shift

Shift register counters Applications

31

Assignments

Edition 10

Page 397~398

Fig. 9-6(a)

9

9.3 Serial IN/Parallel OUT Registers

Data bits enter into registers serially Data bits are taken out of the registers in the

parallel way

1

9.0 Registers

One or more flip-flops used to store and shift data

2

D3

DQ

13

Figure 9–12 A 4-bit parallel in/serial out shift register.

14

Example: Show the data-output waveform for a 4-bit register with the parallel input data and the clock and other control signal.

30

Summary

The concept of shift register Some kinds of shift register

Serial In/Serial Out Serial In/parallel Out Parallel In/Serial Out Parallel In/Parallel Out Bidirectional Shift

Shift register counters Applications

31

Assignments

Edition 10

Page 397~398

Fig. 9-6(a)

9

9.3 Serial IN/Parallel OUT Registers

Data bits enter into registers serially Data bits are taken out of the registers in the

parallel way

1

9.0 Registers

One or more flip-flops used to store and shift data

2

D3

DQ

2019A班数电第九章-69页PPT精选文档

G1

v1 &

Ri

vO1 C

v2

G2

&

5100pF

R 33 0

vO2

vO1上跳至高电平 v2跳变为高电平 vO2为低电平

3.6V

vI

0.3V

1.4V

v1

0.3V

触发器受触发发生一次翻转,

进 入 暂 稳 态 ( vO1=VOH ,

vO1

3.6V 0.3V

3.6V

vO2=VOL)。

v2 0.3V 1.4V

于稳定状态。

当t=t1时,vI上跳变

触发器翻转一次,进入暂稳态

3.6V

vO1

0.3V

3.6V

v2

1.4V 0.3V

vO2

tw 0 t1 t2

9.2 集成门构成的脉冲单元电路

(2) 积分型单稳态触发器

②t1~t2暂稳态 vI=VOH vO1=VOL

&

v2

& vO2

vI

vO1 R

G2

G1

C

电容C放电,电压v2下降

③t≥t2电路的恢复过程

反馈线

Ci vI

G1

v1 &

Ri

vO1 C

v2

G2

&

5100pF

R 33 0

vO2

3.6V

电容C开始放电,电路进入 vI

0.3V

恢复阶段。

恢复时间为 tre(3~ 5)RCvv1O1

当下一个触发脉冲出现时,

1.4V 0.3V

3.6V 0.3V

3.6V

触发器再次进入暂稳态,经 v2 0.3V 1.4V

R1 R2 R2

第九数字电路 120页PPT文档

《 电工电子技术基础》 赵承荻、周玲主编 高等教育出版社

第九章 数字电路

第一节 数制与编码 第二节 逻辑门电路 第三节 触发器 第四节 寄存器和计数器 第五节 译码器与显示器件

章目录 返回 上一页 下一页

《 电工电子技术基础》 赵承荻、周玲主编 高等教育出版社

第九章 数字电路

1. 模拟信号 电子电路中的信号

例:根据输入波形画出输出波形

一个二进制数1101按权展开可以表示为: (1101)2=1×23 +1×22+0×21+1×20

章目录 返回 上一页 下一页

《 电工电子技术基础》 赵承荻、周玲主编 高等教育出版社

3.二-十进制数间的转换

1)二进制数转换成十进制数——乘权相加法 将二进制数按位权展开后相加, 即得等值的十进制数。 例如

“非”门的逻辑表达式 表9-

为:,式中,读作“A 3“非”

非”或“A反”。“非” 门真

门的真值表如表9-3所 值表

示。“非”门的逻辑 功能是“有0出1,有l

AY

出0”。

01

10

章目录 返回 上一页 下一页

《 电工电子技术基础》 赵承荻、周玲主编 高等教育出版社

四、复合逻辑门

1.“与非”门 在“与”门后面接一个“非”门,就构成“与非” 门,其逻辑结构及符号如图所示。

章目录 返回 上一页 下一页

《 电工电子技术基础》 赵承荻、周玲主编 高等教育出版社

五、集成门

例9-3 某逻辑电路是用74LS00构成,其

连线如图9-10(a)所示,其中A、B为输入端,

Y为输出端,画出逻辑电路图,写出逻辑表 达式。

章目录 返回 上一页 下一页

《 电工电子技术基础》 赵承荻、周玲主编 高等教育出版社

第九章 数字电路

第一节 数制与编码 第二节 逻辑门电路 第三节 触发器 第四节 寄存器和计数器 第五节 译码器与显示器件

章目录 返回 上一页 下一页

《 电工电子技术基础》 赵承荻、周玲主编 高等教育出版社

第九章 数字电路

1. 模拟信号 电子电路中的信号

例:根据输入波形画出输出波形

一个二进制数1101按权展开可以表示为: (1101)2=1×23 +1×22+0×21+1×20

章目录 返回 上一页 下一页

《 电工电子技术基础》 赵承荻、周玲主编 高等教育出版社

3.二-十进制数间的转换

1)二进制数转换成十进制数——乘权相加法 将二进制数按位权展开后相加, 即得等值的十进制数。 例如

“非”门的逻辑表达式 表9-

为:,式中,读作“A 3“非”

非”或“A反”。“非” 门真

门的真值表如表9-3所 值表

示。“非”门的逻辑 功能是“有0出1,有l

AY

出0”。

01

10

章目录 返回 上一页 下一页

《 电工电子技术基础》 赵承荻、周玲主编 高等教育出版社

四、复合逻辑门

1.“与非”门 在“与”门后面接一个“非”门,就构成“与非” 门,其逻辑结构及符号如图所示。

章目录 返回 上一页 下一页

《 电工电子技术基础》 赵承荻、周玲主编 高等教育出版社

五、集成门

例9-3 某逻辑电路是用74LS00构成,其

连线如图9-10(a)所示,其中A、B为输入端,

Y为输出端,画出逻辑电路图,写出逻辑表 达式。

章目录 返回 上一页 下一页

《 电工电子技术基础》 赵承荻、周玲主编 高等教育出版社

第9章 数字逻辑基础PPT课件

例如:(例9-2)偶数判别电路的波形图如下:

偶判电路输入输出波形

15.08.2020

9.2.2 逻辑函数几种表示方法的相互转换

逻辑函数5种表示方法相互转换关系

15.08.2020

1.根据逻辑函数表达式画逻辑图 将逻辑函数表达式中变量之间的运算关系用相应的逻 辑符号表示出来,就可以得到该函数的逻辑图。 例9-4 试画出逻辑函数 FABBCAC 的逻辑图。

特点:有1 则1, 全0则0

15.08.2020

逻辑或运算真值表

AB Y 00 0 01 1 10 1 11 1

逻辑或的波形图

真值表特点: 有1 则1, 全0则0

逻辑推广到多变量: Y=A+B+C+D+···

15.08.2020

3.逻辑非(NOT) “非”逻辑:决定事件发生的条件只有一个,条件不 具备时事件发生(成立),条件具备时事件不发生。 记为: Y=A 逻辑非的运算规则 0 =1, 1 =0

符号: A B

&

Y

A B AB Y 00 0 1 01 0 1 10 0 1

多个逻辑变量时:

Y=AB C

11 1 0

15.08.2020

(2) 或非门 表示式: Y= A+B 符号: A ≥1 Y B

真值表

A B AB Y 00 0 1 01 1 0 10 1 0 11 1 0

多个逻辑变量时: Y= A+B+C

15.08.2020

4.根据逻辑表达式求真值表

将自变量所有可能的取值组合代入逻辑 表达式中,计算出相应的逻辑函数的值,便 可列出其真值表

15.08.2020

9.2.3逻辑函数的化简 所谓逻辑函数的化简,就是 使逻辑函数的形式最简单。

偶判电路输入输出波形

15.08.2020

9.2.2 逻辑函数几种表示方法的相互转换

逻辑函数5种表示方法相互转换关系

15.08.2020

1.根据逻辑函数表达式画逻辑图 将逻辑函数表达式中变量之间的运算关系用相应的逻 辑符号表示出来,就可以得到该函数的逻辑图。 例9-4 试画出逻辑函数 FABBCAC 的逻辑图。

特点:有1 则1, 全0则0

15.08.2020

逻辑或运算真值表

AB Y 00 0 01 1 10 1 11 1

逻辑或的波形图

真值表特点: 有1 则1, 全0则0

逻辑推广到多变量: Y=A+B+C+D+···

15.08.2020

3.逻辑非(NOT) “非”逻辑:决定事件发生的条件只有一个,条件不 具备时事件发生(成立),条件具备时事件不发生。 记为: Y=A 逻辑非的运算规则 0 =1, 1 =0

符号: A B

&

Y

A B AB Y 00 0 1 01 0 1 10 0 1

多个逻辑变量时:

Y=AB C

11 1 0

15.08.2020

(2) 或非门 表示式: Y= A+B 符号: A ≥1 Y B

真值表

A B AB Y 00 0 1 01 1 0 10 1 0 11 1 0

多个逻辑变量时: Y= A+B+C

15.08.2020

4.根据逻辑表达式求真值表

将自变量所有可能的取值组合代入逻辑 表达式中,计算出相应的逻辑函数的值,便 可列出其真值表

15.08.2020

9.2.3逻辑函数的化简 所谓逻辑函数的化简,就是 使逻辑函数的形式最简单。

《数字电子技术基础》第9章.数模模数转换电路概要

9.2 A/D转换电路

9.2.4 双积分A/D转换电路

图9.2.10是一个n位双积分A/D转换电路,它由积分器A1、比 较器A2、n位二进制计数器和控制逻辑电路四部分组成。

图9.2.10

双积分A/D转换电路

9.2 A/D转换电路

双积分A/D转换电路先把电压转换成中间 量时间,再将时间转换为数字量,所以也称为 V T转换电路。还可以把电压转换成其他物理 量,如先把电压转换成频率,再将频率转换为 数字量,即V F转换电路。上述介绍的转换方 法属于间接转换,双积分A/D转换电路是间接 转换方法中应用最为普遍的电路。逐次比较、 并行比较等A/D转换方法直接将电压转换为数 字,属于直接转换法。

图9.1.4

权电阻网络D/A转换电路

9.1 D/A转换电路

9.1.2 倒T电阻网络

n位倒T电阻网络D/A转换电路原理图如图9.1.5所示。

图9.1.5

倒T电阻网络D/A转换电路

9.1 D/A转换电路

9.1.3 权电流D/A转换电路

倒T电阻网络D/A转换电路中的模拟开 关存在着导通电阻和导通压降,它们会引 起流过各支路的电流变化,产生转换电流 误差问题。为了改进倒T电阻网络D/A转 换电路的精度,可以采用恒流源代替各支 路电阻产生电流的权电流D/A转换电路。

9.2 A/D转换电路

A/D转换是D/A转换的逆过程,在A/D转换 电路中,将一个输入连续的模拟信号变换为输 出离散的数字信号。若模拟参考量为UERF,则 输出数字量D和输入模拟量A之间的关系为

9.2 A/D转换电路

9.2.1 采样-保持电路

在A/D转换过程中, 持电路,使输入A/D转 换电路的信号在一次转 换时间内保持不变。 所谓采样就是将一 个时间上连续变化的模 拟量转换为时间上离散 的模拟量。图9.2.3表 示出了模拟信号与采样 信号的波形关系。 图9.2.3 模拟信号采样过程

精品课件-数字电子技术-第9章

第9

2.按编程工艺分类 (1)低熔丝和反熔丝编程器件:体积小,集成度高, 速 度高, 易加密, 抗干扰, 耐高温; 只能一次编程, 在设 计初期阶段不灵活, 如Actel的FPGA器件。 (2) EEPROM编程器件: 可反复编程, 不用每次上电重 新下载, 但相对速度慢, 功耗较大, 如大多数CPLD器件。 (3) SRAM编程器件: 可反复编程, 实现系统功能的动 态重构; 每次上电需重新下载, 实际应用时需外挂EEPROM 以保存程序, 如大多数公司的FPGA器件。 (4) 在系统可编程器件。

20世纪80年代中期,Altera公司推出了一种新型的可擦 除、可编程逻辑器件 (ErasableProgrammableLogicDevice,EPLD),它采用CMOS和 UVEPROM工艺制作,集成度比PAL和GAL高得多,设计也更加灵 活,但内部互连能力比较弱。1985年,Xilinx公司首家推出了 现场可编程门阵列(FieldProgrammableGateArray,FPGA)器件, 它是一种新型的高密度PLD,采用CMOS-SRAM工艺制作,其结 构和阵列与PLD不同,内部由许多独立的可编程逻辑模块组成, 逻辑块之间可以灵活地相互连接,具有密度高、编程速度快、 设计灵活和可再配置设计能力等许多优点。FPGA出现后立即 受到世界范围内电子设计工程师的普遍欢迎,并得到迅速发展。

第9

第9

9.1 概述 9.2 可编程逻辑阵列(PLA) 9.3 可编程阵列逻辑(PAL) 9.4 通用阵列逻辑(GAL) 9.5 CPLD、 FPGA可编程逻辑器件 9.6 可编程逻辑器件的开发技术

第9 9.1 概述

随着新的EDA工具的不断出现,设计者可以直接设计出系 统所需要的专用集成电路,从而给电子系统设计带来了革命性 的变化。专用集成电路 (ApplicationSpecificIntegratedCircuit,ASIC)是指专门 为某一应用领域或为专门用户需要而设计、制造的LSI或VLSI 电路,它可以将某些专用电路或电子系统设计在一个芯片上, 构成单片集成系统。

数字电子技术(课件)lec09

2013-7-28

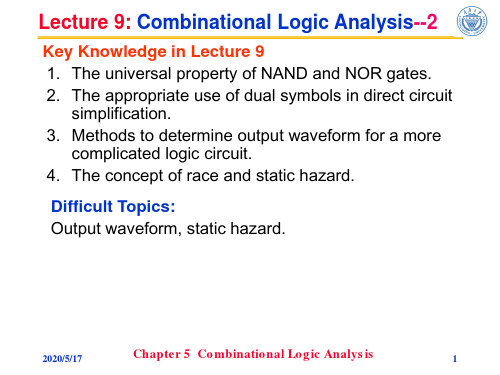

Chapter 5 Combinational Logic Analysis

8

Lecture 9: Combinational Logic Analysis--2

Development of the AND-OR Equivalency

注意:变换符号时从输 出往输入逆向操作。

2013-7-28

Test Your Understanding

Draw the timing diagram for the circuit below, showing the output of G1,G2 and G3 with the input waveforms A and B.

2013-7-28

Chapter 5 Combinational Logic Analysis

10

Lecture 9: Combinational Logic Analysis--2

Test Your Understanding

Directly simplify the logic diagram shown below using the appropriate dual symbols and develop the output expression for the circuit.

Chapter 5 Combinational Logic Analysis

9

Lecture 9: Combinational Logic Analysis--2

Illustration of the Use of Appropriate Dual Symbols

error

Start from output, and work backwards

Chapter 5 Combinational Logic Analysis

8

Lecture 9: Combinational Logic Analysis--2

Development of the AND-OR Equivalency

注意:变换符号时从输 出往输入逆向操作。

2013-7-28

Test Your Understanding

Draw the timing diagram for the circuit below, showing the output of G1,G2 and G3 with the input waveforms A and B.

2013-7-28

Chapter 5 Combinational Logic Analysis

10

Lecture 9: Combinational Logic Analysis--2

Test Your Understanding

Directly simplify the logic diagram shown below using the appropriate dual symbols and develop the output expression for the circuit.

Chapter 5 Combinational Logic Analysis

9

Lecture 9: Combinational Logic Analysis--2

Illustration of the Use of Appropriate Dual Symbols

error

Start from output, and work backwards

《数字电子技术 》课件第9章

2. 实训设备: 万用表, 示波器, 信号源, 直流电源。 实训器件: 面包板一块, DAC0832一片, 运算放大 器741一片, 计数器74LS161两片,导线若干。

3. 实训电路图如图9.1所示。

图 9.1 实训9电路图

4. 1) 查集成电路手册, 了解74LS161、 DAC0832和741的 功能, 确定74LS161、 DAC0832的管脚排列, 了解各管脚 的功能。 2) 按图9.1在实验板上安装好实验电路, 检查电路连接, 确认无误后再接电源。 注意不要将引脚接错。

然后SAR继续令B2为1, 连同第一次比较结果, 经 DAC转换再同模拟输入比较, 并根据比较结果, 决定B2在 寄存器中的取舍。

图9.8 为上述转换过程的时序波形。

图 9.8 四位逐次比较型ADC转换时序波形

2. 间接ADC 1) 图9.9为双积分型ADC的电路图, 该电路由运算放大器 C构成的积分器、 检零比较器C1、时钟输入控制门G、 定 时器和计数器等组成。 下面分别介绍它们的功能。

图 9.5 采样保持电路及波形

2. 采样保持电路的输出, 即量化编码的输入仍然是模拟 量, 它可取模拟输入范围里的任何值。 如果输出的数字量 是3位二进制数, 则仅可取000~111 8种可能值, 因此用数 字量表示模拟量时, 需先将采样电平归一化为与之接近的 离散数字电平, 这个过程称作量化。

9.1.2 A/D转换器的类型

1. 直接ADC 1) 并行ADC 图9.6是输出为三位的并行A/D转换的原理电路。 8个电 阻将参考电压分成8个等级, 其中7个等级的电压分别作为7 个比较器的比较电平。

图 9.6 三位并行A/D转换原理电路

比较器的输出状态由D触发器存储, 并送给编码器, 经过编码器编码得到数字输出量。 表9.1为该电路的转换真 值表。

3. 实训电路图如图9.1所示。

图 9.1 实训9电路图

4. 1) 查集成电路手册, 了解74LS161、 DAC0832和741的 功能, 确定74LS161、 DAC0832的管脚排列, 了解各管脚 的功能。 2) 按图9.1在实验板上安装好实验电路, 检查电路连接, 确认无误后再接电源。 注意不要将引脚接错。

然后SAR继续令B2为1, 连同第一次比较结果, 经 DAC转换再同模拟输入比较, 并根据比较结果, 决定B2在 寄存器中的取舍。

图9.8 为上述转换过程的时序波形。

图 9.8 四位逐次比较型ADC转换时序波形

2. 间接ADC 1) 图9.9为双积分型ADC的电路图, 该电路由运算放大器 C构成的积分器、 检零比较器C1、时钟输入控制门G、 定 时器和计数器等组成。 下面分别介绍它们的功能。

图 9.5 采样保持电路及波形

2. 采样保持电路的输出, 即量化编码的输入仍然是模拟 量, 它可取模拟输入范围里的任何值。 如果输出的数字量 是3位二进制数, 则仅可取000~111 8种可能值, 因此用数 字量表示模拟量时, 需先将采样电平归一化为与之接近的 离散数字电平, 这个过程称作量化。

9.1.2 A/D转换器的类型

1. 直接ADC 1) 并行ADC 图9.6是输出为三位的并行A/D转换的原理电路。 8个电 阻将参考电压分成8个等级, 其中7个等级的电压分别作为7 个比较器的比较电平。

图 9.6 三位并行A/D转换原理电路

比较器的输出状态由D触发器存储, 并送给编码器, 经过编码器编码得到数字输出量。 表9.1为该电路的转换真 值表。

《数字电子技术》课件第九章

图中W0~W3四条字线分别选择存储矩阵中的四个字, 每个字存放四位信息。 制作时, 若在某个字的某一位存入 “1”, 则在该字的字线Wi与位线Dj之间接入二极管; 反之, 就不接二极管。

图 9-2 二极管ROM结构图

读出数据时, 首先输入地址码, 同时输出缓冲级三态 控制端, 使输出缓冲级工作, 则在数据输出端D3~D0可以 获得该地址对应字中所存储的数据。 例如, 当A1A0=00时, W0=1, W1=W2=W3=0, 所以W0被选中, 读出W0对应字中 的数据D3D2D1D0=1100。 当A1A0为01、 10、 11时, 依次读 出的数据是1001、 1010、 1101。 该ROM存储的数据如表 9-1 所示。

如果浮栅Gf上积累了电子, 则使该MOS管的开启电压 变得很高。 此时给控制栅(接在地址选择线上)加+5 V电压时, 该MOS管仍不能导通, 相当于存储了“0”; 反之, 若浮栅 Gf上没有积累电子, MOS管的开启电压较低, 因而当该管 的控制栅被地址选中后, 该管导通, 相当于存储了 “1”。 可见, SIMOS管是利用浮栅是否积累负电荷来表示 信息的。 这种EPROM出厂时为全“1”, 即浮栅上无电子积 累, 用户可根据需要写“0”。

9.1.2 ROM

例如,在表9 -1 中,将输入地址A1A0视为输入变量, 而将D3、D2、D1、D0视为一组输出逻辑变量,则D3、D2、 D1、 D0就是A1、A0的一组逻辑函数。

D3 A1 A0 A1A0 A1 A1 A1A0 m0 m1 m2 m3 D2 A1 A0 A1A0 m0 m3 D1 A1A0 m2 D0 A1A0 A1A0 m1 m3

动态MOS存储单元有四管电路、 三管电路和单管电

路等。 四管和三管电路比单管电路复杂, 但外围电路简单,

图 9-2 二极管ROM结构图

读出数据时, 首先输入地址码, 同时输出缓冲级三态 控制端, 使输出缓冲级工作, 则在数据输出端D3~D0可以 获得该地址对应字中所存储的数据。 例如, 当A1A0=00时, W0=1, W1=W2=W3=0, 所以W0被选中, 读出W0对应字中 的数据D3D2D1D0=1100。 当A1A0为01、 10、 11时, 依次读 出的数据是1001、 1010、 1101。 该ROM存储的数据如表 9-1 所示。

如果浮栅Gf上积累了电子, 则使该MOS管的开启电压 变得很高。 此时给控制栅(接在地址选择线上)加+5 V电压时, 该MOS管仍不能导通, 相当于存储了“0”; 反之, 若浮栅 Gf上没有积累电子, MOS管的开启电压较低, 因而当该管 的控制栅被地址选中后, 该管导通, 相当于存储了 “1”。 可见, SIMOS管是利用浮栅是否积累负电荷来表示 信息的。 这种EPROM出厂时为全“1”, 即浮栅上无电子积 累, 用户可根据需要写“0”。

9.1.2 ROM

例如,在表9 -1 中,将输入地址A1A0视为输入变量, 而将D3、D2、D1、D0视为一组输出逻辑变量,则D3、D2、 D1、 D0就是A1、A0的一组逻辑函数。

D3 A1 A0 A1A0 A1 A1 A1A0 m0 m1 m2 m3 D2 A1 A0 A1A0 m0 m3 D1 A1A0 m2 D0 A1A0 A1A0 m1 m3

动态MOS存储单元有四管电路、 三管电路和单管电

路等。 四管和三管电路比单管电路复杂, 但外围电路简单,

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Latches are similar to flip-flops because they are bistable devices.

CHAPTER 7

Sec.7.1 Latches

It has two stable states that can voluntarily maintain, used to express the logical condition 0 and 1, or binary number 0 and 1.

CHAPTER 7

Sec.7.1 Latches

The S-R (Set-Reset) Latch

Example 7-1 If the S and R waveform in Figure 7-5(a) are applied to the inputs of the latch in Figure 7-4(b), determine the form that will be observed on the Q output. (Q is initially LOW)

Sec.7.1 Latches

The S-R (Set-Reset) Latch

CHAPTER 7

Sec.7.1 Latches

The S-R (Set-Reset) Latch

Inputs SR 11

Comments

NC NC No change. Latch remains in

The 74LS279 is a quad S-R latch. Two of the latches has two S inputs.

CHAPTER 7

Sec.7.1 Latches

The Gated S-R Latch

A gated latch requires an enable input, EN ( G is also used to designate an enable input).

present state.

1

0 Latch Set

0

1 Latch Reset

1

1 Invalid condition

CHAPTER 7

Sec.7.1 Latches

The S-R (Set-Reset) Latch

Figure 7-4 Logic symbols for the S-R and S- R latch.

CHAPTER 7

Sec.7.1 Latches

The Gated S-R Latch

Example 7-2 Determine the Q output of a gated S-R latch.

CHAPTER 7

Sec.7.1 Latches

The Gated D Latch

D latch has only one input in addition to EN, this input is called the D (data) input.

CHAPTER 7

Sec.7.1 Latches

The Gated D Latch

Example 7-3 Determine the Q output waveform of the gated D latch.

CHAPTER 7

Sec.7.1 Latches

The 74LS75 D Latch

CHAPTER 7

Sec.7.1 Latches

The S-R (Set-Reset) Latch

CHAPTER 7

Sec.7.1 Latches

The S-R (Set-Reset) Latch

Negative-OR equivalent of the NAND gate S-R latch

CHAPTER 7

Sec.7.1 Latches

The latch is a type of temporary storage device that has two stable states (bistable) and is normally placed in a category separate from that of flip-flops.

CHAPTER 7

Sec.7.1 Latches

The S-R (Set-Reset) Latch

Application The Latch as a Contact-Bounce Eliminator

CHAPTER 7

Sec.7.1 Latches

The 74LS279 Set-Reset Latch

May set 1 or 0 state according to the different input signal.

CHAPTER 7

Sec.7.1 Latches

The S-R (Set-Reset) Latch

A latch is a type of bistable logic device. A active-HIGH input S-R latch is formed with two cross-coupled NOR gates. An active-LOW input S-R latch is formed with two cross-coupled NAND gates.

Review

• Demultiplexer • Parity Generators / Checkers

Chapter 7 Latches, Flip-Flops, and Timers

Main Contents

• Latches • Edge-Triggered Flip-Flop • Flip-Flop Applications • One-Shots • The 555 Timer

74LS75 is a gated D latch, has four D latches.

CHAPTER 7

Sec.7.2 Edge-Triggered Flip-Flops

Flip-flops are synchronous bistate devices. The output changes state only at a specified point on the triggering input called the clock (CLK), which is designated as control input.

CHAPTER 7

Sec.7.1 Latches

It has two stable states that can voluntarily maintain, used to express the logical condition 0 and 1, or binary number 0 and 1.

CHAPTER 7

Sec.7.1 Latches

The S-R (Set-Reset) Latch

Example 7-1 If the S and R waveform in Figure 7-5(a) are applied to the inputs of the latch in Figure 7-4(b), determine the form that will be observed on the Q output. (Q is initially LOW)

Sec.7.1 Latches

The S-R (Set-Reset) Latch

CHAPTER 7

Sec.7.1 Latches

The S-R (Set-Reset) Latch

Inputs SR 11

Comments

NC NC No change. Latch remains in

The 74LS279 is a quad S-R latch. Two of the latches has two S inputs.

CHAPTER 7

Sec.7.1 Latches

The Gated S-R Latch

A gated latch requires an enable input, EN ( G is also used to designate an enable input).

present state.

1

0 Latch Set

0

1 Latch Reset

1

1 Invalid condition

CHAPTER 7

Sec.7.1 Latches

The S-R (Set-Reset) Latch

Figure 7-4 Logic symbols for the S-R and S- R latch.

CHAPTER 7

Sec.7.1 Latches

The Gated S-R Latch

Example 7-2 Determine the Q output of a gated S-R latch.

CHAPTER 7

Sec.7.1 Latches

The Gated D Latch

D latch has only one input in addition to EN, this input is called the D (data) input.

CHAPTER 7

Sec.7.1 Latches

The Gated D Latch

Example 7-3 Determine the Q output waveform of the gated D latch.

CHAPTER 7

Sec.7.1 Latches

The 74LS75 D Latch

CHAPTER 7

Sec.7.1 Latches

The S-R (Set-Reset) Latch

CHAPTER 7

Sec.7.1 Latches

The S-R (Set-Reset) Latch

Negative-OR equivalent of the NAND gate S-R latch

CHAPTER 7

Sec.7.1 Latches

The latch is a type of temporary storage device that has two stable states (bistable) and is normally placed in a category separate from that of flip-flops.

CHAPTER 7

Sec.7.1 Latches

The S-R (Set-Reset) Latch

Application The Latch as a Contact-Bounce Eliminator

CHAPTER 7

Sec.7.1 Latches

The 74LS279 Set-Reset Latch

May set 1 or 0 state according to the different input signal.

CHAPTER 7

Sec.7.1 Latches

The S-R (Set-Reset) Latch

A latch is a type of bistable logic device. A active-HIGH input S-R latch is formed with two cross-coupled NOR gates. An active-LOW input S-R latch is formed with two cross-coupled NAND gates.

Review

• Demultiplexer • Parity Generators / Checkers

Chapter 7 Latches, Flip-Flops, and Timers

Main Contents

• Latches • Edge-Triggered Flip-Flop • Flip-Flop Applications • One-Shots • The 555 Timer

74LS75 is a gated D latch, has four D latches.

CHAPTER 7

Sec.7.2 Edge-Triggered Flip-Flops

Flip-flops are synchronous bistate devices. The output changes state only at a specified point on the triggering input called the clock (CLK), which is designated as control input.