数字基带信号传输码型发生器的设计

数字基带传输常用码型

双相码:又称为分相码或曼彻斯特码。在 曼彻斯特编码中,每个比特中间引入跳变 来同时代表不同数值和同步信息。一个负 电平到正电平的跳变代表0,而一个正电平 到负电平的跳变则代表1。通过这种跳变使 曼彻斯特编码获得了同步信息和数字编码。 特点:只有两个电平;有足够的定时信息、 无直流、编码简单;缺点是带宽大

CMI——反转码

编码: “1”交替用“11”和“00” “0”用“01” 例: 1 1 0 1 0 0 1 0 11 00 01 11 01 01 00 01 特点: 1) 有较多的电平跃变,定时信息丰富 2) 具有一定的检错能力 3) 是CCITT推荐的PCM接口码型

Miller(密勒码/延迟调制码)

编码: “1”用码元持续中心点跃变表示, 即:01或10,但保持边沿不跃变 单个0:不跃变,且相邻码元边界也不跃变 “0” 00 例: 两个0:第2个0边界跃变,即: 或11

二进制

1

10 01

1

10 10

0

01 00

1

10 01

0

01 11

0

01 00

1

10 01

0

01 11

双相码

密勒码

双相码 密勒码

三元码

三元码是指利用信号幅度的三种取值+1、0、 -1来表示二进制数“1”和“0”。

AMI码(传号交替反转码)

编码规则: (0称为空号,1称为传号) 0变为传输码0 1交替变为传输码+1、-1、+1、-1 例:1001100011→ +100-1+1000-1+1 特点: 1) 统计上无直流(+1-1交替)、低频成分小 2) 进行了二进制→三进制变化,即1B/1T码型 3) 编/译码电路简单 4) 便于观察误码(+1、-1不交替) 5) 缺点:可能出现长的0串,提取定时信号困难

数字基带信号HDB3码的编码器设计与建模

课程设计任务书学生:专业班级:指导教师:工作单位:题目:数字基带信号HDB3码的编码器设计与建模初始条件:(1)MAX PLUSII 10.02 以上版本软件;(2)课程设计辅导书:《通信原理课程设计指导》(3)先修课程:数字电子技术、模拟电子技术、电子设计EDA、通信原理。

要求完成的主要任务:(包括课程设计工作量及其技术要求,以及说明书撰写等具体要求)(1)课程设计时间:1周;(2)课程设计题目:根据指导老师给定的六套题目选择其中二套完成;(3)本课程设计统一技术要求:按照要求对选定的设计题目进行逻辑分析,掌握HDB3码的编码原理,了解各模块电路的逻辑功能,设计通信系统框图,画出实现电路原理图,编写VHDL 语言程序,上机调试、仿真,记录实验结果波形,对实验结果进行分析;(4)课程设计说明书按学校“课程设计工作规”中的“统一书写格式”撰写,并标明参考文献至少5篇;(5)写出本次课程设计的心得体会(至少500字)。

时间安排:第19周参考文献:江国强.EDA技术与应用. :电子工业,2010John G. Proakis.Digital Communications. :电子工业,2011指导教师签名:年月日系主任(或责任教师)签名:年月日摘要本课程设计概括了HDB3数字编码器的研究背景、意义,同时对EDA技术和编码技术作了简要的说明。

设计方面包括规划基于VHDL的HDB3编码器设计的总体方案;基于VHDL的HDB3编码器的软件实现。

其中HDB3码的编码程序设计是在QuartusⅡ软件环境下进行的,首先在QuartusⅡ软件环境下建立一个工程,工程名和程序的实体名一致,并将其作为该工程的设计文件。

然后在VHDL文本编辑窗中输入设计的VHDL源程序,进行编译。

程序编译成功后要进行时序仿真,这一部分同样是在QuartusⅡ软件环境下完成的。

关键词:HDB3;建模;VHDL;编码;QUARTUSⅡ目录1 Quartus Ⅱ简介 (1)2 VHDL语言的介绍 (3)3 HDB3码编码器的建模与实现 (4)3.1 HDB3码的编码规则 (4)3.2 基于VHDL的编码器的建模及实现 (5)3.2.1 编码器的VHDL建模 (5)3.2.2 基于VHDL编码器的实现 (6)3.3编码中单/双极性转换的实现 (8)3.3.1单/双极性转换的流程图 (8)4 HDB3码编码器完整源程序 (9)5 HDB3码编码器的波形仿真及分析 (13)6 总结与心得 (15)7 参考文献 (16)1 Quartus Ⅱ简介Quartus II 是Altera公司的综合性PLD/FPGA开发软件,支持原理图、VHDL、VerilogHDL以及AHDL(Altera Hardware Description Language)等多种设计输入形式,嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整PLD设计流程。

数字信号基带传输系统设计

目录1. 题目 (1)2. 程序总体设计方案、思路 (1)3. 程序主要功能模块实现 (1)4. 程序调试结果及分析 (2)4.1. 信息论的基本计算 (2)4.1.1. 编程实现信源平均信息量的计算(以高斯分布的信源为例) (2)4.1.2. 编程实现信源编码过程(以Huffman编码为例) (3)4.1.3. 编程实现离散信道容量的计算(以输入符号等概分布为例) (3)4.2. 数字信号基带传输系统设计 (4)4.2.1. 单极性非归零码 (4)4.2.2. 单极性归零码 (4)4.2.3. 双极性非归零码 (5)4.2.4. 双极性归零码 (5)4.2.5. 曼彻斯特编码 (6)4.2.6. 密勒码 (6)4.2.7. AMI码 (7)4.2.8. HDB3码 (7)4.2.9. 功率谱分布 (8)4.2.10. 二电平误码率 (8)4.2.11. 多电平误码率 (9)5. 设计总结 (9)6. 源程序 (9)7. 课程设计参考资料..................................... 错误!未定义书签。

8. 评分表............................................... 错误!未定义书签。

1.题目(1)信息论的基本计算(2)数字信号基带传输系统设计2.程序总体设计方案、思路对于题目一首先编程实现信源平均信息量的计算(以高斯分布的信源为例);再编程实现离散信道容量的计算(以输入符号等概分布为例);最后完成编程实现信源编码过程(以Huffman编码为例);对于题目二编程实现常见基带信号的波形、码型转换,包括:单/双极性、非归码,并绘出每种波形、码零/归零码、数字双相码(曼彻斯特码)、密勒码、AMI码、HDB3型的功率谱分布,;并编程实现基带传输系统的误码率计算,包括:二电平和多电平编码的误码率计算(两层含义:一,按公式得到;二,自己做的误码率可以得到。

第五章数字基带传输系统精品PPT课件

6.

当多于一个二进制符号对应一个脉冲的时候, 波形统称为多电平波形或多值波形。

例如,若令两个二进制符号00对应+3E,01 对应+E,10对应-E,11对应-3E,则所得波形 为4电平波形,如图 5 -3(f)所示。

信道:允许基带信号通过的媒质。通常 为有线信道, 如市话电缆、架空明线等。 信道的传输特性通常不满足无失真传输 条件,另外还会进入噪声。 在通信系统 的分析中,常常把噪声等效集中在信道 中引入。

接收滤波器:主要作用是滤除带外噪声, 使输出的基带波形有利于抽样判决。

抽样判决器:在传输特性不理想和噪声 的背景下,在规定时刻(由位定时脉冲 控制)对接收滤波器的输出波形进行抽 样判决,用来恢复与再生基带信号。

由于这种波形的一个脉冲可以代表多个二进 制符号, 故在高数据速率传输系统中,采用这 种信号形式是适宜的。

数字基带信号的数学表示

消息代码的电波形并非一定是矩形的,还 可以是其他形式。但无论采用什么形式的波形, 数字基带信号都可用数学表达式表示。若数字 基带信号中各码元波形相同而取值不同,则可 用

s(t) ang(t nTS)

n

表示。式中,an是第n个信息符号所对应的电平 值(0、1或-1、1等);Ts为码元间隔(周期); g(t)为某种脉冲波形。

对于二进制代码序列,若令g1(t)代表 “0”,g2(t)代表“1”,则 g(tnTS)gg12((ttnnTSTS))( (出 出现 现01) ) 符 符号 号

5.2.2 基带信号的频谱特性

同步 提取

图 5 -1数字基带传输系统

信道信号形成器:基带传输系统的输入是 由终端设备或编码器产生的脉冲序列,它 不一定适合直接在信道中传输。

基带传输码型课程设计

基带传输码型课程设计一、课程目标知识目标:1. 学生理解基带传输的基本概念,掌握不同类型的基带传输码型(如NRZ、RZ、Manchester编码等)的特点及适用场景。

2. 学生能够描述数字信号在基带传输过程中的信号波形,解释码型设计对信号传输性能的影响。

3. 学生掌握基带传输中码间串扰的概念,并能够分析码间串扰产生的原因及其对传输质量的影响。

技能目标:1. 学生能够运用所学知识,针对特定传输场景选择合适的基带传输码型,并进行简单的码型设计。

2. 学生通过实例分析和问题解决,培养逻辑思维能力和实际操作技能,例如使用相关工具或软件模拟基带传输过程。

情感态度价值观目标:1. 培养学生对通信科学的兴趣,激发他们对信息技术发展的好奇心和探索欲。

2. 强化学生合作学习的意识,通过小组讨论和分享,让学生认识到团队协作的重要性。

3. 增强学生面对工程问题的责任感,教育他们理解在码型设计时考虑实际应用需求和社会效益的重要性。

课程性质分析:本课程为电子信息学科方向的基础课程,旨在帮助学生建立扎实的通信原理基础,为后续专业课程学习打下坚实基础。

学生特点分析:考虑到学生所在年级(假定高中二年级),他们已经具备一定的物理基础和数学逻辑能力,但可能缺乏将理论知识应用于实际问题的经验。

教学要求:1. 教学内容要与实际应用紧密结合,提高课程的实用性和针对性。

2. 教学过程中注重启发式教学,鼓励学生主动思考,提高解决问题的能力。

3. 强化实践教学环节,通过案例分析和模拟实验,加深学生对基带传输码型的理解和应用。

二、教学内容1. 基带传输基本概念:介绍基带传输的定义,对比基带传输与频带传输的差异,阐述基带传输的特点和限制。

教材章节:第一章第二节2. 常见基带传输码型:详细讲解NRZ、RZ、Manchester和DiffManchester 等码型的编码原理、波形特点和应用场景。

教材章节:第二章第一、二节3. 码型设计原则:分析基带传输码型的设计原则,包括码间串扰的抑制、信号同步和传输效率等方面的考虑。

数字基带传输系统仿真与设计方案

一、课程题目数字基带传输系统:欲传送的01比特流+码型变换(HDB3码)+基带成型网络(采用升余弦滚降系统)+信道+码型反变换+01比特流。

二、设计要求1.完成一个题目。

2.对通信系统有整体的较深入的理解。

3.提出仿真方案。

4.完成仿真软件的编制。

5.仿真软件的演示。

6.提交详细的设计报告。

三、设计目的1.综合应用《Matlab编程与系统仿真》、《信号与系统》、《现代通信原理》等多门课程知识,使学生建立通信系统的整体概念。

2.培养学生系统设计与系统开发的思想。

3.培养学生利用软件进行通信仿真的能力。

4.培养学生独立动手完成课题设计项目的能力。

5.培养学生查找相关资料的能力。

四、实验条件计算机、Matlab软件、相关资料。

五﹑系统设计方案数字基带传输系统:(1)概念:未经调制的数字信号所占据的频谱是从零频或者很低频率开始,称为数字基带信号,不经载波调制而直接传输数字基带信号的系统,称为数字基带传输系统。

(2)数字基带传输的研究的意义:第一:在利用对称电缆构成的近程数据通信系统中广泛采用这种传输方式。

第二:数字基带传输方式迅速发展,用于低速或高速数据传输。

第三:基带传输系统的许多问题也是带通传输系统必须考虑的问题。

第四:任一个线性调制的带通传输系统,可以等效为一个基带传输系统。

(3)对传输码型的要求:①不含直流分量且低频分量尽量少。

②应含有丰富的定时信息,以便于从接受码流中提取定时信号。

③功率谱的主瓣宽度窄,以节省传输频带。

④不受信息源统计特性的影响,即能适应于信息源的变化。

⑤具有内在的检错能力,即码型应具有一定的规律性,以便宏观监测。

⑥编译码简单,已降低通信延时和成本。

(4)基带传输常用码型:AMI码(传号交替反转码)、HDB3码(三阶高密度双极性码)、双相码、差分双相码、密勒码、CMI码(传号反转码)、块编码等。

(5)其中本次设计采用的HDB3码。

a.HDB3码编码规则:①1——交替变换为+1,-1②0——连0小于等于3则用0电平表示,大于3则用特定码组替换B 0 0 V 或 0 0 0 V③任意两个V之间B的个数为奇数。

设计报告--013---CDMA数字基带发送系统的FPGA设计与实现

CDMA数字基带发送系统的FPGA设计与实现FPGA是电子设计领域中最具活力和发展前途的一项技术,它的影响丝毫不亚于70年代单片机的发明和使用。

可以毫不夸张的讲,FPGA能完成任何数字器件的功能。

在PCB完成以后,还可以利用FPGA的在线修改能力,随时修改设计而不必改动硬件电路。

使用FPGA来开发数字电路,可以大大缩短设计时间,减少PCB面积,提高系统的可靠性。

FPGA的这些优点使得FPGA技术在90年代以后得到飞速的发展,同时也大大推动了EDA软件和硬件描述语言的进步。

本设计主要利用了FPGA及Verilog HDL语言来设计CDMA数字基带发送接收系统[27,28]。

一.FPGA通信系统设计的注意点对于通信系统的建模,除了外围的模拟电路的设计是整个大系统需要考虑外,更重要的是针对纯数字部分的输入、输出接口信号的要求,进行细致的研究。

对于数字通信系统,对于不同的Verilog HDL来建模有着不同的效果。

一般对于选择什么方法来进行数字通信的建模,从以下几个方面讨论研究[27]:·可行性的影响对于以FPGA通用芯片为目标器件的建模和设计,受到输入信号性质的限制,对于一些速度要求较高的通信系统,由于现行的FPGA目标器件的限制,无法使用。

因此对于通信系统的Verilog HDL建模的可行性应在设计系统方案做充分考虑。

·可靠性分析对于通信系统来说,实现系统的可靠性指标是Verilog HDL建模的难点,这一点与实现硬件电路是相似的,用硬件描述语言,实现系统功能,有许多方法,实现建模的方法也可以不同,有时不同的建模风格和方式,可以得到相同的设计结果和相近的可靠性能,同时,对于组合逻辑电路来说,设计的可靠性,还要考虑组合逻辑电路的竞争和冒险现象和硬件延时问题。

·效率的影响系统效率的因素包括芯片资源的优化,软件程序运行的速度等。

从软件设计方面考虑,采用并行方式比串行运行方式运行速率高。

数字基带传输系统设计

论文题目:数字基带传输系统设计 学 院:信息工程学院

专 业 班 级 : 电 信 092 班 指导老师:张瑾 学生姓名:叶园园 王建峰 陈鑫 吴涛 李文科

完成日期: 2012 年 10 月 5 日

研究报告

1、项目题目

数字基带传输系统设计

2、项目概述

数字通信的基带传输方式是数字通信最基本的传输方式, 随着数字通信技术 的发展, 这种方式也有迅速发展的趋势。由于理论上已经证明任何一个采用线性 调制的频带传输系统, 总可以由一个等效的基带传输系统替代,所以对基带传输 系统的研究也将迁移到频带传输系统的研究中,因而具有普遍意义。 本项目选用 Altera 公司的 EP2C5T144C8N 芯片作为处理器, 来实现的数字基 带传输系统。 使其具有数字基带信号发生、 多种编码输出、 信道传输 (模拟加噪) 及解码恢复等功能。其中基带传输码型的编码与解码以及信道噪声的模拟,用 VHDL 硬件描述语言编程实现。单/双极性变换、噪声叠加与信道传输幅频特性的 模拟, 将分别采用中规模数字集成电路和模拟电路实现。系统将具有工作可靠性 高、可在线修改设计等优点。library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity hdb3_coding is port( data_in :in std_logic; clock :in std_logic; data_out :out std_logic_vector(1 downto 0)); end hdb3_coding; architecture rtl of hdb3_coding is signal reg :std_logic_vector(3 downto 0); signal parity :std_logic; --记录破坏点间 1 码个数的奇偶性 signal judge_v :std_logic; --判断是否有破坏符 signal grant_cnt:std_logic; --允许开始计算破坏点间的 1 码个数 signal last_sign:std_logic; --上一输出的符号 signal v_cnt :std_logic_vector(2 downto 0);--v 点位置跟踪计数器 begin process(clock) -- 移位寄存器 ,插 V begin if rising_edge(clock) then if data_in='0' and reg(3 downto 1)="000" then reg<=('1' & reg(3 downto 1)); judge_v<='1'; grant_cnt<='1'; else reg<=data_in & reg(3 downto 1); judge_v<='0'; grant_cnt<='0'; end if; end if; end process; process(clock) --计数 begin if rising_edge(clock) then if grant_cnt='1' and data_in='0' then parity<='0'; elsif grant_cnt='1' and data_in='1' then parity<='1'; elsif data_in='1' then parity<=not parity; end if; end if; end process; process(clock) --V 点跟踪 begin if rising_edge(clock) then

数字基带信号传输码型发生器的设计

数字基带信号传输码型发⽣器的设计数字基带信号发⽣器的设计摘要设计⼀个基于FPGA的数字基带信号发⽣器,⾸先简要介绍了单极性⾮归零码、双极性⾮归零码、单极性归零码、双极性归零码、差分码、交替极性码、分相码、传号反转码等基带码的基本特点,然后根据码型转换原理设计发⽣器模块。

由于EDA技术可以简化电路,集成多块芯⽚,减⼩电路体积,所以程序采⽤VHDL进⾏描述,并⽤quartusII软件仿真实现所有功能,最后将功能集成到FPGA上,并设计电路、制作实物,产⽣的基带码稳定、可靠,可满⾜不同数字基带系统传输需要。

关键词:数字基带码;EDA;VHDL;PCB;FPGAAbstractFPGA-based design a letter-number generator with,first of all we briefly introduce unipolar NRZ code,bipolar NRZ,Unipolar zero yards code,bipolar zero yards code,differential code, alternating polarity code,phase code,code-reversal,and third-order high-density bipolar codes etc.Then we design generator module under the code-conversion design principles.As EDA technology can make circuit simple,integrate multiple chips,reduce the size of circuits,so we take advantage of VHDL to describe it and use quartusII software to simulate.Finally we integrate all the fetures into the FPGA,and design circuit to generate stable and reliable base-band code to meet the different base-band digital transmission system needs.Key words:digital base-band code;EDA;VHDL;PCB;FPGA⽬录摘要 (1)Abstract (2)1前⾔ (5)2数字基带信号 (6)2.1数字基带信号的码型设计原则[2] (6)2.2⾮归零码(NRZ码)[1][3] (6)2.2.1单极性 (6)2.2.2双极性 (7)2.3归零码(RZ码)[1][3] (7)2.3.1单极性 (7)2.3.2双极性 (7)2.4差分码[4] (8)2.5交替极性码(AMI码)[4] (8)2.6分相码(曼彻斯特码)[5] (9)2.7传号反转码(CMI码)[4][6] (9)3EDA概述 (11)3.1硬件描述语⾔[8] (11)3.1.1Verilog-HDL (12)3.1.2VHDL (12)3.2可编程逻辑器件[11] (13)3.3EDA软件[12] (14)4基带码发⽣器的设计原理 (15)4.1基带码发⽣器的原理框图 (15)4.2码型转换原理 (16)5软件设计与仿真 (17)5.1VHDL程序设计[13][14] (17)5.2软件仿真 (19)5.2.1编辑和输⼊设计⽂件 (19)5.2.2创建⼯程 (20)5.2.3全程综合与编译 (22)5.2.4仿真测试 (22)6仿真结果及分析 (23)6.1器件仿真结果 (23)6.2波形仿真结果 (23)6.2.1NRZ的仿真波形 (23)6.2.2DRZ的仿真波形 (24)6.2.3CFM的仿真波形 (24)6.2.4CMI的仿真波形 (25)6.2.5FXM的仿真波形 (25)6.2.6SRZ的仿真波形 (25)6.2.7AMI的仿真波形 (26)6.2.8综合仿真波形 (26)7课设总结 (27)参考⽂献 (28)1前⾔近年来,随着⼤规模集成电路的出现,数字系统的设备复杂程度和技术难度降低,数字通信系统的主要缺点逐渐得到解决,因此数字传输⽅式⽇益受到欢迎。

数字基带信号的传输码型

基带数字信号的表示和传输图1-1:基带传输模型图1)信号形成器:产生适合于信道传输的基带信号波形。

2)信道:允许基带信号通过的媒介。

3)接收滤波器:用来接收信号,尽可能滤除信道噪声和其他干扰,对信道特性进行均衡,使输出的基带信号有利于判决。

4)抽样判决器:在传输特性不理想及噪声背景下,在规定时刻(由位定时脉冲控制)对将接收滤波器的输出波形进行抽样判决,以恢复或再生基带信号。

5)定时脉冲和同步提取:用来抽样的位定时脉冲依靠同步提取电路从接收信号中提取,位定时的准确性将直接影响判决效果。

2.常见的数字基带传输码型(1)AMIAMI(Alternative Mark Inversion)码的全称是传号交替反转码,其编码规则是三元码,“1”交替地变换为“+1”和“-1”,“0”保持不变采用归零码,脉冲宽度为码元宽度之半“0”,“1”不等概时也无直流;零频附近的低频分量小;频率集中在1/2码速处;编解码电路简单,且可以利用传号极性交替这一规律观察五码情况;整流成归零码之后,从中可以提取定时分量。

连0码多时,AMI 整流后的RZ 码连0也多,不利于提取高质量的位同步信号。

AMI 码的波形图如图1-6所示:1 011100000000111+1-1000000000+1+1+1-1-1二进制码二进制波形AMI 波形AMI 码图1-4 数字基带传输系统模型图1-6 AMI 码波形(2)HDB 3码HDB 3(3nd Order High Density Bipolar)码的全称是三阶高密度双极性码,是AMI 码的一种改进,保持了AMI 码的优点,使“0”连续不超过3个。

其编码规则为:“1”交替地变换为+1与-1的半占空归零码,但连“0”数小于或者等于3。

当连“0”数等于4时,用取代节“000V ”或者“B00V ”代替,“V ”的极性与前一个非零符号的极性相同(这破坏了极性交替的规则,所以V 又称为破坏脉冲);并要求相邻的“V ”也满足极性必须交替。

通信原理报告 数字基带信号HDB3码型编码转换实现

通信原理课程设计报告题目:数字基带信号HDB3码型编码转换实现专业班级:姓名:学号:指导教师:设计任务要求:仿真实现数字基带通信系统信源输入24位二进制序列产生HDB3码,通过高斯白噪声信道,接收端滤波、解码的时域图及频谱图。

以矩形波为例,要求实现输入24位二进制序列产生AMI码,HDB3码,接收端滤波、解码上述码型。

摘要HDB3码全称三阶高密度双极性码(英语:High Density Bipolar of Order 3,简称:HDB3码)是一种适用于基带传输的编码方式,它是为了克服AMI码的缺点而出现的,具有能量分散,抗破坏性强等特点。

HDB3码实行转换一般分为三个步骤,先将消息码转换AMI码然后加“V”,接着加“B”,这几部我们可以使用C语言进行编程实现。

为了实现HDB3码的编码与转换,同时加深对通信系统工作原理的了解,我们采用了MATLAB软件进行编码仿真,同时学习掌握MATLAB软件的基础使用。

关键词:AMI码;HDB3码;编码;解码;MATLAB;仿真目录1. 设计原理 (4)1.1 HDB3码的介绍 (4)1.2 HDB3码的编码转换规则 (5)1.3 HDB3码的解码转换规则 (5)1.4 HDB3码的软件程序设计 (6)2. MATLAB软件仿真结果及其分析 (10)2.1MATLAB软件的介绍 (10)2.2 仿真结果图示 (12)2.3 仿真结果分析 (15)3. 设计总结及心得体会 (22)4. 参考文献 (22)5. 致谢 (23)正文1.设计原理1.1 HDB3码的介绍HDB3码即三阶高密度双极性码(英语:High Density Bipolar of Order 3,简称:HDB3码)是一种适用于基带传输的编码方式,“三阶”通俗讲就是最多3个连0码元,“高密度双极性”就是没有直流分量,不会连续出现+1或-1,它是为了克服AMI码的缺点而出现的,具有能量分散,抗破坏性强等特点。

8.15数字基带信号传输码型发生器设计

5.差分码

差分码利用前后码元电平的相对极性变化来传送 信息,又称为相对码。

这种传输码不是用脉冲本身的电平高低来表示二 进制代码的“1”码与“0”码,而是用脉冲波的电平 变化来表示码元的取值,即当码元的取值为“ 1” 时,脉冲波的电平变化一次;而当码元的取值为 “0”时,脉冲波的电平不变。

--分频计数器+1

if count_fri=8 then count_fri:=0;

--计数到8

if count_mov<16 then count_mov:=count_mov+1; --移位计数器+1

latch_sig:=latch_dat(15);

--二进制码高位移入latch_sig中

atch_dat:=latch_dat(14 downto 0)&'0';

由于这些优点,因此它是最常用的码型之一。

但当传输信息中存在长连“ 0”码的情况时,这种 传输码将会由于长时间不出现电平跳变,从而给 接收端在提取定时信号时带来困难。

AMI码在连0码过多时提取定时信号有困难。 这是因为在连0码时AMI输出均为零电平,连0码

这段时间内无法提取同步信号,而前面非连0码 时提取的位同步信号又不能保持足够的时间。 这是这种传输码的不足之处。

--基带码同步信号

variable count_fri : integer range 0 to 8; --分频计数器(码宽定义)

variable count_mov : integer range 0 to 16; --移位计数器

begin

if start='0' then latch_cnt:='0';

实验五 基带码型产生实验

实验五基带码型产生实验一、实验目的1、掌握基带传输码型的特点;2、掌握常用的基带传输码的产生方法;3、能用matlab编写程序产生一些常用的码型,如RZ、NRZ、AMI、Miller、双相码等。

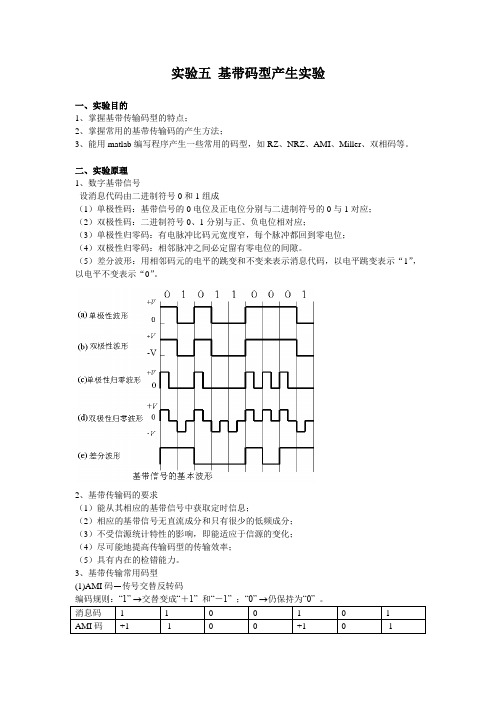

二、实验原理1、数字基带信号设消息代码由二进制符号0和1组成(1)单极性码:基带信号的0电位及正电位分别与二进制符号的0与1对应;(2)双极性码:二进制符号0、1分别与正、负电位相对应;(3)单极性归零码:有电脉冲比码元宽度窄,每个脉冲都回到零电位;(4)双极性归零码:相邻脉冲之间必定留有零电位的间隙。

(5)差分波形:用相邻码元的电平的跳变和不变来表示消息代码,以电平跳变表示“1”,以电平不变表示“0”。

2、基带传输码的要求(1)能从其相应的基带信号中获取定时信息;(2)相应的基带信号无直流成分和只有很少的低频成分;(3)不受信源统计特性的影响,即能适应于信源的变化;(4)尽可能地提高传输码型的传输效率;(5)具有内在的检错能力。

3、基带传输常用码型(1)AMI码-传号交替反转码编码规则:“1” →交替变成“+1”和“-1”;“0” →仍保持为“0”。

消息码 1 1 0 0 1 0 1AMI码+1 -1 0 0 +1 0 -1特点:无直流成分,且只有很少的低频成分,编码简单,提取定时信号困难。

(2)HDB3码-三阶高密度双极性码编码规则:先检查消息代码中的连0情况,当没有4个或4个以上连0时,按AMI码的编码原则;当有时则将每4个连0小段的第4个0变换成与前一个非0符号同极性的符号。

但这可能会破“环极性交替反转”的规律。

这个符号被称为破环符号,用V表示(即+1记为+V,-1记为-V)。

为使附加V符号后原码仍为无直流分量,还必须保证相邻V符号也极性交替。

这一点,当相邻V符号之间有奇数个非0符号时,是能保证的;当有偶数个非0符号时,则不能保证,这时再将该小段的第1个0变换成+B或-B,B符号的极性与前一个非0符号极性相反,并让后面的非0符号从V符号开始在交替变化。

构建数字基带传输课程设计

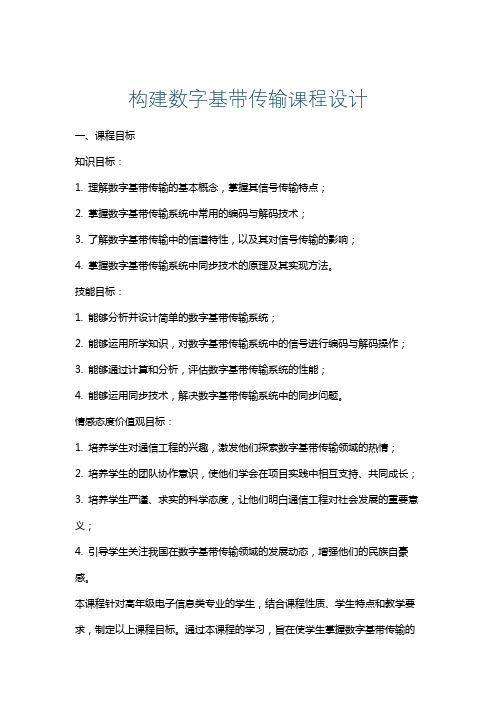

构建数字基带传输课程设计一、课程目标知识目标:1. 理解数字基带传输的基本概念,掌握其信号传输特点;2. 掌握数字基带传输系统中常用的编码与解码技术;3. 了解数字基带传输中的信道特性,以及其对信号传输的影响;4. 掌握数字基带传输系统中同步技术的原理及其实现方法。

技能目标:1. 能够分析并设计简单的数字基带传输系统;2. 能够运用所学知识,对数字基带传输系统中的信号进行编码与解码操作;3. 能够通过计算和分析,评估数字基带传输系统的性能;4. 能够运用同步技术,解决数字基带传输系统中的同步问题。

情感态度价值观目标:1. 培养学生对通信工程的兴趣,激发他们探索数字基带传输领域的热情;2. 培养学生的团队协作意识,使他们学会在项目实践中相互支持、共同成长;3. 培养学生严谨、求实的科学态度,让他们明白通信工程对社会发展的重要意义;4. 引导学生关注我国在数字基带传输领域的发展动态,增强他们的民族自豪感。

本课程针对高年级电子信息类专业的学生,结合课程性质、学生特点和教学要求,制定以上课程目标。

通过本课程的学习,旨在使学生掌握数字基带传输的基本理论和技术,具备一定的实际操作能力,为后续相关课程的学习和实际工程应用打下坚实基础。

同时,注重培养学生的情感态度和价值观,使他们成为具有创新精神和实践能力的优秀通信工程专业人才。

二、教学内容1. 数字基带传输基本概念:信号传输特性、传输系统模型、传输速率与带宽;2. 编码与解码技术:非归零编码、归零编码、双极性编码、差分编码、解码原理及实现;3. 信道特性:信道模型、信道噪声、信道容量、信道失真及其对信号传输的影响;4. 同步技术:时钟同步、载波同步、符号同步的原理及其在数字基带传输系统中的应用;5. 数字基带传输系统性能分析:误码率、眼图、系统性能评估方法;6. 数字基带传输系统设计:系统设计流程、仿真与实验。

教学内容依据课程目标,遵循科学性和系统性原则进行选择和组织。

通信原理概论实验 数字基带传输系统-数字基带信号的码型(一)

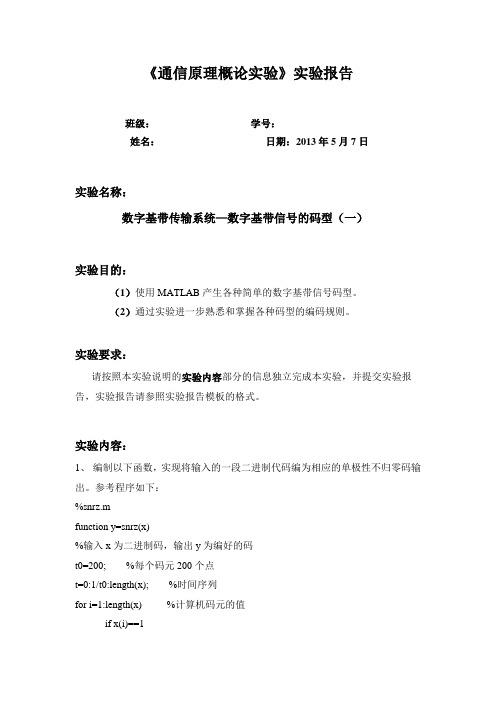

《通信原理概论实验》实验报告班级:学号:姓名:日期:2013年5月7日实验名称:数字基带传输系统—数字基带信号的码型(一)实验目的:(1)使用MATLAB产生各种简单的数字基带信号码型。

(2)通过实验进一步熟悉和掌握各种码型的编码规则。

实验要求:请按照本实验说明的实验内容部分的信息独立完成本实验,并提交实验报告,实验报告请参照实验报告模板的格式。

实验内容:1、编制以下函数,实现将输入的一段二进制代码编为相应的单极性不归零码输出。

参考程序如下:%snrz.mfunction y=snrz(x)%输入x为二进制码,输出y为编好的码t0=200; %每个码元200个点t=0:1/t0:length(x); %时间序列for i=1:length(x) %计算机码元的值if x(i)==1for j=1:t0%如果输入信息为1,码元对应的点值取1y((i-1)*t0+j)=1;end;elsefor j=1:t0%如果输入信息为0,码元对应的点值取0y((i-1)*t0+j)=0;endendendN=length(y);temp=y(N);y=[y,temp];plot(t,y);axis([0,i,-0.1,1.1]);title('单极性不归零码');说明:该函数编制好后,在MATLAB的命令窗口输入:x=[1 1 1 0 1 0 0 1 0 0 0 1 1 0]; %这个二进制序列可以任意修改snrz(x) %执行函数,输出显示对应的码型结果如图所示:2.编制另一个函数,用于产生双极性不归零码。

双极性不归零码的实现同单极性基本一样,只需将snrz.m中判断得到0信息后的语句“y((i-1)*t0+j)=0;”改为“y((i-1)*t0+j)=-1;”。

此外,双极性波形显示的时候,需要将“axis([0,i,-0.1,1.1]);”改为“axis([0,i,-1.1,1.1]);”3.编制以下函数,用于产生单极性归零码。

数字基带信号的码型设计原则

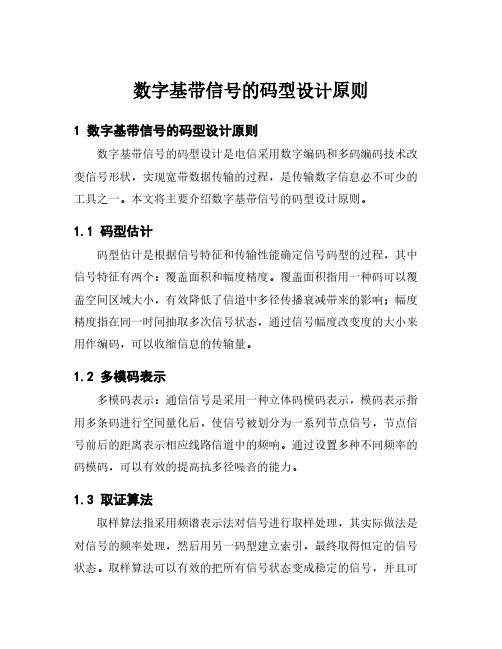

数字基带信号的码型设计原则1 数字基带信号的码型设计原则数字基带信号的码型设计是电信采用数字编码和多码编码技术改变信号形状,实现宽带数据传输的过程,是传输数字信息必不可少的工具之一。

本文将主要介绍数字基带信号的码型设计原则。

1.1 码型估计码型估计是根据信号特征和传输性能确定信号码型的过程,其中信号特征有两个:覆盖面积和幅度精度。

覆盖面积指用一种码可以覆盖空间区域大小,有效降低了信道中多径传播衰减带来的影响;幅度精度指在同一时间抽取多次信号状态,通过信号幅度改变度的大小来用作编码,可以收缩信息的传输量。

1.2 多模码表示多模码表示:通信信号是采用一种立体码模码表示,模码表示指用多条码进行空间量化后,使信号被划分为一系列节点信号,节点信号前后的距离表示相应线路信道中的频响。

通过设置多种不同频率的码模码,可以有效的提高抗多径噪音的能力。

1.3 取证算法取样算法指采用频谱表示法对信号进行取样处理,其实际做法是对信号的频率处理,然后用另一码型建立索引,最终取得恒定的信号状态。

取样算法可以有效的把所有信号状态变成稳定的信号,并且可以根据需要应用不同码型,实现实时测量和取样连续性,为系统决策提供依据。

1.4 信息编码信息编码是把信息用码型的变化来表示,其最大的特点是信息量很小,但是可以传输数据大量的信息。

主要码型有时间域编码、空间域编码和概率编码。

时间域编码把信息用时间序列来表示,是指以位宽和数据顺序来表示信息;空间域编码以信息的位置来表示,如信息在传输中被划分成几部分;而概率编码是把信息用概率来表示,它通过统计一些信息,然后根据这些计算出一个概率值,来表示信号的特征。

综上所述,数字基带信号的码型设计主要包括码型估计、多模码表示、取样算法和信息编码,是传输数字信息不可缺少的有效工具。

数字基带传输系统的FPGA设计与实现

数字基带传输系统的FPGA设计与实现作者:张水英, 金学波, 杜晶晶来源:《现代电子技术》2011年第01期摘要:为了提高系统的集成度和可靠性,降低功耗和成本,增强系统的灵活性,提出一种采用非常高速积体电路的硬件描述语言(VHDL语言)来设计数字基带传输系统的方法。

详细阐述数字基带传输系统中信号码型的设计原则,数字基带传输系统中信号编码原理和译码原理;采用硬件描述语言来设计数字基带信号编码器和译码器并进行仿真;采用原理图设计方法设计数字基带传输系统并仿真;整个系统的设计在QuartusⅡ平台上完成,并在Altera公司的ACEX1K-EP1K30TC144-1芯片上实现。

关键词:数字通信;基带传输系统; VHDL;FPGA中图分类号:TN914-34文献标识码:A文章编号:1004-373X(2011)01-0182-03Design and Implementation of FPGA for Digital Baseband Transmission SystemZHANG Shui-ying, JIN Xue-bo, DU Jing-jing(School of lnformatics & Electronics, Zhejiang Sci-Tech University, Hangzhou 310018, China)Abstract: In order to improve system integration degree and system reliability, reduce power consumption and cost, and improve system flexibility, a method to design digital baseband system with hardware description language (VHDL) adopting the very higt-speed integrated circuit is put forward. The design principle of signal pettern in digital baseband system, the encoding and decoding principles of signal in the digital baseband system are elaborated. The encoder and the decoder for digital baseband signal were designed and simulated with VHDL. The digital baseband system was designed and simulated with schematic diagram design method. The design of the whole system is completed on the platform of Quartus Ⅱ and implemented with ACEX1K-EP1K30TC144-1 of Altera.Keywords: digital communication; baseband transmission system; VHDL; FPGA0 引言现代通信系统中,数字通信系统所占的比例越来越大,系统的数字化、集成化是未来发展的方向。

数字基带传输系统的设计

目录第1章绪论 (1)1.1概述 (1)1.2 System View软件的介绍 (1)第2章数字基带传输系统 (3)2.1 数字基带信号 (3)2.2 数字基带传输 (3)2.3 数字基带传输系统 (4)2.4 数字基带传输的要求及常用码型 (5)第3章数字基带传输系统的设计及仿真 (6)3.1仿真模型框图设计 (6)3.2基带传输系统模型的仿真电路设计 (6)3.3数字基带传输系统的仿真与分析 (7)第4章总结 (11)参考文献 (12)第1章绪论1.1概述20世纪60年代出现了数字传输技术,它采用了数字信号来传递信息,从此通信进入了数字化时代。

目前,通信网已基本实现数字化,在我国公众通信网中传输的信号主要是数字信号。

数字通信技术的应用越来越广泛,例如数字移动通信、数字卫星通信、数字电视广播、数字光纤通信、数字微波通信、数字视频通信、多媒体通信等等。

数字通信系统主要的两种通信模式:数字频带传输通信系统,数字基带传输通信系统。

数字基带信号-指未经调制的数字信号,它所占据的频谱是从零频或很低频率开始的。

数字基带传输系统-指不经载波调制而直接传输数字基带信号的系统,常用于传输距离不太远的情况下。

研究数字基带传输系统的原因:实际中,基带传输不如频带传输应用广泛,但对基带传输的研究仍有非常重要的意义。

这是因为:第一,数字基带系统在近程数据通信系统中广泛采用;第二,数字基带系统的许多问题也是频带传输系统必须考虑的问题;第三,随着数字通信技术的发展,基带传输这种方式也有迅速发展的趋势,它不仅用于低速数据传输,而且还用于高速数据传输;第四,在理论上,任何一个线性调制的频带传输系统,总是可以有一个等效的基带载波调制系统所替代。

因此,很有必要对基带传输系统进行综合系统的分析。

1.2 System View软件的介绍System View是美国ELANIX公司推出的,基于Windows环境下运行的用于系统仿真分析的可视化软件工具,它使用功能模块(Token)去描述程序,无需与复杂的程序语言打交道,不用写一句代码即可完成各种系统的设计与仿真,快速地建立和修改系统、访问与调整参数,方便地加入注释。

数字基带传输系统课程设计(终稿)

数字基带传输系统课程设计(终稿)一、设计目的本课程设计旨在让学生深入理解数字基带传输系统的基本原理、组成结构和传输特性。

通过理论分析和实验操作,培养学生运用所学知识解决实际问题的能力,为后续学习和工作打下基础。

二、设计任务与要求1.设计任务设计一个简单的数字基带传输系统,包括信号生成、调制、传输和接收等环节。

具体要求如下:(1) 信号生成:采用随机二进制序列作为输入信号,信号速率不低于100kbps。

(2) 调制:采用基带调制技术,将二进制序列转换为适合在信道中传输的信号。

(3) 传输:通过有线或无线信道传输调制信号,确保信号在信道中稳定传输。

(4) 接收:在接收端对接收到的信号进行解调,恢复原始二进制序列。

2.设计要求(1) 理论分析:分析数字基带传输系统的基本原理、组成结构和传输特性,为系统设计提供理论支持。

(2) 方案设计:根据设计任务和要求,制定可行的设计方案。

(3) 硬件选择与搭建:根据设计方案,选择合适的硬件设备和电路元件,搭建数字基带传输系统硬件平台。

(4) 软件编程:编写控制程序和信号处理算法,实现数字基带传输系统的各项功能。

(5) 系统测试与优化:对所设计的系统进行测试和优化,确保系统性能达到设计要求。

三、设计步骤与内容1.理论分析(1) 学习数字基带传输系统的基本原理、组成结构和传输特性。

(2) 分析基带调制技术(如QPSK、QAM等)的原理、实现方法和性能特点。

(3) 研究信道噪声对数字基带传输系统性能的影响及应对措施。

2.方案设计(1) 确定系统总体架构:根据设计任务和要求,制定系统的总体架构方案,包括信号生成、调制、传输和接收等环节。

(2) 选择调制方式:根据实际情况选择适合的基带调制方式,如QPSK或QAM等。

(3) 确定信道类型:根据实际应用场景选择信道类型,如有线电缆、光纤或无线信道等。

(4) 制定硬件和软件设计方案:根据总体架构方案,设计硬件电路和软件程序,实现系统的各项功能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数字基带信号发生器的设计摘要设计一个基于FPGA的数字基带信号发生器,首先简要介绍了单极性非归零码、双极性非归零码、单极性归零码、双极性归零码、差分码、交替极性码、分相码、传号反转码等基带码的基本特点,然后根据码型转换原理设计发生器模块。

由于EDA技术可以简化电路,集成多块芯片,减小电路体积,所以程序采用VHDL进行描述,并用quartusII软件仿真实现所有功能,最后将功能集成到FPGA上,并设计电路、制作实物,产生的基带码稳定、可靠,可满足不同数字基带系统传输需要。

关键词:数字基带码;EDA;VHDL;PCB;FPGAAbstractFPGA-based design a letter-number generator with,first of all we briefly introduce unipolar NRZ code,bipolar NRZ,Unipolar zero yards code,bipolar zero yards code,differential code, alternating polarity code,phase code,code-reversal,and third-order high-density bipolar codes etc.Then we design generator module under the code-conversion design principles.As EDA technology can make circuit simple,integrate multiple chips,reduce the size of circuits,so we take advantage of VHDL to describe it and use quartusII software to simulate.Finally we integrate all the fetures into the FPGA,and design circuit to generate stable and reliable base-band code to meet the different base-band digital transmission system needs.Key words:digital base-band code;EDA;VHDL;PCB;FPGA目录摘要 (1)Abstract (2)1前言 (5)2数字基带信号 (6)2.1数字基带信号的码型设计原则[2] (6)2.2非归零码(NRZ码)[1][3] (6)2.2.1单极性 (6)2.2.2双极性 (7)2.3归零码(RZ码)[1][3] (7)2.3.1单极性 (7)2.3.2双极性 (7)2.4差分码[4] (8)2.5交替极性码(AMI码)[4] (8)2.6分相码(曼彻斯特码)[5] (9)2.7传号反转码(CMI码)[4][6] (9)3EDA概述 (11)3.1硬件描述语言[8] (11)3.1.1Verilog-HDL (12)3.1.2VHDL (12)3.2可编程逻辑器件[11] (13)3.3EDA软件[12] (14)4基带码发生器的设计原理 (15)4.1基带码发生器的原理框图 (15)4.2码型转换原理 (16)5软件设计与仿真 (17)5.1VHDL程序设计[13][14] (17)5.2软件仿真 (19)5.2.1编辑和输入设计文件 (19)5.2.2创建工程 (20)5.2.3全程综合与编译 (22)5.2.4仿真测试 (22)6仿真结果及分析 (23)6.1器件仿真结果 (23)6.2波形仿真结果 (23)6.2.1NRZ的仿真波形 (23)6.2.2DRZ的仿真波形 (24)6.2.3CFM的仿真波形 (24)6.2.4CMI的仿真波形 (25)6.2.5FXM的仿真波形 (25)6.2.6SRZ的仿真波形 (25)6.2.7AMI的仿真波形 (26)6.2.8综合仿真波形 (26)7课设总结 (27)参考文献 (28)1前言近年来,随着大规模集成电路的出现,数字系统的设备复杂程度和技术难度降低,数字通信系统的主要缺点逐渐得到解决,因此数字传输方式日益受到欢迎。

数字传输系统中,传输对象通常是二元数字信息,而设计数字传输系统的基本考虑是选择一组有限的离散的波形来表示数字信息。

这些取值离散的波形可以是未经调制的电信号,也可以是调制后的信号。

未经调制的数字信号所占据的频谱是从零域或很低频率开始,称为数字基带信号。

不经载波调制而直接传输数字基带信号的系统,称为数字基带传输系统。

数字基带传输系统方框图如图1-1所示。

图1-1数字基带传输系统方框图目前,虽然数字基带传输的应用不是很广泛,但对于基带传输系统的研究仍然十分有意义,主要是因为:1、在利用对称电缆构成的近程数据通信系统中广泛采用了这种传输方式;2、随着数字通信技术的发展,基带传输方式也有迅速发展的趋势;3、基带传输中包含带通传输的许多基本问题;4、任何一个采用线性调制的带通传输系统,可以等效为一个基带传输系统。

2数字基带信号数字基带信号是数字信息的一种表现形式,被用于数字基带传输系统。

可以用不同电压或电流的代码来表示基带码。

不同形式的基带码具有不同的频谱结构,合理地设计基带码是基带传输首先要考虑的问题[1]。

2.1数字基带信号的码型设计原则[2](1)对于传输频率很低的信道来说,线路传输码型的频谱中应不含直流分量。

(2)可以从基带信号中提取位定时信号。

在基带传输系统中,需要从基带信号上提取位定时信息,这就要求编码功率谱中具有位定时线谱。

(3)要求基带编码具有内在检错能力。

(4)码型变换过程应具有透明性,即与信源的统计特性无关。

(5)尽量减少基带信号频谱中的高频分量。

这样可以节省传输频带,提高信道的频谱利用率,还可以减少串扰。

2.2非归零码(NRZ码)[1][3]非归零码分为两种,即单极性和双极性。

2.2.1单极性这种传输码的零电平与正电平(或负电平)分别对应于二进制代码中的“0”码与“1”码。

他的特点是:脉冲极性单一,有直流分量;脉冲波的占空比为100%,即一个脉冲持续的时间等于一个码元的宽度,在整个码元期间电平保持不变。

该码经常在近距离传输时被采用。

图2-1单极性非归零码2.2双极性2.2.2.2这种传输码的正、负电平分别对应于二进制代码中的“1”码与“0”码。

从信号的一般统计规律看,由于“1”码与“0”码出现的概率相等,所以这种传输码的平均电平为零,即无直流分量。

这样在接收端恢复信号时,其判决电平可取为0V,因而可消除因信道对直流电平的衰减而带来判决电平变化的影响。

这种传输码还有抗干扰能力强的特点。

该码常在CCITT的V系列接口标准或RS232C接口标准中使用。

图2-2双极性非归零码2.3归零码(RZ码)[1][3]归零码也分为两种,即单极性和双极性。

2.3.1单极性与单极性非归零码不同,发送“1”时在整个码元期间高电平只持续一段时间,在码元的其余时间内则返回到零电平,即此方式中,在传送“1”码时发送一个宽度小于码元持续时间的归零脉冲;传送“0”码时不发送脉冲。

其特征是所用脉冲宽度比码元宽度窄。

主要优点是可以直接提取同步信号。

单极性归零码脉冲间隔明显,有利于减小码元间的波形干扰和提取同步时钟信息,但由于脉宽窄,码元能量小,匹配接收时的输出信噪比要比NRZ码低。

图2-3单极性归零码2.3.2双极性这种传输码与单极性归零码相似,都是脉冲的持续时间小于码元宽度,并且都是在码元时间内回到零值。

与单极性归零码不同的是,“1”码与“0”码分别是用正、负两种电平来表示。

由于相邻脉冲之间必有零电平区域存在,因此,在接收端根据接收波形归于零电平便知道1b的信息已接收完毕,以便准备下一比特信息的接收。

正负脉冲的前沿起了启动信号的作用,后沿起了终止信号的作用,有利于接收端提取定时信号。

因此可以保持正确的比特同步,即收发之间无需特别定时,且各符号独立地构成起止方式。

此方式也叫做自同步方式。

图2-4双极性归零码2.4差分码[4]差分码利用前后码元电平的相对极性变化来传送信息,又称为相对码。

这种传输码不是用脉冲本身的电平高低来表示二进制代码的“1”码与“0”码,而是用脉冲波的电平变化来表示码元的取值,即当码元的取值为“1”时,脉冲波的电平变化一次;而当码元的取值为“0”时,脉冲波的电平不变。

这种方式的特点是,即使接收端收到的码元极性与发送端的完全相反,也能正确进行判决。

采用这种波形传送二进制代码时,可以消除设备初态的影响,尤其对于调相系统来说,可以有效地消除解调时相位模糊的问题。

图2-5差分码2.5交替极性码(AMI码)[4]AMI码名称较多,如双极方式码、平衡对称码、传号交替反转码等。

他是CCITT建议作为基带传输系统中的传输码型之一。

编码规则是,二进制代码中的“1”码由正、负极性交替的脉冲表示,其脉宽等于码元周期的一半;二进制代码中的“0”码由零电平表示。

此方式是单极性方式的变形,即把单极性方式中的“0”码与零电平对应,而“1”码发送极性交替的正、负电平。

这种码型实际上把二进制脉冲序列变成为三电平的符号序列(故叫伪三元信号),其优点如下:在“1”、“0”码不等概条件下也无直流成分,且零频附近低频分量小,因此对具有变压器或其他交流耦合的传输信道来说,不易受到隔直特性的影响;若接收端收到的码元极性与发送端完全相反也能正确判决;只要进行全波整流就可以变为单极性码,如果交替极性码是归零的,变为单极性归零码后就可以提取同步信号。

由于这些优点,因此他是最常用的码型之一。

但当传输信息中存在长连“0”码的情况时,这种传输码将会由于长时间不出现电平跳变,从而给接收端在提取定时信号时带来困难。

AMI码在连“0”码过多时提取定时信号有困难。

这是因为在连“0”码时AMI输出均为零电平,连“0”码这段时间内无法提取同步信号,而前面非连“0”码时提取的位同步信号又不能保持足够的时间。

这是这种传输码的不足之处。

图2-6交替极性码2.6分相码(曼彻斯特码)[5]这种码型的特点是每个码元用两个连续极性相反的脉冲表示。

如“1”码用正、负脉冲表示,“0”码用负、正脉冲表示。

这种码型不论信号的统计关系如何,均完全消除了直流分量,且有较尖锐的频谱特性。

同时这种码在连“1”和连“0”的情况下都能显示码元间隔,这有利于接收端提取码同步信号。

该码在本地局域网中常被使用。

图2-7分相码2.7传号反转码(CMI码)[4][6]传号反转码(CMI码)是由CCITT建议、适合于光信道传输的码型之一。