AT89S52英文资料及中文翻译

AT89S52单片机应用中英文翻译

本科毕业设计(论文)AT89S52单片机应用中英文翻译专业名称:电气工程及其自动化年级班级:学生姓名:指导老师:二O一二年六月九日AT89S52 MCU ApplicationsFunction Characteristic DescriptionThe AT89S52 is a low-power, high-performance CMOS 8-bit microcontroller with 8K bytes of in-system programmable Flash memory. The device is manufactured using Atmel’s high-density nonvolatile memory technology and is compatible with the indus-try-standard 80C51 instruction set and pinout. The on-chip Flash allows the program memory to be reprogrammed in-system or by a conventional nonvolatile memory pro-grammer. By combining a versatile 8-bit CPU with in-system programmable Flash on a monolithic chip, the Atmel AT89S52 is a powerful microcontroller which provides a highly-flexible and cost-effective solution to many embedded control applications.The AT89S52 provides the following standard features: 8K bytes of Flash, 256 bytes of RAM, 32 I/O lines, Watchdog timer, two data pointers, three 16-bit timer/counters, a six-vector two-level interrupt architecture, a full duplex serial port, on-chip oscillator, and clock circuitry. In addition, the AT89S52 is designed with static logic for operation down to zero frequency and supports two software selectable power saving modes. The Idle Mode stops the CPU while allowing the RAM, timer/counters, serial port, and interrupt system to continue functioning. The Power-down mode saves the RAM con-tents but freezes the oscillator, disabling all other chip functions until the next interrupt or hardware reset.Pin DescriptionVCC :Supply voltage.GND :Ground.Port 0:Port 0 is an 8-bit open drain bidirectional I/O port. As an output port, each pin can sink eight TTL inputs. When 1s are written to port 0 pins, the pins can be used as high-impedance inputs. Port 0 can also be configured to be the multiplexed low-order address/data bus during accesses to external program and data memory. In this mode, P0 has internal pull-ups. Port 0 also receives the code bytes during Flash programming and outputs the code bytes dur-ing program verification. External pull-ups are required during program verification.Port 1:Port 1 is an 8-bit bidirectional I/O port with internal pull-ups. The Port 1 outputbuffers can sink/source four TTL inputs. When 1s are written to Port 1 pins, they are pulled high by the inter-nal pull-ups and can be used as inputs. As inputs, Port 1 pins that are externally being pulled low will source current (IIL) because of the internal pull-ups. In addition, P1.0 and P1.1 can be configured to be the timer/counter 2 external count input (P1.0/T2) and the timer/counter 2 trigger input (P1.1/T2EX), respectively, as shown in the follow-ing table 1. Port 1 also receives the low-order address bytes during Flash programming and verification.Port 2:Port 2 is an 8-bit bidirectional I/O port with internal pull-ups. The Port 2 output buffers can sink/source four TTL inputs. When 1s are written to Port 2 pins, they are pulled high by the inter-nal pull-ups and can be used as inputs. As inputs, Port 2 pins that are externally being pulled low will source current (IIL) because of the internal pull-ups. Port 2 emits the high-order address byte during fetches from external program memory and dur-ing accesses to external data memory that use 16-bit addresses (MOVX @ DPTR). In this application, Port 2 uses strong internal pull-ups when emitting 1s. During accesses to external data memory that use 8-bit addresses (MOVX @ RI), Port 2 emits the contents of the P2 Special Function Register. Port 2 also receives the high-order address bits and some control signals during Flash program-ming and verification.Port 3:Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. The Port 3 output buffers can sink/source four TTL inputs. When 1s are written to Port 3 pins, they are pulled high by the inter-nal pull-ups and can be used as inputs. As inputs, Port 3 pins that areexternally being pulled low will source current (IIL) because of the pull-ups. Port 3 receives some control signals for Flash programming and verification. Port 3 also serves the functions of various special features of the AT89S52, as shown in the fol-lowing table 2.RST:Reset input. A high on this pin for two machine cycles while the oscillator is running resets the device. This pin drives high for 98 oscillator periods after the Watchdog times out. The DISRTO bit in SFR AUXR (address 8EH) can be used to disable this feature. In the default state of bit DISRTO, the RESET HIGH out feature is enabled.ALE/PROG:Address Latch Enable (ALE) is an output pulse for latching the low byte of the address during accesses to external memory. This pin is also the program pulse input (PROG) during Flash programming. In normal operation, ALE is emitted at a constant rate of 1/6 the oscillator frequency and may be used for external timing or clocking purposes. Note, however, that one ALE pulse is skipped dur-ing each access to external data memory. If desired, ALE operation can be disabled by setting bit 0 of SFR location 8EH. With the bit set, ALE is active only during a MOVX or MOVC instruction. Otherwise, the pin is weakly pulled high. Setting the ALE-disable bit has no effect if the microcontroller is in external execution mode.PSEN:Program Store Enable (PSEN) is the read strobe to external program memory. When the AT89S52 is executing code from external program memory, PSEN is activated twice each machine cycle, except that two PSEN activations are skipped during eachaccess to exter-nal data memory.EA/VPP:External Access Enable. EA must be strapped to GND in order to enable the device to fetch code from external program memory locations starting at 0000H up to FFFFH. Note, however, that if lock bit 1 is programmed, EA will be internally latched on reset. EA should be strapped to VCC for internal program executions. This pin also receives the 12-volt programming enable voltage (VPP) during Flash programming.XTAL1:Input to the inverting oscillator amplifier and input to the internal clock operating circuit.XTAL2:Output from the inverting oscillator amplifier.Program MemoryIf the EA pin is connected to GND, all program fetches are directed to external memory. On the AT89S52, if EA is connected to VCC, program fetches to addresses 0000H through 1FFFH are directed to internal memory and fetches to addresses 2000H through FFFFH are to external memory.Data MemoryThe AT89S52 implements 256 bytes of on-chip RAM. The upper 128 bytes occupy a parallel address space to the Special Function Registers. This means that the upper 128 bytes have the same addresses as the SFR space but are physically separate from SFR space. When an instruction accesses an internal location above address 7FH, the address mode used in the instruction specifies whether the CPU accesses the upper 128 bytes of RAM or the SFR space. Instructions which use direct addressing access the SFR space. For example, the following direct addressing instruction accesses the SFR at location 0A0H (which is P2). MOV 0A0H, #data. Instructions that use indirect addressing access the upper 128 bytes of RAM. For example, the following indirect addressing instruction, where R0 contains 0A0H, accesses the data byte at address 0A0H, rather than P2 (whose address is 0A0H).MOV @R0, #data. Note that stack operations are examples of indirect addressing, so the upper 128 bytes of data RAM are available as stack space.Watchdog TimerThe WDT is intended as a recovery method in situations where the CPU may be subjected to software upsets. The WDT consists of a 14-bit counter and the Watchdog Timer Reset (WDTRST) SFR. The WDT is defaulted to disable from exiting reset. To enable the WDT, a user must write 01EH and 0E1H in sequence to the WDTRST register (SFR location 0A6H). When the WDT is enabled, it will increment every machine cycle while the oscillator is running. The WDT timeout period is dependent on the external clock frequency. There is no way to disable the WDT except through reset (either hardware reset or WDT overflow reset). When WDT over-flows, it will drive an output RESET HIGH pulse at the RST pin.In Power-down mode the oscillator stops, which means the WDT also stops. While in Power-down mode, the user does not need to service the WDT. There are two methods of exiting Power-down mode: by a hardware reset or via a level-activated external interrupt which is enabled prior to entering Power-down mode. When Power-down is exited with hardware reset, servicing the WDT should occur as it normally does whenever the AT89S52 is reset. Exiting Power-down with an interrupt is significantly different. The interrupt is held low long enough for the oscillator to stabilize. When the interrupt is brought high, the interrupt is serviced. To prevent the WDT from resetting the device while the interrupt pin is held low, the WDT is not started until the interrupt is pulled high. It is suggested that the WDT be reset during the interrupt service for the interrupt used to exit Power-down mode. To ensure that the WDT does not overflow within a few states of exiting Power-down, it is best to reset the WDT just before entering Power-down mode. Before going into the IDLE mode, the WDIDLE bit in SFR AUXR is used to determine whether the WDT continues to count if enabled. The WDT keeps counting during IDLE (WDIDLE bit = 0) as the default state. To prevent the WDT from resetting the AT89S52 while in IDLE mode, the user should always set up a timer that will periodically exit IDLE, service the WDT, and reenter IDLE mode. With WDIDLE bit enabled, the WDT will stop to count in IDLE mode and resumes the count upon exit from IDLE.Timer 0 and 1Timer 0 and Timer 1 in the AT89S52 operate the same way as Timer 0 and Timer 1 in the AT89C51 and AT89C52. For further information o n the timers’ operation, please click on the document link below:/dyn/resources/prod_documents/DOC4316.PDFTimer 2Timer 2 is a 16-bit Timer/Counter that can operate as either a timer or an event counter. The type of operation is selected by bit C/T2in the SFR T2CON. Timer 2 has three operating modes: capture, auto-reload (up or down counting), and baud rate generator. The modes are selected by bits in T2CON, as shown in Table 6-1. Timer 2 consists of two 8-bit registers, TH2 and TL2. In the Timer function, the TL2 register is incremented every machine cycle. Since a machine cycle consists of 12 oscillator periods, the count rate is 1/12 of the oscil-lator frequency.In the Counter function, the register is incremented in response to a 1-to-0 transition at its corre-sponding external input pin, T2. In this function, the external input is sampled during S5P2 of every machine cycle. When the samples show a high in one cycle and a low in the next cycle, the count is incremented. The new count value appears in the register during S3P1 of the cycle following the one in which the transition was detected. Since two machine cycles (24 oscillator periods) are required to recognize a 1-to-0 transition, the maximum count rate is 1/24 of the oscillator frequency. To ensure that a given level is sampled at least once before it changes, the level should be held for at least one full machine cycle.InterruptsThe AT89S52 has a total of six interrupt vectors: two external interrupts (INT0and INT1), three timer interrupts (Timers 0, 1, and 2), and the serial port interrupt. Each of these interrupt sources can be individually enabled or disabled by setting or clearing a bit in Special Function Register IE. IE also contains a global disable bit, EA, which disables all interrupts at once. Note that bit position IE.6 is unimplemented. User software should not write a 1 to this bit position, since it may be used in future AT89 products. Timer 2 interrupt is generated by the logical OR of bits TF2 and EXF2 in register T2CON. Nei-ther of these flags is cleared by hardware when the service routine is vectored to. In fact, the service routine may have to determine whether it was TF2 or EXF2 that generated the interrupt, and that bit will have to be cleared in software. The Timer 0 and Timer 1 flags, TF0 and TF1, are set at S5P2 of the cycle in which the timers overflow. The values are then polled by the circuitry in the next cycle. However, the Timer 2 flag, TF2, is set at S2P2 and is polled in the same cycle in which the timer overflows.Oscillator CharacteristicsXTAL1 and XTAL2 are the input and output, respectively, of an inverting amplifier that can be configured for use as an on-chip oscillator. Either a quartz crystal or ceramic resonator may be used. To drive the device from an external clock source, XTAL2 should be left unconnected while XTAL1 is driven,. There are no requirements on the duty cycle of the external clock signal, since the input to the internal clock-ing circuitry is through a divide-by-two flip-flop, but minimum and maximum voltage high and low time specifications must be observed.Power-down ModeIn the Power-down mode, the oscillator is stopped, and the instruction that invokes Power-down is the last instruction executed. The on-chip RAM and Special Function Registers retain their values until the Power-down mode is terminated. Exit from Power-down mode can be initiated either by a hardware reset or by an enabled external interrupt. Reset redefines the SFRs but does not change the on-chip RAM. The reset should not be activated before VCC is restored to its normal operating level and must be heldactive long enough to allow the oscillator to restart and stabilize.Idle ModIn idle mode, the CPU puts itself to sleep while all the on-chip peripherals remain active. The mode is invoked by software. The content of the on-chip RAM and all the special functions regis-ters remain unchanged during this mode. The idle mode can be terminated by any enabled interrupt or by a hardware reset. Note that when idle mode is terminated by a hardware reset, the device normally resumes pro-gram execution from where it left off, up to two machine cycles before the internal reset algorithm takes control. On-chip hardware inhibits access to internal RAM in this event, but access to the port pins is not inhibited. To eliminate the possibility of an unexpected write to a port pin when idle mode is terminated by a reset, the instruction following the one that invokes idle mode should not write to a port pin or to external memory.AT89S52单片机应用功能特征描述AT89S52是一种低功耗、高性能CMOS8位微控制器,具有8K 在系统可编程Flash 存储器。

单片机温度控制系统毕业论文中英文资料外文翻译文献

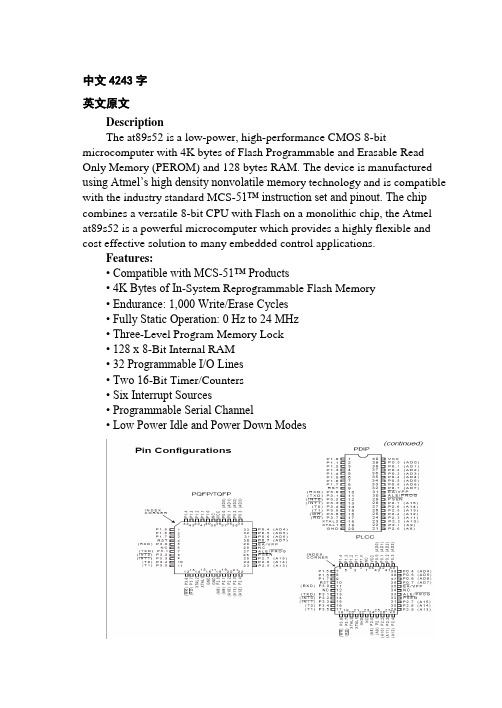

单片机温度控制系统中英文资料外文翻译文献英文原文DescriptionThe at89s52 is a low-power, high-performance CMOS 8-bit microcomputer with 4K bytes of Flash Programmable and Erasable Read Only Memory (PEROM) and 128 bytes RAM. The device is manufactured using Atmel’s h igh density nonvolatile memory technology and is compatible with the industry standard MCS-51™ instruction set and pinout. The chip combines a versatile 8-bit CPU with Flash on a monolithic chip, the Atmelat89s52 is a powerful microcomputer which provides a highly flexible and cost effective solution to many embedded control applications.Features:• Compatible with MCS-51™ Products• 4K Bytes of In-System Reprogrammable Flash Memory• Endurance: 1,000 Write/Erase Cycles• Fully Static Operation: 0 Hz to 24 MHz• Three-Level Program Memory Lock• 128 x 8-Bit Internal RAM• 32 Programmable I/O Lines• Two 16-Bit Timer/Counters• Six Interrupt Sources• Programmable Serial Channel• Low Power Idle and Power Down ModesThe at89s52 provides the following standard features: 4K bytes of Flash, 128 bytes of RAM, 32 I/O lines, two 16-bit timer/counters, a five vectortwo-level interrupt architecture, a full duplex serial port, on-chip oscillator and clock circuitry. In addition, the at89s52 is designed with static logic for operation down to zero frequency and supports two software selectable power saving modes. The Idle Mode stops the CPU while allowing the RAM, timer/counters, serial port and interrupt system to continue functioning. The Power Down Mode saves the RAM contents but freezes the oscillator disabling all other chip functions until the next hardware reset.Pin Description:VCC Supply voltage.GND Ground.Port 0Port 0 is an 8-bit open drain bidirectional I/O port. As an output port each pin can sink eight TTL inputs. When is are written to port 0 pins, the pins can be used as high impedance inputs.Port 0 may also be configured to be the multiplexed loworderaddress/data bus during accesses to external program and data memory. In this mode P0 has internal pullups.Port 0 also receives the code bytes during Flash programming, and outputs the code bytes during program verification. External pullups are required during program verification.Port 1Port 1 is an 8-bit bidirectional I/O port with internal pullups. The Port 1 output buffers can sink/source four TTL inputs. When 1s are written to Port 1 pins they are pulled high by the internal pullups and can be used as inputs. As inputs, Port 1 pins that are externally being pulled low will source current (IIL) because of the internal pullups.Port 1 also receives the low-order address bytes during Flash programming and verification.Port 2Port 2 is an 8-bit bidirectional I/O port with internal pullups. The Port 2 output buffers can sink/source four TTL inputs. When 1s are written to Port 2 pins they are pulled high by the internal pullups and can be used as inputs. As inputs, Port 2 pins that are externally being pulled low will source current (IIL) because of the internal pullups.Port 2 emits the high-order address byte during fetches from external program memory and during accesses to external data memory that use 16-bit addresses (MOVX @ DPTR). In this application it uses strong internalpull-ups when emitting 1s. During accesses to external data memory that use 8-bit addresses (MOVX @ RI), Port 2 emits the contents of the P2 Special Function Register.Port 2 also receives the high-order address bits and some control signals during Flash programming and verification.Port 3Port 3 is an 8-bit bidirectional I/O port with internal pullups. The Port 3 output buffers can sink/source four TTL inputs. When 1s are written to Port 3 pins they are pulled high by the internal pullups and can be used as inputs. As inputs, Port 3 pins that are externally being pulled low will source current (IIL) because of the pullups.Port 3 also serves the functions of various special features of theat89s52 as listed below:Port 3 also receives some control signals for Flash programming andverification.RSTReset input. A high on this pin for two machine cycles while theoscillator is running resets the device.ALE/PROGAddress Latch Enable output pulse for latching the low byte of theaddress during accesses to external memory. This pin is also the program pulse input (PROG) during Flash programming.In normal operation ALE is emitted at a constant rate of 1/6 theoscillator frequency, and may be used for external timing or clockingpurposes. Note, however, that one ALE pulse is skipped during each access to external Data Memory.If desired, ALE operation can be disabled by setting bit 0 of SFRlocation 8EH. With the bit set, ALE is active only during a MOVX or MOVC instruction. Otherwise, the pin is weakly pulled high. Setting the ALE-disable bit has no effect if the microcontroller is in external execution mode.PSENProgram Store Enable is the read strobe to external program memory. When the at89s52 is executing code from external program memory, PSEN is activated twice each machine cycle, except that two PSENactivations are skipped during each access to external data memory.EA/VPPExternal Access Enable. EA must be strapped to GND in order to enable the device to fetch code from external program memory locations starting at 0000H up to FFFFH. Note, however, that if lock bit 1 is programmed, EA will be internally latched on reset. Port pinalternate functions P3.0rxd (serial input port) P3.1txd (serial output port) P3.2^int0 (external interrupt0) P3.3^int1 (external interrupt1) P3.4t0 (timer0 external input) P3.5t1 (timer1 external input) P3.6^WR (external data memory write strobe) P3.7 ^rd (external data memory read strobe)EA should be strapped to VCC for internal program executions.This pin also receives the 12-volt programming enable voltage(VPP) during Flash programming, for parts that require 12-volt VPP.XTAL1Input to the inverting oscillator amplifier and input to the internal clock operating circuit.XTAL2Output from the inverting oscillator amplifier.Oscillator CharacteristicsXTAL1 and XTAL2 are the input and output, respectively, of an inverting amplifier which can be configured for use as an on-chip oscillator, as shown in Figure 1. Either a quartz crystal or ceramic resonator may be used. To drive the device from an external clock source, XTAL2 should be left unconnected while XTAL1 is driven as shown in Figure 2. There are no requirements on the duty cycle of the external clock signal, since the input to the internal clocking circuitry is through a divide-by-two flip-flop, but minimum and maximum voltage high and low time specifications must be observed.Idle ModeIn idle mode, the CPU puts itself to sleep while all the onchip peripherals remain active. The mode is invoked by software. The content of the on-chip RAM and all the special functions registers remain unchanged during this mode. The idle mode can be terminated by any enabled interrupt or by a hardware reset.It should be noted that when idle is terminated by a hard ware reset, the device normally resumes program execution, from where it left off, up to two machine cycles before the internal reset algorithm takes control. On-chip hardware inhibits access to internal RAM in this event, but access to the port pins is not inhibited. To eliminate the possibility of an unexpected write to a port pin when Idle is terminated by reset, the instruction following the one that invokes Idle should not be one that writes to a port pin or to external memory.Status of External Pins During Idle and Power Down Modesmode Program memory ALE ^psen Port0 Port1Port2Port3idle internal 1 1 data data data Data Idle External 1 1 float Data data Data Power down Internal 0 0 Data Data Data Data Power down External 0 0 float data Data data Power Down ModeIn the power down mode the oscillator is stopped, and the instructionthat invokes power down is the last instruction executed. The on-chip RAMand Special Function Registers retain their values until the power down modeis terminated. The only exit from power down is a hardware reset. Resetredefines the SFRs but does not change the on-chip RAM. The reset shouldnot be activated before VCC is restored to its normal operating level andmust be held active long enough to allow the oscillator to restart andstabilize.Program Memory Lock BitsOn the chip are three lock bits which can be left unprogrammed (U) orcan be programmed (P) to obtain the additional features listed in the tablebelow:Lock Bit Protection ModesWhen lock bit 1 is programmed, the logic level at the EA pin issampled and latched during reset. If the device is powered up without a reset,the latch initializes to a random value, and holds that value until reset isactivated. It is necessary that the latched value of EA be in agreement with the current logic level at that pin in order for the device to function properly. Programming the Flash:The at89s52 is normally shipped with the on-chip Flash memory array in the erased state (that is, contents = FFH) and ready to be programmed.The programming interface accepts either a high-voltage (12-volt) or alow-voltage (VCC) program enable signal.The low voltage programming mode provides a convenient way to program the at89s52 inside the user’s system, while the high-voltage programming mode is compatible with conventional third party Flash or EPROM programmers.The at89s52 is shipped with either the high-voltage or low-voltage programming mode enabled. The respective top-side marking and device signature codes are listed in the following table.Vpp=12v Vpp=5vTop-side mark at89s52xxxxyywwat89s52xxxx-5yywwsignature (030H)=1EH(031H)=51H(032H)=FFH (030H)=1EH (031H)=51H (032H)=05HThe at89s52 code memory array is programmed byte-bybyte in either programming mode. To program any nonblank byte in the on-chip Flash Programmable and Erasable Read Only Memory, the entire memory must be erased using the Chip Erase Mode.Programming Algorithm:Before programming the at89s52, the address, data and control signals should be set up according to the Flash programming mode table and Figures 3 and 4. To program the at89s52, take the following steps.1. Input the desired memory location on the address lines.2. Input the appropriate data byte on the data lines.3. Activate the correct combination of control signals.4. Raise EA/VPP to 12V for the high-voltage programming mode.5. Pulse ALE/PROG once to program a byte in the Flash array or the lock bits. The byte-write cycle is self-timed and typically takes no more than 1.5 ms. Repeat steps 1 through 5, changing the address and data for the entire array or until the end of the object file is reached.Data Polling: The at89s52 features Data Polling to indicate the end of a write cycle. During a write cycle, an attempted read of the last byte written will result in the complement of the written datum on PO.7. Once the write cycle has been completed, true data are valid on all outputs, and the next cycle may begin. Data Polling may begin any time after a write cycle has been initiated.Ready/Busy: The progress of byte programming can also be monitored by the RDY/BSY output signal. P3.4 is pulled low after ALE goes high during programming to indicate BUSY. P3.4 is pulled high again when programming is done to indicate READY.Program Verify: If lock bits LB1 and LB2 have not been programmed, the programmed code data can be read back via the address and data lines for verification. The lock bits cannot be verified directly. Verification of the lock bits is achieved by observing that their features are enabled.Chip Erase: T he entire Flash Programmable and Erasable Read Only Memory array is erased electrically by using the proper combination of control signals and by holding ALE/PROG low for 10 ms. The code array is written with all “1”s. The chip erase operation must be executed before the code memory can be re-programmed.Reading the Signature Bytes: The signature bytes are read by the same procedure as a normal verification of locations 030H, 031H, and 032H, except that P3.6 and P3.7 must be pulled to a logic low. The values returned are as follows.(030H) = 1EH indicates manufactured by Atmel(031H) = 51H indicates 89C51(032H) = FFH indicates 12V programming(032H) = 05H indicates 5V programmingProgramming InterfaceEvery code byte in the Flash array can be written and the entire array can be erased by using the appropriate combination of control signals. The write operation cycle is selftimed and once initiated, will automatically time itself to completion.中文翻译描述at89s52是美国ATMEL公司生产的低电压,高性能CMOS8位单片机,片内含4Kbytes的快速可擦写的只读程序存储器(PEROM)和128 bytes 的随机存取数据存储器(RAM),器件采用ATMEL公司的高密度、非易失性存储技术生产,兼容标准MCS-51产品指令系统,片内置通用8位中央处理器(CPU)和flish存储单元,功能强大at89s52单片机可为您提供许多高性价比的应用场合,可灵活应用于各种控制领域。

气体检测系统中英文对照外文翻译文献

⽓体检测系统中英⽂对照外⽂翻译⽂献中英⽂对照翻译研究智能⽓体检测系统⽂摘根据统计数据,中国近年来,煤⽓泄漏时有发⽣,对⼈⾝安全造成很⼤威胁,因此⽓体检测和监控系统是需要作为⼀个安全装置在家庭应⽤。

在本⽂中,智能⽓体检测系统的设计。

该检测仪采⽤单⽚机AT89S52为控制核⼼,采⽤催化燃烧式⽓体传感器元件MC112作为⽓体传感器(CH4)检测。

该系统的主要功能如下:浓度的实时监测CH4和显⽰的浓度值;发射声光报警信号,如果CH4浓度值超过报警值通过键盘⾯板输⼊;串⾏通信⼝发送数据地⾯以上主机。

软件调试和硬件仿真上述系统也实现在同⼀时间。

关键词:数据采集,传感器,串⾏通信,单⽚机。

在本⽂中,检测系统采⽤单⽚机作为控制计算机;整个系统的⽰意图如图1所⽰。

选择理由:单⽚机作为控制核⼼,它具有体积⼩尺⼨,⾼可靠性,低价格,使其成为⾏业使⽤⾮常合适智能仪表、实时控制领域。

系统的操作界⾯如图2所⽰。

在右上⾓号码显⽰默认的或⽤户定义的⽓体浓度值,在左上⾓显⽰检测到的⽓体浓度值。

报警灯的设置。

所有的功能通过设置控制⾯板上的按键控制,包括电源键,复位键,数据采集的关键。

其他键包括⼗个数字键,调整值键和回车键来改变阈值。

基本操作程序如下:⾸先按下电源键,系统初始化机数据采集的关键,LED在右上⾓显⽰的阈值1;⽤户可以定制阈值调整值的按键和数字键,然后按回车键确认更改。

系统开始检测⽓体浓度和上显⽰这些参左叶⾯积,同时实时数据的传输,通过RS-485总线主机地⾯上的。

3⽓体检测系统的硬件系统设计主要包括主控单元系统的硬件结构,传感器和信号放⼤电路,A/D转换模块,声光报警电路,键盘显⽰模块,串⼝通信模块。

3.1主控单元具有集成度⾼,体积⼩,价格低,单⽚机已⼴泛应⽤于⼯业过程中⼴泛应⽤包括控制,数据采集,机电⼀体化,智能仪表,家⽤电器和⽹络技术,以及显著提⾼的程度技术和⾃动化。

考虑在芯⽚选择两个因素,⼀是抗⼲扰的能⼒,提⾼单⽚机应⽤系统的⼲扰,图2. 系统运⾏界⾯图所以单⽚机必须有较⾼的外界⼲扰;⼆是单⽚机的性能价格⽐。

AT89S52手册

UART

在AT89S52 中,UART的操作与AT89C51和AT89C52一样。为了获得更深入的关于UART的信息,可参考ATMEL网站()。从这个主页,选择“Products”,然后选择“8051-Architech Flash Microcontroller”,再选择“ProductOverview”即可。

对于89S52,如果EA接VCC,程序读写先从内部存储器(地址为0000H~1FFFH)开始,接着从外部寻址,寻址地址为:2000H~FFFFH。

数据存储器

AT89S52有256字节片内数据存储器。高128字节与特殊功能寄存器重叠。也就是说高128字节与特殊功能寄存器有相同的地址,而物理上是分开的。当一条指令访问高于7FH 的地址时,寻址方式决定CPU 访问高128 字节RAM 还是特殊功能寄存器空间。直接寻址方式访问特殊功能寄存器(SFR)。

P3口引脚第二功能:

P3.0 RXD(串行输入)

P3.1 TXD(串行输出)

P3.2 INT0(外部中断0)

P3.3 INT1(外部中断1)

P3.4 T0(定时器0外部输入)

P3.5 T1(定时器1外部输入)

P3.6 WR(外部数据存储器写选通)

P3.7 RD(外部数据存储器写选通)

P1 口:P1 口是一个具有内部上拉电阻的8 位双向I/O 口,p1 输出缓冲器能驱动4 个TTL 逻辑电平。对P1 端口写“1”时,内部上拉电阻把端口拉高,此时可以作为输入口使用。作为输入使用时,被外部拉低的引脚由于内部电阻的原因,将输出电流(IIL)。此外,P1.0和P1.2分别作定时器/计数器2的外部计数输入(P1.0/T2)和时器/计数器2的触发输入(P1.1/T2EX),具体如下表所示。在flash编程和校验时,P1口接收低8位地址字节。

可燃气体报警器中英文对照外文翻译文献

可燃气体报警器中英文对照外文翻译文献(文档含英文原文和中文翻译)原文:Design of Combustible Gas Detection system using WirelessKeywords:TGS813, AT89S52, DS18B20, nRF905, TC35iAbstract.The detection device of combustible gas are designed in the presented work,using wireless transceiver and GSM network.The system realize the wireless transmission of the gas concentration,and also can send alarm information to user’s mobile when an exception occurs.The system consists of two parts: a master and slave. The function of the slave is to collect data, process data and transffer the data to the master.The taskof the master is to receive data and display it by LED.The signal acquisition is completed by sensor TGS813 and A/D converter TLC2543. Thewireless transmission is achieved through wireless transceiver nRF905. Since the accuracy of thesensor is affected by the environment,using DS18B20 to achieve temperature compensation.And with wireless communication module TC35i and GSM network platform, we can send thealarm information to use r’s mobile promptly.IntroductionGas detection is widely used in petroleum, chemical, metallurgy, family, shopping malls,gas stations and other places. Currently, how to monitor the hazardous gas fast and accuratelyare the important issues. Although the gas detection technology is relatively mature, but mostproducts has many shortcomings, such as single function, operating complex, bulky, expensiveand low sensitivity. Wireless communication technology applied to the gas monitoring field, canresolve the problem of remote monitoring in special environment, such as high temperature, low temperature, toxic gas.and unable to wiring .In the presented work, the combustible gas detectoris fully functional (with wireless transceiver), simple, small size, low cost, and has high sensitivity. The equipment can greatlyimprove the system's detection capability and accuracy with temperature compensation algorithm, and also can send alarm information to the user's mobile phone promptly through theGSM network.System designThe system consists of two parts as shown in Figure 1.Fig. 1 Overall system block diagramThe slave part mainly complete data collection and wireless transmission. The master part mainly complete receiving data, displaying and sending alarm message.The signal of gas concentration is collected by combustible gas sensor which generates a weak electrical signal. The signal can be amplified and stabilized by conditioning circuit. And then A/D circuit converts the analog signal to digital signal which microcontroller can process. In order to improve the measurement accuracy, and reduce the impact of temperature, design a temperature compensation circuit to collect tempreture data. AT89S52 process the collected data and send data to the master by wireless transceiver.The master receives the data and displays it by LED. And if the gas concentration being abnormal,the system will drive speaker for an alarm signal and use TC35i module to send alarm information to user’s mobile.Hardware designSignal acquisition and conditioning circuit. Figure 2 shows data acquisition circuit. TGS813 is a Gas sensing resistive sensor. The conductivity of TGS813 is influenced by the concentration of combustible gases in air, the greater the concentration, the higher conductivity. In system R0, R9, R10 and RS (inTGS813) form a bridge circuit to convert resistance to voltage signal. Operational amplifier A connected as a voltage follower with resistors R7 and regulator D1 make up the voltage regulator circuit to supply power for the bridge. In order to the voltage adapt to the A/D converter, the voltage is amplified by opamp B, and the magnification can be adjusted through resistor R11.Fig. 2 Gas concentration signal acquisition circuitFig. 3 Temperature compensation circuitTemperature compensation circuit. The resistance of Rs is greatly affected by temperature. In order to improve system accuracy, the results must be temperature compensated or temperature correction.In system, using temperature sensor DS1820 to collect temperature signal, and using software method for temperature correction.Wireless transmission module. Wireless transceiver is achieved by a single-chip RF transceiver nRF905. MCU and nRF905 realize data and commands interaction through the SPI interface.The typical application schematic is shown in Figure 4. The antenna part is 50Ω single-ended antenna.The communication frequency is 433MHz, and operating voltage is3.3V. The value of resistors,capacitors and inductor is determined by the datasheet of nRF905. GSM short message unit. The interface circuit of TC35i and MCU is shown in Figure 5. The communication between MCU and TC35i is via serial, and the rate is 9600bps. Communicationsmode is 8-bit asynchronous with a start bit, 8 data bits, and 1 stop bit. But the serial input of TC35i requires CMOS level, and serial output of 89C52 requires TTL level. In order to achieve the voltage conversion the system use the way of resistors sharing voltage. Fig. 4 nRF905 Application SchematicFig. 5 TC35i and MCU interface circuitSoftware DesignThe software system includes data acquisition module, temperature compensation module, and wireless transceiver moduleWireless sending program. NRF905 data sending process is as follows:1) When having data to send, the microcontroller send the receiver's address and the data to nRF905 chronologically by the SPI interface.Then placed the data to be transmitted into TxBuf register, send WTP command to write the data to TX-Payload register, and send WTA command to write TX address to the TX-Address register.2) The microcontroller set TRX_CE=1 and TX_EN=1 to stimulate nRF905 ShockBurstTM sending mode. When data transmission completed, the data ready pin is set high;3) Beacause of AUTO_RETRAN being high, the data of nRF905 is constantly re-issued untilTRX_CE=0.4) when TRX_CE pin is set low, means the data transmission completed and nRF905 enter idlemode.Wireless receiving program. NRF905 data receiving process is as follows:1)When TRX_CE = 1 and TX_EN = 0, nRF905 enters ShockBurstTM receive modechecking constantly and waiting for receiving data.2)When nRF905 detect the carrier having same frequency band, the carrier detect pin will beset high.3)When nRF905 receive a matched address, the address matches pin will be set high.4) When packet correctly received, the word head, address and CRC bits will automatically be removed, and the data ready pin will be set high.5) MCU set TRX_CE to "0", and nRF905 enter to idle mode.6) When all the data received, nRF905 set data ready pin and address matching pin to "0", and nRF905 turn to shutdown mode or ShockBurstTM transmitmode and receive mode.Fig.6 Wireless data transmission flow chartFig.7 Wireless data receiving flow chartSummaryDesigned an equipment to detect the concentration of combustible gas, which has wireless transceiver functions and can send the alarm information to user’s mobile promptly through GSM.Experimental results show that the devices have high precision, stability and reliability. It can meet most applications which need real-time monitoring of combustible gas concentration.References[1] Liu S, Chen Q, Wang H G, eat. Electrical capacitance tomography for gas solids flow measurement for circulating fluidized beds [J].Flow Measurement and Instrumentation,2005,16(2-3):135-144.[2] TGS 813-for the Detection of Combustible Gases [DB/OL].2009-08-12.[3] Liu Wei, Chen HeXin,Zhang JunWei,etc. Intelligent control and alarm system based on TC35i. IEEE.2008 International Symposium on Computer Science and Computational Technology(ISCSCT), Shanghai, 2008:80-83译文:使用无线的可燃气体检测系统的设计关键词:TGS813,AT89S52单片机,DS18B20,nRF905,TC35i摘要;可燃气体检测装置是在所提出的工作设计,使用无线收发器和GSM网络。

单片机温度控制系统中英文翻译资料

中文4243字英文原文DescriptionThe at89s52 is a low-power, high-performance CMOS 8-bit microcomputer with 4K bytes of Flash Programmable and Erasable Read Only Memory (PEROM) and 128 bytes RAM. The device is manufactured using Atmel’s high density nonvolatile me mory technology and is compatible with the industry standard MCS-51™ instruction set and pinout. The chip combines a versatile 8-bit CPU with Flash on a monolithic chip, the Atmelat89s52 is a powerful microcomputer which provides a highly flexible and cost effective solution to many embedded control applications.Features:• Compatible with MCS-51™ Products• 4K Bytes of In-System Reprogrammable Flash Memory• Endurance: 1,000 Write/Erase Cycles• Fully Static Operation: 0 Hz to 24 MHz• Three-Level Program Memory Lock• 128 x 8-Bit Internal RAM• 32 Programmable I/O Lines• Two 16-Bit Timer/Counters• Six Interrupt Sources• Programmable Serial Channel• Low Power Idle and Power Down ModesThe at89s52 provides the following standard features: 4K bytes of Flash, 128 bytes of RAM, 32 I/O lines, two 16-bit timer/counters, a five vectortwo-level interrupt architecture, a full duplex serial port, on-chip oscillator and clock circuitry. In addition, the at89s52 is designed with static logic for operation down to zero frequency and supports two software selectable power saving modes. The Idle Mode stops the CPU while allowing the RAM, timer/counters, serial port and interrupt system to continue functioning. The Power Down Mode saves the RAM contents but freezes the oscillator disabling all other chip functions until the next hardware reset.Pin Description:VCC Supply voltage.GND Ground.Port 0Port 0 is an 8-bit open drain bidirectional I/O port. As an output port each pin can sink eight TTL inputs. When is are written to port 0 pins, the pins can be used as high impedance inputs.Port 0 may also be configured to be the multiplexed loworderaddress/data bus during accesses to external program and data memory. In this mode P0 has internal pullups.Port 0 also receives the code bytes during Flash programming, and outputs the code bytes during program verification. External pullups are required during program verification.Port 1Port 1 is an 8-bit bidirectional I/O port with internal pullups. The Port 1 output buffers can sink/source four TTL inputs. When 1s are written to Port 1 pins they are pulled high by the internal pullups and can be used as inputs. As inputs, Port 1 pins that are externally being pulled low will source current (IIL) because of the internal pullups.Port 1 also receives the low-order address bytes during Flash programming and verification.Port 2Port 2 is an 8-bit bidirectional I/O port with internal pullups. The Port 2 output buffers can sink/source four TTL inputs. When 1s are written to Port 2 pins they are pulled high by the internal pullups and can be used as inputs. As inputs, Port 2 pins that are externally being pulled low will source current (IIL) because of the internal pullups.Port 2 emits the high-order address byte during fetches from external program memory and during accesses to external data memory that use 16-bit addresses (MOVX @ DPTR). In this application it uses strong internalpull-ups when emitting 1s. During accesses to external data memory that use 8-bit addresses (MOVX @ RI), Port 2 emits the contents of the P2 Special Function Register.Port 2 also receives the high-order address bits and some control signals during Flash programming and verification.Port 3Port 3 is an 8-bit bidirectional I/O port with internal pullups. The Port 3 output buffers can sink/source four TTL inputs. When 1s are written to Port 3 pins they are pulled high by the internal pullups and can be used as inputs. As inputs, Port 3 pins that are externally being pulled low will source current (IIL) because of the pullups.Port 3 also serves the functions of various special features of theat89s52 as listed below:Port 3 also receives some control signals for Flash programming andverification.RSTReset input. A high on this pin for two machine cycles while theoscillator is running resets the device.ALE/PROGAddress Latch Enable output pulse for latching the low byte of the address during accesses to external memory. This pin is also the program pulse input (PROG) during Flash programming.In normal operation ALE is emitted at a constant rate of 1/6 theoscillator frequency, and may be used for external timing or clockingpurposes. Note, however, that one ALE pulse is skipped during each access to external Data Memory.If desired, ALE operation can be disabled by setting bit 0 of SFRlocation 8EH. With the bit set, ALE is active only during a MOVX or MOVC instruction. Otherwise, the pin is weakly pulled high. Setting the ALE-disable bit has no effect if the microcontroller is in external execution mode.PSENProgram Store Enable is the read strobe to external program memory. When the at89s52 is executing code from external program memory, PSEN is activated twice each machine cycle, except that two PSEN activations are skipped during each access to external data memory.EA/VPPExternal Access Enable. EA must be strapped to GND in order to enable the device to fetch code from external program memory locations starting at 0000H up to FFFFH. Note, however, that if lock bit 1 is programmed, EA will be internally latched on reset. Port pinalternate functions P3.0rxd (serial input port) P3.1txd (serial output port) P3.2^int0 (external interrupt0) P3.3^int1 (external interrupt1) P3.4t0 (timer0 external input) P3.5t1 (timer1 external input) P3.6^WR (external data memory write strobe) P3.7 ^rd (external data memory read strobe)EA should be strapped to VCC for internal program executions.This pin also receives the 12-volt programming enable voltage(VPP) during Flash programming, for parts that require 12-volt VPP.XTAL1Input to the inverting oscillator amplifier and input to the internal clock operating circuit.XTAL2Output from the inverting oscillator amplifier.Oscillator CharacteristicsXTAL1 and XTAL2 are the input and output, respectively, of an inverting amplifier which can be configured for use as an on-chip oscillator, as shown in Figure 1. Either a quartz crystal or ceramic resonator may be used. To drive the device from an external clock source, XTAL2 should be left unconnected while XTAL1 is driven as shown in Figure 2. There are no requirements on the duty cycle of the external clock signal, since the input to the internal clocking circuitry is through a divide-by-two flip-flop, but minimum and maximum voltage high and low time specifications must be observed.Idle ModeIn idle mode, the CPU puts itself to sleep while all the onchip peripherals remain active. The mode is invoked by software. The content of the on-chip RAM and all the special functions registers remain unchanged during this mode. The idle mode can be terminated by any enabled interrupt or by a hardware reset.It should be noted that when idle is terminated by a hard ware reset, the device normally resumes program execution, from where it left off, up to two machine cycles before the internal reset algorithm takes control. On-chip hardware inhibits access to internal RAM in this event, but access to the port pins is not inhibited. To eliminate the possibility of an unexpected write to a port pin when Idle is terminated by reset, the instruction following the one that invokes Idle should not be one that writes to a port pin or to external memory.Status of External Pins During Idle and Power Down Modesmode Program memory ALE ^psen Port0 Port1Port2Port3idle internal 1 1 data data data Data Idle External 1 1 float Data data Data Power down Internal 0 0 Data Data Data Data Power down External 0 0 float data Data data Power Down ModeIn the power down mode the oscillator is stopped, and the instructionthat invokes power down is the last instruction executed. The on-chip RAMand Special Function Registers retain their values until the power down modeis terminated. The only exit from power down is a hardware reset. Resetredefines the SFRs but does not change the on-chip RAM. The reset shouldnot be activated before VCC is restored to its normal operating level andmust be held active long enough to allow the oscillator to restart andstabilize.Program Memory Lock BitsOn the chip are three lock bits which can be left unprogrammed (U) orcan be programmed (P) to obtain the additional features listed in the tablebelow:Lock Bit Protection ModesWhen lock bit 1 is programmed, the logic level at the EA pin issampled and latched during reset. If the device is powered up without a reset,the latch initializes to a random value, and holds that value until reset isactivated. It is necessary that the latched value of EA be in agreement with the current logic level at that pin in order for the device to function properly. Programming the Flash:The at89s52 is normally shipped with the on-chip Flash memory array in the erased state (that is, contents = FFH) and ready to be programmed.The programming interface accepts either a high-voltage (12-volt) or alow-voltage (VCC) program enable signal.The low voltage programming mode provides a convenient way to program the at89s52 inside the user’s system, while the high-voltage programming mode is compatible with conventional third party Flash or EPROM programmers.The at89s52 is shipped with either the high-voltage or low-voltage programming mode enabled. The respective top-side marking and device signature codes are listed in the following table.Vpp=12v Vpp=5vTop-side mark at89s52xxxxyywwat89s52xxxx-5yywwsignature (030H)=1EH(031H)=51H(032H)=FFH (030H)=1EH (031H)=51H (032H)=05HThe at89s52 code memory array is programmed byte-bybyte in either programming mode. To program any nonblank byte in the on-chip Flash Programmable and Erasable Read Only Memory, the entire memory must be erased using the Chip Erase Mode.Programming Algorithm:Before programming the at89s52, the address, data and control signals should be set up according to the Flash programming mode table and Figures 3 and 4. To program the at89s52, take the following steps.1. Input the desired memory location on the address lines.2. Input the appropriate data byte on the data lines.3. Activate the correct combination of control signals.4. Raise EA/VPP to 12V for the high-voltage programming mode.5. Pulse ALE/PROG once to program a byte in the Flash array or the lock bits. The byte-write cycle is self-timed and typically takes no more than 1.5 ms. Repeat steps 1 through 5, changing the address and data for the entire array or until the end of the object file is reached.Data Polling: The at89s52 features Data Polling to indicate the end of a write cycle. During a write cycle, an attempted read of the last byte written will result in the complement of the written datum on PO.7. Once the write cycle has been completed, true data are valid on all outputs, and the next cycle may begin. Data Polling may begin any time after a write cycle has been initiated.Ready/Busy: The progress of byte programming can also be monitored by the RDY/BSY output signal. P3.4 is pulled low after ALE goes high during programming to indicate BUSY. P3.4 is pulled high again when programming is done to indicate READY.Program Verify: If lock bits LB1 and LB2 have not been programmed, the programmed code data can be read back via the address and data lines for verification. The lock bits cannot be verified directly. Verification of the lock bits is achieved by observing that their features are enabled.Chip Erase: T he entire Flash Programmable and Erasable Read Only Memory array is erased electrically by using the proper combination of control signals and by holding ALE/PROG low for 10 ms. The code array is written with all “1”s. The chip erase operation must be executed before the code memory can be re-programmed.Reading the Signature Bytes: The signature bytes are read by the same procedure as a normal verification of locations 030H, 031H, and 032H, except that P3.6 and P3.7 must be pulled to a logic low. The values returned are as follows.(030H) = 1EH indicates manufactured by Atmel(031H) = 51H indicates 89C51(032H) = FFH indicates 12V programming(032H) = 05H indicates 5V programmingProgramming InterfaceEvery code byte in the Flash array can be written and the entire array can be erased by using the appropriate combination of control signals. The write operation cycle is selftimed and once initiated, will automatically time itself to completion.中文翻译描述at89s52是美国ATMEL公司生产的低电压,高性能CMOS8位单片机,片内含4Kbytes的快速可擦写的只读程序存储器(PEROM)和128 bytes 的随机存取数据存储器(RAM),器件采用ATMEL公司的高密度、非易失性存储技术生产,兼容标准MCS-51产品指令系统,片内置通用8位中央处理器(CPU)和flish存储单元,功能强大at89s52单片机可为您提供许多高性价比的应用场合,可灵活应用于各种控制领域。

中英文外文翻译PLC和微处理器定

Introductions of PLC and MCUA PLC is a device that was invented to replace the necessary sequential relay circuits for machine control. The PLC works by looking at its inputs and depending upon their state, turning on/off its outputs .The user enters a program, usually via software or programmer that gives the desired results.PLC are used in many “real world〞applications. If there is industry present, chances are good that there is a PLC present. If you are involved in machining, packaging, material handling, automated assembly or countless other industries, you are probably already using them. If you are not, you are wasting money and time. Almost any application that needs some type of electrical control has need for PLC.For example, let’s assume that when a switch turns on we want to turn a solenoid on for 5 seconds and then turn it off regardless of how long the switch is on for. We can do this with a simple external timer. What if the process also needed to count how many times the switch individually turned on? We need a lot of external counters.As you can see, the bigger the process the more of a need we have for a PLC. We can simply program the PLC to count its inputs and turn the solenoids on for the specified time.We will take a look at what i s considered to be the “top 20〞PLC instructions. It can be safely estimated that with a firm understanding of there instructions one can solve more than 80% of the applications in existence.That‘s right, more than 80%! Of course we’ll learn more than jus t these instructions to help you solve almost ALL your potential PLC applications.The PLC mainly consists of a CPU, memory areas, and appropriate circuits to receive input/output data, as shown in Fig. 19.1 We can actually consider the PLC to be a box full of hundreds or thousands of separate relays, counters, timer and date storage locations. Do these counters, timers, etc. really exist? No, they don’t “physically〞exist but rather they are simulated and can be considered software counters, timers, etc. These internal relays are simulated through bit locations in registers.What does each part do?INPUT RELAYS-(contacts) These are connected to the outside world. They physically exist and receive signals from switches, sensors, etc... Typically they are not relays but rather they are transistors.INTERNAL UTILITY RELAYS-(contacts) These do not receive signals from the outside world nor do they physically exist. They are simulated relays and are what enables a PLC to eliminate external relays. There are also some special relays that are dedicated to performing only one task. Some are always on while some are always off. Some are on only once during power-on and are typically user for initializing data what was stored.COUNTERS These again do not physically exist. They are simulated counters and they can be programmed to count pulses. Typically these counters can count up, down or both up and down. Since there are simulated, they are limited in their counting speed. Some manufacturers also include high-speed counters that are hardware based. We can think of these as physically existing. Most timers these counters can count up, down or up and down.TIMERS These also do not physically exist. They come in many varieties and increments. The most common type is an on-delay type. Other include off-delay and both retentive and non-retentive types. Increments vary from 1ms through 1s.OUTPUT RELAYS-(coil) These are connected to the outside world. They physically exist and send on/off signals to solenoids, lights, etc… They can be transistors, relays, or triacs depending upon the model chosen.DATA STORAGE-Typically there are registers assigned to simply store data. There are usually used as temporary storage for math or data manipulation. They can also typically be user power-up they will still have the same contents as before power war removed. Very convenient and necessary!A PLC works by continually scanning a program. We can think of this scan cycle as consisting of 3 important steps, as shown in Fig. There are typically more than 3 but we can focus on the important parts and not worry about the others. Typically the others are checking the system and updating the current and timer values.Step 1-CHECK INPUT STATUS-First the PLC takes a look at each input to determine if it is on or off. In other words, is the sensor connected to the first input on? How about the second input? How about the third…It records this data into its memory to be used during the next step.Step 2-EXECUTE PROGRAM-Next the PLC executes your program one instruction at a time. Maybe your program said that if the first input was on then it should turn on the first output. Since is already knows which inputs are on/off from the previous step, it will be able to decide whether the first output should be turned onbased on the state of the first input. It will store the execution results for use later during the next step.Step 3-UPDATE OUTPUT STSTUS-Finally the PLC updates the status of outputs. It updates the outputs based on which inputs were on during the first step and the results of executing your program during the second step. Based on the example in step 2 it would now turn on the first output because the first input was on and your program said to turn on the first output when this condition is true.After the third step the PLC goes back to step one and repeats the steps continuously. One scan time is defined as the time is takes to execute the 3 steps listed above. Thus a practical system is controlled to perform specified operations as desired.The AT89S52 is a low-power, high-performance CMOS 8-bit microcontroller with 8Kbytes of in-system programmable Flash memory. The device is manufactured using Atmel’s high-density nonvolatile memory technology and is compatible with the industry-standard 80C51 instruction set and pin-out. The on-chip Flash allows the program memory to be reprogrammed in-system or by a conventional nonvolatile memory programmer. By combining a versatile 8-bit CPU with in-system programmable Flash on a monolithic chip, the Atmel AT89S52 is a powerful microcontroller which provides a highly-flexible and cost-effective solution to many embedded control applications.The AT89S52 provides the following standard features: 8K bytes of Flash, 256 bytes of RAM, 32 I/O lines, Watchdog timer, two data pointers, three 16-bit timer/counters, a six-vector two-level interrupt architecture, a full duplex serial port, on-chip oscillator, and clock circuitry. In addition, the AT89S52 is designed with static logic for operation down to zero frequency and supports two software selectable power saving modes. The Idle Mode stops the CPU while allowing the RAM, timer/counters, serial port, and interrupt system to continue functioning. The Power-down mode saves the RAM contents but freezes the oscillator, disabling all other chip functions until the next interrupt or hardware reset.Port 0 is an 8-bit open drain bidirectional I/O port. As an output port, each pin can sink eight TTL inputs. When is written to port 0 pins, the pins can be used as high-impedance inputs.Port 0 can also be configured to be the multiplexed lowered address/data bus during accesses to external program and data memory. In this mode, P0 has internal pull-ups.Port 0 also receives the code bytes during Flash programming and outputs the code bytes during program verification. External pull-ups are required during program verification.Port 1 is an 8-bit bidirectional I/O port with internal Port 1 output buffers can sink/source four TTL inputs. When 1s are written to Port 1 pins, they are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 1 pins that are externally being pulled low will source current (I IL) because of the internal pull-ups.In addition, P1.0 and P1.1 can be configured to be the timer/counter 2 external count input (P1.0/T2) and the timer/counter 2 trigger input (P1.1/T2EX).PLC和微处理器简介PLC(可编程逻辑控制器)是极限控制中为代替必要的继电器时序电路而创造的一种设备。

单片机AT89S52介绍

AT89S52简介AT89S52是一个8位单片机,片内ROM全部采用FLASH ROM技术,与MCS-51系列完全兼容,它能以3V的超低电压工作,晶振时钟最高可达24MHz。

AT89S52是标准的40引脚双列直插式集成电路芯片,有4个八位的并行双向I/O端口,分别记作P0、P1、P2、P3。

第31引脚需要接高电位使单片机选用内部程序存储器;第9引脚是复位引脚,要接一个上电手动复位电路;第40脚为电源端VCC,接+5V电源,第20引脚为接地端VSS,通常在VCC和VSS引脚之间接μF高频滤波电容。

第18、19脚之间接上一个12MHz的晶振为单片机提供时钟信号。

AT89S52单片机说明如下:此芯片是一种高性能低功耗的采用CMOS工艺制造的8位微控制器,它提供下列标准特征:8K字节的程序存储器,256字节的RAM,32条I/O线,2个16位定时器/计数器, 一个5中断源两个优先级的中断结构,一个双工的串行口, 片上震荡器和时钟电路。

引脚说明::电源电压·VCC·GND:地·P0口:P0口是一组8位漏极开路型双向I/O口,作为输出口用时,每个引脚能驱动8个TTL逻辑门电路。

当对0端口写入1时,可以作为高阻抗输入端使用。

当P0口访问外部程序存储器或数据存储器时,它还可设定成地址数据总线复用的形式。

在这种模式下,P0口具有内部上拉电阻。

在EPROM编程时,P0口接收指令字节,同时输出指令字节在程序校验时。

程序校验时需要外接上拉电阻。

·P1口:P1口是一带有内部上拉电阻的8位双向I/O口。

P1口的输出缓冲能接受或输出4个TTL逻辑门电路。

当对P1口写1时,它们被内部的上拉电阻拉升为高电平,此时可以作为输入端使用。

当作为输入端使用时,P1口因为内)。

部存在上拉电阻,所以当外部被拉低时会输出一个低电流(IIL·P2口:P2是一带有内部上拉电阻的8位双向的I/O端口。

电气工程及其自动化专业AT89S52单片机应用大学毕业论文英文文献翻译及原文

毕业设计(论文)外文文献翻译文献、资料中文题目:AT89S52单片机应用文献、资料英文题目: AT89S52 MCU Applications文献、资料来源:文献、资料发表(出版)日期:院(部):专业:电气工程及其自动化班级:姓名:学号:指导教师:翻译日期: 2017.02.14本科毕业设计(论文)AT89S52单片机应用中英文翻译专业名称:电气工程及其自动化年级班级:学生姓名:指导老师:AT89S52 MCU ApplicationsFunction Characteristic DescriptionThe AT89S52 is a low-power, high-performance CMOS 8-bit microcontroller with 8K bytes of in-syste m programmable Flash memory. The device is manufactured using Atmel’s high-density nonvolatile memory technology and is compatible with the indus-try-standard 80C51 instruction set and pinout. The on-chip Flash allows the program memory to be reprogrammed in-system or by a conventional nonvolatile memory pro-grammer. By combining a versatile 8-bit CPU with in-system programmable Flash on a monolithic chip, the Atmel AT89S52 is a powerful microcontroller which provides a highly-flexible and cost-effective solution to many embedded control applications.The AT89S52 provides the following standard features: 8K bytes of Flash, 256 bytes of RAM, 32 I/O lines, Watchdog timer, two data pointers, three 16-bit timer/counters, a six-vector two-level interrupt architecture, a full duplex serial port, on-chip oscillator, and clock circuitry. In addition, the AT89S52 is designed with static logic for operation down to zero frequency and supports two software selectable power saving modes. The Idle Mode stops the CPU while allowing the RAM, timer/counters, serial port, and interrupt system to continue functioning. The Power-down mode saves the RAM con-tents but freezes the oscillator, disabling all other chip functions until the next interrupt or hardware reset.Pin DescriptionVCC :Supply voltage.GND :Ground.Port 0:Port 0 is an 8-bit open drain bidirectional I/O port. As an output port, each pin can sink eight TTL inputs. When 1s are written to port 0 pins, the pins can be used as high-impedance inputs. Port 0 can also be configured to be the multiplexed low-order address/data bus during accesses to external program and data memory. In this mode, P0 has internal pull-ups. Port 0 also receives the code bytes during Flash programming and outputs the code bytes dur-ing program verification. External pull-ups are required during program verification.Port 1:Port 1 is an 8-bit bidirectional I/O port with internal pull-ups. The Port 1 outputbuffers can sink/source four TTL inputs. When 1s are written to Port 1 pins, they are pulled high by the inter-nal pull-ups and can be used as inputs. As inputs, Port 1 pins that are externally being pulled low will source current (IIL) because of the internal pull-ups. In addition, P1.0 and P1.1 can be configured to be the timer/counter 2 external count input (P1.0/T2) and the timer/counter 2 trigger input (P1.1/T2EX), respectively, as shown in the follow-ing table 1. Port 1 also receives the low-order address bytes during Flash programming and verification.Port 2:Port 2 is an 8-bit bidirectional I/O port with internal pull-ups. The Port 2 output buffers can sink/source four TTL inputs. When 1s are written to Port 2 pins, they are pulled high by the inter-nal pull-ups and can be used as inputs. As inputs, Port 2 pins that are externally being pulled low will source current (IIL) because of the internal pull-ups. Port 2 emits the high-order address byte during fetches from external program memory and dur-ing accesses to external data memory that use 16-bit addresses (MOVX @ DPTR). In this application, Port 2 uses strong internal pull-ups when emitting 1s. During accesses to external data memory that use 8-bit addresses (MOVX @ RI), Port 2 emits the contents of the P2 Special Function Register. Port 2 also receives the high-order address bits and some control signals during Flash program-ming and verification.Port 3:Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. The Port 3 output buffers can sink/source four TTL inputs. When 1s are written to Port 3 pins, they are pulled high by the inter-nal pull-ups and can be used as inputs. As inputs, Port 3 pins that areexternally being pulled low will source current (IIL) because of the pull-ups. Port 3 receives some control signals for Flash programming and verification. Port 3 also serves the functions of various special features of the AT89S52, as shown in the fol-lowing table 2.RST:Reset input. A high on this pin for two machine cycles while the oscillator is running resets the device. This pin drives high for 98 oscillator periods after the Watchdog times out. The DISRTO bit in SFR AUXR (address 8EH) can be used to disable this feature. In the default state of bit DISRTO, the RESET HIGH out feature is enabled.ALE/PROG:Address Latch Enable (ALE) is an output pulse for latching the low byte of the address during accesses to external memory. This pin is also the program pulse input (PROG) during Flash programming. In normal operation, ALE is emitted at a constant rate of 1/6 the oscillator frequency and may be used for external timing or clocking purposes. Note, however, that one ALE pulse is skipped dur-ing each access to external data memory. If desired, ALE operation can be disabled by setting bit 0 of SFR location 8EH. With the bit set, ALE is active only during a MOVX or MOVC instruction. Otherwise, the pin is weakly pulled high. Setting the ALE-disable bit has no effect if the microcontroller is in external execution mode.PSEN:Program Store Enable (PSEN) is the read strobe to external program memory. When the AT89S52 is executing code from external program memory, PSEN is activated twice each machine cycle, except that two PSEN activations are skipped during eachaccess to exter-nal data memory.EA/VPP:External Access Enable. EA must be strapped to GND in order to enable the device to fetch code from external program memory locations starting at 0000H up to FFFFH. Note, however, that if lock bit 1 is programmed, EA will be internally latched on reset. EA should be strapped to VCC for internal program executions. This pin also receives the 12-volt programming enable voltage (VPP) during Flash programming.XTAL1:Input to the inverting oscillator amplifier and input to the internal clock operating circuit.XTAL2:Output from the inverting oscillator amplifier.Program MemoryIf the EA pin is connected to GND, all program fetches are directed to external memory. On the AT89S52, if EA is connected to VCC, program fetches to addresses 0000H through 1FFFH are directed to internal memory and fetches to addresses 2000H through FFFFH are to external memory.Data MemoryThe AT89S52 implements 256 bytes of on-chip RAM. The upper 128 bytes occupy a parallel address space to the Special Function Registers. This means that the upper 128 bytes have the same addresses as the SFR space but are physically separate from SFR space. When an instruction accesses an internal location above address 7FH, the address mode used in the instruction specifies whether the CPU accesses the upper 128 bytes of RAM or the SFR space. Instructions which use direct addressing access the SFR space. For example, the following direct addressing instruction accesses the SFR at location 0A0H (which is P2). MOV 0A0H, #data. Instructions that use indirect addressing access the upper 128 bytes of RAM. For example, the following indirect addressing instruction, where R0 contains 0A0H, accesses the data byte at address 0A0H, rather than P2 (whose address is 0A0H).MOV @R0, #data. Note that stack operations are examples of indirect addressing, so the upper 128 bytes of data RAM are available as stack space.。

AT89S52单片机中英文对照外文翻译文献