300mm硅单晶及抛光片标准

粗糙度、光洁度、抛光级别对应表-玻璃光洁度等级-300目粗糙度

抛光等级对照表

Polish Grade Comparision

Ra是在取样长度内轮廓偏距绝对值的算术平均值

Rmax是在取样长度内最大峰高与最大谷深的高度差

Rmax和Ra没有直接关系,统计上两者间的关系大概是Rmax = 4Ra

μin是半导体方面的单位与1μm=39.37μin

倒三角是日本的粗糙度,一个三角是是1.6, 两个三角就是3。

2

国标新旧标准对照:

表面光洁度14级=Ra 0。

012

表面光洁度13级=Ra 0。

025

表面光洁度12级=Ra 0。

050

表面光洁度11级=Ra 0.1

表面光洁度10级=Ra 0。

2

表面光洁度9级=Ra 0.4

表面光洁度8级=Ra 0。

8

表面光洁度7级=Ra 1。

6

表面光洁度6级=Ra 3。

2

表面光洁度5级=Ra 6.3

表面光洁度4级=Ra 12.5

表面光洁度3级=Ra 25

表面光洁度2级=Ra 50

表面光洁度1级=Ra 100

以上表面粗糙度单位均为μm,即微米。

300mm硅单晶及抛光片标准

4.0 4.1 4.2 4.3 4.4 4.5 4.6 4.7 4.8 4.9 5.0 5.0 5.2 5.3 5.5

结构特性 位错蚀坑密度 滑移 系属结构 孪晶 漩涡 浅蚀坑 氧化层错(OISF) 氧化物沉淀 硅片制备特性 晶片ID标志 正表面薄膜 洁净区 非本征吸除 背封 见注2 无 无 无 无 见注1 无 无 无 不规定 不规定 不规定 不规定

6.0 6.1 6.2 6.3 6.6 6.7 6.8 6.9 6.11 6.12 6.14 7.0 7.1

机械特性 直径 主基准位置 主基准尺寸 边缘轮廓 厚度 厚度变化(TTV) 晶片表面取向 翘曲度 峰——谷差 平整度/局部 正表面化学特性 表面金属沾污 钠/铝/铬/铁/镍/铜/锌/钙 ≤5×1010/cm2 300±0.2mm 见SEMI M1 见SEMI M1 见SEMI M1 775±25μm 10μm max 1-0-0±1° 50μm max 用户规定 见注3

表1 尺寸和公差要求

特 直 性 径 尺 寸 300.00 725 1.00 90 100 10 ≥0.80 公差 ±0.20 ±20 +0.25, -0.00 +5,-1 单位A mm μm mm ° μm μm

厚 度,中 心 点 切 口 (见图7) 深 角 翘 曲 度 最 大 值B 总厚度变化(GBIR)C 最大值 背面光泽度D 抛光的边缘轮廓表面加 工度E 边缘轮廓 座标:(见图4) 表3 Cy Cx 度

300mm硅单晶及抛光片标准

有研半导体材料股份有限公司 孙燕

一、300 mm硅单晶及抛光片现状

300mm硅抛光片的产品、工艺技术在国外已经很成熟。 而在我国起步较晚,还处于试验阶段。 因此对于集成电路所需的300mm硅片的基本参数指标、 金属污染和缺陷控制、表面形态与质量、成本等都面临着新 的挑战。硅材料的生产工艺、技术、检测方法已成为今后研 究的主要内容,同时也是推动产业发展的关键所在。 随着300mm硅单晶及抛光片的诞生,我们也面临一个制定 相应的国家标准的问题。

硅片的等级标准

硅片的检测1:硅片表面光滑洁净2:TV:220±20um 。

3:几何尺寸:边长:125±0.5mm;对角150±0.5mm、148±0.5mm、165±0.5mm;边长:103±0.5mm、对角:135±0.5mm;边长:150±0.5mm、156±0.5mm、对角:203±0.5mm、200±0.5mm、。

同心度:任意两个弧的弦长之差≤1mm垂直度:任意两边的夹角:90°±0.3二、合格品一级品:垂直度:任意两边的夹角:90°±0.5二级品:1:表面有少许污渍、线痕。

凹痕、轻微崩边。

2:220±30um ≤TV≤220±40um。

3:凹痕:硅片表面凹痕之和≤30um4:崩边范围:崩边口不是三角形,崩边口长度≤1mm ,深度≤0.5mm 5:几何尺寸:边长:125±0.52mm;对角150±0.52mm、148±0.52mm、165±0.52mm;边长:103±0.52mm、对角:135±0.52mm;边长:150±0.52mm、156±0.52mm、对角:203±0.52mm、200±0.52mm、。

同心度:任意两个弧的弦长之差≤1.5mm垂直度:任意两边的夹角:90°±0.8三级品:1:表面有油污但硅片颜色不发黑,有线痕和硅洛现象。

2:220±40um ≤TV≤220±60um。

3:硅落:整张硅片边缘硅晶脱落部分硅晶脱落。

三、不合格品严重线痕、厚薄片:TV>220±60um。

崩边片:有缺陷但可以改¢103的硅片气孔片:硅片中间有气孔外形片:切方滚圆未能磨出的硅片。

倒角片(同心度):任意两个弧的弦长之差>1.5mm菱形片:(垂直度):任意两边的夹角>90°±0.8凹痕片:硅片两面凹痕之和>30um脏片:硅片表面有严重污渍且发黄发黑尺寸偏差片:几何尺寸超过二级片的范围。

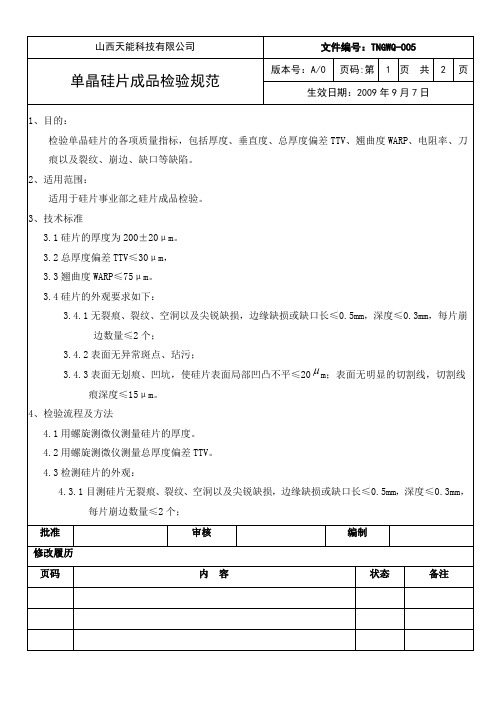

单晶硅片成品检验规范

4.3检测硅片的外观:

4.3.1目测硅片无裂痕、裂纹、空洞以及尖锐缺损,边缘缺损或缺口长≤0.5mm,深度≤0.3mm,每片崩边数量≤2个;

批准

审核

编制

修改履历

页码

内容

状态

Hale Waihona Puke 备注4.3.2目测硅片表面无异常斑点、玷污;

4.3.3目测表面无凹坑,使硅片表面局部凹凸不平≤20μm;

4.3.4目测表面无明显的切割线,切割刀痕深度≤20μm。

6、验收规则

抽样频率为500PCS为一个单位即20%,每25PCS为一篮,每一篮抽5PCS,记录在《线切割硅片返工卡》、《#机硅片检验记录表》中,电阻率、少子寿命及尺寸全检记录在表单编号:TNGWQ-OO1-01《圆棒检验记录》、表单编号:TNGWQ-OO2-01《方棒检验记录》中。

附表三 《退片检验反馈单》表单编号:TNGWQ-005-03

附表四《单晶硅片电阻率抽测记录》表单编号:TNGWQ-005-04

附表五 《厚度抽测简易图》表单编号:TNGWQ-005-05

7.5检验工序必须保证及时正确的检验校验的成品几半成品及原料,防止因产品积压影响上下工序的正常生产。

7.6对已经检验完成的成品、废品,要及时办理入库手续,不得随意阻滞交验的物品,必须及时反馈检验信息给相关人员检验结果。

8、相关记录

附表一《线切割返工卡》表单编号:TNGWQ-005-01

附表二 《#机检验记录表》表单编号:TNGWQ-005-02

3.4.1无裂痕、裂纹、空洞以及尖锐缺损,边缘缺损或缺口长≤0.5mm,深度≤0.3mm,每片崩边数量≤2个;

3.4.2表面无异常斑点、玷污;

单晶硅技术参数

单晶硅抛光片的物理性能参数同硅单晶技术参数厚度(T) 200-1200um总厚度变化(TTV)<10um弯曲度(BOW)<35um翘曲度(WARP)<35um单晶硅抛光片的表面质量:正面要求无划道、无蚀坑、无雾、无区域沾污、无崩边、无裂缝、无凹坑、无沟、无小丘、无刀痕等。

背面要求无区域沾污、无崩边、无裂缝、无刀痕。

(2)加工工艺知识多晶硅加工成单晶硅棒:多晶硅长晶法即长成单晶硅棒法有二种:CZ(Czochralski)法FZ(Float-Zone Technique)法目前超过98%的电子元件材料全部使用单晶硅。

其中用CZ法占了约85%,其他部份则是由浮融法FZ生长法。

CZ法生长出的单晶硅,用在生产低功率的集成电路元件。

而FZ法生长出的单晶硅则主要用在高功率的电子元件。

CZ法所以比FZ法更普遍被半导体工业采用,主要在于它的高氧含量提供了晶片强化的优点。

另外一个原因是CZ法比FZ法更容易生产出大尺寸的单晶硅棒。

目前国内主要采用CZ法CZ法主要设备:CZ生长炉CZ法生长炉的组成元件可分成四部分(1)炉体:包括石英坩埚,石墨坩埚,加热及绝热元件,炉壁(2)晶棒及坩埚拉升旋转机构:包括籽晶夹头,吊线及拉升旋转元件(3)气氛压力控制:包括气体流量控制,真空系统及压力控制阀(4)控制系统:包括侦测感应器及电脑控制系统加工工艺:加料→熔化→缩颈生长→放肩生长→等径生长→尾部生长(1)加料:将多晶硅原料及杂质放入石英坩埚内,杂质的种类依电阻的N或P型而定。

杂质种类有硼,磷,锑,砷。

(2)熔化:加完多晶硅原料于石英埚内后,长晶炉必须关闭并抽成真空后充入高纯氩气使之维持一定压力范围内,然后打开石墨加热器电源,加热至熔化温度(1420℃)以上,将多晶硅原料熔化。

(3)缩颈生长:当硅熔体的温度稳定之后,将籽晶慢慢浸入硅熔体中。

由于籽晶与硅熔体场接触时的热应力,会使籽晶产生位错,这些位错必须利用缩劲生长使之消失掉。

缩颈生长是将籽晶快速向上提升,使长出的籽晶的直径缩小到一定大小(4-6mm)由于位错线与生长轴成一个交角,只要缩颈够长,位错便能长出晶体表面,产生零位错的晶体。

单晶硅抛光片的物理性能参数同硅单晶技术参数

单晶硅抛光片的物理性能参数同硅单晶技术参数新闻来源:中国太阳能电池资讯网作者:未知日期:2006-6-1 9:26:00 点击数:269厚度(T)200-1200um总厚度变化(TTV)<10um弯曲度(BOW)<35um翘曲度(W ARP)<35um单晶硅抛光片的表面质量:正面要求无划道、无蚀坑、无雾、无区域沾污、无崩边、无裂缝、无凹坑、无沟、无小丘、无刀痕等。

背面要求无区域沾污、无崩边、无裂缝、无刀痕。

(2)加工工艺知识多晶硅加工成单晶硅棒:多晶硅长晶法即长成单晶硅棒法有二种:CZ(Czochralski)法FZ(Float-Zone Technique)法目前超过98%的电子元件材料全部使用单晶硅。

其中用CZ法占了约85%,其他部份则是由浮融法FZ生长法。

CZ法生长出的单晶硅,用在生产低功率的集成电路元件。

而FZ 法生长出的单晶硅则主要用在高功率的电子元件。

CZ法所以比FZ法更普遍被半导体工业采用,主要在于它的高氧含量提供了晶片强化的优点。

另外一个原因是CZ法比FZ法更容易生产出大尺寸的单晶硅棒。

目前国内主要采用CZ法CZ法主要设备:CZ生长炉CZ法生长炉的组成元件可分成四部分(1)炉体:包括石英坩埚,石墨坩埚,加热及绝热元件,炉壁(2)晶棒及坩埚拉升旋转机构:包括籽晶夹头,吊线及拉升旋转元件(3)气氛压力控制:包括气体流量控制,真空系统及压力控制阀(4)控制系统:包括侦测感应器及电脑控制系统加工工艺:加料→熔化→缩颈生长→放肩生长→等径生长→尾部生长(1)加料:将多晶硅原料及杂质放入石英坩埚内,杂质的种类依电阻的N或P型而定。

杂质种类有硼,磷,锑,砷。

(2)熔化:加完多晶硅原料于石英埚内后,长晶炉必须关闭并抽成真空后充入高纯氩气使之维持一定压力范围内,然后打开石墨加热器电源,加热至熔化温度(1420℃)以上,将多晶硅原料熔化。

(3)缩颈生长:当硅熔体的温度稳定之后,将籽晶慢慢浸入硅熔体中。

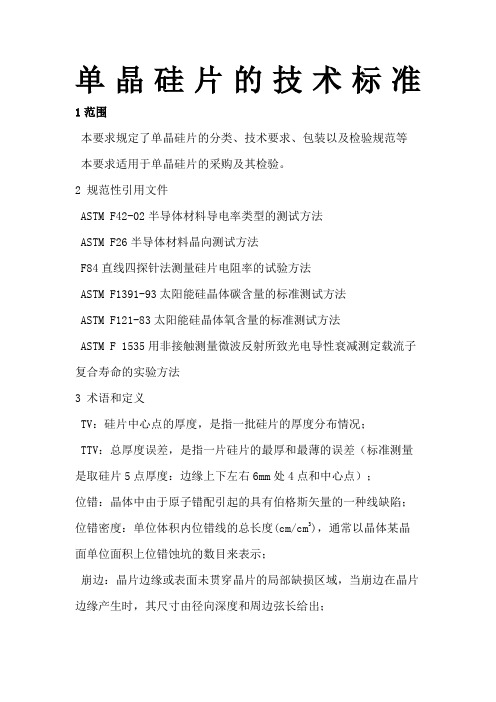

单晶硅片的技术标准

单晶硅片的技术标准1 范围本要求规定了单晶硅片的分类、技术要求、包装以及检验规范等本要求适用于单晶硅片的采购及其检验。

2 规范性引用文件ASTM F42-02 半导体材料导电率类型的测试方法ASTM F26 半导体材料晶向测试方法F84 直线四探针法测量硅片电阻率的试验方法ASTM F1391-93 太阳能硅晶体碳含量的标准测试方法ASTM F121-83 太阳能硅晶体氧含量的标准测试方法ASTM F 1535 用非接触测量微波反射所致光电导性衰减测定载流子复合寿命的实验方法3 术语和定义TV :硅片中心点的厚度,是指一批硅片的厚度分布情况;TTV :总厚度误差,是指一片硅片的最厚和最薄的误差(标准测量是取硅片5点厚度:边缘上下左右6mn处4点和中心点);位错:晶体中由于原子错配引起的具有伯格斯矢量的一种线缺陷;位错密度:单位体积内位错线的总长度(cm/cm3),通常以晶体某晶面单位面积上位错蚀坑的数目来表示;崩边:晶片边缘或表面未贯穿晶片的局部缺损区域,当崩边在晶片边缘产生时,其尺寸由径向深度和周边弦长给出;裂纹、裂痕:延伸到晶片表面,可能贯穿,也可能不贯穿整个晶片厚度的解理或裂痕;四角同心度:单晶硅片四个角与标准规格尺寸相比较的差值。

密集型线痕:每1cm上可视线痕的条数超过5条4分类单晶硅片的等级有A级品和B级品,规格为:125’ 1251 (mm)125’ 125 H (mm)156’ 156(mm。

5技术要求外观见附录表格中检验要求。

外形尺寸方片TV为200士20 um,测试点为中心点;方片TTV小于30um,测试点为边缘6mn处4点、中心1点;硅片TTV以五点测量法为准,同一片硅片厚度变化应小于其标称厚度的15%相邻C段的垂直度:90°士;其他尺寸要求见表1。

表1单晶硅片尺寸要求图1硅单晶片尺寸示意图材料性质导电类型:硅片电阻率:见下表;硅片少子寿命:见下表(此寿命为2mmf羊片钝化后的少子寿命);晶向:表面晶向<100>+/°;位错密度w 3000pcs/cm2;氧碳含量:氧含量w 20ppma碳含量w。

300mm硅片技术发展现状与趋势-有研硅股-

300mm硅片技术发展现状与趋势 周旗钢(有研半导体材料股份有限公司,北京100088)摘要:综合评述了300 mm硅材料在晶体生长、硅片成形、表面质量控制、衬底优化以及表征等方面的研究现状和发展趋势,特别是国内在300mm硅技术研究中所获得的一些成果。

关键词:硅材料;300mm硅片;单晶硅生长技术1前言 半个世纪以来,半导体产业发展迅猛,这主要有赖于两个因素:一个是加工尺寸不断变细,提高集成度,降低器件单位成本;另一个是硅衬底尺寸不断变大,增加硅片单位面积可获得芯片的数量。

而且两个因素互相影响,互相促进发展。

加工尺寸不断变细,带动衬底材料质量不断得到改善,衬底材料的不断改善反过来又不断促进了加工尺寸变细的实现。

集成电路技术发展遵从摩尔定律,工艺线宽越来越细,并开始进入纳米时代。

当前,国际主流生产技术为0.25~0.35µm,先进生产技术为0.13~0.10µm,90nm技术已开始投入小批量生产,并研究成功65nm技术。

按照国际半导体产业发展路线图预测[1],2010年将采用45纳米技术,2016年和2018年将分别发展到22nm和18nm。

半导体硅衬底材料也正从200mm迈向300mm直径。

130nm以下的集成电路将主要使用300mm 直径的硅片,目前它的制备技术正日渐完善,以适应纳米集成电路的严格要求。

2 硅单晶的生长技术 从200mm到300mm,硅片直径增加1.5倍,晶体的重量将近似于直径的2次方增长,也就是增长大约3倍,故200mm直径硅晶锭的典型荷重为90kg,而为了获得同样多的合格硅片数量300mm 直径的硅晶锭的荷重一般达200~300kg。

晶体重量的大幅度增加,一方面要求有更大的坩埚装料和更庞大且昂贵的专门设备,从而大大增加了成本;另一方面,也使熔体流动、热量和质量传输、缺陷的形成和迁移等更为复杂,给300mm 硅单晶的生长带来了很大的困难。

另外,晶锭的提拉和搬运也成了重要问题。

硅片检验标准

好亚光伏能源有限公司文件编号:Q09-PZ-01单晶硅片检验标准.版本号:A/1 页码:第1页共4页生效日期:2009-7-15一、目的为明确产品质量要求,加强产品质量管控,使公司单晶生产成品执行的检测工作有据可依,特制定本标准。

二、适用范围适用于线切割后太阳能级单晶硅片的品质检验。

三、主要内容1、检测环境要求:温度18~28℃,湿度不大于60%。

2、硅片分类原则:项目内容A符合《硅单晶切割片企业内控标准》的硅片B物理参数合格,但外观存在:线痕、崩边、边缘、色差、外圆未磨光、尺寸不良(边长、对角线)、倒角差、厚度异常、TTV异常,且符合下表-B级品判定标准C物理参数合格,但外观存在:线痕、崩边、尺寸不良(边长、对角线)、应力、花片、污片、倒角差、厚度异常、TTV异常,且符合下表-C级品判定标准不合格品物理性能不合格或缺角、缺口、亮点、穿孔;备注:电阻率按照0.5~1Ω.cm,1~3Ω.cm,3~6Ω.cm单独包装入库2、判定标准(见下表):批准审核编制修改履历页码内容状态备注受控好亚光伏能源有限公司文件编号:Q09-PZ-01 单晶硅片检验标准版本号:A/1页码:第2页 共4页生效日期:2009-7-15内容 项目检测标准A等外品不合格品备注BC厚度T 及 厚度偏差TV 总厚度变化TTV WARP :① 180u m ±20 u m ; ② 200 u m ±20 u m ③ TTV ≤30um ; ④warp ≤50um① 180u m ±25 u m ; ② 200 u m ±25u m ③ TTV ≤40 u m ④ warp ≤50um① 180u m ±25 u m ; ② 200 u m ±25u m ③ TTV ≤40 u m ④ warp ≤50um其中厚度T 为硅片中心点厚度,TV 为一批硅片中心点厚度偏差,TTV 同一张硅片厚度最大值减去最小值,warp 为硅片的翘曲度。

单晶硅企业标准标准

0I CS企业标准硅单晶XXX有限公司发布前言本标准修改采用了Ibis Technology《美国Ibis公司硅单晶产品样本》,其他技术要求执行了GB/T 12962-2005标准。

编写格式按GB/T 1.1-2009《标准化工作导则第1部分:标准结构和编写》标准修订。

本标准于XXX 首次发布。

硅单晶1 范围本标准规定了硅单晶的产品术语、要求、试验方法、检验规则以及标志、包装、运输、贮存。

本标准适用于直拉法制备的硅单晶。

产品主要用于制作太阳能电池及其组件。

2 规范性引用文件下列文件对于本文件的应用是必不可少的。

凡是注日期的引用文件,仅所注日期的版本适用于本文件。

凡是不注日期的引用文件,其最新版本(包括所有的修改单)适用于本文件。

GB/T1550 非本征半导体材料导电类型测试方法GB/T1551 硅锗单晶电阻率测定直流二探针法GB/T1552 硅锗单晶电阻率测定直排四探针法GB/T1553 硅和锗体内少数载流子寿命测定光电导衰减法GB/T1554 硅晶体完整性化学择优腐蚀检验方法GB/T1555 半导体单晶晶向测定方法GB/T1557 硅晶体中间隙氧含量的红外吸收测量方法GB/T1558 硅中代位碳原子含量红外吸收测量方法GB/T11073 硅片径向电阻率变化的测量方法GB/T12964 硅单晶抛光片GB/T13387 电子材料晶片参考面长度测量方法GB/T14140 (所有部分)硅片直径测量方法GB/T14143 300μm-900μm硅片间隙氧含量红外吸收测量方法GB/T14844 半导体材料牌号表示方法Ibis Technology 美国Ibis公司硅单晶产品样本3 术语和定义下列术语和定义适用于本标准。

3.1 径向电阻率变化晶片中心点与偏离中心的某一点或若干对称分布的设定点(典型设定点是晶片半径的1/2处或靠近晶片边缘处)的电阻率之间的差值。

这种电阻率的差值可以表示为中心值的百分数。

又称径向电阻率剃度。

单晶硅片的技术标准

单晶硅片的技术标准1范围本要求规定了单晶硅片的分类、技术要求、包装以及检验规范等本要求适用于单晶硅片的采购及其检验。

2 规范性引用文件ASTM F42-02半导体材料导电率类型的测试方法ASTM F26半导体材料晶向测试方法F84直线四探针法测量硅片电阻率的试验方法ASTM F1391-93太阳能硅晶体碳含量的标准测试方法ASTM F121-83太阳能硅晶体氧含量的标准测试方法ASTM F 1535用非接触测量微波反射所致光电导性衰减测定载流子复合寿命的实验方法3 术语和定义TV:硅片中心点的厚度,是指一批硅片的厚度分布情况;TTV:总厚度误差,是指一片硅片的最厚和最薄的误差(标准测量是取硅片5点厚度:边缘上下左右6mm处4点和中心点);位错:晶体中由于原子错配引起的具有伯格斯矢量的一种线缺陷;位错密度:单位体积内位错线的总长度(cm/cm3),通常以晶体某晶面单位面积上位错蚀坑的数目来表示;崩边:晶片边缘或表面未贯穿晶片的局部缺损区域,当崩边在晶片边缘产生时,其尺寸由径向深度和周边弦长给出;裂纹、裂痕:延伸到晶片表面,可能贯穿,也可能不贯穿整个晶片厚度的解理或裂痕;四角同心度:单晶硅片四个角与标准规格尺寸相比较的差值。

密集型线痕:每1cm上可视线痕的条数超过5条4 分类单晶硅片的等级有A级品和B级品,规格为:125′125Ⅰ(mm)、125′125Ⅱ(mm)、156′156(mm)。

5 技术要求外观见附录表格中检验要求。

外形尺寸方片TV为200±20 um,测试点为中心点;方片TTV小于30um,测试点为边缘6mm处4点、中心1点;硅片TTV以五点测量法为准,同一片硅片厚度变化应小于其标称厚度的15%;相邻C段的垂直度:90o±;其他尺寸要求见表1。

表1单晶硅片尺寸要求图1硅单晶片尺寸示意图材料性质导电类型:硅片电阻率:见下表;硅片少子寿命:见下表(此寿命为2mm样片钝化后的少子寿命);晶向:表面晶向<100>+/°;位错密度≤3000pcs/cm2;氧碳含量:氧含量≤20ppma,碳含量≤。

300mm直拉单晶硅生长缺陷研究

300mm直拉单晶硅生长缺陷研究300mm直拉单晶硅生长缺陷研究引言:300mm直拉单晶硅生长是半导体行业中非常重要的工艺步骤之一。

然而,在这个过程中,会出现一些缺陷,对单晶硅的质量和性能产生不利影响。

对300mm直拉单晶硅生长缺陷进行详细研究是至关重要的。

一、背景介绍1.1 单晶硅的应用单晶硅作为半导体材料,在电子器件制造中广泛应用。

它具有优异的电子特性和热特性,适用于制造高性能集成电路和太阳能电池等。

1.2 300mm直拉单晶硅生长工艺300mm直拉单晶硅生长是通过将多晶硅块加热融化,并通过引入种子晶体进行快速凝固形成单晶硅棒。

这个过程需要严格控制温度、压力和气氛等参数。

二、常见缺陷类型及其影响2.1 晶界缺陷由于快速凝固过程中的温度梯度和结构变化,会导致晶界缺陷的形成。

晶界缺陷会降低单晶硅的电子迁移率和机械强度。

2.2 气泡缺陷在单晶硅生长过程中,气体溶解度会随着温度的变化而改变,导致气泡的形成。

气泡缺陷会影响单晶硅的光学特性和电子性能。

2.3 晶体结构缺陷由于生长过程中的温度梯度和结构变化,会导致晶格结构不完整,形成晶体结构缺陷。

这些缺陷会影响单晶硅的机械强度和电子特性。

三、研究方法3.1 试样制备采用标准的300mm直拉单晶硅生长工艺制备试样,并根据需要进行切割和抛光处理,以获得表面平整、无损伤的试样。

3.2 显微镜观察使用光学显微镜、扫描电子显微镜等仪器对试样进行观察,分析不同位置和深度上的缺陷类型和分布情况。

3.3 表征技术分析利用X射线衍射、拉曼光谱等表征技术,对试样的晶体结构和晶格缺陷进行分析,以了解缺陷形成的机制。

3.4 数值模拟通过数值模拟方法,模拟300mm直拉单晶硅生长过程中的温度场、应力场和流场分布等参数,以预测可能出现的缺陷类型和位置。

四、研究进展与结果4.1 晶界缺陷研究结果通过显微镜观察和数值模拟,发现快速凝固过程中的温度梯度会导致晶界缺陷的形成。

进一步研究表明,优化生长参数可以减少晶界缺陷的数量和尺寸。

硅抛光片的几何参数及一些参数定义1

硅抛光片的几何参数及一些参数定义集成电路硅片的规格要求比较严格,必须有一系列参数来表示和限制。

主要包括:硅片的直径或边长,硅片的厚度、平整度、翘曲度及晶向的测定,下面分别一一讨论。

1.硅片的直径(边长),硅片的厚度是硅片的重要参数。

如果硅片的直径(边长)太大,基于硅片的脆性,要求厚度增厚,这样就浪费昂贵的硅材料,而且平整度难于保证,对后续加工及电池的稳定性影响较大,再说单晶硅的硅锭直径也很难产生很大;直径或边长太小,厚度减小,用材少,平整度相对较好,电池的稳定性较好,但是硅片的后续加工会增加电极等方面的成本。

一般情况下,太阳能电池的硅片是根据硅锭的大小设置直径或边长的大小,一般的圆形单晶、多晶硅硅片的直径为(76.2mm)或(101.6mm),而单晶正方形硅片的边长为100mm、125mm、150mm;多晶正方形硅片的边长为100mm、150mm、210mm。

2.硅片的平整度是硅片的最重要参数,它直接影响到可以达到的特征线宽和器件的成品率。

对于太阳能硅片则影响转换效率和寿命,不同级别集成电路的制造需要不同的平整度参数,平整度目前分为直接投影和间接投影,直接投影的系统需要考虑的是整个硅片的平整度,而分步进行投影的系统需要考虑的是投影区域的局部的平整度。

太阳能硅片要求较低,硅片的平整度一般用TIR和FPD这两个参数来表示。

(1)TIR(TotalIndicationReading)表示法对于在真空吸盘上的硅片的上表面,最常用的参数是用TIR来表示。

如图一所示,假定一个通过对于硅片的上表面进行最小二次方拟合得到的参考平面,TIR 定义则为相对于这一参考平面的最大正偏差与最大负偏差之和。

TIR=a+b图一、TIR 和FPD 的定义图二、 BOW 的定义(2)FPD(Focal Plane Deviation)表示法如果选择的参考面与掩膜的焦平面一致,FPD 定义则是相对于该参考面的正或负的最大偏差中数值较大的一个,如图一所示。

300mm硅片精密化学机械抛光村几何参数优化

300mm硅片精密化学机械抛光村几何参数优化党宇星;徐继平;刘斌;叶松芳;肖清华;闫志瑞;石瑛;张果虎;周旗钢;柳滨;郭强生;王东辉【摘要】对于评价用于极大规模集成电路(ULSI)生产的300mm硅抛光片的表面质量,需要关注两个关键参数即:SRQR和GBIR。

在中国电子科技集团第四十五研究所研发的中国第一台最终化学精密抛光机的验证过程中,我们发现为了提高硅片表面的几何参数,必须监控抛光前硅片的形貌,并根据不同的硅片表面形貌来改变抛光头的区域压力。

通过深入分析抛光前硅片的表面形貌,我们发现当硅片形貌为凹陷形状时。

抛光后的硅片表面将严重恶化。

由此,根据每个硅片不同的形貌,我们用特殊设计的抛光头来调整背压的区域分布,然后再进行抛光。

最终,经过抛光头区域压力调整后的硅片几何参数比调整前得到了大幅提升,并已经能够满足我们的产品指标并可以用于生产。

%For the advanced Ultra-large Scale Integrated Circuits geometry parameters of the 300 mm prime silicon wafers: SRQR and manufacturers. During the acceptance tests of the first China-made (ULSI) manufacturing, two key GBIR are of major interest tothe final-touch chemical-mechanical machine (CMP). We find that to enhance the geometry parameters, we have to know the geometry of incoming wafers and to modify the polishing head pressure accordingly. After investigation of the geometry of the incoming wafers, we find wafers with concave thickness profile would be deteriorated seriously after final-touch CMP. According to the shape of every wafer, we vary the backing pressure distribution of our special designed polishing head. Eventually,the wafer thickness geometry after modification could fulfill our demand,which demonstrates that our own-made machine could be used in mass production.【期刊名称】《电子工业专用设备》【年(卷),期】2012(041)010【总页数】7页(P27-33)【关键词】最终化学机械抛光;硅片;极大规模集成电路;硅片几何参数;硅材料【作者】党宇星;徐继平;刘斌;叶松芳;肖清华;闫志瑞;石瑛;张果虎;周旗钢;柳滨;郭强生;王东辉【作者单位】有研半导体材料股份有限公司,北京100088;有研半导体材料股份有限公司,北京100088;有研半导体材料股份有限公司,北京100088;有研半导体材料股份有限公司,北京100088;有研半导体材料股份有限公司,北京100088;有研半导体材料股份有限公司,北京100088;有研半导体材料股份有限公司,北京100088;有研半导体材料股份有限公司,北京100088;有研半导体材料股份有限公司,北京100088/有色金属研究总院,北京100088;中国电子科技集团第四十五研究所,北京100176;中国电子科技集团第四十五研究所,北京100176;中国电子科技集团第四十五研究所,北京100176【正文语种】中文【中图分类】TN305.21 IntroductionFor more than half a century,prime silicon wafer is being used as thefundamental material for ULSI manufacturing[1~3].With the technology node of ULSI decreases to less than 20 nm and the diameter of the wafers increases to more than 300 mm,extremely tight requirements are being placed on both the shape of the prime wafer and the flatness of its surface.To fulfill thestringentrequirements in lithography device processing step during the 300 mm and below 90 nm ULSI manufacturing,the key geometry parameters are site front least square range(SFQR)and global backside ideal range(GBIR)[4].Since the demonstration of chemical mechanical polishing(CMP)in the 1960s,it has been employed as the best technique for silicon wafer thinning and planarization[5].The final-touch CMP process can be divided into one-step,two-step,and three-step types.Generally,with moresteps thepolishing could achieve higher precision.Currently,three-step polishing,which includes:rough-polishing,intermediate-polishing and final-touch CMP,is the most acceptable polishing method.The main purpose of final-touch CMP is to achieve a clean and micro-roughness-free (haze-free)surface.At the same time,to keep the variation of the wafer geometry as trivial as possible or even an improvement during final-touch CMP is also necessary[6].Recently,the first China-made 300 mm silicon wafer final-touch CMP machine was successfully made.During the qualification check,we have performed a series of experiments to ensure the quality of wafer surface could fulfill the specifications of ULSItechnology.Hereafter,we demonstrate a method to conserve or enhance the wafer thickness geometry with ourmachine.We perform experimentsby optimizing theprocessand adjusting own-designed polishing head accordingly.The effect on GBIRand SFQRvalues is analyzed with clearly different incoming geometries using a variety of polishing recipes.2 ProcessThe acceptance check flow of prime wafer processing by final-touch CMP machine is shown in Fig.1.As we can see from Fig.1,the process flow of acceptance check of prime wafer processing can be summarized as follows:Firstly,the incoming 300 mm wafer finishing up grinding and edge-polishing was measured topography of the wafer with an advanced flatness/wafer characterization system ADE AFS-3220.Secondly,the surface of the wafer was double-side polished by CMP machine SPEEDFAM20B.Thirdly,the wafer was pre-cleaned via the AKrion V3 Semi-Auto Bench with chemicals.Fourthly,which is the acceptance check step,the wafer was final-touch CMP with our own made final polishing machine PG-1201.During the polishing,the environmental temperature is constant at 20 and the humidity keeps at 46%.As we all know,it is important to maintain the environmental conditions for regular processing.There are two steps during the final-touch polishing.The first step is a rough polishing step which uses Suba 600 made by Rodel Inc.as polishing pad and SR310 made by Dupont Inc.as slurry.The second step is a finishing polish step utilizing 7355 polishing pad and Fujimi Inc.'s FGL-3900 as slurry.Before starting each polishing cycle,the polishing pad was conditioned in order to prevent the glazing effect.To verify if the topography conforms to our acceptancecheck standard,we measured the surface topography of the wafers withthe advanced flatness/wafer characterization system ADE AFS-3220.Fig.1 Process flow of the acceptance inspection process3 Results and DiscussionThe acceptance check process lasts about two months.Table 1 and Table 2 show the values and units of major parameters of platen 1 and platen 2 we first used,respectively.The major parameters include:polishingtime(T),carrier down force(DF),retaining ring force(RF),and rotation speedof platen(SP).During the experiments,we used four steps recipe.After releasing the vacuum pressure,the first step was to gradually push down the wafer on the platen with backing pressure from the carrier.The second step was the first actual polishing step with the carrier down force increases.The third step was the vital step for removing the damaged layer induced by double-side polishing.The fourth step aimed to have a super smooth surface.Table 1 Parameters for the polishing platen 1Parameter Polishing Time(T)/s Carrier Down Force(DF)/N Retaining ring force(RF)/N Rotation speed of platen(SP)/r·min-1 Step1 10 0 100 20 Step2 10 300 100 35 Step 3 90 1120 100 60 Step4 15 700 80 55Table 2 Parameters for the polishing platen 2Parameter Polishing Time(T)/s Carrier Down Force(DF)/N Retaining ring force(RF)/N Rotation speed of platen(SP)/r·min-1 Step1 10 0 100 20 Step2 10 300 100 35 Step 3 80 950 100 45 Step4 15 300 60 40According to IC manufacturer's requirement,two differentthicknessgeometry properties of polishing wafers are of the major interest.After the negotiation with our customer,the acceptance criterion for the geometry property of the wafer surface for 90 nm technology node is determined as: 1)Variation of(G)lobal(B)ackside(I)deal Focal Plane(R)ange(GBIR):If GBIR var<0,it shows that the global flatness of the wafer surface after CMP is better than that of the wafer surface before CMP.If GBIR var>0,it shows that the global flatness of the wafer surface after CMP is worse than before CMP.However,regardless how GBIRchanges,as long as the variation satisfies the condition that:the GBIRafter CMP satisfies our requirement.2)Variation of(S)ite (F)rontside Least S(Q)uares Focal Plane(R)ange(SFQR) We define:Thereby:If SFQR var<0,it demonstrates that the maximum site flatness of the wafer surface after CMP is smaller than that of the wafer surface before CMP.If SFQR var>0,it demonstrates that the maximum site flatness of the wafer surface after CMP is larger than before CMP.The acceptance check criterion of SFQRvariation for 90 nm technology node is determined as:with a site size of 25 cm×25 cm including partial size:We arranged experimental wafers as 10 pieces for each group and perform experiments according to the process flow in Fig.1.Hereafter in paragraphs and figures,we use"GBIR bef"to indicate GBIRvalue before polishing,"GBIR bef"to indicate GBIR value after polishing,and"GBIR var"to represent GBIR variation.The similar definition applies to those values of SFQR.The left primary axis is for GFQR value and the right secondary axis is for SFQRvalue.The acceptance criteria are indicated by the horizontal lines in figures.After the measurement of Lot 1,we have the results as shown in Fig.2.As sketched here,all SFQR var of the ten pieces are smaller than 0.2 μm while SFQR var of the last wafer is larger than 0.05 μm,which does not conform to the specification.Therefore,there are nine out of ten pieces of wafers qualified the test while one piece failed.Fig.2 Geometry parameters of Lot 1As to Lot 2,we have the result shown in Fig.3.As illustrated,SFQR var of the last wafer does not meet our requirement.Hence,for this lot,there are nine out of ten wafers passed the acceptance check.Fig.3.Geometry parameters of Lot 2For Lot 3,the measured results are shown in Fig.4,where we can observe that wafers No.1,4,6 are not accepted.Hence,there are seven out of ten wafers passed the acceptance check.The ratio of acceptance is about 70%. For Lot 4 to Lot 10,the measured results are shown in Fig.5.As we can see from the figure,for the 70 pieces examined,there are altogether 57 piecesof wafer passed the acceptance criteria.The ratio of acceptance reaches 81%.Fig.4 Geometry parameters of Lot 3Fig.5 Geometry parameters of Lot 4 to Lot 10However,with the time,the performance of CMP deteriorates.In Fig.6,the results of Lot 11 to Lot 15 are shown.Only 20 out of 50 pieces were accepted,which manifested that some problems existed with the present polishing process.It is worth while examining the wafers more closely. Fig.6 Geometry parameters of Lot 11 to Lot 15Let us now attempt to extend the observation into the consideration of the polishing head structure.The structure of the polishing head is revealed in Fig.7,in which the innermost two pressure rings are for backing pressure 1;the intermediate two rings are for vacuum pressure during operation;the outmost two rings are for backing pressure 2.During CMP,we set the backing pressure 1 and 2 at the same value.This brings us to the consideration of the geometries of wafers.Fig.7 The structure of the carrier headTherefore,we measured the topography of rejected wafers,which are schematized in Fig.8.As the diagram indicates,the contour of the wafer before polishing is clear concave thickness profiles.The variation of GBIR is 0.221 μm which is larger than our required 0.2 μm.It demonstrates deteriorates of the geometry.In order to achieve good geometry parameters GBIR and SFQR,we have to achieve a contour as flat as possible,or at least it should be as close to the shape before polishing.Inother words,an edge-fast removal would have beennecessary.However,under the same baking pressure values for zone 1 and zone 2,it is hard to achieve this purpose.As can be seen from the right figure in Fig.8,the contour of the wafer after polishing is even more concave.To enhance the geometry parameters after polishing,we modify the backing pressure of zone 2 to be larger than zone 1.The geometry before polishing is shown in the left figure in Fig.9.The modified recipe leads to an improved geometry which is shown in the right figure in Fig.9.As we can observe,the shape is very close to the shape before final-touch CMP and the GBIR variation is-0.178 which indicates an improvement of the geometry.Fig.8.The wafer topography before modifying backing pressure(left)before final CMP(right)after final CMPBy using the modified recipe,we polish some more wafers and the results are shown in Fig.10.As sketched here,the geometry parameters are remarkably improved.Overall,for the 50 wafers polished,there are only 3 wafers being rejected.The acceptance ratio reaches 94%.Fig.9.The wafer topography after modifying backing pressure(left)before final CMP(right)after final CMPFig.10.Geometry parameters of Lot 16 to Lot 204 ConclusionsIn this study,we have performed a qualification check on wafer geometry by using first 300 mm final-touch CMP machine made by us.The objectiveis to fulfill the requirements of the subsequent 90 nm ULSI manufacturing.For the first batch of wafers(Lot 1 to Lot 10),GBIR and SFQR variation of 82 out of 100 pieces of wafers could fulfill the requirements.However,for the subsequent Lot 11 to Lot 15,the acceptance level drastically drops to 40%.After a thoroughly investigation,we found the deterioration owing to that the incoming wafers are concave thickness diameter profiles.Thanks to our special designed structure of the polishing head,we could modify site backing pressure.As to the concave profile,an edge-fast silicon removal profile should be chosen.Following the suitable pressure distribution of the polishing head,we have improved the polishing results.Finally,corresponding to the demands of 90 nm technology node,we enhance the geometry acceptance level to 94%. REFERENCES:[1] L.C.Zhang,A.Q.Biddut,and Y.M.Ali.Dependence of pad performance on its texture in polishing mono-crystalline siliconwafers[J].Int.J.Mech.Sci.,2010(52):657-662.[2] E.S.Lee,S.C.Hwang,J.T.Lee,and J.K.Won.A study on the characteristic of parameters by the response surface method in final waferpolishing[J].Int.J.Precis.Eng.Man.,2009(10):25-30.[3] Y.L.Liu,K.L.Zhang,F.Wang,and W.G.Di.Investigation on the final polishing slurry and technique of silicon substrate inULSI[J].Microelectron.Eng.,2003(66):438-444.[4] International Technology Roadmap for Semiconductor 2006update[Z].Semiconductor Industry Association Report,Sematec Inc.(2006).[5] M.Forsberg.Effect of process parameters on material removal rate in chemical mechanical polishing ofSi(100)[J].Microelectron.Eng.,2009(77):319-326.[6] H.T.Young,H.T.Liao,and H.Yi.Surface integrity of silicon wafers in ultra precision machining[J].Int.J.Adv.Manuf.Technol.,2006(29):372-378.。

国家标准-集成电路用低密度晶体原生凹坑硅单晶抛光片-编制说明-预审稿

国家标准《集成电路用低密度-晶体原生凹坑硅单晶抛光片》(预审稿)编制说明一、工作简况1.立项目的与意义集成电路产业是信息技术产业的核心,是国家重要的基础性、先导性和战略性产业,是推动国民经济和信息化发展的主要高新技术。

近10年来,我国的集成电路产业发展迅猛,在家电、通信、汽车等行业,国内厂商获得不错的收获。

4G领域,海思半导体、展讯、联芯科技等的4G芯片逐步进入市场;高铁领域,自动控制和功率变换的核心芯片IGBT芯片实现国产化;金融卡领域,大唐微电子的金融卡芯片已经通过农业银行、光大银行等银行测试;智能硬件领域,国芯科技的数字电视芯片、华为的机顶盒和智能网关芯片等产品市场占有率稳步提高。

但是我国集成电路在CPU、存储器等高端通用芯片上与国外存在着不小的差距,目前线宽65纳米及以下的这部分高端产品几乎完全依赖进口。

随着高端集成电路市场在国内的兴起,对硅抛光片的要求越来越高,除了几何参数、颗粒、金属等重要指标外,对抛光片的颗粒和晶体原生凹坑(COP)的要求越来越高,特别是对于线宽越小的器件,清洗工艺能够洗掉硅片表面的颗粒,却不能洗掉硅片表面的COP。

COP的存在不仅会使栅氧化物的完整性(GOI)受到严重破坏,还会造成PN结漏电、槽型电容短路或绝缘失效等问题,从而降低集成电路的成品率,对后道集成电路制造产生严重的不良后果。

COP是硅单晶生长过程中形成的空洞型微缺陷,目前主要有两类控制方法,即从根源或后续工艺过程来减少或覆盖COP,从而满足对小尺寸COP敏感的集成电路要求。

本标准的制定将有利于界定和规范Low COP产品的检测指标,促进Low COP产品的研究与开发,有利于行业的统一和对产品质量的把控,也有利于与国际先进水平产品接轨,该标准的制定与实施也将有助集成电路国有化的研究与发展。

2.任务来源根据国标委综合[]号文件的要求,由有研半导体材料有限公司负责《集成电路用低密度-晶体原生凹坑硅单晶抛光片》(简称LOW-COP片)的制订工作,项目计划编号为国标委发[2019]22号20192102-469。

国家标准硅抛光片表面颗粒测试方法中国有色金属标准质量信息网

国家标准《硅抛光片表面颗粒测试方法》(讨论稿)编制说明一、工作简况1. 标准简况:近年来,随着大规模集成电路使用硅片直径的增大和品质的极大提升,衬底片表面的纳米级颗粒和微小缺陷(像COP)严重影响器件的质量,直接影响着供需双方的成品率。

因此,抛光片、外延片等镜面表面的颗粒要求已成为关键参数,也是出厂和进货检验的主要参数。

由于国内外硅抛光片外延片直径越来越多,而要求的颗粒直径越来越小,一般都要求对0.10 到0.5 微米直径的颗粒进行探测和计数。

这已经远远超过了人的肉眼可以辨别的极限,因此各企业对抛光片表面颗粒、COP等众多缺陷的检验基本上都依赖硅片表面检查系统(简称SSIS)。

在修订后的标准中体现如何正确使用该方法和设备设置,并正确评价测量结果。

使标准修订后具有更普遍的实用性。

由于颗粒的测量的主要原理是利用SSIS 产生的激光束在待测镜面晶片表面进行扫描,并收集和确定来自晶片表面的局部散射光(LLSs)的强度和位置,与事先设置的一组已知尺寸的聚苯乙烯乳胶球等效的散射光(LSE)的强度进行比较,得到晶片表面的一系列不同直径尺寸的LLS 的总数和分布,将其作为晶片表面的颗粒尺寸和数量。

换句话说,从一个未知的LLS 收到的信号相当于从一个已知尺寸的聚苯乙烯胶乳(PSL)获得的信号。

除此之外,扫描仪对散射光与反射光的区分收集和处理,也可得到晶片表面的划伤、桔皮、抛光液残留;外延片表面划伤、棱锥、乳突等大面积缺陷。

通过对晶片表面小的凸起和凹陷的辨别及其在片子上位置的分布特征,可以探测分辨出COP。

通过对检测背景信号中低频信号的处理,得到晶片表面微粗糙度的参数Haze(雾)。

因此现在的SSIS 已经可以探测镜面晶片上几乎所有类型的缺陷。

随着硅片抛光和外延工艺的不断进步,晶片表面其他大面积缺陷,像划伤、桔皮、波纹、棱锥、堆垛层错等等数量上也越来越少了。

更多的还是颗粒或者COP。

习惯上我们所有这些表面缺陷粗略的统称为颗粒。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一、300 mm硅单晶及抛光片现状

300mm硅抛光片的产品、工艺技术在国外已经很成熟。 而在我国起步较晚,还处于试验阶段。

因此对于集成电路所需的300mm硅片的基本参数指标、 金属污染和缺陷控制、表面形态与质量、成本等都面临着新 的挑战。硅材料的生产工艺、技术、检测方法已成为今后研 究的主要内容,同时也是推动产业发展的关键所在。

二、 国外涉及300mm产品标准的现状

SEMI的硅单晶的产品标准主要是抛光片规范SEMI M1。 它由一系列直径从2英寸、100mm,直到300mm,及直径 350mm和400mm硅单晶抛光片规格组成,其中只涉及了 最基本的尺寸指标:直径、厚度、晶向、切口或参考面尺 寸极其公差;弯曲度、翘曲度、总厚度变化的最大允许 值,以及轮廓的要求。并且参数都是最宽泛的。SEMI M1.15直径300mm硅单晶抛光片规格(切口)见下表所示。

0.5~50.0 ohm-cm 无 无 无

≤32ppma(旧版ASTMF121-79) 不规定

4.0 结构特性 4.1 位错蚀坑密度 4.2 滑移 4.3 系属结构 4.4 孪晶 4.5 漩涡 4.6 浅蚀坑 4.7 氧化层错(OISF) 4.8 氧化物沉淀 4.9 硅片制备特性 5.0 晶片ID标志 5.0 正表面薄膜 5.2 洁净区 5.3 非本征吸除 5.5 背封

SEMI M8是针对半导体器件制备中用作检验和工艺控制的硅 单晶抛光试验片。对2英寸到300mm的试验片的订货项目及要求。 以及0.13μm线宽的300mm试验片规范指南。

SEMI M24《优质硅单晶抛光片规范》是针对150-300mm直 径, 用于颗粒检测、金属沾污监控、和光刻工艺图形测量的硅单 晶抛光片。针对0.25-0.13μm不同线宽的要求的抛光片规格,给 出了三种不同用途硅片的项目要求。

SEMI M8中设计线宽0.13μm的300mm硅单晶抛光试验片规范指南

项目

1.0

一般特性

1.1

生长方法

1.2

晶向

1.3

导电类型

1.4

掺杂剂

1.5

标称边缘去除

2.0

电学特性

2.1

电阻率

2.2

径向电阻率变化

2.3

电阻率条纹

2.4

少数载流子寿命

3.0

化学特性

3.1

氧浓度

3.2

径向氧变化

P型试验片

CZ或MCZ 1-0-0 P型 硼 3mm

用户评估测试指标

用户评估:

1.对同一根单晶头部、中部和尾部分别切取7 片、25片和13 片,加工后 送交用户进行评估:GBIR 平均1.19um,最大的GBIR 小于2um;大部分硅 片表面〉0.12um 的颗粒数少于50 个/片。 2.送交1350 片12 英寸硅单晶抛光片于用户进行评估。 GBIR 平均 0.85um,最大的GBIR 小于1.61um;硅片表面 〉0.12um LPD平均值32.4,最 大值为80 个/片。表面金属低于1E10atoms/cm2。 3.提供的12 英寸硅抛光片用于A(Particle)、B(Super Flat)、C(Control) 和E(Mechanical)规格评估 。评估项目最关键的三项指标:表面颗粒、COP 和表面金属污染。评估结果认为:样品全部能够满足C E类片子的表面缺 陷和金属污染的要求,95.7%的片子可以满足A B类硅片的表面金属和金属 污染要求。

项目

硅片直径及允许偏差mm

硅片厚度及允许偏差 μm

总厚度变化 μm

翘曲度 μm

总平整度 μm

局部平整度(SFQR) μm (25*25)

局部光散射体 ≥0.12μm

LLSs (个/片)

≥0.16μm ≥0.2μm

表面金属 atoms/cm2

Cu/Cr/Fe/Ni/Zn Al /K/Na/Ca

指标 300±0.2 775±20 ≤2 ≤50 ≤1.0 ≤0.13 <100 <50 <20 ≤1.0e10 ≤5.0e10

单位A mm μm

+0.25, -0.00

mm

+5,-1

°

μm

μm

μm μm

表2 取向要求

特

性

切 口 中 心 线 取 向A

副参考面位置

表面取向

要求 <110>±1° 无副参考面 [100]±1°

除此之外,SEMI标准中涉及300mm的标准还有,SEMI M8 《硅单晶抛光试验片规范》, SEMI M24《优质硅单晶抛光片规 范》。标准中包含术语、订货单内容、合格证、抽样标准、详尽 的各个参数的测试方法、表面缺陷的判别标准、包装和标志的内 容,但其中也有不少项目是没有具体规定或者要求按照用户规格 或由供需双方协商。

随着300mm硅单晶及抛光片的诞生,我们也面临一个制定 相应的国家标准的问题。

有研硅股1997年成功拉制了第一根300mm硅单晶。近几年 来一直生产直径230-450mm的硅单晶。2007年生产的300mm硅 抛光片作为陪片已经通过用户的评估测试。并完成了12寸硅 外延主体设备、配套管路及检测设备的调试和外延片的研 制,样品已通过用户的测试。 下面我们给出了WACKER的产品标准;我们2006年在质量 技术监督局备案的企业标准中对300mm单晶及抛光试验片的 主要技术指标要求;以及我们生产的300mm抛光片送到用 户,用户的测试数据。

表1 尺寸和公差要求

特性

直

径

厚 度,中 心 点

切 口 (见图7)

深度

角

翘 曲 度 最 大 值B

总厚度变化(GBIR)C 最大值

背面光泽度D

抛光的边缘轮廓表面加 工度E

边缘轮廓

表3

座标:(见图4) Cy

Cx

尺寸 300.00 725

1.00 90 100 10

≥0.80

(T/4)F 194 100

公差 ±0.20 ±20

见注1 无 无 无 不规定 不规定 不规定 不规定

见注2 无 无 无 无

6.0 机械特性 6.1 直径 6.2 主基准位置 6.3 主基准尺寸 6.6 边缘轮廓 6.7 厚度 6.8 厚度变化(TTV) 6.9 晶片表面取向 6.11 翘曲度 6.12 峰——谷差 6.14 平整度/局备案的企业标准指标

项目 晶向 掺杂元素 电阻率范围Ω.cm 径向电阻率变化 氧含量 atoms/cm3 碳含量 atoms/cm3 位错密度 个/ cm3 体金属含量(Fe) atoms/cm3

指标 <100>±0.5º 硼 0.5-20 ≤10% ≤1.1e18 ≤2.0e16 ≤10 ≤5.0e10