32位乘法器

基于跳跃式Wallace树的低功耗32位乘法器

摘

要 : 了提高乘法器 的综合性能 , 3 方面对乘法器 进行 了优化设计 。 用改进的 B O 算法 生成各个部分积 , 用跳跃式 Wa ae 为 从 个 采 0t h 利 lc l

树结构进行部分积压缩 ,通过 改进的 L NG加法器对压缩结果进行求和 。在 F G 上进行 验证与测试 ,并在 O1 m MI I PA .8g S C工艺下进行逻

la fo a l c e r h t c u e t o e p r g W la e t e a c i t r O c mp e s p ri lp o u t a d i to u e h o fe N G dd r t o r e r s a ta r d c , n n d c s t e m di d LI r i a e o c mp t e fn ls m ft e r s l u e t i a u o e u tof h h

W al c e .Th e i n i e l e y u i g Ale a SFPGA . y t ss p a e n nd r u n f 3 - i u t ir a e a c mp ih d o 1 m la e t e r e d sg sr ai d b s n t r ’ z S n he i , l c me ta o t g o 2 b tm l pl c o ls e n O.8 g i i e r S I poes M C r c s .Co a e t o v n i n li l r wi r d to a a l c r e h e mu tp ir r d c s t e mu tp i a i n tme h we mp d wi c n e to a mu tp i t ta ii n lW la e te ,t l l e u e h li lc t i ,t e po r r h l e h i e o d s i a i n a d t ea e fmul p irb 9%, 8 a d 1 isp to n ao t le y 2 h r i 3 % n 7%.

32位浮点乘法器的设计与仿真代码

32位浮点乘法器的设计与仿真代码一、引言随着计算机科学和技术的不断发展,浮点乘法器在科学计算、图像处理、人工智能等领域中扮演着重要的角色。

本文将详细讨论32位浮点乘法器的设计与仿真代码,并深入探讨其原理和实现方法。

二、浮点数表示在开始设计32位浮点乘法器之前,我们首先需要了解浮点数的表示方法。

浮点数由符号位、阶码和尾数组成,其中符号位表示数的正负,阶码确定数的大小范围,尾数表示数的精度。

三、浮点乘法器的原理浮点乘法器的原理基于乘法运算的基本原理,即将两个数的尾数相乘,并将阶码相加得到结果的阶码。

同时需要考虑符号位的处理和对阶的操作。

下面是32位浮点乘法器的基本原理:1.获取输入的两个浮点数A和B,分别提取出符号位、阶码和尾数。

2.将A和B的尾数相乘,得到乘积P。

3.将A和B的阶码相加,得到结果的阶码。

4.对乘积P进行规格化,即将小数点左移或右移,使其满足规定的位数。

5.对结果的阶码进行溢出判断,若溢出则进行相应的处理。

6.将符号位与结果的阶码和尾数合并,得到最终的浮点乘积。

四、浮点乘法器的设计根据浮点乘法器的原理,我们可以开始进行浮点乘法器的设计。

设计的关键是确定乘法器中各个部件的功能和连接方式。

下面是浮点乘法器的设计要点:1.输入模块:负责接收用户输入的两个浮点数,并提取出符号位、阶码和尾数。

2.乘法模块:负责将两个浮点数的尾数相乘,得到乘积P。

3.加法模块:负责将两个浮点数的阶码相加,得到结果的阶码。

4.规格化模块:负责对乘积P进行规格化操作,使其满足规定的位数。

5.溢出判断模块:负责判断结果的阶码是否溢出,并进行相应的处理。

6.输出模块:负责将符号位、阶码和尾数合并,得到最终的浮点乘积。

五、浮点乘法器的仿真代码为了验证浮点乘法器的设计是否正确,我们需要进行仿真测试。

下面是一段简单的浮点乘法器的仿真代码:module floating_point_multiplier(input wire [31:0] a,input wire [31:0] b,output wire [31:0] result);wire [31:0] mantissa;wire [7:0] exponent;wire sign;// 提取符号位assign sign = a[31] ^ b[31];// 提取阶码assign exponent = a[30:23] + b[30:23];// 尾数相乘assign mantissa = a[22:0] * b[22:0];// 规格化assign {result[30:23], result[22:0]} = {exponent, mantissa};// 处理溢出always @(*)beginif (exponent > 255)result = 32'b0; // 结果溢出为0else if (exponent < 0)result = 32'b0; // 结果溢出为0elseresult[31] = sign;endendmodule六、浮点乘法器的应用浮点乘法器在科学计算、图像处理、人工智能等领域中有着广泛的应用。

乘法器原理

乘法器原理乘法器原理是计算机科学中非常重要的原理,它是实现计算机高效计算的基础。

本文将详细介绍乘法器原理的相关知识,包括乘法器的基本概念、实现原理、应用场景等方面。

一、乘法器的基本概念乘法器是一种用于计算两个数的乘积的计算机硬件。

它是计算机中最常用的算术电路之一,可以用来进行乘法运算,是实现计算机高效计算的关键组件之一。

乘法器通常由多个门电路组成,其中最常用的是AND门、OR门和XOR门。

它的输入是两个二进制数,输出是它们的乘积。

乘法器的输出通常是一个二进制数,它的位数等于输入的两个二进制数的位数之和。

乘法器的输出可以通过一系列的加法器进行加法运算,从而得到最终的结果。

乘法器的性能取决于它的位宽、延迟和功耗等因素。

在实际应用中,乘法器的位宽通常是32位或64位,延迟时间通常在几个时钟周期内,功耗通常在几个瓦特以下。

二、乘法器的实现原理乘法器的实现原理可以分为两种,即基于布斯算法的乘法器和基于蒙哥马利算法的乘法器。

1、布斯算法乘法器布斯算法乘法器是一种基于移位和加法的乘法器。

它通过将一个数分解成多个部分,然后逐位进行计算,最后将它们相加得到最终结果。

布斯算法乘法器的核心是部分积的计算,它可以通过移位和相加操作来实现。

例如,假设要计算两个8位二进制数A和B的乘积,可以将A和B分别分解成4位二进制数A1、A0和B1、B0,然后按照如下方式计算部分积:P1 = A1 × B0P2 = A0 × B1P3 = A0 × B0P4 = A1 × B1最终的结果可以通过将这些部分积相加得到:P = P1 × 2^8 + P2 × 2^4 + P3 + P4 × 2^12布斯算法乘法器的主要优点是简单、易于实现,但它的缺点是速度较慢,需要多次移位和加法操作。

2、蒙哥马利算法乘法器蒙哥马利算法乘法器是一种基于模重复平方和模乘的算法。

它利用模运算的性质,将乘法转化为模运算和加法运算,从而减少了乘法器的复杂度和延迟时间。

乘法器和除法器

手工进行乘法运算

×

2 3 4 5 9 8 7 6 11 4 20 27 30

手工进行乘法运算

手工进行乘法运算

×

? ? ? ? ? ? ? ? ? 2 3 4 5 9 8 7 6 114 20 27 30 ? ? ? ? ? ? ? ? ? ? ? ? ??

较为简单的数字

× 1 0 0 0 1 0 0 1 1 0 0 0

Shift right

8-bit Adder

Multiplier

0 1 0 0

4-bit

Write

0 0 0 0 1 0 0 0

8-bit

Product

Control test

乘法器的工作过程(2)

0 0 0 1 0 0 0 0

8-bit Multiplicand

Shift left

第2轮

1 0 0 0 two × 1 0 0 1two

0 0 0

乘积 Product

十进制和二进制运算的选择

采用十进制的ENIAC 采用二进制的EDVAC

十进制和二进制运算的选择

电子管是一种“全或无”设备( allor-none ),适合表示只有两个数值 的系统,即二进制。 二进制可以大幅度地简化乘法和除法 的运算过程。尤其是对于乘法,不再 需要十进制乘法表,也不再需要两轮 的加法。 关于EDVAC的 报告草案 1945 必须要记住,十进制才是适合人使用 约翰· 冯· 诺依曼 的。因此,输入输出设备需要承担二 John Von Neumann 进制和十进制之间的转换工作。 1903~1957

简化后的运算过程

× 0 0 0 1 0 0 1 0 0 1 1 1 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0

基于改进型选择进位加法器的32位浮点乘法器设计

基于改进型选择进位加法器的32位浮点乘法器设计作者:刘容赵洪深李晓今来源:《现代电子技术》2013年第16期摘要:在修正型Booth算法和Wallace树结构以及选择进位加法器的基础上,提出了一种新型32位单精度浮点乘法器结构。

该新型结构通过截断选择进位加法器进位链,缩短了关键路径延时。

传统选择进位加法器每一级加法器的进位选择来自上级的进位输出。

提出的结构可以提前计算出尾数第16位的结果,它与Wallace树输出的相关位比较就可得出来自前一位的进位情况进而快速得到进位选择。

在Altera的EP2C70F896C6器件上,基于该结构实现了一个支持IEEE754 浮点标准的4级流水线浮点乘法器,时序仿真表明,该方法将传统浮点乘法器结构关键路径延时由6.4 ns减小到5.9 ns。

关键词:修正Booth算法; Wallace树结构;选择进位加法器;浮点乘法器中图分类号: TN702⁃34 文献标识码: A 文章编号: 1004⁃373X(2013)16⁃0133⁃04浮点乘法器是数字处理器的重要组成单元,它的性能直接关系到整个数字系统的性能。

所以浮点乘法器一直以来是人们研究的热点。

而乘法器的设计主要是对速度、面积、功耗等因素的优化与折中。

Booth 算法大大缩小了部分积数量;Wallace tree、dadda tree等压缩树结构实现部分积的并行求和提高了乘法器的速度,进位保留加法器(Carry Save Adder,CSA)则实现最终两个部分积的快速求和。

文献[1]基于乘法器各级核心器件是加法器的思想,通过优化加法器减小了乘法器的延时。

文献[2]设计了一种改进的基4 Booth编码和华莱士树的24位符号定点乘法器,在功耗和面积降低的同时,延时也得到了减小,做到了芯片性能和设计复杂度之间的良好折中。

文献[3]提出了一种适用于FPGA结构的改进型Wallace tree架构乘法器,实现了资源和性能的合理平衡。

高速乘法器的性能比较简介对基于阵列乘法器修正布斯算法(mba)乘法

高速乘法器的性能比较简介:对基于阵列乘法器、修正布斯算法(MBA)乘法器、华莱士(WT)乘法器和MBA-WT混合乘法器的四种架构的32位乘法器性能进行了比较,在选择乘法器时,应根据实际应用,从面积、速度、功耗等角度权衡考虑乘法是数字信号处理中重要的基本运算。

在图像、语音、加密等数字信号处理领域,乘法器扮演着重要的角色,并在很大程度上左右着系统性能。

随着实时信号处理的提出和集成电路工艺水平的进步,人们开始致力于高速乘法器设计。

最 初,阵列乘法采用移位与求和算法,部分乘积项(Partial Product, PP)数目决定了求和运算的次数,直接影响乘法器的速度。

修正布斯算法(Modified Booth Algorithm, MBA)对乘数重新编码,以压缩PP。

华莱士树(Wallace Tree, WT)结构改变求和方式,将求和级数从O(N)降为O(logN),提高了运算速度,但是WT存在结构不规整,布线困难的缺点。

用4:2压缩器(4:2 compressor)代替全加器(FA)可以解决这一问题。

将MBA算法和WT结构的优点相结合,形成了MBA-WT乘法器。

以下1~4节将分别介绍阵列乘法器、MBA乘法器、WT乘法器、MBA WT乘法器。

最后对四种乘法器的性能进行比较,并总结全文。

1 阵列乘法器阵 列乘法器基于移位与求和算法。

被乘数与乘数中的某一位相乘,产生一组PP,将该组PP移位,使LSB与乘数对应位对齐;求出全部PP,并相应移位;对所有 PP 求和,得到乘积。

因此,加法阵列结构非常重要。

CRA (Carry Ripple Adder)存在进位问题,运算速度慢。

CSA (Carry Save Adder)将本级进位传至下级,求和速度快,且速度与字长无关。

阵列乘法器中,CSA把PP阵列缩减至Sum和Carry两项,再用高速加法 器求和得积。

阵列乘法器结构规范,利于布局布线。

因 为乘数和被乘数可正、可负,所以一般用二进制补码表示,以简化加、减运算。

fx2n 32位乘法指令

fx2n 32位乘法指令FX2N 32位乘法指令是一种在FX2N系列可编程控制器中常用的指令,用于实现32位数据的乘法运算。

该指令的设计旨在提供高效、精确且可靠的乘法运算功能,以满足工业控制系统对数据处理的需求。

在工业自动化领域,乘法运算是一项常见且重要的操作。

许多应用场景需要对不同设备的数据进行乘法运算,以实现各种控制策略。

例如,在液位控制系统中,需要根据液位传感器的数据和设定值之间的差异来控制阀门的开度,从而维持液位在设定范围内。

而在电机控制系统中,需要根据电机的转速和负载之间的关系来调整电机的输出功率。

这些场景中,乘法运算是必不可少的一步。

FX2N 32位乘法指令通过将两个32位数据相乘,得到一个64位的结果。

由于FX2N系列控制器的位数限制,无法直接使用64位数据进行计算。

因此,该指令将结果拆分成两个32位数据,分别存储在两个寄存器中。

这种设计可以有效地解决位数限制的问题,同时保证计算结果的准确性。

在使用FX2N 32位乘法指令时,需要注意以下几点。

首先,需要提前准备好要进行乘法运算的两个32位数据,并将其分别存储在指定的寄存器中。

其次,在进行乘法计算之前,需要先将两个数据加载到乘法器中。

然后,使用乘法指令执行乘法运算,并获取结果。

最后,根据需要,可以将结果存储在指定的寄存器中,以便后续的数据处理和控制操作。

FX2N 32位乘法指令的设计考虑了运算速度和计算精度的平衡。

在进行乘法运算时,指令会自动进行数值的扩展和截断,以确保结果的准确性。

同时,该指令采用了高效的算法和硬件支持,能够在短时间内完成复杂的乘法计算。

这种高效性和准确性使得FX2N系列控制器在工业自动化领域得到了广泛的应用。

除了乘法指令本身,FX2N系列控制器还提供了其他丰富的指令和功能,以满足不同应用场景的需求。

例如,可以通过逻辑指令实现与、或、非等逻辑运算;通过数学指令实现加减乘除运算;通过比较指令实现大小判断等。

这些指令的组合和应用,可以实现各种复杂的控制策略和算法。

32位乘法器 c语言

32位乘法器 c语言32位乘法器C语言实现概述:32位乘法器是一种用于执行32位乘法运算的电路或程序。

在数字信号处理、计算机视觉、图像处理等领域,32位乘法器是非常常见的。

本文将介绍如何使用C语言实现一个32位乘法器。

I. 算法原理在计算机中,通常使用二进制数表示数字。

因此,我们可以将两个32位二进制数相乘得到一个64位的结果。

然而,由于CPU只能处理有限的位数,所以我们需要将这个结果截断为低32位和高32位两部分。

具体来说,设A和B分别为两个32位二进制数,则它们的乘积可以表示为:A ×B = (a31 × 2^31 + a30 × 2^30 + ... + a1 × 2^1 + a0 × 2^0) × (b31 × 2^31 + b30 × 2^30 + ... + b1 × 2^1 + b0 × 2^0)= (a31b0 + a30b1 + ... + a1b30 + a0b31)×2^31 +(a31b1 + a30b2 + ... + a1b31)×2^30 +(a31b2 + a30b3+ ...+a3b30+a2b31)×2^29 +... +(a24b7+a23b8+...+a8b23+a7b24)×2^8 +(a15b16+a14b17+...+a1b31)×2^1 +(a0b31)其中,ai和bi分别为A和B的第i位二进制数。

可以看出,这个乘积的低32位部分为:L = a0b31 + (a1b30 << 1) + (a2b29 << 2) + ... + (a30b1 << 30) + (a31b0 << 31)而高32位部分为:H = (a31b0 + a30b1 + ... + a0b31) + (a31b1 + a30b2 + ... +a1b31)×2^1 +(a31b2 + a30b3+ ...+a3b30+a2b31)×2^2 +... +(a24b7+a23b8+...+a8 b23+a7 b24 )×2^23II. C语言实现下面是一个使用C语言实现32位乘法器的示例代码。

stc32g 硬件乘除法

stc32g 硬件乘除法摘要:1.STC32G 简介2.硬件乘法器3.硬件除法器4.应用实例正文:【1.STC32G 简介】STC32G 是一款高性能、低功耗的32 位单片机,广泛应用于各种嵌入式系统中。

它内部集成了丰富的硬件功能,如硬件乘除法器等,为开发者提供了极大的便利。

【2.硬件乘法器】STC32G 硬件乘法器可以实现两个16 位数据的乘法运算,其运算结果为32 位。

使用硬件乘法器可以大大提高乘法运算的速度,减轻CPU 的负担。

要使用硬件乘法器,需要先设置相应的控制和状态寄存器(CSSR),然后通过指针寄存器(PTR)指向待乘数据。

在完成乘法运算后,结果会自动存储在指定的寄存器中。

【3.硬件除法器】STC32G 硬件除法器可以实现两个16 位数据的除法运算,其运算结果为32 位。

使用硬件除法器同样可以提高除法运算的速度,减轻CPU 的负担。

要使用硬件除法器,需要先设置相应的控制和状态寄存器(CSSR),然后通过指针寄存器(PTR)指向待除数据和商寄存器。

在完成除法运算后,商和余数会自动存储在指定的寄存器中。

【4.应用实例】假设我们要计算两个16 位整数相乘的结果,我们可以按照以下步骤使用STC32G 的硬件乘法器:1.设置CSSR 寄存器,使能硬件乘法器。

2.将待乘数1 和待乘数2 分别存储在指定的寄存器中。

3.设置PTR 寄存器,使其指向待乘数1 和待乘数2。

4.启动硬件乘法器。

5.硬件乘法器完成运算后,结果会自动存储在指定的寄存器中。

通过以上步骤,我们可以轻松地实现硬件乘法器的使用。

同样地,对于硬件除法器,我们也可以按照类似的步骤进行操作。

32位乘法器 c语言

32位乘法器简介在计算机科学中,乘法运算是一个基本且常见的操作。

为了实现快速且准确的乘法运算,计算机中有专门的电路和算法来实现乘法操作。

本文将讨论如何使用C语言编写一个32位乘法器,介绍其原理、实现方法和效果。

原理32位乘法器是指可以将两个32位的二进制数相乘,并得出结果的电路或算法。

乘法运算的基本原理是将两个数的每一位相乘,并将结果相加。

实现方法下面介绍如何使用C语言编写一个32位乘法器。

步骤1:定义变量和输入首先,我们需要定义两个32位的无符号整数作为输入。

可以使用C语言的unsigned int类型来表示这两个数。

unsigned int num1, num2;然后,我们需要从用户输入中获取这两个数的值。

可以使用C语言的scanf函数来实现。

printf("请输入第一个数:");scanf("%u", &num1);printf("请输入第二个数:");scanf("%u", &num2);步骤2:实现乘法运算接下来,我们使用C语言的乘法运算符(*)来计算两个数的相乘结果。

unsigned long long result = (unsigned long long)num1 * num2;由于两个32位的数相乘可能会得到一个64位的结果,我们需要将结果存储在一个64位的变量中。

可以使用unsigned long long类型来表示这个变量。

需要注意的是,在C语言中,两个32位的数相乘得到的结果是一个32位的数,因此我们需要使用强制类型转换将其转换为64位的数。

步骤3:输出结果最后,我们使用printf函数将乘法运算的结果输出。

printf("乘法运算的结果为:%llu\n", result);需要注意的是,在格式字符串中,我们使用%llu来表示64位的无符号整数。

功能测试通过输入不同的数进行测试,验证32位乘法器的正确性和准确性。

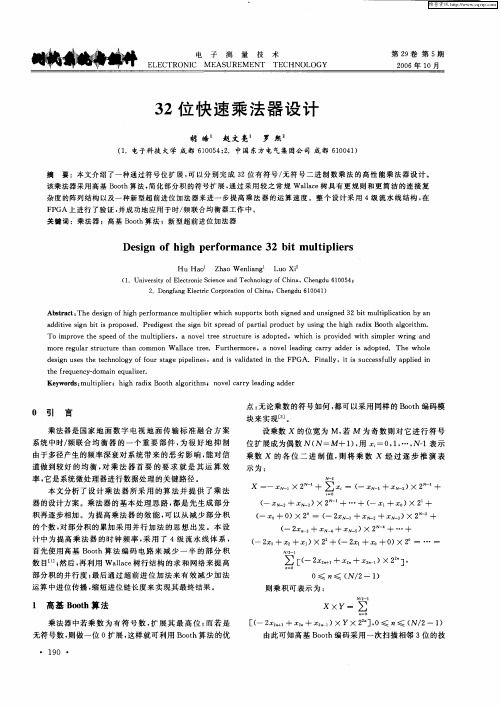

32位快速乘法器设计

De i n o g r o m a c 2 b t m u tp i r s g f hi h pe f r n e 3 i l i le s

Hu H a o Z a e l n h oW ni g a Lu o Xi

( .Un v r iy o e t o i inc n c no o y o i a,Ch n d 0 5 1 i e st fEl c r n c Sce e a d Te h l g fCh n e g u 61 0 4; 2 .Do g a g El c rc Co p r to fCh na n f n e t r o a i n o i ,Ch n u 6 00 ) i e gd 1 41

第6O 2年5 0第 21 0月 9 期 卷

摘

要 :本文介绍了一种通过符号位扩展 , 以分别完 成 3 可 2位有 符号/ 无符号 二进 制数 乘法 的高性 能乘 法器设 计 。

该 乘 法 器 采 用 高 基 B oh算 法 , 化 部 分 积 的符 号 扩 展 , 过 采 用 较 之 常 规 W al e 具 有 更 规 则 和 更 简 洁 的 连 接 复 ot 简 通 lc 树 a

Ab t a t Th e i n o i h p ro ma c l p irwh c u p r sb t in d a d u i n d 3 i mu t l a in b n sr c : e d sg f g e f r n e mu t l ih s p o t o h sg e n ns e 2 b t h i e g li i t y a p c o a d tv i n b ti p o o e .P e i e tt e sg i s r a fp r il r d c y u i g t eh g a i o t l o ih . d i es i s rp s d i g r d g s h i n b t p e d o a t o u tb sn h i h r d x B o h a g rt m ap To i r v h p e ft e mu tp ir ,a n v lt e t u t r s a o t d,wh c s p o i e t i p e ig a d mp o e t e s e d o h l l s o e r e s r c u e i d p e i e i h i r vd d wi sm l r wrn n h mo e r g l rs r c u e t a o r e u a tu t r h n c mmo a l c r e Fu t e mo e a n v lla i g c r y a d r i a o t d Th o e n W l e te. a rh r r , o e e d n a r d e s d p e . e wh l d sg s st e t c n lg ff u t g i e i e ,a d i a i a e n t e FP e i n u e h e h o o y o o rs a e p p l s n s v l t d i h GA. Fi al ,i i s c e s u l p l d i n d nl y t s u c s f ly a p i n e t e fe u n y d ma n e u l e . h rq e c - o i q ai r z Ke wo d : li l r h g a i o t l o ih ; n v l a r e d n d e y r s mu tp i  ̄ i h r d x B o h ag r m e t o e c r y la i g a d r

3.10硬件乘法器芯片资料

}

硬件乘法器 —— 应用举例(3/6)

◆例2、利用硬件乘法器计算两个16位无符号整数的乘积,

__bis_SR_register(LPM4_bits);// Nhomakorabea入LPM4

// 调试用,验证结果是否正确,正确结果RESLO == 0x0060

//RESHI == 0x0626

__no_operation();

}

硬件乘法器 —— 应用举例(2/6)

◆用库函数调用,实现例1相同功能

相关程序如下:

➢结果扩展寄存器SUMEXT的内容取决于乘法器的操作,如下表所 列。如果操作数是16位或更短时,32位结果决定符号和进位位。如

果其中一个操作数大于16位,则结果为64位。

硬件乘法器 —— 操作(6/10)

➢MPYC位反映了乘法器的进位,如下表所列,如果没有选择小数模式或者饱和模式,

则该位可以作为结果的第33位或第65位。对于MAC或者MACS操作,MPYC位反映32 位或64位累积的进位,不作为MAC和MACS连续操作的33位或第65位。

相关程序如下:

#include <msp430f6638.h>

void main(void)

{

WDTCTL = WDTPW+WDTHOLD; // 关闭看门狗定时器 MPY = 0x1234; //载入第一个无符号整型操作数,表明是无符号乘法

OP2 = 0x5678; //载入第二个无符号整型操作数后,开始运算

硬件乘法器 —— 操作(8/10)

➢可以通过如下图所示右移小数点来增大表示的范围。16位有符号的

Q14格式可以表示从–2.0 到 1.999938965≈2.0的数。

➢乘法器采用16位有符号Q15或32位Q31的好处是:两个在-1.0 到 1.0范围内的两个数的乘积总是在同一范围内。 ➢

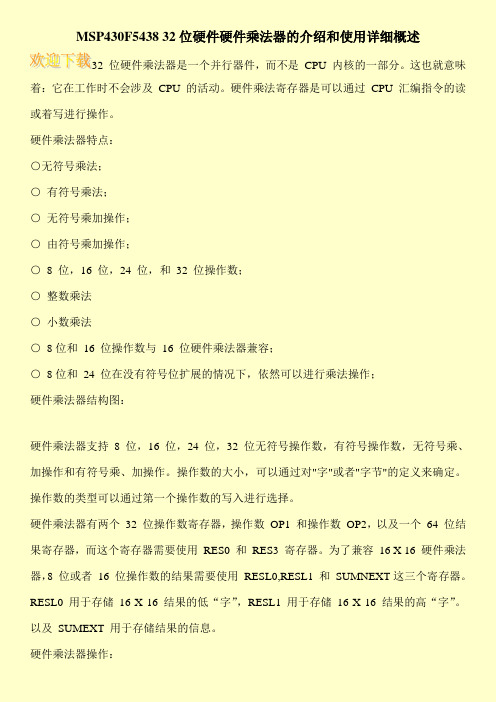

MSP430F5438 32位硬件硬件乘法器的介绍和使用详细概述

MSP430F5438 32位硬件硬件乘法器的介绍和使用详细概述

32 位硬件乘法器是一个并行器件,而不是CPU 内核的一部分。

这也就意味着:它在工作时不会涉及CPU 的活动。

硬件乘法寄存器是可以通过CPU 汇编指令的读或着写进行操作。

硬件乘法器特点:

○无符号乘法;

○有符号乘法;

○无符号乘加操作;

○由符号乘加操作;

○8 位,16 位,24 位,和32 位操作数;

○整数乘法

○小数乘法

○8位和16 位操作数与16 位硬件乘法器兼容;

○8位和24 位在没有符号位扩展的情况下,依然可以进行乘法操作;

硬件乘法器结构图:

硬件乘法器支持8 位,16 位,24 位,32 位无符号操作数,有符号操作数,无符号乘、加操作和有符号乘、加操作。

操作数的大小,可以通过对"字"或者"字节"的定义来确定。

操作数的类型可以通过第一个操作数的写入进行选择。

硬件乘法器有两个32 位操作数寄存器,操作数OP1 和操作数OP2,以及一个64 位结果寄存器,而这个寄存器需要使用RES0 和RES3 寄存器。

为了兼容16 X 16 硬件乘法器,8 位或者16 位操作数的结果需要使用RESL0,RESL1 和SUMNEXT这三个寄存器。

RESL0 用于存储16 X 16 结果的低“字”,RESL1 用于存储16 X 16 结果的高“字”。

以及SUMEXT 用于存储结果的信息。

硬件乘法器操作:。

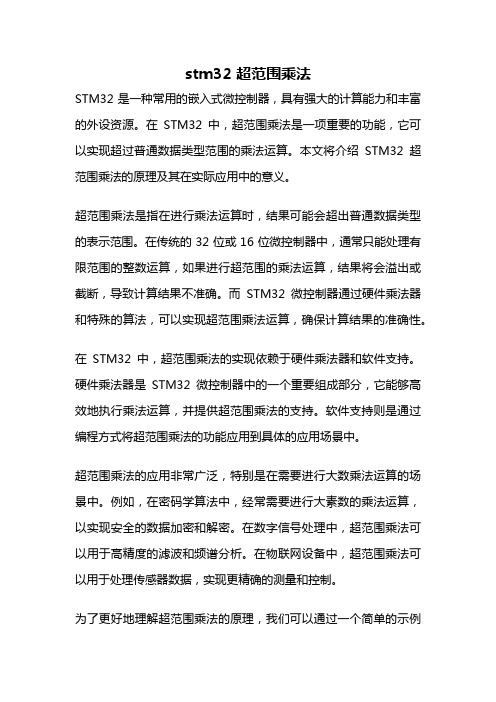

stm32 超范围乘法

stm32 超范围乘法STM32是一种常用的嵌入式微控制器,具有强大的计算能力和丰富的外设资源。

在STM32中,超范围乘法是一项重要的功能,它可以实现超过普通数据类型范围的乘法运算。

本文将介绍STM32超范围乘法的原理及其在实际应用中的意义。

超范围乘法是指在进行乘法运算时,结果可能会超出普通数据类型的表示范围。

在传统的32位或16位微控制器中,通常只能处理有限范围的整数运算,如果进行超范围的乘法运算,结果将会溢出或截断,导致计算结果不准确。

而STM32微控制器通过硬件乘法器和特殊的算法,可以实现超范围乘法运算,确保计算结果的准确性。

在STM32中,超范围乘法的实现依赖于硬件乘法器和软件支持。

硬件乘法器是STM32微控制器中的一个重要组成部分,它能够高效地执行乘法运算,并提供超范围乘法的支持。

软件支持则是通过编程方式将超范围乘法的功能应用到具体的应用场景中。

超范围乘法的应用非常广泛,特别是在需要进行大数乘法运算的场景中。

例如,在密码学算法中,经常需要进行大素数的乘法运算,以实现安全的数据加密和解密。

在数字信号处理中,超范围乘法可以用于高精度的滤波和频谱分析。

在物联网设备中,超范围乘法可以用于处理传感器数据,实现更精确的测量和控制。

为了更好地理解超范围乘法的原理,我们可以通过一个简单的示例来说明。

假设我们需要计算两个超过32位的整数的乘法结果,传统的32位微控制器无法直接处理这个运算。

但是在STM32中,我们可以利用硬件乘法器和软件支持来实现超范围乘法。

具体的步骤如下:1. 将两个超过32位的整数分割成多个32位的部分,例如将64位整数分割成两个32位的部分。

2. 使用硬件乘法器执行32位整数的乘法运算,得到中间结果。

3. 使用软件支持将多个32位的中间结果进行累加,得到最终的乘法结果。

通过这种方式,STM32可以有效地处理超范围的乘法运算,并得到准确的结果。

除了超范围乘法,在STM32中还有其他一些相关的功能,如超范围加法和超范围减法。

32位高速浮点乘法器优化设计

集成电路设计与开发n墨i乒mdD目幛l叩m∞IofIc32位高速浮点乘法器优化设计周德金1,孙锋2,于宗光2(1.江南大学信息工程学院,江苏无锡214036;2.中国电子科技集团公司第五十八研究所,江苏无锡214035)摘要:设计了一种用于频率为200MHz的32位浮点数字信号处理器(DSP)中的高速乘法器。

采用修正B∞tll算法与wa‰e压缩树结合结构完成Carrysum形式的部分积压缩,再由超前进位加法器求得乘积。

对乘法器中的4.2压缩器进行了优化设计,压缩单元完成部分积压缩的时间仅为1.47曲,乘法器延迟时间为3.5哪。

关键词:浮点乘法器;Bootll编码;4.2压缩器;超前进位加法器中图分类号:TN332.22文献标识码:A文章编号:1003.353x(200r7)10J0000.04Des咖ofa32.bitIIigh-Speednoa铀g-PoiIltMultiplierzHouDe.jinl,suNFen92,Yuz叽分gua孑(1.删钿m砌nE喈打姗{嗜,瑚t豇l如,SD砒册毙rlg娩‰妙,阢硝2l加36,嘶u;2.77le58山脑凹旆触出地,凹粥,‰i214035,C越眦)Abs仃act:Allig}I-speedmultiplierin200MHz32bitnoating—pointDSP啪8p陀鸵nted.M0d正edb∞tllalgoritllm如dtlleWallacetr∞wem岫edto剐ucetllec盯rys盯epaItialproductto蛐matldc邺r、nect0坞,aca玎ylook-alleadadd盯w∞d鹤ignedtocon、rerttlIe8岫“c缸ryve=cto糟tofinalfom蚍.Theope珀tir唔cycletin抡oftllecoⅡlpre鹪ionuIliti81.47n8by叩tiIIIi五ngthe4—2coⅡ甲r嘲晦。

基4BOOTH编码的高速32×32乘法器的设计与实现

中图分类号 TP332. 2+2

文献标识码 A

A High-Speed 32×32 b Multiplier I mplementation Using I mpr oved Radix-4 Booth Coder s

ZHOU Wan-ting and LI Lei

(Research Inst itute of Electroni c Science and Technol ogy, University of Electronic of Science and Technology of China Chengdu 610054)

收稿日期:2008 03 04 作者简介:周婉婷(1982 ),女,硕士生,主要从事检测技术方面的研究.

增刊

周婉婷 等: 基 4 BOOTH 编码的高速 32×32 乘法器的设计与实现

107

32 b之间的算法中,基4 BOOTH算法在具有高速特

性的同时仍能保持低功耗。

设乘数为B,基4 BOOTH算法原理为:

n2

∑ B = bn 1 2n 1 + bk 2k =

k=0

2n 1

2n 1

∑ ∑ (b2k + b2 k 1 2b2k +1 )22 k =

Ek 2 2k

(1 )

k =0

k= 0

式中 Ek 为乘数被划分后的值。基4 BOOTH编码需

要乘பைடு நூலகம்是奇数位,如果是偶数,则需要在最后一位

加一 个0 。由 式( 1)可 知,基4BO O TH 编码 可以 减少 一

Vol.37 suppl Jun. 2008

基 4 BOOTH编 码 的 高 速 32×32乘 法 器 的 设 计 与 实 现

Wallace树乘法器

1 概述

在专用集成电路设计中,面积小但功能强大的CPU内核 可以为设计提供很大的方便。而乘法器是CPU中的一个重要 部件,其速度和面积直接影响整个CPU的性能。自文献[1]提 出Booth乘法器后,就不断有人提出基于Booth算法的乘法器 设计,但乘法器的处理过程大致相同,都是先生成部分积然 后进行相加。本文针对乘法器的设计特点,从改进Booth二阶 算法、跳跃式Wallace树[2]和LING加法器[3]3 个方面对乘法器 进行了优化设计。在硬件实现上,改进Booth二阶算法编码电 路简单,部分积的产生速度快、功耗小;与传统Wallace树相 比,跳跃式Wallace树部分积的压缩速度快,减少了电路内部 的伪翻转,动态功耗得到明显的降低;LING加法器与常见的 加法器相比在速度上具有明显的优势,能够有效实现对压缩 结果的相加,使整体性能得到明显提升。实验结果表明,本 文设计的乘法器可以满足高性能的处理要求。

基于改进4-2压缩结构的32位浮点乘法器设计

基于改进4-2压缩结构的32位浮点乘法器设计

邵磊;李昆;张树丹;于宗光;徐睿

【期刊名称】《微计算机信息》

【年(卷),期】2007(023)009

【摘要】本文介绍一种用于高性能DSP的32位浮点乘法器设计,通过采用改进Booth编码的树状4-2压缩器结构,提高了速度,降低了功耗,该乘法器结构规则且适合于VLSI实现,单个周期内完成一次24位整数乘或者32位浮点乘.整个设计采用Verilog HDL语言结构级描述,用0.25um单元库进行逻辑综合.完成一次乘法运算时间为24.30ns.

【总页数】3页(P224-225,199)

【作者】邵磊;李昆;张树丹;于宗光;徐睿

【作者单位】214036,江苏无锡,江南大学信息工程学院;214036,江苏无锡,江南大学信息工程学院;214035,江苏无锡,中国电子集团第58研究所;214035,江苏无锡,中国电子集团第58研究所;214035,江苏无锡,中国电子集团第58研究所

【正文语种】中文

【中图分类】TP332.2

【相关文献】

1.基于CTGAL电路的绝热4-2压缩器和乘法器设计 [J], 汪鹏君;徐建;戴静

2.基于改进型选择进位加法器的32位浮点乘法器设计 [J], 刘容;赵洪深;李晓今

3.基于改进4—2压缩结构的32位浮点乘法器设计 [J], 邵磊;李昆;张树丹;于

宗光;徐睿

4.32位并行浮点乘法器设计 [J], 张菁

5.基于混合压缩结构的新型浮点乘法器设计 [J], 姚上上;沈立

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

32位乘法器逻辑原理图:

实验原理:乘法可以通过逐渐项相加原理来实现。

从被乘数的最低位开始,若为1则乘数左移后与上一次的和相加;若为0左移后以全零相加,直至被乘数的最高位。

32位移位相加乘法器运算数据时序图:

工作原理:clr信号的上跳沿及其高电平有两个功能,即模块regsht清零和被乘数dina[31.。

0]向移位寄存器shft加载;它的低电平则作为乘法使能信号,clk为乘法时钟信号。

当被乘数加载于32位右移寄存器shft后,随着每一时钟节拍,最低位在前,由低位到高位逐位移出。

当为1时,4位乘法器and32打开,32位乘数din[31..0]在同一节拍进入加法器,与上一次存在regsht的数相加,其和在下一时钟节拍的上升沿被锁进此锁存器。

而当被乘数的移出位为0时,此and32全零输出。

如此反复,直至32个时钟脉冲后,最后乘积完整出现在regsht端口。