直接数字频率合成(DDS)方法

直接数字频率合成器(DDS)总结

直接数字频率合成器(直接数字频率合成器(DDS DDS DDS)总结)总结知识收集2008-07-2113:45:46阅读128评论0字号:大中小订阅直接合成法是用一个或多个石英晶体振荡器的振荡频率作为基准频率,由这些基准频率产生一系列的谐波,这些谐波具有与石英晶体振荡器同样的频率稳定度和准确度;然后,从这一系列的谐波中取出两个或两个以上的频率进行组合,得出这些频率的和或差,经过适当方式处理(如经过滤波)后,获得所需要的频率。

DDS 是直接数字式频率合成器(Direct Digital Synthesizer )的英文缩写。

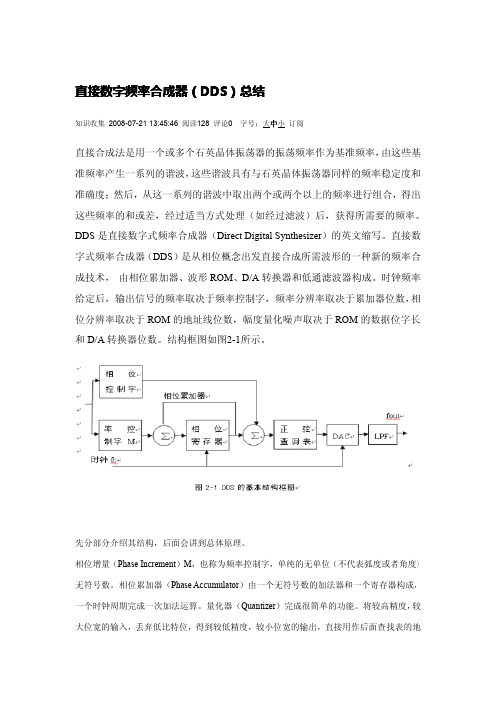

直接数字式频率合成器(DDS )是从相位概念出发直接合成所需波形的一种新的频率合成技术,由相位累加器、波形ROM 、D/A 转换器和低通滤波器构成。

时钟频率给定后,输出信号的频率取决于频率控制字,频率分辨率取决于累加器位数,相位分辨率取决于ROM 的地址线位数,幅度量化噪声取决于ROM 的数据位字长和D/A 转换器位数。

结构框图如图2-1所示。

先分部分介绍其结构,后面会讲到总体原理。

相位增量(Phase Increment )M ,也称为频率控制字,单纯的无单位(不代表弧度或者角度)无符号数。

相位累加器(Phase Accumulator )由一个无符号数的加法器和一个寄存器构成,一个时钟周期完成一次加法运算。

量化器(Quantizer )完成很简单的功能。

将较高精度,较大位宽的输入,丢弃低比特位,得到较低精度,较小位宽的输出,直接用作后面查找表的地址。

正余弦查找表(Sine/Cosine Lookup Table)存放正余弦数值。

DDS的工作原理:DDS的基本原理是利用采样定理,通过查表法产生波形[2]。

由于,(2-1)其中Δθ为一个采样间隔ΔT之间的相位增量,采样周期,即:(2-2)控制Δθ就可以控制不同的频率输出。

Δθ是由频率控制字M控制的,即:(2-3)所以改变M就可以得到不同的输出频率。

如何进行电路的频率合成和分析

如何进行电路的频率合成和分析电路的频率合成和分析是电子领域中的重要技术,它在通信、无线电、音频处理等领域有广泛的应用。

本文将介绍如何进行电路的频率合成和分析。

一、频率合成频率合成是指通过某种技术或装置,将多个频率的信号按照一定的规律组合成一个新的信号。

常见的频率合成方法有锁相环(PLL)和直接数字频率合成(DDS)两种。

1. 锁相环(PLL)锁相环是一种广泛应用于频率合成的技术,它通过反馈控制的方式将输入信号和参考信号的频率和相位同步。

锁相环通常由相位比较器、调频器(VCO)、低通滤波器和分频器组成。

相位比较器用于比较输入信号和参考信号的相位差,得到一个误差信号。

该误差信号被送入调频器,调频器根据误差信号来调整输出频率,使其与参考信号保持同步。

调频器的输出信号经过低通滤波器滤波后作为反馈信号送回相位比较器。

通过不断调整和反馈,最终实现了频率的合成。

2. 直接数字频率合成(DDS)直接数字频率合成是一种通过数字方式生成信号的方法。

它利用数字信号处理技术,将输入的数字相位信号转换为相应的模拟频率信号。

DDS一般由相位累加器、查找表和数字控制模块组成。

相位累加器是DDS的核心部件,它用于产生相位累加序列。

根据输入的相位控制信号,相位累加器不断累加,得到不同的相位值。

查找表将相位累加器输出的相位值映射到具体的幅度值,从而得到对应的模拟频率信号。

数字控制模块用于控制相位累加器的工作模式和频率分辨率。

二、频率分析频率分析是对信号频率成分进行分析和测量的过程。

常用的频率分析方法包括傅里叶变换和频谱分析仪。

1. 傅里叶变换傅里叶变换是一种将时域信号转换为频域信号的数学方法。

通过傅里叶变换,可以将复杂的信号分解为多个不同频率的正弦波成分。

傅里叶变换的结果是频谱,用于表示信号中各频率成分的幅度和相位信息。

2. 频谱分析仪频谱分析仪是一种专门用于测量和分析信号频谱的设备。

它通过将输入信号变换到中频范围,并采用滤波、增益和检波等技术,最终显示出信号在频率和幅度上的分布情况。

DDS直接数字频率合成器

西安邮电学院验证方案一、总体验证方案1.系统功能描述:8×256的单口RAM完成256个8位计数器,计数器的初值分别为0-255,时钟频率为10MHz,计数器计数频率为5/256MHz。

具体功能:RAM的每一个存储器都可以实现0-255的计数功能,并且数码管显示当前工作的寄存器中的数据。

当一个计数周期后,寄存器中的数据跳回初始状态,并且自动开始工作。

二、具体模块的验证方案1.时钟分频模块1)功能描述:该模块把系统外部输入的信号clk(10MHZ)进行二分频,输出系统时钟clk_2(5MHZ)。

代码:module div_2 (clk_2,clk,div_set);output clk_2;input div_set;input clk;reg clk_2;always @ (posedge clk or posedge div_set)beginif (div_set)clk_2<=1'b0;elseclk_2=~clk_2;endendmodule2)具体验证:i.分频控制信号(div_set=0)时输出频率(clk_2)的始终为0。

ii.分频控制信号(div_set=1)时输出信号(clk_2)与系统外部输入信号(clk)的频率满足二分频关系。

2.计数器模块1)功能描述:计数器可以实现0-255的自加功能,当一个计数周期完后,自动开始下一个计数周期。

代码:module count(in,en,clk_2,out,set);input [7:0] in;input en,clk_2,set;output out;reg [7:0] out;always @ (set)out<= in;always@(posedge clk_2)if(set)out<=8'b00000000;elseif(en)out<=out+1;elseout<=out;endmodule3.单口RAM模块1)功能描述:该RAM有256个存储器,当复位信号ram_set的电平为底时,存储器地址归零。

直接数字频率合成技术DDS

幅

位

度

码

码

数模变换器 DAC

时 钟

低通滤波器 LPF 输出

图3-11 相位/幅度变换装置

假设DAC的输入幅度码是四位,则它的输出幅度与输 入幅度码之间的关系是按线性变化的,如表3-1所示。

二进制幅度码 0000 0001 0010 0011 0100 0101 0110 0111

表 3-1

十进制幅度 二进制幅度码

0.1875

0 +1.1875

续表 3 - 4

8 1000 17π/16 -0.1951 0011 0.1875 1 9 1001 19π/16 - 0.5556 1001 0.5625 1 10 1010 21π/16 - 0.8316 1101 0.8125 1 11 1011 23π/16 -0.9808 1111 0.9375 1 12 1100 25π/16 -0.9808 1111 0.9375 1 13 1101 27π/16 -0.8316 1101 0.8125 1 14 1110 29π/16 -0.5556 1001 0.5625 1 15 1111 31π/16 -0.1951 0011 0.8175 1

② 将模2π的累加相位变换成相应的正弦函数值的幅度, 这里幅度可先用代码表示,这可以用一只读存储器ROM来 存储一个正弦函数表的幅值代码;

③ 用幅度代码变换成模拟电压,这可由数模变换器 DAC来完成;

④ 相位累加器输出的累加相位在两次采样的间隔时间 内是保持的,最终从DAC输出的电压是经保持的阶梯波。

2. 相位与幅度的变换

累加器输出的相位码,需先经过一个相位码/幅度码变换 装置之后,再经数/模变换生成阶梯波,最后通过低通滤波 器才能得到所需的模拟电压。

直接数字频率合成技术(DDS)

DDS直接数字频率合成技术

2, 采用分立IC电路系统实现,一般有CPU, RAM, ROM, D/A, CPLD, 模拟滤波器等组成

3, CPLD,FPGA实现

•用QuartusII采用原理图输入来完成顶层设计。 •相位累加器调用lmp_add_sub加减法器或用HDL实现 •波形存储器(ROM)通过调用lpm_rom元件实现,其LPM_FILE 的值*.mif是一个存放波形幅值的文件。注意,利用波形幅值的奇、 偶对称特性,最多可以节省3/4的资源。 •频率控制字与频率之间的转换可以调用乘除法模块实现 •波形存储器设计主要考虑的问题是其容量的大小,这是非常可观 的。

超宽的相对宽带

超高的捷变速率(可实现跳频)

超细的分辨率

相位的连续性

输出波形灵活

可编程全数字化

杂散来源主要有:相位累加器相位舍位误差 造成的杂散;幅度量化误差(由存储器有限

字长引起)造成的杂散和DAC非理想特性造

但存在杂散大的缺点 成的杂散。

频率上限目前还只能达到数百兆

(主要是受DAC速度的限制)

DDS直接数字频率合成技术

DDS直接数字频率合成技术

设相位累加器的位宽为N, Sin表的大小为2p,累加器的 高P位用于寻址Sin表.

时钟频率为fc, 若累加器按步进M累加直至溢出,称M 为频率控制字。

高P位作为地址

ROM

······

波形数据 累加

频率控制字M

DDS直接数字频率合成技术

▪相位累加器

DDS系统的核心是相位累加器,它 由一个加法器和一个相位寄存器组成; 每来一个时钟,相位寄存器以步长增 加,相位寄存器的输出与频率控制字 (M)相加,然后输入到正弦查询表地址 上。

EDA课程设计直接数字频率合成器(DDS)

,a click to unlimited possibilities

汇报人:

目录

01 添 加 目 录 项 标 题

02 D D S 的 原 理

03 D D S 的 硬 件 实 现

04 D D S 的 应 用

05 D D S 的 软 件 仿 真 与实现

06 D D S 的 优 化 与 改 进

医疗领域:用于 医疗设备的信号 处理和传输

军事领域:用于 雷达、通信、电 子对抗等设备的 信号处理

工业领域:用于 工业自动化设备 的信号处理和控 制

Part Five

DDS的软件仿真与 实现

软件仿真工具介绍

MATL AB:强大的数学计算和图形处理 能力,适合进行信号处理和仿真

Simulink:MATL AB的扩展工具,可以 进行系统级仿真,支持DDS模块

DDS的动态范围扩展

动态范围扩展原理:通过调整DDS的输出电压和频率,实现动态范围的 扩展 动态范围扩展方法:采用数字信号处理技术,如滤波、放大、压缩等

动态范围扩展效果:提高DDS的输出信号质量,降低噪声和失真

动态范围扩展应用:在通信、雷达、电子对抗等领域具有广泛应用

THANKS

汇报人:

DDS的频率分辨率优化

频率分辨率定义:衡 量DDS性能的重要参 数,表示输出信号的 频率精度和稳定度。

优化方法1:采用高 精度的参考时钟源, 提高时钟频率,减小 DDS的相位截断误差。

优化方法2:增加相 位累加器的位数,扩 大频率调制的范围, 提高频率分辨率。

优化方法3:采用数 字滤波技术,对DDS 输出信号进行滤波处 理,减小杂散分量, 提高频率分辨率。

实际应用:通过对DDS的相位噪声 进行降低,可以提高信号的纯度, 减小干扰和失真,从而提高通信、 雷达、电子对抗等系统的性能。

DDS原理及仿真

DDS原理及仿真DDS(Direct Digital Synthesis)直接数字合成是一种通过数字信号处理器(DSP)或者微处理器实现频率合成的方法,它可以生成高精度、稳定和可调节的连续频率信号。

DDS技术是一种广泛应用于无线通信、雷达、测量仪器等领域的频率合成技术。

本文将详细介绍DDS的原理及仿真方法。

DDS是通过以下几个基本组成部分来实现频率合成的:1. 相位累加器(Phase Accumulator):相位累加器是DDS的核心组件之一,它用于产生一个连续变化的相位信号。

相位累加器将一个初始相位值作为输入,并在每个时钟周期内按照设定的相位增量进行累加。

相位累加器的输出用于更新、控制数字控制振荡器(Digital Control Oscillator,DCO)的输出频率。

2. 数字控制振荡器(Digital Control Oscillator):DCO是DDS的另一个核心组件,它根据相位累加器的输出计算并产生一个数字化的频率信号。

DCO的输出被转换成模拟信号后为DDS系统提供频率源。

3. 相位加法器(Phase Adder):相位加法器主要用于将相位累加器输出的相位信号和相位修正信号进行相加,从而实现频率的调制或增强。

4. 数字控制字寄存器(Digital Control Word Register):数字控制字寄存器用于存储并传输DDS的相位增量值。

通过改变相位增量值,可以调节DDS系统的输出频率。

DDS仿真方法:DDS系统的设计和验证通常需要借助仿真工具来进行,以确保系统性能和可靠性。

下面介绍一种常用的DDS仿真方法。

1. 建立模型:首先,根据DDS系统的硬件规格和设计要求,建立一个仿真模型。

这个模型可以使用MATLAB、Simulink等建模软件来搭建,通过连线、添加模块等操作来构建一个完整的DDS系统。

2.添加输入信号:为DDS系统添加一个输入信号,该输入信号包含频率、幅度等参数,代表DDS的控制信号。

直接数字式频率合成器DDS

/dzdgdq/jsqy/40028.shtml/view/229432.htm?fr=ala0_1/view/38405.htm?fr=ala0_1_1直接数字式频率合成器DDS2010-04-25 18:06直接数字频率合成技术(Direct DigitalFrequencySynthesis,即DDFS,一般简称DDS)是从相位概念出发直接合成所需波形的一种新的频率合成技术。

DDS的工作原理是以数控振荡器的方式,产生频率、相位可控制的正弦波(SineWave)。

电路一般包括基准时钟、频率累加器、相位累加器、幅度/相位转换电路、D/A转换器和低通滤波器(LPF)。

其中,频率累加器对输入信号进行累加运算,产生频率控制数据(Frequency Data或相位步进量Phase Increment)。

相位累加器由N位全加器和N位累加寄存器级联而成,对代表频率的二进制码进行累加运算,是典型的反馈电路,产生累加结果Y。

幅度/相位转换电路实质是一个波形存储器(WaveformMemory),以供查表使用。

读出的数据送入D/A转换器和低通滤波器。

具体工作过程如下:每来一个时钟脉冲Fclk,N位加法器将频率控制数据X与累加寄存器输出的累加相位数据相加,把相加后的结果Y送至累加寄存器的输入端。

累加寄存器一方面将在上一时钟周期作用后所产生的新的相位数据反馈到加法器的输入端,以使加法器在下一时钟的作用下继续与频率控制数据X相加;另一方面,将这个值作为取样地址值送入幅度/相位转换电路(即波形存储器),幅度/相位转换电路根据这个地址值输出相应的波形数据。

最后,经数/模转换(D/AConverter)和低通滤波器(LowPass Filter)将波形数据转换成所需要的模拟波形。

相位累加器在基准时钟的作用下,进行线性相位累加,当相位累加器累加满量时就会产生一次溢出,这样就完成了一个周期,这个周期也就是DDS合成信号的一个频率周期。

直接数字频率合成器DDS的实现方法

收稿日期:2000201210作者简介:郭刚(19562),男,河南郑州人,河南省电子规划研究院高级工程师。

文章编号:100423918(2000)022*******直接数字频率合成器(DDS )的实现方法郭 刚1, 胡新华2(1.河南省电子规划研究院,河南郑州 450008;2.郑州市乐金科技发展有限公司,河南郑州 450003)摘 要:分析了直接数字频率合成器的基本算法和误差。

研究了用可编程逻辑器件实现直接数字频率合成器的方法。

提出了工程应用中注意的问题。

关键词:直接数字频率合成器;分频器;除法器;减计数器;超前借位中图分类号:TN784 文献标识码:A在科学实验或工程应用中,我们可能会需要一个可以连续调整频率的信号源。

例如在一个步进电机控制系统中,步进电机的转速范围是0.01转/秒~几十转/秒,转速绝对误差≤0.005转/秒。

那么就需要信号源的频率能从几Hz 到10kHz 之间连续变化;并且在任意一频率点时,频率绝对误差小于0.01Hz 。

如果使用模拟锁相环的方法来实现就是非常困难的;采用直接数字频率合成器(Direct Digital Frequency Synthesis 简称DDS )技术,就可以很容易的实现上述要求。

直接数字频率合成技术是70年代发展起来,但是因为工艺和成本等原因,一直没有进入实用。

随着人们对通信技术、自动控制技术的要求越来越高,直接数字频率合成技术显示出了广阔的应用情景。

和模拟锁相环技术相比,数字直接分频技术具有信号响应速度快,相位调整方便,误差小的优点。

1 直接数字频率合成器基本原理 我们在通过数字技术得到某一目标频率f d 时,一般情况下是需要有一个基准频率源f 0,一个分频系数为m 0的分频器。

分频器的分频系数和基准频率、目标频率有如下关系:m 0=f 0÷f d (1)令人遗憾的是分频器的分频系数只能是整数,所以在一般情况下,实际分频系数m 1,并不等于需要的分频器分频系数m 0,他们有如下关系:m 1=int (m 0)≤m 0(2)因此,我们只能通过分频器得到的实际频率f d1,也就有f d1≥f d 。

直接数字频率合成(DDS)方法

摘要多功能信号发生器是信号发生器中的一种,广泛应用于电子测量、电力工程、物矿勘探、医疗、振动分析、声学分析、故障诊断及教学科研等多方面,是工程师进行产品研发和生产的必备仪器之一。

它的主要功能是为待测设备提供稳定、可靠并可以人工调节和控制的信号源。

本文采用由美国学者J.TierncyC.M.Rader和B.Gold1971年提出来的直接数字频率合成(DDS)方法,在CPLD可编程逻辑器件利用VHDL编写波形发生程序,实现多功能信号发生器。

本课题设计的多功能信号发生器利用CPLD可在线编程的特点、DDS的原理,可以实现多种频率、相位的方波、正弦波、三角波、锯齿波,甚至任意波形。

在输出端接入可编程运放后,还能实现多种幅值的波形。

关键词:多功能信号发生器 DDS 可编程逻辑器件 VHDL 数字系统设计AbstractThe multi-function signal take place the machine to is in the signal occurrence machine a kind of, being apply in the electronics to measure extensively, the electric power engineering, the thing mineral 勘 explore, medical treatment, vibration analysis, the voice learns analysis, breaks down to examine a patient and the teaching research etc. is various, is one of the essential instruments that the engineer carries on the product development and produce.Its main function is for treat to measure the equipments to provide the stability, the credibility is also can with the signal of artificial regulate and control source.The direct numerical frequency that this literary grace use to be put forward by the American scholar J.TierncyC.M.Rader and B.Gold1971 year synthesize( DDS) the method, making use of the VHDL plait to write a form occurrence procedure in the CPLD programmable logic machine piece, carrying out the multi-function signal occurrence machine.Multi-function signal the occurrence machine of this topic design make use of CPLD can on-line plait distance of principle of characteristics, DDS, can carry out various frequencies, mutually the square wave, sine wave, triangle wave, the teeth of a saw wave of, even arbitrarily a form.After exportation carry connect to go into the programmable luck to put, can still carry out a form for be worth of various. Keywords:Multi-functional signal generator DDS CPLD VHDL The design of digital system目录第一章:绪论 (4)§1.1设计要求 (4)§1.2信号发生器的发展历史 (4)§1.3我国信号发生器市场现状 (5)第二章:多功能信号发生器的设计 (6)§2.1设计指导思想 (6)§2.2信号发生器的构成 (7)§2.3波形发生设计 (8)§2.1.1方波的发生 (8)§2.1.2锯齿波的发生 (8)§2.1.3三角波的产生 (9)§2.1.4正弦波的产生 (9)§2.1.5各种波之间的切换 (10)§2.4信号仿真波形 (11)§2.5数字信号的数模转换 (12)第三章:结论 (14)§3.1多功能信号发生器的功能 (14)§3.2多功能信号发生器的改进思想 (14)第四章:谢辞 (15)第五章:参考文献 (16)第一章绪论测量仪器从宏观上可分为两大类,即激励和检测,其中激励仪器主要是各类信号发生器。

DDS技术及应用

4、 AD9851的应用举例 解:当外部参考时钟频率为30MHz的情况 下,如果要满足以下几种技术要求: (1)6倍参考时钟倍乘器工作; (2)相位置于11.25°; (3)选择power2up模式; (4)输出信号频率为10M Hz。

(8)相位可调,可接收来自单片机的5位相位控制字。

2 AD9851引脚功能

AD9851为28引脚表帖元件,其引脚 排列如下所示。

D0~D7,8位数据输入口,可给内部寄存 器装入40位控制数据。 PGND,6倍参考时钟倍乘器地。 PVCC,6倍参考时钟倍乘器电源。 W-CL K,字装入信号,上升沿有效。 FQ-UD,频率更新控制信号,时钟上升沿确 认输入数据有效。

fo=fc*K/2N

当K=1时,DDS为最小频率输出,则DDS的最小频率分 辨率可达:

Δf= fc*1/2N

四、DDS芯片9851功能介绍

1、AD9851主要特性如下:

(1)单电源工作(+2.7~+5.25V);

(2)工作温度范围-45~85℃; (3)低功耗,在180M Hz系统时钟下,功率为555mW。电源设置有

3.1基于FPGA正弦信号发生器

采用计数的方法产生地址信号,波形存 储器根据地址信号将数据读出,然后经过D/A 转换和滤波器将数字量转换为模拟信号;而 且还可以通过改变计数器的参数,改变地址 信号,实现频率连续可调。

基准时钟 (频率f)

计数(地 址发生器)

正弦波数据存 储ROM

D/A转换

滤波器

3.2直接数字频率合成(DDS)技术及应用

DDS的数学模型可归结为;在每一个时钟周期2兀内, 频率控制字K(FrequencyControlWords)与N比特相位累加器 累加一次,并同时对2N取模运算,得到的和(以N位二进制数 表示)作为相位值,以二进制代码的形式去查询正弦函数表 ROM,将相位信息转变成相应的数字量化正弦幅度值, ROM输出的数字正弦波序列再经数模转换器转变为阶梯模 拟信号,最后通过低通滤波器平滑后得到一个纯净的正弦模 拟信号。当DDS中的相位累加器计数大于2N时,累加器自动 溢出最高位,保留后面的N比特数字于累加器中,即相当于 做模余运算。可以看出:该相位累加器平均每2N /K个时钟周 期溢出一次。可见K和时钟频率f共同决定着DDS输出信号f 的频率值,它们之间的关系满足。

DDS是什么意思DDS结构DDS原理是什么

DDS是什么意思DDS结构DDS原理是什么DDS是Direct Digital Synthesis(直接数字合成)的缩写,是一种通过数字技术实现精确频率合成的方法。

它是一种基于数字信号处理的频率合成技术,通过数字计算产生具有可变频率和可控幅度的信号。

DDS结构是由相位累加器、频率控制字寄存器、相位修正器、乘法器和低通滤波器等组成。

其中,相位累加器是DDS结构的核心部分,用于积累上一个时刻的相位和当前时刻的相位增量。

频率控制字寄存器用于存储控制合成频率的参数,相位修正器用于实现相位的调整,乘法器用于将相位修正后的信号与合适的参考信号相乘,低通滤波器用于滤除乘法器输出中的高频成分,得到最终合成的信号。

DDS原理是基于一定的采样率对输入的频率和幅度进行数字化处理,将输入波形分成很多个小的时间片段,对每个时间片段进行采样,然后通过数学运算将这些离散的采样值合成为连续的波形。

具体来说,DDS原理包括以下几个步骤:1.选择合适的采样率:采样率决定了精度和频率范围。

一般来说,采样率应是合成频率的几倍,以确保能够包含足够的频率信息。

2.数字化输入信号:将输入信号经过模数转换器(ADC)转变为数字信号,以便在数字系统中进行处理。

3.相位累加器:相位累加器用于积累上一个时刻的相位和当前时刻的相位增量,根据相位累加器的值可以确定输出波形的相位。

4.频率控制:通过控制频率控制字寄存器中的参数,可以改变合成的频率。

5.相位修正:相位修正器用于对输出波形的相位进行修正,以消除相位误差。

6.乘法器:将相位修正后的信号与合适的参考信号进行乘法运算,得到合成的信号。

7.低通滤波器:为了得到平滑的输出信号,将乘法器输出的信号经过低通滤波器进行滤波,去除高频成分。

通过这些步骤,DDS可以实现高精度的频率合成,且合成频率范围广,精度高,输出稳定性好。

它在通信领域、测试仪器、测量设备等领域有广泛的应用。

基于matlab的直接数字频率合成DDS的仿真

数字信号处理课程设计:题目一:DDS(直接数字频率合成)原理及仿真姓名:王鹏飞学号:专业:光学工程一、设计目的利用Matlab软件编程实现DDS(直接数字频率合成技术)。

二、DDS原理1、DDS简介自20世纪70年代以来,由于大规模集成电路的发展及计算机技术的普及,开创了另一种频率合成方法——直接数字频率合成法(DDS即Direct Digital Frequency Synthesis)。

它突破了模拟频率合成法的原理,从“相位”的概念出发进行频率合成这种方法不仅可以给出不同频率的正弦波,而且还可以给出初始相位的正弦波,甚至可以给出各种任意波形。

这在模拟频率合成法中是无法实现的。

相比传统频率合成技术,DDS具有如下一些优点:⑴频率分辨率高,输出频点多,可达2的N次方个频点(N为相位累加器位数);⑵频率切换速度快,可达us量级;⑶频率切换时相位连续;⑷可以输出宽带正交信号;⑸输出相位噪声低,对参考频率源的相位噪声有改善作用;⑹可以产生任意波形;⑺全数字化实现,便于集成,体积小,重量轻。

在各行各业的测试应用中,信号源扮演着极为重要的作用。

但信号源具有许多不同的类型,不同类型的信号源在功能和特性上各不相同,分别适用于许多不同的应用。

目前,最常见的信号源类型包括任意波形发生器,函数发生器,RF信号源,以及基本的模拟输出模块。

信号源中采用DDS技术在当前的测试测量行业已经逐渐称为一种主流的做法。

2、DDS基本原理图1 以ROM(正弦查询表)为基础组成的DDS原理图在正弦波1周期内,按相位划分为若干等分,将各相位所对应的幅值A按二进制编码并存入ROM中。

把1周期60等分,由于正弦波一周期为奇对称,半周期为偶对称,因此ROM中只需存储0到π/2范围内的幅值码。

若以一周期60等分计算,在0到π/2之间共有15等分,其幅值在ROM中共占16个地址单元。

因为24=16,所以可按4位地址吗对数据ROM进行寻址。

现设幅值码为5位,则在0到π/2范围内编码关系如表1所示。

直接数字频率合成知识点汇总(原理_组成_优缺点_实现)

直接数字频率合成知识点汇总(原理_组成_优缺点_实现)直接数字频率合概述DDS同DSP(数字信号处理)一样,也是一项关键的数字化技术。

DDS是直接数字式频率合成器(Direct Digital Synthesizer)的英文缩写。

DDS 是从相位概念出发直接合成所需要波形的一种新的频率合成技术。

直接数字频率合成是一种新的频率合成技术和信号产生的方法,具有超高速的频率转换时间、极高的频率分辨率分辨率和较低的相位噪声,在频率改变与调频时,DDS能够保持相位的连续,因此很容易实现频率、相位和幅度调制。

此外,DDS技术大部分是基于数字电路技术的,具有可编程控制的突出优点。

因此,这种信号产生技术得到了越来越广泛的应用,很多厂家已经生产出了DDS专用芯片,这种器件成为当今电子系统及设各中频率源的首选器件。

直接数字频率合成原理工作过程为:1、将存于数表中的数字波形,经数模转换器D/A,形成模拟量波形。

2、两种方法可以改变输出信号的频率:(1)改变查表寻址的时钟CLOCK的频率,可以改变输出波形的频率。

(2)、改变寻址的步长来改变输出信号的频率.DDS即采用此法。

步长即为对数字波形查表的相位增量。

由累加器对相位增量进行累加,累加器的值作为查表地址。

3、D/A输出的阶梯形波形,经低通(带通)滤波,成为质量符合需要的模拟波形。

直接数字频率合成系统的构成直接数字频率合成主要由标准参考频率源、相位累加器、波形存储器、数/模转换器、低通平滑滤波器等构成。

其中,参考频率源一般是一个高稳定度的晶体振荡器,其输出信号用于DDS中各部件同步工作。

DDS的实质是对相位进行可控等间隔的采样。

直接数字频率合成优缺点优点:(1)输出频率相对带宽较宽输出频率带宽为50%fs(理论值)。

但考虑到低通滤波器的特性和设计难度以及对输出信号杂散的抑制,实际的输出频率带宽仍能达到40%fs。

(2)频率转换时间短DDS是一个开环系统,无任何反馈环节,这种结构使得DDS的频率转换时间极短。

dds

直接数字频率合成(Direct Digital Frequency Synthesis,DDS)技术是一种新的全数字的频率合成原理,它直接从相位出发合成所需的波形。

其建立在采样定理的基础上,首先对需要产生的波形进行采样,将采样值数字化后存入存储器作为查找表,然后再通过查表将数据读出,经过D/A转换器转换成模拟量,把存入的波形重新合成出来。

它具有频率切换速度快、频率分辨率高、相位可连续线性变化、生成的正弦/余弦信号正交特性等特点,并且其数字压控振荡器NCO的相位、幅度均得以数字化。

1 DDS基本工作原理DDS主要由相位累加器、波形存储器、数模转换器、低通滤波器构成,如图1所示。

其中,相位累加器由N位加法器与N位累加寄存器级联构成,如图2所示。

每当输入一个采样时钟脉冲,相位累加器的输出就增加一个步长的相位量B△θ,在波形存储器中存储着一张正弦函数查询表,对应不同的相位码输出相位不同的幅度编码。

D/A转换器将数字量形式的波形幅值转换成模拟量形式。

低通滤波器用于滤除不需要的取样分量,以便输出频谱纯净的正弦波信号。

相位累加器是整个DDS的核心,它的输入是相位增量B△θ,而B△θ与输出频率fout的关系是:B△θ=2N·(fout/fclk)。

相位累加器的输入即是频率字输入,当系统基准时钟fclk为2N时,B△θ就等于fout。

频率字输入经过一组同步寄存器,使得当频率字改变时不会干扰相位累加器的正常工作。

2正弦频率源设计本文设计的软件正弦频率源是基于DDS技术的正弦信号发生器和任意序列信号发生器,其设计框图如图3所示。

其中,正弦ROM查找表完成fsin(Bθ)的查表转换,它的输入是相位调制器的输出,事实上就是ROM的地址值,输出送往D/A,转化成模拟信号。

由于相位调制器的输出数据位宽M也是ROM的地址位宽,因此在实际的DDS结构中N往往很大,而M总为10左右,M太大会导致ROM容量的成倍上升。

3任意序列信号发生器设计要实现数字调制,正弦频率源模块还需要产生序列信号,如伪随机序列,其在扩频通信系统中起着十分关键的作用。

dds芯片使用方法

dds芯片使用方法DDS芯片是一种数字直接频率合成器(Direct Digital Synthesizer),用于产生高精度的时钟信号和频率合成。

DDS芯片通常由一个数字控制器、相位累加器、频率增量器、相位转换器和数字模拟转换器(DAC)等核心部件组成。

DDS芯片的使用方法如下:1. 设置基础频率:DDS芯片的工作基于一个基础频率,通常通过将基础频率值写入芯片内部的寄存器来设置。

这个基础频率决定了输出信号的频率范围,可以根据需要进行调整。

2. 设置相位累加器:相位累加器是DDS芯片中的关键组件,用于控制输出信号的相位。

通过写入相位累加器的数值,可以设置输出信号的相位。

相位累加器的数值可以根据需要进行递增或递减,从而实现相位的变化。

3. 设置频率增量器:频率增量器用于控制输出信号的频率。

通过设置频率增量器的数值,可以实现输出信号频率的递增或递减。

频率增量器的数值通常与基础频率相乘,从而得到最终的输出信号频率。

4. 设置相位转换器:相位转换器用于将相位累加器的数值转换为DAC的输入信号。

通过相位转换器,DDS芯片可以将数字控制的相位信息转换为模拟信号输出。

5. 进行数字模拟转换:DDS芯片的输出信号是一个模拟信号,需要通过数字模拟转换器(DAC)将数字信号转换为模拟信号。

通过设置DAC的输入值,可以控制输出信号的幅值。

6. 输出信号:设置完以上参数后,DDS芯片就可以输出一个高精度的时钟信号和频率合成信号。

输出信号可以通过芯片的输出端口进行接收和使用。

DDS芯片的使用方法相对简单,只需要设置好基础频率、相位累加器、频率增量器和相位转换器等参数,就可以产生所需的时钟信号和频率合成信号。

由于DDS芯片具有高精度、灵活性强的特点,被广泛应用于通信、仪器仪表、无线电和声音合成等领域。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

摘要多功能信号发生器是信号发生器中的一种,广泛应用于电子测量、电力工程、物矿勘探、医疗、振动分析、声学分析、故障诊断及教学科研等多方面,是工程师进行产品研发和生产的必备仪器之一。

它的主要功能是为待测设备提供稳定、可靠并可以人工调节和控制的信号源。

本文采用由美国学者J.TierncyC.M.Rader和B.Gold1971年提出来的直接数字频率合成(DDS)方法,在CPLD可编程逻辑器件利用VHDL编写波形发生程序,实现多功能信号发生器。

本课题设计的多功能信号发生器利用CPLD可在线编程的特点、DDS的原理,可以实现多种频率、相位的方波、正弦波、三角波、锯齿波,甚至任意波形。

在输出端接入可编程运放后,还能实现多种幅值的波形。

关键词:多功能信号发生器 DDS 可编程逻辑器件 VHDL 数字系统设计AbstractThe multi-function signal take place the machine to is in the signal occurrence machine a kind of, being apply in the electronics to measure extensively, the electric power engineering, the thing mineral 勘 explore, medical treatment, vibration analysis, the voice learns analysis, breaks down to examine a patient and the teaching research etc. is various, is one of the essential instruments that the engineer carries on the product development and produce.Its main function is for treat to measure the equipments to provide the stability, the credibility is also can with the signal of artificial regulate and control source.The direct numerical frequency that this literary grace use to be put forward by the American scholar J.TierncyC.M.Rader and B.Gold1971 year synthesize( DDS) the method, making use of the VHDL plait to write a form occurrence procedure in the CPLD programmable logic machine piece, carrying out the multi-function signal occurrence machine.Multi-function signal the occurrence machine of this topic design make use of CPLD can on-line plait distance of principle of characteristics, DDS, can carry out various frequencies, mutually the square wave, sine wave, triangle wave, the teeth of a saw wave of, even arbitrarily a form.After exportation carry connect to go into the programmable luck to put, can still carry out a form for be worth of various. Keywords:Multi-functional signal generator DDS CPLD VHDL The design of digital system目录第一章:绪论 (4)§1.1设计要求 (4)§1.2信号发生器的发展历史 (4)§1.3我国信号发生器市场现状 (5)第二章:多功能信号发生器的设计 (6)§2.1设计指导思想 (6)§2.2信号发生器的构成 (7)§2.3波形发生设计 (8)§2.1.1方波的发生 (8)§2.1.2锯齿波的发生 (8)§2.1.3三角波的产生 (9)§2.1.4正弦波的产生 (9)§2.1.5各种波之间的切换 (10)§2.4信号仿真波形 (11)§2.5数字信号的数模转换 (12)第三章:结论 (14)§3.1多功能信号发生器的功能 (14)§3.2多功能信号发生器的改进思想 (14)第四章:谢辞 (15)第五章:参考文献 (16)第一章绪论测量仪器从宏观上可分为两大类,即激励和检测,其中激励仪器主要是各类信号发生器。

多功能信号发生器是信号发生器中的一种,广泛应用于电子测量、电力工程、物矿勘探、医疗、振动分析、声学分析、故障诊断及教学科研等多方面,是工程师进行产品研发和生产的必备仪器之一。

它的主要功能是为待测设备提供稳定、可靠并可以人工调节和控制的信号源,如正弦波、方波、三角波、锯齿波、白噪声和扫频信号以及用户定义的任意波形。

§1.1设计要求要求用CPLD器件实现多功能发生器,可以输出四种波形,分别是方波、锯齿波、三角波和正弦波。

VHDL即超高速集成电路硬件描述语言,主要用于描述数字系统的行为、结构、功能和接口。

用VHDL语言编写波形发生程序。

§1.2信号发生器的发展历史作为工业产品特别是电力、电子产品的研制和生产领域中最重要的测试设备之一,信号发生器的发展历史可以追溯到上世纪40年代。

1943年惠普为海军研究实验室开发了第一台信号发生器,从而使得人们在测试设备时可以利用可控的信号源进行比较完善和安全的测试和测量。

在随后的二十年间,信号发生器一直随着电子技术、计算机技术的发展而发展,几乎成为这些技术发展的一个缩影。

从技术上看,信号发生器经历了由模拟信号发生器、数字式信号发生器到虚拟信号发生器的发展过程。

从四十到六十年代,信号发生器都是完全用以电子管工艺为基础的模拟电路搭建的,往往调节范围受到限制,因而划分为音频、高频、超高频、射频和微波等信号发生器,其信号的精度和可控性都不好,而且可产生的信号的种类很少,对于较复杂的信号,其电路都非常复杂,造成体积庞大,不易移动。

六七十年代,随着晶体管工艺的出现、大规模和超大规模集成电路的应用,数字电路在信号发生器中得到广泛的应用,从而大大提高了信号发生器的精度,减少了电路本身产生的造神,体积也大为缩小。

八十年代开始,计算机已经在工业生活中逐渐占据了重要的位置,信号发生器也开始从纯粹的由分立元件搭建改为以微处理器为核心的集成系统,这时候的新号发生器已经发生重大的变化,比如说,它所能产生信号的种类大大增加;通用性得到很大的提高;任意波信号可以通过人工设定在同一台信号发生器中产生;频宽也大大地增加了;过去的多种类的新号发生器也简单地划分为低频和高频两种,低频信号的频宽从0~50MHZ,高频则可达到20GHZ以上,但它仍存在人机界面不友好,软硬件升级维护困难等缺点。

九十年代以后虚拟一起进入了人们的视野。

这种完全以计算机软件为核心,辅以相应的硬件设备的测试系统代表了未来测试仪器的发展方向。

人们可以在友好的人机见面环境中轻松地进行各种复杂的操作,信号发生器也从一个完全独立的测试设备,而成为整个虚拟仪器系统中一个必不可少的子模块。

信号发生器中的一项关键技术是信号频率的变动控制。

早期的信号发生器大都借助电阻电容,电感电容、谐振腔、同轴线作为振荡回路产生正弦或其他函数波形,频率的变动由机械驱动可变元件(如电容器或谐振腔)来完成,其缺点是显而易见的,那就是频率不稳,噪声大,频率的改变控制不容易,这就催生了锁相频率合成器(Phase Locked Frequency Synthesize)。

这是一次技术上的飞跃,它基于锁相环路原理,从一个高准确度、高稳定度的参考晶体振荡器中综合处大量离散频率,集成度高,可靠性好且价格低廉,直到现在锁相频率合成仍然是工程应用中最为普遍的技术。

而直接数字频率合成(Direct Digital Frequency Synthesize,DDFS)则是近几年来最新发展的技术,它完全摆脱间接数字合成的乘法/除法电路,直接在基准时钟的准确相位控制下获得合成频率输出,其频率控制模块中的相位累加器由寄存器和加法器组成,相位信息存储在波形存储器内,再经数模转换后输出最低合成频率,随着频率控制输入的增长,输出合成频率亦增加。

相位累加器的宽度增加时,输出合成频率的准确度相应增加。

DDFS频率变换速度主要取决于累加器和数模转换器的开关时间,显然要比模拟电路快得多,因此广泛采用DDFS技术是必然的发展趋势。

§1.3我国信号发生器市场现状目前我国经济开始进入一个新的发展时期,经济的快速发展将加快企业的技术改造步伐,各行业特别是电子、通信行业对先进任意波的需求更加强劲。

据最新电子商情报道,从1998年开始,由于国家采取了扩大内需发展经济的决策,扩大了国产任意波发生的市场,销量增长都在30%左右。

但我国的任意波发生器市场大部分被国外产品所占领,国内产品市场占有率很低。

目前,Anritsu、Agilent、Advantest、R/S、TEKTRONIX、NI几家著名仪器公司都在生产各类任意波信号发生器,如Agilent公司生产的HP33120A函数/任意波发生器、Advantest公司生产的33120A函数/任意波发生器。

Agilent的信号发生器一直是业界公认的高水平仪器,而且种类和型号最多,产品功能全、技术含量高。

近几年Anritsu、Agilent、Advantest、R/S,NI等外国公司在我国的销售额逐年大幅度上升,Agilent公司在中国销售的任意波信号发生器已极大地超过国内产品。

我国的仪器技术水平在发展中国家处于领先地位,且价格便宜。

境外有的销售商已把目标转向国内的产品,出口到北美、欧洲、东南亚的任意波发生器逐年增加,所以扩大外销产品是扩大国产任意波市场的一条重要出路。