同步时序电路

异步时序电路和同步时序电路

异步时序电路和同步时序电路哎呀,今天咱们聊聊异步时序电路和同步时序电路。

你可能会问,这两者有什么区别,听起来是不是挺无聊的?其实不然,这就像是两种不同性格的人,碰到一起,总能擦出火花。

先说说异步时序电路吧。

想象一下,一个聚会,大家都是自由散漫的那种,想来就来,想走就走,完全不受时间的束缚。

有人在角落里玩手机,有人在舞池里狂舞,气氛虽然热烈,但大家各自的节奏可就五花八门了。

异步电路就是这样的,它不依赖统一的时钟信号,输入信号一来,电路立马就响应,像是在说:“我就是要做自己!”这种电路灵活得很,像个自由奔放的小孩,随心所欲。

不过,这样的好处也有风险。

想想看,聚会里一旦有人喝多了,场面可就乱了套,容易出乱子。

再说说同步时序电路,这可就跟异步电路截然不同了。

想象一下,一个严格的舞蹈排练,大家都得听指挥,跟着节拍走。

统一的时钟信号就像是那位严厉的老师,时刻提醒大家:“跟上我的节奏!”每个输入信号的变化都要等到时钟信号的“允许”,这就保证了电路的稳定性和可靠性。

同步电路就像一个井然有序的团队,大家互相配合,做事情效率高得很。

虽然有时会觉得有点无趣,但保证了事情不出岔子,真是“稳如老狗”。

这两种电路各有千秋,选哪个还得看具体的场景。

异步电路那种自由度很适合处理突发的信号,就像是生活中的突发事件,有时候就是要灵活应对。

而同步电路呢,适合那些要求高精度和稳定性的场合,就像是在做手术,丝毫不能马虎。

可以说,选择哪种电路就像选对象,适合的才是最好的。

再说到设计上,异步电路的设计难度可不小哦。

要考虑到各种可能的信号变化和干扰,这就像是在解谜题,有点像侦探故事,时刻要小心翼翼。

而同步电路虽然设计起来相对简单,但也有自己的烦恼,时钟信号的频率得精准,不然就可能出现“时钟偏差”,那样可就悲剧了。

在实际应用中,异步电路多用于一些要求快速响应的场合,比如一些特殊的传感器或者高速数据处理。

而同步电路则更常见于电脑、手机等我们日常用到的电子产品,毕竟谁也不想在玩游戏的时候卡住,对吧?所以说,这两者就像是好搭档,互相补充,各自发挥着重要作用。

同步时序电路和异步时序电路差异

同步时序电路和异步时序电路差异英文回答:Synchronous sequential circuits.Synchronous sequential circuits are a type of digital circuit that operates in synchronism with a clock signal. The clock signal is a periodic square wave that is used to synchronize the operation of the circuit. Synchronous sequential circuits are typically used in applications where precise timing is required.One of the advantages of synchronous sequentialcircuits is that they are relatively easy to design and analyze. This is because the operation of the circuit is determined by the clock signal, which is a known quantity. Synchronous sequential circuits are also relatively immune to noise and other disturbances.However, synchronous sequential circuits also have someThis is because the clock signal must be used tosynchronize every operation of the circuit. Another disadvantage is that synchronous sequential circuits can be complex to design in some cases.Asynchronous sequential circuits.Asynchronous sequential circuits are a type of digital circuit that operates without a clock signal. The operation of an asynchronous sequential circuit is determined by the input signals and the current state of the circuit. Asynchronous sequential circuits are typically used in applications where high speed is required.One of the advantages of asynchronous sequentialcircuits is that they can be very fast. This is because the circuit does not have to wait for a clock signal to operate. Another advantage is that asynchronous sequential circuits can be relatively simple to design in some cases.However, asynchronous sequential circuits also havedifficult to design and analyze. This is because the operation of the circuit is not determined by a known quantity, such as a clock signal. Another disadvantage is that asynchronous sequential circuits can be susceptible to noise and other disturbances.中文回答:同步时序电路。

同步和异步时序电路的优缺点

同步和异步时序电路的优缺点同步和异步时序电路是数字电路中常见的两种时序电路设计方式。

它们各自有着优点和缺点,下面将对它们进行详细分析。

同步时序电路是指所有触发器的时钟信号均来自于一个公共的时钟源。

它的优点主要体现在以下几个方面:1. 同步时序电路具有较高的可靠性。

由于所有触发器的时钟信号都是同一个源,因此它们的状态变化是同步的,能够保证各个部分之间的数据传输是有序的,减少了数据的丢失和错误。

2. 同步时序电路具有较低的功耗。

由于所有触发器的时钟信号是同步的,它们的工作时间是重叠的,可以减少部分触发器的工作时间,从而降低功耗。

3. 同步时序电路具有较好的抗干扰能力。

由于时钟信号是统一的,它们在传输过程中对噪声和干扰的容忍度较高,能够有效地抵抗外界干扰。

然而,同步时序电路也存在一些缺点:1. 同步时序电路的设计复杂度较高。

由于所有触发器都需要受到时钟信号的控制,需要进行精确的时序设计和时钟分配,增加了设计的难度和复杂度。

2. 同步时序电路的时钟频率有限。

由于时钟信号需要在整个电路中传输,当电路规模较大时,时钟信号的传输延迟会增加,从而限制了时钟频率的提高。

异步时序电路是指触发器的时钟信号不是来自公共的时钟源,而是根据输入信号的变化进行触发。

它的优点主要体现在以下几个方面:1. 异步时序电路具有较高的灵活性。

由于不受统一的时钟信号控制,可以根据输入信号的变化进行触发,灵活性更强,适用于复杂的数据交互和处理。

2. 异步时序电路的时钟频率不受限制。

由于时钟信号的触发是根据输入信号的变化进行的,不受统一时钟信号的传输延迟影响,因此可以实现较高的时钟频率。

3. 异步时序电路具有较低的延迟。

由于触发信号的传输不需要等待统一的时钟源,因此可以减少延迟,提高电路的响应速度。

然而,异步时序电路也存在一些缺点:1. 异步时序电路的设计复杂度较高。

由于触发信号的变化需要根据输入信号的变化进行触发,需要进行复杂的时序设计和状态分析,增加了设计的难度和复杂度。

同步和异步时序电路的优缺点

同步和异步时序电路的优缺点同步和异步时序电路是数字电路中常用的两种设计方法。

它们在电路的时钟控制和数据传输方面有着不同的优缺点。

同步时序电路是在电路中引入一个时钟信号,以控制各个部件的工作时序。

同步时序电路的优点在于稳定性高,各个部件的工作同步且可靠。

由于同步时序电路的工作时序是由时钟信号确定的,因此各个部件之间的协调和同步非常容易实现。

同步时序电路适用于对时序要求严格的场合,如高速通信、数据存储等领域。

然而,同步时序电路也存在一些缺点。

首先,同步时序电路对时钟信号的要求较高,时钟信号的频率、占空比等参数需要精确控制,否则会导致电路工作不正常。

其次,同步时序电路的设计和调试比较复杂,需要考虑时钟信号的传输延迟、时序冲突等问题。

此外,同步时序电路的时钟频率受限于电路中最慢的部件,可能无法充分发挥其他部件的性能。

与同步时序电路相比,异步时序电路不依赖于时钟信号,而是通过数据本身的变化来控制工作时序。

异步时序电路的优点在于灵活性高,可以根据数据的变化实时调整工作时序,适应不同的工作负载。

此外,异步时序电路不受时钟频率的限制,可以充分发挥各个部件的性能。

然而,异步时序电路也存在一些缺点。

首先,由于异步时序电路没有统一的时钟信号来控制工作时序,各个部件之间的协调和同步比较困难。

因此,在设计和调试异步时序电路时需要考虑时序冲突、冒险等问题,增加了工作的复杂性。

其次,由于异步时序电路的工作时序不固定,可能会导致数据错误和冗余计算,降低电路的性能和效率。

同步时序电路和异步时序电路各有优缺点。

同步时序电路适用于对时序要求严格的场合,稳定性高;而异步时序电路适用于灵活性要求较高的场合,性能较好。

在实际应用中,需要根据具体的需求和设计要求选择适合的时序电路设计方法。

同步和异步时序电路的优缺点

同步和异步时序电路的优缺点引言时序电路是数字电路中的一种重要电路,用于控制电路的时序和数据流动。

同步和异步是时序电路的两种基本设计方式。

本文将从优缺点的角度来探讨同步和异步时序电路的特点。

同步时序电路同步时序电路是指时钟信号作为电路中各个部分的统一节拍,控制电路的运行和数据的传输。

同步时序电路的优缺点如下:优点1.稳定性高:同步时序电路使用统一的时钟信号来同步各个部分的操作,因此能够保证电路的稳定性和可靠性。

2.设计简单:同步时序电路的设计相对简单,因为各个部分的操作都是基于统一的时钟信号进行的,不需要考虑时序和数据的同步问题。

3.时序控制灵活:同步时序电路的时序控制非常灵活,可以根据需求来调整时钟信号的频率和相位,以满足不同的应用需求。

缺点1.延迟高:同步时序电路的运行速度受到时钟信号的限制,因此可能存在较高的延迟。

特别是在时钟频率较高的情况下,延迟问题会更加明显。

2.功耗较高:同步时序电路在每个时钟周期都会进行操作,即使没有数据需要处理,也会消耗一定的功耗。

3.容错性差:同步时序电路对于输入数据的稳定性要求较高,一旦输入数据有误,可能会导致电路的功能失效。

异步时序电路异步时序电路是指各个部分的操作不依赖于统一的时钟信号,而是通过控制信号来实现时序和数据的同步。

异步时序电路的优缺点如下:优点1.速度快:异步时序电路的速度受到电路中最慢的部分的限制,可以根据具体情况来调整各个部分的运行速度,从而实现更高的工作频率。

2.功耗低:异步时序电路仅在需要处理数据时才进行操作,因此在没有数据需要处理时,可以降低功耗,提高电路的能效。

3.容错性好:异步时序电路对于输入数据的稳定性要求较低,能够容忍一定的输入数据误差,提高了电路的容错性。

缺点1.设计复杂:异步时序电路的设计相对复杂,因为需要考虑各个部分的时序和数据的同步问题,可能需要引入额外的控制电路和状态机来实现。

2.稳定性差:由于异步时序电路的各个部分操作相对独立,可能存在时序和数据的不一致问题,导致电路的稳定性较差。

同步时序电路和异步时序电路的差异

同步时序电路和异步时序电路的差异同步时序电路和异步时序电路,这俩听起来是不是有点像“打火机”和“火柴”——看起来差不多,但用法一不小心就能差出天际。

其实啊,它们的区别比想象的要大,像是两个性格完全不同的人,一个讲究规矩、一个自由散漫。

你要是搞懂它们,你就能轻松在电子电路的世界里穿梭自如,感觉像在逛自己家后花园一样。

先说说同步时序电路,别看名字里有个“同步”,这东西其实是非常讲规矩的。

它的基本法则就是:一切都得听“时钟”的指挥,明白不?它就像是一个严格的班主任,每天都得定时敲响铃声,告诉大家:“嘿,时间到了,赶紧换地方,做事情!”大家的动作都得按照这个固定的时钟信号来走。

就好比你每天上学,钟表指针一到点,所有同学都得同时起立,整齐划一,动作一模一样,真的是分毫不差。

所有的操作都在这个统一的时钟下进行,丝毫不允许有人慢半拍、急三分。

嗯,这就是同步电路的基本特点:有一个统一的时间基准,一切都由时钟信号来掌控。

那异步时序电路呢?哎,别看它名字里有个“异步”,其实它可不喜欢那么死板的规则。

它讲究的就是“自由自在,随心所欲”。

你可以理解成它是一群没有班主任的学生,每个人都有自己的节奏,根本不用等别人做完自己的事。

这就像你跟几个朋友一起去喝咖啡,大家进咖啡馆的时间完全不一样,也没有什么固定的“点钟”,每个人随时可以做自己的事情,只要能看清楚周围的环境,做得不突兀,就行。

异步电路也差不多,它们不会强求有一个统一的时钟信号,而是通过各自的信号变化来决定接下来的动作。

说白了,异步电路就是一个没有“规矩”的系统,每个部分都靠自己来决定什么时候开始工作,和谁合作,怎么合作。

它们更灵活,但也容易出问题,毕竟没有时钟这个“领头羊”来规范每个人的行为,难免会有点“各自为政”的感觉。

那这两者的差别有什么影响呢?你以为这只是个小问题?不管是同步还是异步,它们在电路的设计上都能让人“脑袋冒烟”。

同步电路虽然看起来规规矩矩,但它对时钟信号的要求非常严格,时钟的频率不稳定或者出现延迟,就可能让整个系统瘫痪。

同步和异步时序电路的优缺点

同步和异步时序电路的优缺点同步和异步时序电路是数字电路中常用的两种时序控制方式。

它们在实际应用中各有优缺点,下面将分别进行介绍。

同步时序电路是指所有时序元件使用的是同一个时钟信号,各个元件在时钟的上升沿或下降沿进行状态转换。

同步时序电路具有以下优点:1. 稳定性好:同步时序电路中所有元件都受到同一个时钟信号的控制,因此元件之间的状态转换是有规律可循的。

这样可以避免由于信号传输延迟等原因引起的不稳定性问题。

2. 可靠性高:同步时序电路中的状态转换是在时钟信号的控制下进行的,所有元件在同一个时刻进行状态转换,因此不会出现因为某个元件状态转换出错而导致整个系统功能失效的情况。

3. 设计灵活性强:同步时序电路中的各个元件之间是通过时钟信号进行同步的,因此可以方便地对系统进行扩展和修改,只需要调整时钟信号的频率或者引入新的时钟信号即可。

然而,同步时序电路也存在一些缺点:1. 时钟频率限制:同步时序电路中所有元件都受到同一个时钟信号的控制,因此时钟频率的选择对整个系统的性能有很大影响。

如果时钟频率过高,会增加系统的功耗和成本;如果时钟频率过低,会降低系统的运行速度。

2. 时钟分配问题:当系统中的元件数量较多时,会出现时钟信号的分配问题。

由于时钟信号需要同时传输到各个元件,因此会增加布线的复杂度和功耗。

异步时序电路是指各个时序元件的状态转换不依赖于统一的时钟信号,而是根据元件自身的输入信号进行控制。

异步时序电路具有以下优点:1. 灵活性强:由于异步时序电路不依赖于统一的时钟信号,因此每个元件的状态转换可以根据需要进行调整,提供了更大的设计灵活性。

2. 节约功耗:异步时序电路只有在需要进行状态转换时才会进行,而不是像同步时序电路那样在每一个时钟周期都进行状态转换。

这样可以节约功耗,提高系统的能效。

3. 抗干扰能力强:由于异步时序电路中各个元件的状态转换不依赖于统一的时钟信号,因此可以减少由于干扰信号对时钟信号的影响,提高系统的抗干扰能力。

同步时序电路设计步骤

同步时序电路设计步骤同步时序电路是一种能够根据输入信号的时序关系,产生相应时序输出信号的电路。

它在数字系统中广泛应用,用于控制时序要求严格的设备和系统。

设计一个同步时序电路需要经过以下步骤:1. 确定时序要求:首先,需要明确同步时序电路的功能和时序要求。

这包括输入信号的时序特性、输出信号的时序关系、时钟频率等。

通过分析时序要求,设计者可以确定电路应该具备的功能和性能。

2. 确定时钟信号:时钟信号在同步时序电路中起着关键作用,它用于同步各个触发器的状态。

设计者需要确定时钟信号的频率,并根据需求选择合适的时钟源。

常见的时钟源包括晶体振荡器、时钟发生器等。

3. 选择触发器类型:触发器是同步时序电路的核心组件,它能够存储和传递信息。

根据时序要求,设计者需要选择合适的触发器类型。

常见的触发器包括D触发器、JK触发器、T触发器等。

不同类型的触发器具有不同的特性和功能,设计者需要根据具体情况进行选择。

4. 绘制状态转移图:状态转移图是同步时序电路设计的重要工具,它能够清晰地描述电路的状态和状态之间的转移关系。

通过绘制状态转移图,设计者可以更好地理解电路的功能和时序要求,并进行必要的优化和修改。

5. 进行逻辑设计:根据状态转移图,设计者可以开始进行逻辑设计。

逻辑设计包括选择适当的逻辑门和触发器,进行布线和连接等。

在这个过程中,设计者需要根据时序要求确定逻辑门和触发器的输入输出关系,并进行逻辑优化,以提高电路的性能和可靠性。

6. 进行时序分析:时序分析是同步时序电路设计中不可或缺的一步。

通过时序分析,设计者可以验证电路的正确性和稳定性。

时序分析包括计算电路的最长和最短传播延迟、时钟抖动等。

设计者可以通过仿真工具或手工计算来进行时序分析。

7. 进行电路验证:在设计完成后,设计者需要进行电路验证,以确保电路能够按照设计要求正常工作。

电路验证可以通过实际硬件实现、仿真验证等方式进行。

在验证过程中,设计者需要根据输入信号和时钟信号,观察输出信号是否符合时序要求。

同步时序逻辑电路和异步时序逻辑电路

同步时序逻辑电路和异步时序逻辑电路1. 引言说到电路,大家可能会觉得有点儿高深莫测,其实它们就像生活中的各种小插曲,错综复杂但又充满趣味。

今天我们来聊聊两种电路:同步时序逻辑电路和异步时序逻辑电路。

听起来很正式吧?其实就像两位老朋友,各有各的个性,给我们的生活带来不同的滋味。

2. 同步时序逻辑电路2.1 什么是同步电路先说说同步时序逻辑电路。

想象一下,大家一起跳舞,必须跟着节拍来对吧?这就是同步电路的工作原理。

它们依靠一个时钟信号来统一行动,一切都得在这个时钟的节奏下进行。

你想想,如果没有这个节拍,大家就会乱成一团,完全没法协调。

2.2 优点与缺点同步电路的优点可多了。

首先,它们容易设计,因为所有的动作都得听从同一个“老大”——时钟。

这样一来,故障也比较容易定位,就像在大合唱里找出跑调的那个人,轻而易举!但是,当然了,凡事都有两面。

它们在速度上可能会受到限制,因为要等时钟信号到位才能开始下一步,仿佛总得等着老大下命令。

3. 异步时序逻辑电路3.1 什么是异步电路接下来,我们来聊聊异步时序逻辑电路。

这家伙就有点儿“放飞自我”的意思。

想象一下,大家随意地跳舞,没有固定的节拍,各自随心所欲,热火朝天。

这种电路不需要时钟信号,各个部分可以独立工作,就像一场即兴表演,想跳就跳,想停就停。

3.2 优点与缺点异步电路的优点就是速度快,反应灵敏。

因为没有时钟的限制,它们可以在需要的时候马上响应,特别适合处理突发事件,像是过马路时的红绿灯,红灯一亮就得停下,绿灯一闪立马走。

可是,快可不代表好,有时候这就像在一场没有指挥的音乐会上,大家都想表现,结果弄得一团糟,容易出现竞争和冲突。

4. 比较与应用4.1 各自的应用领域那么,这两种电路究竟哪种更好呢?这就要看情况了。

同步电路一般用于那些需要稳定和可靠性的地方,比如计算机和大型系统。

而异步电路则适合需要快速反应的地方,比如一些高频交易系统或者一些需要低延迟的通信设备。

时序电路的作用

时序电路的作用1. 时序电路简介时序电路是指一类能够按照预定的时间顺序进行状态切换的电路。

它由各种触发器、计数器和时钟信号等组成,广泛应用于数字系统中,用于控制和调度各个部件的运行顺序。

时序电路在数字系统中起着至关重要的作用。

2. 时序电路的分类2.1 同步时序电路同步时序电路是指通过同步信号进行状态切换的电路。

同步时序电路中,各个触发器和计数器的状态变化是同步进行的,由时钟信号来驱动。

典型的同步时序电路包括时钟分频器和状态机等。

同步时序电路通过统一的时钟信号来保证各个部件的同步运行,能够提高系统的稳定性和可靠性。

2.2 异步时序电路异步时序电路是指通过异步信号进行状态切换的电路。

异步时序电路中,各个触发器和计数器的状态变化是独立进行的,不需要时钟信号来驱动。

典型的异步时序电路包括门闩电路和脉冲生成电路等。

异步时序电路能够根据特定的输入信号实时响应,具有较高的灵活性和响应速度。

3. 时序电路的作用时序电路在数字系统中发挥着重要的作用,具有以下几个方面的功能:3.1 控制信号的生成和延时时序电路能够根据时钟信号和输入信号生成各个部件的控制信号,并对信号进行延时处理。

通过时序电路可以实现复杂的控制逻辑,对各个部件的运行顺序和时序进行精确控制,确保数字系统的正常工作。

3.2 数据的存储和传递时序电路中的触发器和计数器等部件能够存储和传递数据。

触发器可以将输入的数据存储起来,并在时钟信号的作用下将数据传递给下一个触发器或计数器,从而实现数据的传输和处理。

时序电路可以在不同的时钟周期中完成各个数据操作,确保数据的正确性和稳定性。

3.3 状态的控制和转换时序电路中的状态机可以对系统的状态进行控制和转换。

状态机能够根据输入信号的变化和时钟信号的触发,按照预定的状态转移规则进行状态的切换。

通过状态机的设计,可以实现复杂的状态控制和决策逻辑,使系统能够按照特定的流程和顺序进行运行。

3.4 时序逻辑的实现时序电路能够实现各种时序逻辑的功能。

同步时序电路

同步时序电路同步时序电路是一种基础的数字电路,它在许多电子设备中都有广泛的应用。

本文将从定义、分类、原理、设计和应用等方面对同步时序电路进行详细介绍。

一、定义同步时序电路是指在时序控制下,各个电路模块之间能够精确地协调工作,从而实现预定的功能。

它是一种特殊的时序电路,可以对时序信号进行处理和控制,保证电路的稳定性和可靠性。

二、分类根据不同的功能和工作原理,同步时序电路可以分为以下几种类型:1.触发器型同步时序电路:利用触发器的特性进行时序控制,实现时序信号的稳定和精确控制。

2.计数器型同步时序电路:利用计数器的特性进行时序计数和控制,实现多种复杂的时序功能。

3.状态机型同步时序电路:利用状态机的特性进行时序状态转换和控制,实现多种复杂的控制功能。

4.时钟型同步时序电路:利用时钟信号进行时序同步和控制,实现多种复杂的时序功能。

三、原理同步时序电路的工作原理主要包括时序控制、时序同步、时序存储和时序输出等方面。

1.时序控制:时序控制是同步时序电路的核心,它通过对时序信号进行处理和控制,实现电路的稳定和可靠工作。

2.时序同步:时序同步是同步时序电路的重要特性之一,它能够确保不同电路模块之间的时序信号同步,从而实现预定的功能。

3.时序存储:时序存储是同步时序电路的另一个重要特性,它能够将时序信号暂时存储在存储器中,以便后续处理和控制。

4.时序输出:时序输出是同步时序电路的最终结果,它通过将时序信号输出到其他电路模块中,实现预定的功能。

四、设计同步时序电路的设计需要考虑多种因素,包括电路结构、时序控制、时序同步、时序存储和时序输出等方面。

1.电路结构:电路结构是同步时序电路的基础,需要选择合适的电路结构来实现预定的功能。

2.时序控制:时序控制是同步时序电路的核心,需要合理设计时序控制电路,以实现精确的时序控制。

3.时序同步:时序同步是同步时序电路的重要特性之一,需要设计合理的时序同步电路,以确保不同电路模块之间的时序信号同步。

同步时序电路和异步时序电路

同步时序电路和异步时序电路

时序电路是一种电子电路,它可以驱动其他芯片,从而形成复杂的电路系统,用于控制和操纵计算机中的信号。

时序电路可以分为同步和异步两类。

同步时序电路是一种受控的时序电路,它在一定的时序上收取信号。

它的工作原理是,一个称为时钟的信号在一定的时序上做为控制标志来触发另一个信号,使其进行变化,从而实现模拟信号的转换。

由于同步时序电路可以在预定的时序上生成控制信号,因此它用在计算机中数据处理和传输中,主要用于实现数据的可靠传输。

异步时序电路是一种非受控的时序电路,它不依赖于控制信号,而是依赖于比特流中的特定的比特组合。

异步时序电路可以自动识别特定的比特组合,并重新组合它们,从而实现信号的转换。

由于它可以重新组合比特组合,因此它用在计算机中存储和传输中,主要用于实现数据的可靠传输。

同步时序电路和异步时序电路在性能和特性上有很大差别。

同步时序电路依赖于时钟信号,由复杂的时序和回路组成,具有高精度、高可靠性、高效率,但受时钟频率的限制,其处理的信号的传输速率较低。

相反,异步时序电路不依赖于时钟,它的结构相对简单,精度、可靠性和效率较低,但是它可以处理高速比特流,传输速率较高。

总之,同步时序电路和异步时序电路都是重要的时序电路,它们在计算机中都扮演着重要的角色,在信号处理和数据传输中都有着广泛的应用。

由于这两种电路在性能和特性上有很大差别,因此应根据

具体应用场景选择合适的时序电路,以实现最优的计算机控制和数据处理。

同步时序逻辑电路的自启动设计

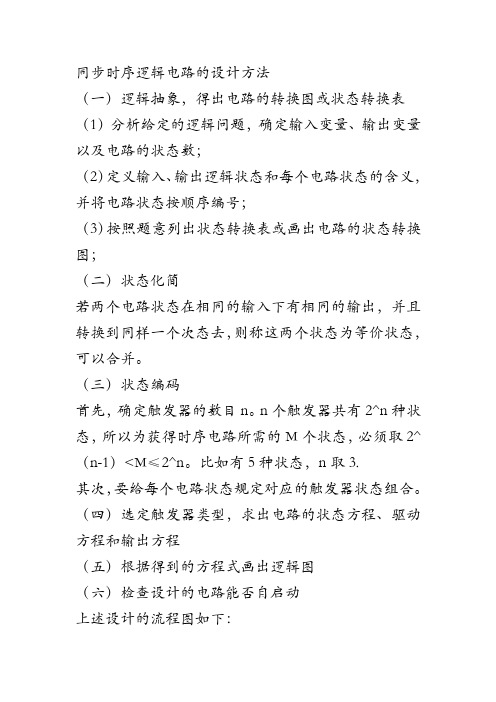

同步时序逻辑电路的设计方法

(一)逻辑抽象,得出电路的转换图或状态转换表(1)分析给定的逻辑问题,确定输入变量、输出变量以及电路的状态数;

(2)定义输入、输出逻辑状态和每个电路状态的含义,并将电路状态按顺序编号;

(3)按照题意列出状态转换表或画出电路的状态转换图;

(二)状态化简

若两个电路状态在相同的输入下有相同的输出,并且转换到同样一个次态去,则称这两个状态为等价状态,可以合并。

(三)状态编码

首先,确定触发器的数目n。

n个触发器共有2^n种状态,所以为获得时序电路所需的M个状态,必须取2^(n-1)<M≤2^n。

比如有5种状态,n取3.

其次,要给每个电路状态规定对应的触发器状态组合。

(四)选定触发器类型,求出电路的状态方程、驱动方程和输出方程

(五)根据得到的方程式画出逻辑图

(六)检查设计的电路能否自启动

上述设计的流程图如下:。

同步和异步时序电路的优缺点

同步和异步时序电路的优缺点同步和异步时序电路是数字电路中常见的两种设计方式,它们在工作原理、应用场景和优缺点等方面存在差异。

一、同步时序电路的特点及优缺点同步时序电路是指电路中各个部件的时钟信号是同步的,即它们都根据同一个时钟信号进行工作。

同步时序电路具有以下特点:1. 同步性强:同步时序电路中各个部件的时钟信号是同步的,它们在时钟的上升沿或下降沿进行操作,因此能够确保电路的各个部件在相同的时间完成操作,保证了电路的同步性。

2. 设计简单:同步时序电路的设计相对比较简单,因为各个部件的时钟信号是同步的,所以不需要考虑时序逻辑和时序关系,只需要根据时钟信号进行操作即可。

3. 适用范围广:同步时序电路适用于处理各种类型的数据和信号,包括数字信号、模拟信号和混合信号等。

然而,同步时序电路也存在一些缺点:1. 时钟频率限制:同步时序电路的时钟频率一般较高,因为各个部件需要在一个时钟周期内完成操作,所以时钟频率的提高会增加电路的复杂度和功耗。

2. 时序关系复杂:同步时序电路中各个部件之间的时序关系比较复杂,需要进行严格的时序分析和时序约束,以确保电路的正确性和稳定性。

二、异步时序电路的特点及优缺点异步时序电路是指电路中各个部件的时钟信号是异步的,即它们根据各自的时钟信号进行工作,不依赖于其他部件的时钟信号。

异步时序电路具有以下特点:1. 独立性强:异步时序电路中各个部件的时钟信号是独立的,它们可以根据自己的时钟信号进行操作,不受其他部件的影响。

2. 灵活性高:异步时序电路的设计比较灵活,因为各个部件的时钟信号是独立的,所以可以根据实际需求进行灵活的时序设计。

3. 时钟频率自适应:异步时序电路的时钟频率可以根据实际需求进行自适应调节,不需要严格按照同步时序电路的时钟频率进行设计。

然而,异步时序电路也存在一些缺点:1. 设计复杂度高:异步时序电路的设计相对比较复杂,因为各个部件的时钟信号是异步的,所以需要考虑时序逻辑和时序关系,以确保电路的正确性和稳定性。

同步和异步时序电路的优缺点

同步和异步时序电路的优缺点同步和异步时序电路是数字电路中常用的两种设计方式,它们各有优缺点。

本文将从多个方面对它们进行比较和分析。

一、定义同步时序电路是指电路中所有时钟信号都是同一源头产生的,各部分的动作按照时钟的上升或下降沿进行同步,从而保证各部分的操作是有序的。

异步时序电路则是各个部分之间没有时钟信号的统一,它们的操作完全依靠事件的发生和完成。

二、优点比较1. 稳定性:同步时序电路由于所有操作都在时钟信号的控制下进行,因此具有很好的稳定性。

而异步时序电路则容易受到外部干扰的影响,稳定性较差。

2. 同步性:同步时序电路的各个部分操作是按照统一的时钟信号进行同步的,因此各部分之间的数据传输更加可靠,不容易出现数据丢失或错误。

而异步时序电路的各部分操作是依靠事件的发生和完成,因此数据传输的同步性较差,容易出现数据错误。

3. 设计复杂度:同步时序电路的设计相对简单,因为所有操作都是按照时钟信号同步进行的。

而异步时序电路的设计较为复杂,因为需要考虑事件的发生和完成的时序问题。

4. 可扩展性:同步时序电路由于时钟信号的统一,可以很方便地进行扩展,增加新的模块或功能。

而异步时序电路则需要考虑各个事件之间的时序关系,扩展性较差。

三、缺点比较1. 延迟:同步时序电路在时钟信号的作用下,各部分操作是按照统一的时序进行的,因此会有一定的延迟。

而异步时序电路的各部分操作是依靠事件的发生和完成,因此延迟较小。

2. 功耗:同步时序电路由于所有操作都在时钟信号的控制下进行,因此会有一定的功耗。

而异步时序电路的各部分操作是依靠事件的发生和完成,因此功耗较低。

3. 灵活性:同步时序电路的各部分操作是按照统一的时钟信号进行同步的,因此灵活性较差,不容易适应复杂的场景。

而异步时序电路的各部分操作是依靠事件的发生和完成,因此灵活性较好,可以适应各种复杂的场景。

同步和异步时序电路各有优缺点,选择使用哪种方式需要根据具体的应用场景来决定。

同步和异步时序电路的优缺点

同步和异步时序电路的优缺点同步和异步时序电路是数字电路中常见的两种设计方式。

它们各有优缺点,下面将分别进行介绍。

同步时序电路是指在时钟信号的控制下,所有的电路元件都按照同步的节奏进行工作。

同步时序电路的优点是稳定性高,因为所有的电路元件都是在时钟信号的控制下进行工作,所以不会出现电路元件之间的时序问题。

此外,同步时序电路的设计比较简单,因为所有的电路元件都是按照同步的节奏进行工作,所以不需要考虑电路元件之间的时序问题,只需要考虑时钟信号的控制即可。

但是同步时序电路也有一些缺点。

首先,同步时序电路的时钟信号需要传输到所有的电路元件中,这会导致时钟信号的延迟和抖动,从而影响电路的性能。

其次,同步时序电路的时钟频率受限于电路中最慢的电路元件,这会导致电路的速度受限。

异步时序电路是指在没有时钟信号的控制下,电路元件按照自己的时序进行工作。

异步时序电路的优点是速度快,因为电路元件不需要等待时钟信号的控制,可以直接进行工作。

此外,异步时序电路的时钟频率不受限制,因为每个电路元件都是按照自己的时序进行工作。

但是异步时序电路也有一些缺点。

首先,由于电路元件是按照自己的时序进行工作,所以容易出现时序问题,如冒险、悬空等问题。

这些问题会导致电路的稳定性和可靠性下降。

其次,异步时序电路的设计比较复杂,因为需要考虑电路元件之间的时序问题,需要采用一些特殊的电路元件来解决时序问题。

综上所述,同步和异步时序电路各有优缺点。

在实际应用中,需要根据具体的需求来选择合适的设计方式。

如果要求电路稳定性高、设计简单,可以选择同步时序电路;如果要求电路速度快、时钟频率不受限制,可以选择异步时序电路。

但是需要注意的是,在选择异步时序电路时,需要特别注意时序问题,以保证电路的稳定性和可靠性。

同步时序逻辑电路

例3:

1)C、F等价;

2)A、B相应旳次态为C、F和B、A,而C、F等价,A、 B和B、A交错,所以A、B等价;

3)A、E相应旳次态为:C和B、E, 而B、E相应旳次态是F、C和A、E, 因为F、C等价, 所以它们构成循环,A、E等价,B、E也等价

3)状态编码、并画出编码形式旳状态图及状态表。 在得到简化旳状态图后,要对每一种状态指定1个二进制代码, 这就是状态编码(或称状态分配)。

二、环节:

1、一般过程:

2、详细阐明:

1)由给定旳逻辑功能求出原始状态图:

原始状态图:直接由要求实现旳逻辑功能求得旳状态转换图。

画出原始状态图是设计旳最关键环节:a)分析给定旳逻辑功 能,拟定输入变量,输出变量及该电路应包括旳状态,并用 字母S0,S1….表达这些状态。b分别以上述状态为现态,考察 在每一种可能旳输入组合作用下应转入哪个状态及相应旳输 出,便可求得符合题意旳状态图。

次态对等效是指状态Si和SJ旳次态对Sk和SJ满足等价旳两个条 件。例如,状态S1和S2旳次态对为S3和S4,它们既不相同,也 没有与状态对S1,S2直接构成交错和循环。但是,状态S3和S4 旳输出完全相同,且其次态相同或交错或循环。

等效状态旳传递性:若状态S1 和S2等效,状态S2 和S3等效, 则状态S1 和S3也等效,记作:(S1,S2), (S2,S3) (S1,S2, S3)。

例4 , P224

表中旳状态顺序依次标上第一种状态至倒数第二个状态旳状 态名称,而纵向自上到下依次标上第二个状态至最终一种状 态旳状态名称。表中每个方格代表一种状态对。

2)顺序比较,寻找等效状态对;对照原始状态表或图对每个 状态对进行比较,成果有三:a)状态对等效;b)状态对不等 效;c)状态对是否等效需进一步检验。(将它们旳次态对填 入相应表格中)。

同步和异步时序电路的优缺点

同步和异步时序电路的优缺点同步和异步时序电路是数字电路中常见的两种时序电路设计方式。

它们在实际应用中各有优缺点,下面将分别从多个方面进行介绍。

1. 同步时序电路的优点:同步时序电路是指各个触发器在同一个时钟脉冲的控制下进行状态转换的电路。

它的优点如下:① 稳定性好:同步电路中所有触发器的状态转换都是在时钟脉冲控制下进行的,时钟脉冲的上升沿或下降沿可以视为触发器的稳定边沿,因此同步电路具有较好的稳定性。

② 设计灵活:同步电路中的各个触发器在同一个时钟信号的控制下进行状态转换,因此可以根据时钟信号的频率和相位来控制触发器的工作,从而达到灵活设计的目的。

③ 抗噪声干扰:时钟信号在同步电路中可以视为一个同步信号,它的上升沿或下降沿可以作为触发器的稳定边沿。

同步电路中的触发器在同步信号的控制下进行状态转换,可以有效抑制噪声干扰,提高系统的抗干扰能力。

2. 同步时序电路的缺点:同步时序电路也存在一些缺点,主要包括以下几个方面:① 设计复杂:同步电路中的各个触发器需要在同一个时钟信号的控制下进行状态转换,因此需要进行时序分析和时序设计,这增加了电路设计的复杂性。

② 延迟较大:同步电路中的触发器都是在同一个时钟脉冲的控制下进行状态转换,因此触发器之间存在一定的时序延迟,这对于一些对时延要求较高的应用场景可能不太适用。

③ 对时钟信号要求高:同步电路中的触发器需要受到时钟信号的同步控制,因此对时钟信号的频率和相位有较高的要求,这对时钟信号的稳定性和可靠性提出了一定的要求。

3. 异步时序电路的优点:异步时序电路是指各个触发器在不依赖于时钟脉冲的控制下进行状态转换的电路。

它的优点如下:① 灵活性好:异步电路中的触发器不依赖于时钟脉冲的控制,可以根据输入信号的变化情况进行状态转换,因此具有较好的灵活性。

② 延迟较小:异步电路中的触发器不受时钟信号的控制,状态转换更加及时,因此延迟较小,适用于对时延要求较高的应用场景。

③ 设计简单:异步电路中的触发器不需要进行时序分析和时序设计,设计较为简单。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

n1 n1 n1 Q3 Q2 Q1

0 0 0 1 0 0 0 0

0 1 1 0 1 1 0 0 0 0 1 0 1 0 0 0

17 17

第四章 同步时序逻辑电路 第三步,画出状态图

18 18

第四章

同步时序逻辑电路

4.4 同步时序路的设计

设计方法

状态转换表的简化

同步时序电路设计举例

19 19

给定逻辑功能 写原始状态图 原始状态表 状态简化得最小化状态表

设 计 方 法

状态编码

选触发器类型,求控制函数、输出函数 画逻辑电路图 画出全状态图, 检查设计,如不 符合要求,重新设计

第五章

时序逻辑电路

4.4 同步时序路的设计

例:设计一“011”序列检测器,每当输入011码时,对应 最后一个1,电路输出为1。 解: 1. 画出原始状态图(或称转移图)与原始状态表 输入端X: 输出端Z: 1/0 A 1/0 D 0/0 0/0 0/0 B 1/0 C 输入一串行随机信号 当X出现011序列时,Z=1;否则Z=0

Q1n

T触发器的状态 方程为:

Xn Q1n Xn Q1n Xn Q1n

Qn 1 TQn TQn

T Qn

Q2 n1 T2 n Q2 n T2 n Q2 n

X Q Q X Q Q 2 n 1 n 2n n n 1 n 代入则得到

6

将T1n、 T2n 两个触发器的状态方程

• 例4.3 假设某同步时序电路的输入为x, 其输出为z。X输入为一组按时间顺序排 列的二进制代码,当输入序列为101时, 输出Z为1,否则Z为0,试作出该电路的 mealy型和moore型原始状态图和状态表。

30 30

第四章

同步时序逻辑电路 4.4 同步时序电路的设计

• 解:设初态为S0;

X=0

1 0 0

0 1 0

1 1 1

0 0 0

1 0 0

1 0 0

1 0 0

0 1 0

10 10

第四章

同 步 时 序 电 路 的 分 析 方

法

同步时序逻辑电路

第二节 同步时序电路分析

写各触发器的控制函数

写电路的输出函数

写触发器的状态方程 作状态转换表及状态转换图 作时序波形图 无要求可不画

简单的电路可直接 绘出状态转换图

得到电路的逻辑功能

5 5

第五章

时序逻辑电路

第二节 同步时序电路分析

例:已知某同步时序电路的逻辑图,试分析电路的逻辑功能 解:1.写出各触发器的控制函数和电路的输出函数 控制函数: T1n = Xn T2n = XnQ1n 输出函数: 2.写状态方程

Zn = XnQ2nQ1n

Q1n Q1n X T1n Q1n T1n Q1n 1 Q2n X

16 16

第四章 同步时序逻辑电路 J K Q J QQ K 第二步,列状态表

2 2 3 1 2,

J 1 Q3 , K1 1

1 3

1

Q3 Q2 Q1 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1

J3K3,J2K2,J1K1 0 1, 0 0, 1 1 0 1, 1 1, 1 1 0 1, 0 0, 1 1 1 1, 1 1, 1 1 0 1, 0 0, 0 1 0 1, 1 1, 0 1 0 1, 0 0, 0 1 1 1 1 1 0 1

1

A/0 C/0 D/1 A/0

11

A B C Q1Q0--两个触发器状态 X 0 1 Q1nQ0n

0 0 0 1 1 0 01/0 01/0 01/0 00/0 10/0 00/1

Sn+1/Zn Sn A B C 0 B/0 B/0 B/0 1 A/0 C/0 A/1

Q1n+1Q0n+1/Zn

Sn+1/Zn

S0

X=1 X=0

S0

X=1

S1

X=1 X=0

S2

X=0

X=1

S3

S1

S1

S0

第五章

时序逻辑电路

4.4 同步时序路的设计

4. 确定触发器类型,编写状态表,求控制函数及输出函数。 触发器类型: 选T触发器 状态转换表 编写状态表: 现 入 现 态 次 态 现控制入 现输出 1)填X=0与X=1时 Q1n+1Q0n+1 T1 T0 Xn Q1n Q0n Zn 电路的现态与次态, 0 1 0 0 0 1 0 0 及相应的现输出 同:T=0 0 0 1 0 1 0 0 0 不同:T=1 2)填写相应的T 、 1 1 0 1 0 0 1 1 0 T0的状态 1 0 0 0 0 0 0 0 根据现态与次态 1 0 1 1 0 1 1 0 决定T值 1 1 0 0 0 1 0 1 3)填T1、T0的卡诺 图,求函数的表达式

24

第四章

同步时序逻辑电路

4.4 同步时序路的设计

全 功能状态转换表

现入 Xn 0 0 0 1 1 1 0 1

现 态 次 态 现控制入 现输出 Q1n Q0nQ1n+1Q0n+1T1 T0 Zn 1 0 0 0 1 0 0 0 1 0 1 0 0 0 1 1 0 0 1 1 0 0 0 0 0 0 0 0 0 1 1 0 1 1 0 1 0 0 0 1 0 1 1 1 1 1 0 0 1 0 1 1 0 1 0 0

第五章

时序逻辑电路

第一节 时序电路概述

第二节 同步时序电路的分析 第三节 同步时序电路的设计

第四节 异步时序电路

1

第四章 第五章

同步时序逻辑电路 时序逻辑电路

本章教学目标

1. 理解时序电路的基本概念;

2. 掌握同步时序电路的描述与分析;

3. 掌握同步时序电路的设计;

4. 掌握异步时序电路的分析; 5. 了解电平异步时序电路。

28 28

00

1/0

0/0 0/0 0/0 1/1

01

1/0 10

11

给定逻辑功能 写原始状态图 原始状态表 状态简化得最小化状态表

设 计 方 法

状态编码

选触发器类型,求控制函数、输出函数 画逻辑电路图 画出全状态图, 检查设计,如不 符合要求,重新设计

第四章

同步时序逻辑电路 4.4 同步时序电路的设计

得到电路的逻辑功能

11 11

第四章

同步时序逻辑电路 例4.1 分析逻辑功能

• 第一步 列输出函数 和控制函数的表达式

J 1 1, K 1 1 x y J K 2 2 1

• 第二步建立状态转换 表

12 12

第四章

输入 x

0 0 0 0

J 1 1, K 1 1 x y 1 J 2 K 2

7 7

第四章

同步时序逻辑电路

第二节 同步时序电路分析

现入 Xn 0 0 0 0 1 1 1 1 现 态 现控制入 次 态 现输出 Q2n Q1n T2n T1n Q2n+1 Q1n+1 Zn 0 0 0 0 0 0 0 0 1 0 0 0 1 0 1 0 0 0 1 0 0 1 1 0 0 1 1 0 1 0 0 0 0 1 0 0 1 1 0 1 0 0 1 0 1 1 1 1 0 1 1 0 0 0 0 1

0/0

Sn A B C D

X

0

B/0 B/0 B/0 B/0

1

A/0 C/0 D/1 A/0

21

1/1

Sn+1/Zn

同步时序电路设计

对任意输入,相 应的输出都相同 2. 状态简化 尽量采用 相邻代码 等价状态可以合并为一个状态 3. 状态编码 00 01 10 Sn A B C D

原始状态表 X 0 B/0 B/0 B/0 B/0 X

1/1

11 1/0

1/0

10

X=0时

保持原态

输出不仅取决于电路本身的状态,而且也与输入变量X有关

电路属于米莱型、可控模4计数器电路

9 9

第四章

同步时序逻辑电路

第二节 同步时序电路分析

4. 作时序波形图

初始状态Q2nQ1n为00,输入X 的序列为1111100111, X=1模4 X=1模4 加计数 X=0 加计数 保持原态

发器的输入及现态量 转换关系的表格 态及组合输出 Z 第二节 同步时序电路分析 Q 1n+1=XnQ1nn

同步时序逻辑电路 输入:输入信号、触 输出:触发器的次 描述输入与状态

Xn Q1n Q2 n Xn Q1n Q2 n

现输出 次 态 Q2n+1 Q1n+1 Zn 0 0 0 0 1 0 1 0 0 1 1 0 0 1 0 1 0 0 1 1 0 0 0 1

23

第五章

时序逻辑电路

4.4 同步时序路的设计

Q1Q0取11组合的态未使用,在卡诺图中暂按无关项处理

T1 Q1 XQ0 表达式为: T XQ XQ 0 0 0

Z XQ1 Q0

根据化简时约束项的使用情况,反填状态表,得全状态表

T0: XQ1Q0为111时,以1对待 XQ1Q0为011时,以0对待

2

2

第四章

同步时序逻辑电路

第一节 时序电路概述

一、组合电路与时序电路的区别 1. 组合电路:电路的输出 只与电路的输入有关,

与电路的前一时刻的状态无关

2. 时序电路:

电路在某一给定时刻的输出

由触发器保存 取决于该时刻电路的输入 还取决于前一时刻电路的状态

时序电路: 组合电路 + 触发器

电路的状态与时间顺序有关

26 26

第四章

同步时序逻辑电路