第7章 半导体存储器与可编程逻辑器件习题解答

数字电路第七章答案

数字电路第七章答案第七章可编程逻辑器件第一节基本内容一、基本知识点(一)可编程逻辑器件基本结构可编程逻辑器件是70年代发展起来的新型逻辑器件,相继出现了只读存储器、可编程只读存储器、可编程逻辑阵列、可编程阵列逻辑、通用阵列逻辑和可擦写编程逻辑器件等多个品种,它们的组成和工作原理基本相似。

的基本结构由与阵列和或阵列构成。

与阵列用来产生有关与项,或阵列把所有与项构成“与或”形式的逻辑函数。

在数字电路中,任何组合逻辑函数均可表示为与或表达式,因而用“与门-或门”两级电路可实现任何组合电路,又因为任何时序电路是由组合电路加上存储元件(触发器)构成的,因而的“与或”结构对实现数字电路具有普遍意义。

在中,输入电路中为了适应各种输入情况,每一个输入信号都配有一缓冲电路,使其具有足够的驱动能力,同时产生原变量和反变量输出,为与门阵列提供互补信号输入。

输出电路的输出方式有多种,可以由或阵列直接输出,构成组合方式输出,也可以通过寄存器输出,构成时序方式输出。

输出既可以是低电平有效,也可以是高电平有效;既可以直接接外部电路,也可以反馈到输入与阵列,由此可见的输出电路根据不同的可编程逻辑器件有所不同。

(二)可编程逻辑器件分类1.按编程部位分类有着大致相同的基本结构,根据与阵列和或阵列是否可编程,分为三种基本类型:(1)与阵列固定,或阵列可编程(2)与或阵列均可编程(3)与阵列可编程,或阵列固定归纳上述的结构特点,列于表7-1。

表7-1 各种的结构特点2.按编程方式分类(1)掩膜编程(2)熔丝与反熔丝编程(3)紫外线擦除、电可编程(4)电擦除、电可编程(5)在系统编程()(三)高密度可编程逻辑器件通常衡量可编程逻辑器件芯片的密度是以芯片能容纳等效逻辑门的数量,一般是以2000为界限,即芯片容纳等效逻辑门小于2000门,称它为低密度可编程逻辑器件或简单的可编程逻辑器件(),若大于2000等效逻辑门,称为高密度可编程逻辑器件()。

第七、八、九章部分习题解答

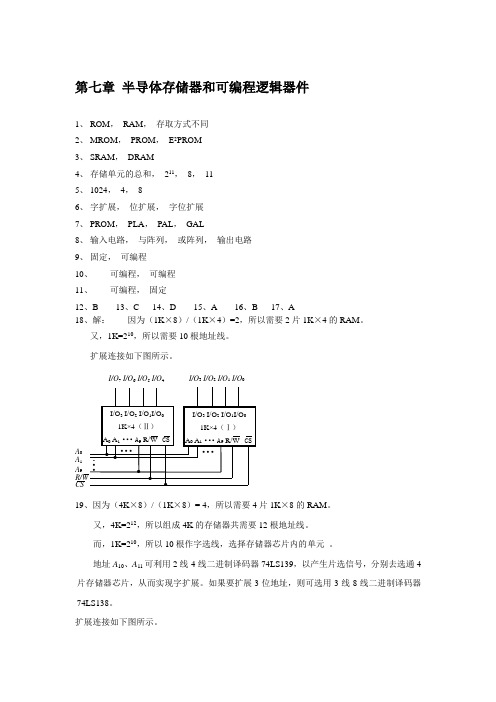

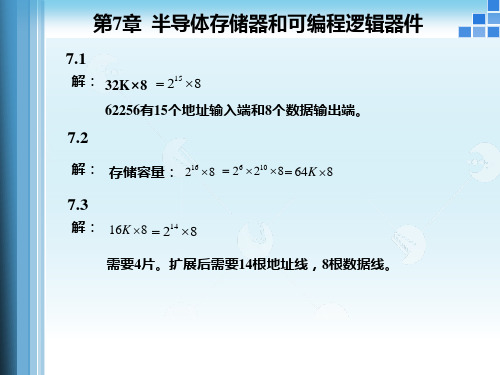

第七章半导体存储器和可编程逻辑器件1、ROM,RAM,存取方式不同2、MROM,PROM,E2PROM3、SRAM,DRAM4、存储单元的总和,211,8,115、1024,4,86、字扩展,位扩展,字位扩展7、PROM,PLA,PAL,GAL8、输入电路,与阵列,或阵列,输出电路9、固定,可编程10、可编程,可编程11、可编程,固定12、B 13、C 14、D 15、A 16、B 17、A18、解:因为(1K×8)/(1K×4)=2,所以需要2片1K×4的RAM。

又,1K=210,所以需要10根地址线。

扩展连接如下图所示。

19、因为(4K×8)/(1K×8)= 4,所以需要4片1K×8的RAM。

又,4K=212,所以组成4K的存储器共需要12根地址线。

而,1K=210,所以10根作字选线,选择存储器芯片内的单元。

地址A10、A11可利用2线-4线二进制译码器74LS139,以产生片选信号,分别去选通4片存储器芯片,从而实现字扩展。

如果要扩展3位地址,则可选用3线-8线二进制译码器74LS138。

扩展连接如下图所示。

第八章 脉冲波形的产生与变换4、(1)工作原理(略);(2)暂稳态维持时间t w =1.1RC=10ms ; (3)u c 和u o 的波形如下图:u ou ct t tu i (ms)(ms)(ms)5 10 25 30 45 503.33V(4)若u i 的低电平维持时间为15m s ,要求暂稳态维持时间t w 不变,可加入微分电路 5、(1)该电路为555定时器构成的施密特触发器。

……………………….........(2) 5脚为外部参考电压输入Vs ,作施密特触发器时,改变的是反转电压Vt +和Vt -,Vt +=Vs 和 Vt-=0.5Vs 。

当大于Vt+或小Vt-时翻转。

调节5脚的电压值 就是调整翻转电压值。

不过不接入Vco 那么默认为Vcc Vt+=2/3VccVt-=1/3Vcc 由电路图可知,电路的阈值电压为TH1s 4V U U ==,TH 2s 12V 2U U ==在给定输入u i 信号条件下,电路输出u o 的波形如图10.4(b)所示。

数电-带答案

第一章 逻辑代数基础 例题1.与(10000111)BCD 相等的十进制数是87, 二进制数是1010111 十六进制数是57,2.AB+CD=0(约束项)求 的最简与或表达式。

解:D C A C B A Z +=,见图1-1, 得3.若F(A,B,C,D)=∑m(0,1,2,3,4,7,15)的函数可化简为: 则可能存在的约束项为( 3 )。

见图1-21.逻辑函数式Y A B C D =++()的反演式为 D C B A + 2. 在下列不同进制的数中,数值最大的数是( D )1051A.() .101010B 2() 163E C.() D.(01011001)8421BCD 码 3、用卡诺图化简下式为最简与或式。

D C B A ++ Y(A,B,C,D)= ∑m(0,2,4,5,6,8,9)+ ∑d(10,11,12,13,14,15) 4.已知F ABC CD =+选出下列可以肯定使F=0的情况( D )A. A=0,BC=1B. B=C=1C. D=0,C=1D. BC=1,D=1 5、是8421BCD 码的是( B )。

A 、1010 B C 、1100 D 、11016、欲对全班43个学生以二进制代码编码表示,最少需要二进制码的位数是( B )。

A 、5B 、6C 、8D 、437、逻辑函数F(A,B,C) = AB+B C+C A 的最小项标准式为( D )。

A 、F(A,B,C)=∑m(0,2,4)B 、F(A,B,C)=∑m(1,5,6,7)C 、F(A,B,C)=∑m (0,2,3,4)D 、F(A,B,C)=∑m(3,4,6,7)Z A BC A B AC D =++Z Z AC AC =+()B C D C D ++1..2..3..4..AC A DA C AB A D A B A B B C++++8、用代数法化简下式为最简与或式。

A+CC B BC C B A BCD A A F ++++=判断题1.若两个函数具有不同的真值表,则两个逻辑函数必然不相等。

数字电子技术基础知识单选题100道(含答案)

数字电子技术基础知识单选题100道(含答案)一、数字逻辑基础1. 以下不属于数字信号特点的是()。

A. 时间上离散B. 数值上离散C. 抗干扰能力强D. 信号幅度连续答案:D。

数字信号在时间和数值上都是离散的,且抗干扰能力强,而模拟信号幅度是连续的。

2. 十进制数15 对应的二进制数是()。

A. 1111B. 1101C. 1011D. 1001答案:A。

15=8+4+2+1,对应的二进制为1111。

3. 二进制数1010 对应的十进制数是()。

A. 8B. 9C. 10D. 11答案:C。

1010=2³+2¹=8+2=10。

4. 8421BCD 码1001 表示的十进制数是()。

A. 9B. 11C. 13D. 15答案:A。

8421BCD 码中1001 对应9。

5. 逻辑函数的最小项之和表达式是()。

A. 唯一的B. 不唯一的C. 有时唯一有时不唯一D. 不确定答案:A。

逻辑函数的最小项之和表达式是唯一的。

二、逻辑门电路6. 以下不属于基本逻辑门的是()。

A. 与门B. 或门C. 非门D. 与非门答案:D。

与非门是由与门和非门组合而成,不属于基本逻辑门。

7. 三输入端与门的输出为0,当且仅当()。

A. 三个输入全为0B. 三个输入全为1C. 至少一个输入为0D. 至少一个输入为1答案:A。

与门只有当所有输入都为1 时输出才为1,否则输出为0。

8. 三输入端或门的输出为1,当且仅当()。

A. 三个输入全为0B. 三个输入全为1C. 至少一个输入为0D. 至少一个输入为1答案:D。

或门只要有一个输入为1 时输出就为1。

9. 非门的逻辑功能是()。

A. 有0 出1,有1 出0B. 全0 出1,全1 出0C. 相同出0,不同出1D. 不同出0,相同出1答案:A。

非门对输入信号取反。

10. 与非门的逻辑功能是()。

A. 有0 出1,全1 出0B. 全0 出1,有1 出0C. 相同出0,不同出1D. 不同出0,相同出1答案:A。

数字电子技术存储器与可编程逻辑器件习题及答案

第8章存储器与可编程逻辑器件8.1存储器概述自测练习1.存储器中可以保存的最小数据单位是()。

(a)位(b)字节(c)字2.指出下列存储器各有多少个基本存储单元?多少存储单元?多少字?字长多少?(a)2K×8位()()()()(b)256×2位()()()()(c)1M×4位()()()()3.ROM是()存储器。

(a)非易失性(b)易失性(c)读/写(d)以字节组织的4.数据通过()存储在存储器中。

(a)读操作(b)启动操作(c)写操作(d)寻址操作5.RAM给定地址中存储的数据在()情况下会丢失。

(a)电源关闭(b)数据从该地址读出(c)在该地址写入数据(d)答案(a)和(c)6.具有256个地址的存储器有()地址线。

(a)256条(b)6条(c)8条(d)16条7.可以存储256字节数据的存储容量是()。

(a)256×1位(b)256×8位(c)1K×4位(d)2K×1位答案:1. a2.(a)2048×8;2048;2048;8(b)512;256;256;2(c)1024×1024×4;1024×1024;1024×1024;43.a4.c5.d6.c7.b8.2随机存取存储器(RAM)自测练习1.动态存储器(DRAM)存储单元是利用()存储信息的,静态存储器(SRAM)存储单元是利用()存储信息的。

2.为了不丢失信息,DRAM必须定期进行()操作。

3.半导体存储器按读、写功能可分成()和()两大类。

4.RAM电路通常由()、()和()三部分组成。

5.6116RAM有()根地址线,()根数据线,其存储容量为()位。

答案:1.栅极电容,触发器2.刷新3.只读存储器,读/写存储器4.地址译码,存储矩阵,读/写控制电路5.11,8,2K×8位8.3 只读存储器(ROM)自测练习1.ROM可分为()、()、()和()几种类型。

半导体器件基础习题答案(完美版)

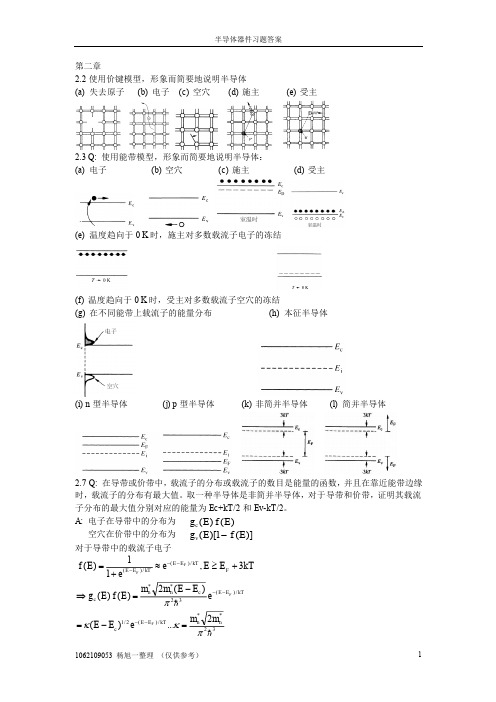

gv ( E )[1 f ( E )]

f (E)

1 1 e

( E E F ) / kT

e ( E EF ) / kT , E EF 3kT

gc (E) f (E)

* * mn 2mn ( E Ec ) ( E EF ) / kT e 2 3 * * mn 2mn 2 3

半导体器件习题答案

A:clear; %specification of basic parameters kT=0.0259; ni=1.0e10; NB=logspace(13,18); EFiD=kT.*log(NB./ni); EFiA=-EFiD; %plot out Fermi level positioning

p ea k , hole

2 3

1 1 1 ( Ev E )1/ 2 E peak,hole Ev kT 1/ 2 2( Ev E ) kT 2

2.16 与浓度相关的问题 (a) Q: 均匀掺杂N A 1015 / cm3 的 p 型硅片,在温度 T 0K 时,平衡状态的空穴和电子 浓度是多少? A: 由于 T 趋于 0 K,因此 n->0,p->0 nN 和 (b) Q: 掺入杂质浓度为 N 的半导体 N ni 且所有的杂质全部被电离, 请判断杂质是施主还是受主?说明理由 A: 杂质是施主,因为 对于施主 n N D , p ni2 / N D 度是多少? A: 硅片在 300K 的温度下的本征载流子浓度为 ni 1010 / cm 3 n 105 / cm3 假设非简并,则 p ni2 / n 1015 / cm3 结果显示确实为非简并 (d) Q: 在温度 T=300K,样品硅的费米能级位于本征费米能级之上 0.259eV 处,空穴和电子 的浓度是多少? A: 硅片在 300K 的温度下的本征载流子浓度为

数字电子技术课后习题答案

ABACBC

BC

A

00 01 11 10

00

1

0

1

11

0

1

0

Y ABC

❖ 3.13某医院有一、二、三、四号病室4间,每室设有 呼叫按钮,同时在护士值班室内对应的装有一号、 二号、三号、四号4个指示灯。

❖ 现要求当一号病室的按钮按下时,无论其它病室的 按钮是否按下,只有一号灯亮。当一号病室的按钮 没有按下而二号病室的按钮按下时,无论三、四号 病室的按钮是否按下,只有二号灯亮。当一、二号 病室的按钮都未按下而三号病室的按钮按下时,无 论四号病室的按钮是否按下,只有三号灯亮。只有 在一、二、三号病室的按钮均未按下四号病室的按 钮时,四号灯才亮。试用优先编码器74148和门电路 设计满足上述控制要求的逻辑电路,给出控制四个 指示灯状态的高、低电平信号。

HP RI/BIN

I0

0/ Z1 0 10 ≥1

I1

1/ Z1 1 11

I2

2/ Z1 2 12 18

YS

I3

3/ Z1 3 13

I4

4/ Z1 4 14

YEX

I5

5/ Z1 5 15

I6

6/ Z1 6 16

I7

7/ Z1 7 17

Y0

V18

Y1

ST

E N

Y2

(b)

74148

(a)引脚图;(b)逻辑符号

A

00 01 11 10

00

0

0

1

11

1

0

1

Y AB BC AC

由于存在AC 项,不存在相切的圈,故无冒险。

❖ 4.1在用或非门组成的基本RS触发器中,已知 输入SD 、RD的波形图如下,试画出输出Q, Q

数字电子技术江晓安答案

数字电子技术江晓安答案【篇一:数字电路教学大纲】txt>一、课程基本情况教学要求:二、课程的性质、目的和任务:①、课程性质:《数字电子技术》是机电一体化技术、电气自动化技术等专业的一门专业基础课,是理论和实际紧密结合的应用性很强的一门课程。

是在学完《电路基础》和《模拟电子技术》课程后,继续学习数字电子技术方面知识和技能的一门必修课。

②、本课程的目的:从培养学生的智力技能入手,提高他们分析问题、解决问题以及实践应用的能力,为学习其它有关课程和毕业后从事电子、电气工程、自动化以及计算机应用技术方面的工作打下必要的基础。

③、本课程的任务:本课程的主要任务是使学生掌握数字电子技术的基本概念、基本理论、基础知识和基本技能,熟悉数字电路中一些典型的、常用的集成电路原理,功能及数字器件的特性和参数。

掌握数字电路的分析方法和设计方法。

通过这门课程的学习和训练,达到掌握先进电子技术的目的。

并为今后学习有关专业课及解决工程实践中所遇到的数字系统问题打下坚实的基础。

本课程的研究内容该课程教学内容主要包括:逻辑代数基础、门电路、触发器等与数电技术及相关的课题。

本课程的研究方法三、本课程与相关课程的联系(先修后修课程)本课程的先修课程是高等数学、普通物理、电路理论及模拟电子技术,本课程应在电路理论课学过一学期之后开设。

要求学生在网络定理(如戴维南定理、迭加原理和诺顿定理等)、双口网络、线性交流电路和暂态分析等方面具有一定基础。

?四、教学内容和基本要求各章节主要内容、重点难点及学生所需掌握的程度。

(一般了解,理解和重点掌握)教学内容:第一章数制和码制第一节概述第二节几种常用的数制第三节不同数制间的转换第四节二进制算术运算第五节几种常用的编码第一节概述第二节逻辑代数中的三种基本运算第三节逻辑代数的基本公式和常用公式第四节逻辑代数的基本定理第五节逻辑函数及其表示方法第六节逻辑函数的化简方法第七节具有无关项的逻辑函数及其化简第三章门电路第一节概述第二节半导体二极管门电路第三节 cmos门电路第四节 ttl门电路第四章组合逻辑电路第一节概述第二节组合逻辑电路的分析方法和设计方法第三节若干常用的组合逻辑电路第四节组合逻辑电路中的竞争——冒险现象第五章触发器第一节概述第二节sr锁存器第三节电平触发的触发器第四节脉冲触发的触发器第五节边沿触发的触发器第六节触发器的逻辑功能及其描述方法第一节概述第二节时序逻辑电路的分析方法第三节若干常用的时序逻辑电路第四节时序逻辑电路的设计方法第五节时序逻辑电路中的竞争——冒险现象第七章半导体存储器第一节概述第二节只读存储器(rom)第三节随机存储器(ram)第四节存储器容量的扩展第五节用存储器实现组合逻辑函数第八章可编程逻辑器件第一节概述第二节可编程阵列逻辑(pal)第三节通用阵列逻辑(gal)第四节可擦除的可编程逻辑器件(epld)第五节复杂的可编程逻辑器件(cpld)第六节现场可编程门阵列(fpga)第七节在系统可编程通用数字开关(ispgds)第八节 pld的编程第九章脉冲波形的产生和整形第一节概述第二节施密特触发器第三节单稳态触发器第四节多谐振荡器第五节 555定时器及其应用第十章数-模和模-数转换第一节概述第二节 d/a转换器第三节 a/d转换器五、课程考核办法课程成绩由两部分组成:平时成绩和期末考试平时成绩考核方式:由学习中心辅导教师负责考核或网上作业系统自测期末考试考核方式:大作业/考试笔试/口试开卷/闭卷总评成绩构成:平时成绩20%;考试成绩80%。

课后习题答案第8章 存储器和可编程逻辑器件

课后习题答案第8章存储器和可编程逻辑器件课后习题答案第8章-存储器和可编程逻辑器件第8章半导体存储器和可编程逻辑器件8-1根据读写功能和信息的可存储性,存储器的类型是什么?并简要描述每种情况自的特点。

答:根据读写功能,存储器可分为只读存储器(ROM)和随机存取存储器(RAM)。

在随机存取存储器的工作过程中,它不仅可以从任何单元读取信息,还可以将外部信息写入任何单元。

因此,它具有读写方便的优点,但由于其波动性,不利于数据的长期保存。

在正常操作期间,存储在只读存储器中的数据是固定的,只能读取,不能在任何时候写入。

ROM是一种非易失性设备。

当设备断电时,存储的数据不会丢失。

存储器按信息的可保存性可分为易失性存储器和非易失性存储器。

易失性存储器在系统关闭时会失去存储的信息,它需要持续的电源供应以维持数据。

非易失存储器在系统关闭或无电源供应时仍能保持数据信息。

8-2什么是sram?什么是dram?它们在工作原理、电路结构和读/写操作的特点是什么?解答:sram(staticrandomaccessmemory)为静态随机存储器,其存储单元是在静态触发器的基础上附加控制电路构成的。

dram(dynamicrandomaccessmemory)为动态随机存储器,常利用mos管栅极电容的电荷存储效应来组成动态存储器,为了避免存储信息的丢失,必须定时地对电路进行动态刷新。

SRAM的数据由触发器存储。

只要不断电,数据就可以保存,但其存储单元中使用的管数很大,因此功耗大,集成度有限。

DRAM通常使用MOS管的栅极电容来存储信息。

由于充电的存储时间有限,为了避免存储数据的丢失,必须由刷新电路定期刷新,但其存储单元中使用的管数较少,因此功耗小,集成度高。

SRAM速度很快,但价格昂贵;DRAM比SRAM 慢,但比ROM快。

8-3少条?回答:存储矩阵是256个字?有8条4位RAM地址线和4条数据线。

若ram的存储矩阵为256字?4位,试问其地址线和数据线各为多一8-4某仪器的存储器有16位地址线,8位数据线,试计算其最大存储容多少钱?解答:最大存储容量为216?8=524288=512kbit(位)8-5其逻辑图。

电子教案-电子技术(第5版_吕国泰)教学资源51134-第7章 半导体存储器和可编程逻辑器件-电子课件

第四节、可编程逻辑器件

5、在系统可编程逻辑器件(ispPLD)

在系统可编程逻辑器件(ispPLD)是20世纪90 年代推出的一种高性能大规模数字集成电路,它成 功地将原属于编程器的有关电路也集成于ispPLD中。 因此, ispPLD的最大特点是,编程时既不需要使 用编程器,也不需要将器件从系统的电路板上取下, 用户可以直接在系统上进行编程。

22

第四节、可编程逻辑器件

2、可编程阵列逻辑(PAL)

可编程阵列逻辑(PAL)是20世纪70年代末期 出现的产品,它是由可编程的与阵列和固定的或阵 列所组成的与或逻辑阵列。

PAL比PLA工艺简单,易于编程和实现,既有 规则的阵列结构,又有灵活多变的逻辑功能,使用 较方便。但其输出方式固定而不能重新组态,编程 是一次性的。

可编程逻辑阵列(PLA)是20世纪70年代中期 出现的逻辑器件,它既包括可编程的与阵列,也包 括可编程的或阵列;不仅可用于实现组合逻辑电路 功能,如果在或阵列的输出外接触发器,还可用于 实现时序逻辑电路功能。

PLA 的与阵列不是全译码,而是可编程的。同 时,其或阵列也是可编程的。用它来实现同样的逻 辑函数,其阵列规模要比ROM小得多。

2、存取周期 连续两次读(写)操作间隔的最短时间称 为存取周期。

一、固定ROM 二、可编程ROM 二、ROM的应用实例

ROM的结构框图 存储矩阵 地址译码器 读出电路

第二节、只读存储器

7

一、固定ROM 1、二极管掩模ROM

第二节、只读存储器

8

第二节、只读存储器

9

2、MOS管掩模ROM

18

(2) RAM的字扩展

第三节、随机存取存储器

19

第四节、可编程逻辑器件

第07章_习题及答案

D、标准“或—与”表达式

二、判断改错题 1.PLA的与门阵列是可编程的,或门阵列是固定的。( X) 2.用PROM实现四位二进制到Gray码的转换时,要求PROM的容量 为4 × 4b。( X ) 3.进行逻辑设计时,采用PLD器件比采用通用逻辑器件更加灵活方 便。( ) 4.用GAL器件即可实现组合电路功能,又可实现时序电路功能。 ( )

二、选择

1. B D 2. D 3. C 4. C 5. C 6.A 7. D 8. C 9.A 10.A 11. D 12.B

可编程逻辑器件习题答案 一、选择题 1、ABC 2、B 3.BCD 4、C 6、D

二、判断 1. 2. 3. 4.

三、填空题

1.输入缓冲 2.寄存器模式 3.固定 4. 可编程 与阵列 可编程 固定 或阵列 输出缓冲 简单模式 可编程 固定 可编程 可编程 PROM PLA PAL GAL 复合模式

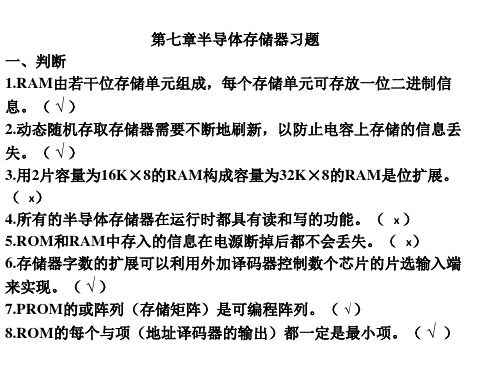

第七章半导体存储器习题 一、判断 1.RAM由若干位存储单元组成,每个存储单元可存放一位二进制信

息。( ) 2.动态随机存取存储器需要不断地刷新,以防止电容上存储的信息丢

失。( ) 3.用2片容量为16K×8的RAM构成容量为32K×8的RAM是位扩展。 ( x) 4.所有的半导体存储器在运行时都具有读和写的功能。( x ) 5.ROM和RAM中存入的信息在电源断掉后都不会丢失。( x) 6.存储器字数的扩展可以利用外加译码器控制数个芯片的片选输入端 来实现。( ) 7.PROM的或阵列(存储矩阵)是可编程阵列。( )

9.一个容量为512×1的静态RAM具有 A 。

B.地址线1根,数据线9根 D.地址线9根,数据线512根 D.无读/无写

10.只读存储器ROM在运行时具有 A 功能。

数字电子技术存储器与可编程逻辑器件习题及答案

第8章存储器与可编程逻辑器件8.1存储器概述自测练习1.存储器中可以保存的最小数据单位是()。

(a)位(b)字节(c)字2.指出下列存储器各有多少个基本存储单元?多少存储单元?多少字?字长多少?(a)2K×8位()()()()(b)256×2位()()()()(c)1M×4位()()()()3.ROM是()存储器。

(a)非易失性(b)易失性(c)读/写(d)以字节组织的4.数据通过()存储在存储器中。

(a)读操作(b)启动操作(c)写操作(d)寻址操作5.RAM给定地址中存储的数据在()情况下会丢失。

(a)电源关闭(b)数据从该地址读出(c)在该地址写入数据(d)答案(a)和(c)6.具有256个地址的存储器有()地址线。

(a)256条(b)6条(c)8条(d)16条7.可以存储256字节数据的存储容量是()。

(a)256×1位(b)256×8位(c)1K×4位(d)2K×1位答案:1. a2.(a)2048×8;2048;2048;8(b)512;256;256;2(c)1024×1024×4;1024×1024;1024×1024;43.a4.c5.d6.c7.b8.2随机存取存储器(RAM)自测练习1.动态存储器(DRAM)存储单元是利用()存储信息的,静态存储器(SRAM)存储单元是利用()存储信息的。

2.为了不丢失信息,DRAM必须定期进行()操作。

3.半导体存储器按读、写功能可分成()和()两大类。

4.RAM电路通常由()、()和()三部分组成。

5.6116RAM有()根地址线,()根数据线,其存储容量为()位。

答案:1.栅极电容,触发器2.刷新3.只读存储器,读/写存储器4.地址译码,存储矩阵,读/写控制电路5.11,8,2K×8位8.3 只读存储器(ROM)自测练习1.ROM可分为()、()、()和()几种类型。

半导体存储器和可编程逻辑器件习题解答

复习思考题6-1ROM一共分为几种,它们都有哪些特性?答:只读存储器(ROM)实际上是一个具有n个输入和m个输出的组合逻辑电路,分为掩模ROM、PROM和EPROM三种。

掩模只读存储器是最早出现的只读存储器,在存储器出厂的时候,存储器中的数据就已经被固化在它的内部了;掩模只读存储器之能够读取数据,而不能写入数据。

PROM的总体结构和掩模ROM相同,都是由地址译码器、存储矩阵和输出电路构成。

PROM和掩模ROM不同的地方则在于,它们的存储单元具有不同的结构;PROM既可以读也可以写,但是只能写入一次。

可擦除的可编程存储器(EPROM)中存储的数据可以被反复擦除和重新编程,所以,它的应用范围比PROM更加广泛。

6-2为什么说ROM实际上一种组合逻辑电路?答:因为ROM中没有时钟信号,地址输入端和数据输出端构成了组合逻辑的一一对应关系。

6-3掩模ROM和PROM有什么区别?答:PROM和掩模ROM不同的地方则在于,它们的存储单元具有不同的结构;掩模只读存储器只能够读取数据,而不能写入数据,PROM既可以读也可以写,但是只能写入一次。

6-4PROM和EPROM的最大区别是什么?答:PROM存储单元和EPROM不同。

前者主要是熔丝和反熔丝结构,而后者则采用各种可擦除半导体结构。

PROM只能写一次,而EPROM能反复地擦和写。

6-5SRAM和DRAM的区别是什么?在实际中,它们各自有什么用途?答:它们的存储单元结构不同。

SRAM不需要刷新,而DRAM需要不断地周期性地刷新。

6-6当字数不够用,位数也不够用时,应该怎样扩展存储器的存储容量?答:可以进行字扩展和位扩展。

6-7可编程逻辑器件主要有哪几种?答:有PAL、GAL、CPLD和FPGA等6-8PAL器件和ROM的区别是什么?答:ROM只有或阵列都可以编程,而与阵列不能编程;PAL只有与阵列能编程,或阵列是固定的。

6-9怎样用PAL实现任意组合逻辑函数?用PAL实现任意组合逻辑函数有什么限制?答:先将逻辑函数式化简,再按照乘积和的方式在PAL中进行编程。

模电课件第七章 半导体存储器和可编程逻辑器件

(2)可编程逻辑器件

(Programmable Logic Device,PLD)

可编程逻辑器件是20世纪70年代后期发展起来的一种功能特殊 的大规模集成电路,它是一种可以由用户定义和设置逻辑功能 的器件。 特点:结构灵活、集成度高、处理速度快、可靠性高

(3)微处理器

微处理器主要指通用的微处理机芯片,它的功能由汇编语言 编写的程序来确定,具有一定的灵活性。但该器件很难与其 他类型的器件直接配合,应用时需要用户设计专门的接口电 路。 微处理器是构成计算机的主要部件。目前除用作CPU外,多 用于实时处理系统。

2. PLD器件的连接表示方法 (1)PLD 器件的连接表示法

固定连接

可编程连接

不连接

(2)门电路表示法

1

A

A

A

1

A

A

A

反向缓冲器

A

&

B

F

C

ABC

&

F

与门

A

≥1

B

F

C

ABC

≥1

F

或门

缓(冲d)器

ABC

(3) 阵列图

1

1

1

& D=BC

& E=AABBCC=0 & F=AABBCC=0

& G=1

1)浮栅注入 MOS 管(FAMOS 管) 存储单元采用两只 MOS管 缺点:集成度低、击穿电压高、速度较慢

2)叠层栅注入 MOS 管(SIMOS 管)

层叠栅存储单元

叠层栅MOS管剖面示意图

控制栅 与字线 相连,控制信息的 读出和写入

浮栅 埋在二氧化硅绝缘层, 处于电“悬浮”状态, 不与外部导通,注入电 荷后可长期保存

数电-半导体存储器练习题

× √

B D

SRAM 以上都对

× ×

分析提示

DRAM利用 利用MOS管的栅极电容对电荷的存储效应存储信息, 管的栅极电容对电荷的存储效应存储信息, 利用 管的栅极电容对电荷的存储效应存储信息 电荷不能长期存储。 电荷不能长期存储。 SRAM 以寄存器为存储元件,只有在带电状态下才能存储信息。 以寄存器为存储元件,只有在带电状态下才能存储信息。 DRAM、 SRAM 属于“易失性”存储器,不能实现组合逻辑函 属于“易失性”存储器, 、 数。 EPROM,利用 管作存储元件, ,利用MOS管作存储元件,存储矩阵的字、位线交叉 管作存储元件 存储矩阵的字、 处接入不接入存储元件的连接方式决定所存储信息的内容是0或 , 处接入不接入存储元件的连接方式决定所存储信息的内容是 或1, 连接方式确定后所存储的信息可长期保存不变, 连接方式确定后所存储的信息可长期保存不变,可实现组合逻辑函 数

第

4

页

数字电子技术

第 7 章 半导体存储器

单项选择题 ( )。

4、有 10 位地址和 8 位字长的存储器,其存储容量为 、 位字长的存储器, A C 256×10 位 × 1024×10 位 ×

× ×

B D

512×8 位 × 1024×8 位 ×

× √

分析提示

10 位地址所对应 存储字数为: 210=1024 存储字数为: 每个字的字长为: 每个字的字长为: 8 位 字数× 存储容量 = 字数×字长 =1024 × 8 位

第

14

页

数字电子技术

第 7 章 半导体存储器

单项选择题 )。

14、只读存储器ROM,当电源断电后再通电时,所存储的内容 ( 、只读存储器 ,当电源断电后再通电时, A C 全部改变 不确定

第7章 存半导体储器与可编程逻辑器件(习题)

YY21

AC A

BC AB BC

Y0 AB AC

Y0 m3 m5 m6 m7

YY21

m3 m0

m4 m2

m6 m3

m7 m4

m5

m6

m7

Y3 m1 m3 m6 m7

7.8

解: 列出ROM数据表:

Y3 m(5,6,7,8,9) Y2 m(1,2,3,4,9) Y1 m(0,3,4,7,8) Y0 m(0,2,4,6,8)

A2 A1 A0 A2 A1A0 A2 A1 A0 A1 A0 A2 A1A0

D1 m(0,2,4,6) A2 A1 A0 A2 A1 A0 A2 A1 A0 A2 A1 A0

A2 A0 A2 A0 A0

7.7 解: 先把逻辑表达式化成最小项的形式。

Y0 AB AC BC

D2 m(1,6,7)

A2 A1A0 A2 A1 A0 A2 A1A0

A2 A1A0 A2 A1

D1 m(0,3,4)

地址/输入 A2 A1 A0 000 001 010 011 100 101 110 111

数据/输出 D3 D2 D1 D0 0011 1100 1001 0010 0011 1000 0101 1100

需要4片。扩展后需要12根地址线,4根数据线。

7.5

解: 8K 8 213 8

需要16片。扩展后需要13根地址线,8根数据线。

7.6

解:D3 m(1,2,5,7)

A2 A1A0 A2 A1 A0 A2 A1A0 A2 A1A0 A2 A1A0 A2 A1 A0 A2 A0 A1A0 A2 A1 A0 A2 A0

ABCD ABCD

Y1 ABC D ABC D ABC D ABCD

《数字电子技术基础》第六章习题答案

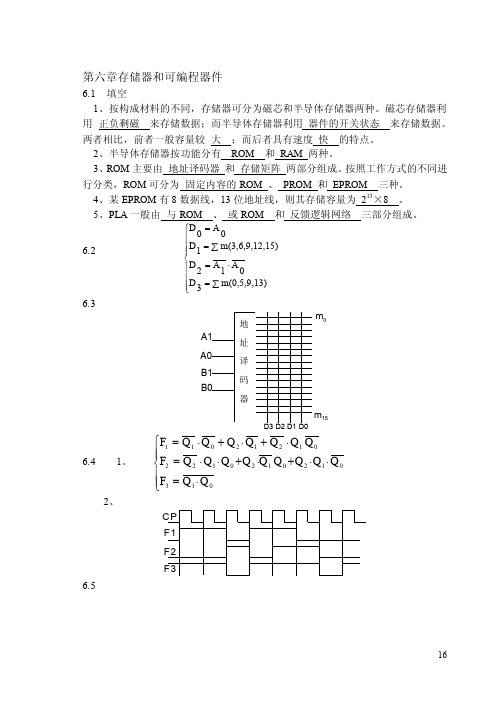

第六章存储器和可编程器件6.1 填空1、按构成材料的不同,存储器可分为磁芯和半导体存储器两种。

磁芯存储器利用 正负剩磁 来存储数据;而半导体存储器利用 器件的开关状态 来存储数据。

两者相比,前者一般容量较 大 ;而后者具有速度 快 的特点。

2、半导体存储器按功能分有 ROM 和 RAM 两种。

3、ROM 主要由 地址译码器 和 存储矩阵 两部分组成。

按照工作方式的不同进行分类,ROM 可分为 固定内容的ROM 、 PROM 和 EPROM 三种。

4、某EPROM 有8数据线,13位地址线,则其存储容量为 213×8 。

5、PLA 一般由 与ROM 、 或ROM 和 反馈逻辑网络 三部分组成。

6.2 D 0A 0D 1m(3,6,9,12,15)D 2A 1A 0D 3m(0,5,9,13)==∑=⋅=∑⎧⎨⎪⎪⎪⎩⎪⎪⎪ 6.3地址译码器A1A0D3 D2 D1 D0B1B0m 0m 156.4 1。

F Q Q Q Q Q Q Q F Q Q Q Q Q Q Q Q Q F Q Q 110212102210210210310=⋅+⋅+⋅=⋅⋅+⋅+⋅⋅=⋅⎧⎨⎪⎪⎩⎪⎪2、CP F1F2F36.5A AB BC C i-1i-1S i C i6.6 用PLA 实现BCD8421码十进制加法计数器和相应的显示译码电路。

D 1Q1Q1D2 Q2 Q2D3 Q3Q3D4Q4Q49 87654 3210a b c d e f ga b cdef g下面资料为赠送的地产广告语不需要的下载后可以编辑删除就可以,谢谢选择,祝您工作顺利,生活愉快!地产广告语1、让世界向往的故乡2、某沿河楼盘:生活,在水岸停泊3、一江春水一种人生4、某钱塘江边楼盘:面对潮流经典依旧5、海景房:站在家里,海是美景;站在海上,家是美景6、以山水为卖点的楼盘:山水是真正的不动产7、某城区的山腰上的楼盘:凌驾尊贵俯瞰繁华8、某地势较高的楼盘:高人,只住有高度的房子9、某学区房:不要让孩子输在起跑线上10、尾盘:最后,最珍贵11、回家就是度假的生活12、生命就该浪费在美好的事情上我们造城——2、我的工作就是享受生活——3、我家的客厅,就是我的生活名片——4、在自己的阳台看上海的未来——5、公园不在我家里我家住在公园里——6、这里的花园没有四季——7、***,装饰城市的风景——8、***,我把天空搬回家——9、房在林中,人在树下——10、生活,就是居住在别人的爱慕里——11、到〖星河湾〗看看好房子的标准——12、好生活在〖珠江〗——13、爱家的男人住〖百合〗城市岸泊:城市的岸泊,生活的小镇生活之美不缺少,在于发现情趣不在于奢华,在于精彩生活有了美感才值得思考……玫瑰庄园:山地生态,健康人生卓越地段,超大社区一种完整且完善的环境,像原生一样和谐原生景象自然天成人本理念精品建筑知名物业智能安防诚信为本实力铸造比华利山庄:海岸生活——引领世界的生活方式海岸生活——22公里的奢华海岸生活——高尚人生的序曲海岸生活——人与自然的融合苹果二十二院街:人文自然现代铺的蔓伸荣和山水美地:让世界向往的故乡香港时代:时代精英开拓未来领衔建筑,彰显尊贵绿地崴廉公寓:金桥40万平方米德国音乐艺术生活汇都国际:昆明都心,城市引擎财富之都风情之都梦幻之都文化之都商贸之都西部首座巨型商业之城颠峰商圈的原动力,缔造西部财富新领地新江湾城:绿色生态港国际智慧城新江湾城,一座承载上海新梦想的城区上海城投,全心以赴建设知识型,生态型花园城区风和日丽:入住准现楼,升值在望湾区大户,空中花园大格局下的西海岸市中心:市中心少数人的专属颠峰珍贵市中心的稀世名宅正中心城市颠峰领地颠峰勾勒稀世名宅繁华不落幕的居家风景地利皇者尽得先机稀世经典180席阳光国际公寓:阳光金桥来自纽约的生活蓝本钟宅湾:海峡西岸生态人居休闲商务区汇聚国际财富与人居梦想的绝版宝地二十一世纪是城市的世纪,二十一世纪也是海洋的世纪谁控制了海洋,谁就控制了一切站在蓝色海岸的前沿,开启一个新的地产时代东南门户海湾之心海峡西岸生态人居休闲商务区让所有财富的目光聚集钟宅湾,这里每一天都在创造历史上海A座(科维大厦):创富人生的黄金眼掘金上海!创富人生!远东大厦:花小公司的钱,做大公司的事未来城:无可挑战的优势无可限量的空间绿地集团:居住问题的答疑者,舒适生活的提案人茶马驿栈:精明置业时机享受附加值财富最大化雪山下的世外桃源茶马古道上千年清泉之乡金地格林春岸:城市精英的梦想家园繁华与宁静共存,阔绰身份不显自露建筑覆盖率仅20%,令视野更为广阔占据最佳景观位置,用高度提炼生活完美演绎自然精髓,谱写古城新篇章创新房型推陈出新,阔气空间彰显不凡365天的贴身护卫,阔度管理以您为尊金地格林小城:心没有界限,身没有界限春光永驻童话之城我的家,我的天下东渡国际:梦想建筑,建筑梦想齐鲁置业:传承经典,创新生活比天空更宽广的是人的思想创新远见生活嘉德中央公园:一群绝不妥协的居住理想家完成一座改变你对住宅想象的超越作品极至的资源整合丰富住家的生活内涵苛求的建造细节提升住家的生活品质地段优势,就是永恒价值优势设计优势,就是生活质量优势景观优势,就是生命健康优势管理优势,就是生活品味优势空中华尔兹:自然而来的气质,华尔兹的生活等级享受,没有不可逾越的极限所谓完美的习惯,是舒适空间的心情定格!临江花园:经典生活品质风景中的舞台美林别墅:源欧美经典纯自然空间住原味别墅赏园林艺术淡雅怡景温馨自然钱江时代:核心时代,核心生活核心位置创意空间优雅规划人文景观财富未来城市精神,自然风景,渗透私人空间泰达时尚广场:是球场更是剧场城市经济活力源时尚天津水舞中国未来都会休闲之居创意时尚天天嘉年华健康快乐新境界商旅新天地缔造好生意城市运营战略联盟,参与协作,多方共赢华龙碧水豪园:浪漫一次,相守一生东方莱茵:品鉴品位宜家宜人建筑一道贵族色彩品鉴一方美学空间品位一份怡然自得荡漾一股生命活力坐拥一处旺地静宅体会一种尊崇感受常青花园(新康苑):新康苑生活感受凌驾常规大非凡生活领域成功人士的生活礼遇拥有与自己身份地位相等的花园社区在属于自己的宴会餐厅里会宾邀朋只与自己品味爱好相同的成功人士为邻孩子的起步就与优越同步酒店式物管礼遇拥有[一屋两公园前后是氧吧]的美极环境水木清华:住在你心里福星惠誉(金色华府):金色华府,市府街才智名门——释放生命的金色魅力真正了解一个人,要看他的朋友,看他的对手。

第7章 半导体存储器与可编程逻辑器件习题解答

思考题与习题7.1 选择题7.14 选择题1)存储容量为8K×8位的ROM 存储器,其地址线为 条。

CA 、8B 、12C 、13D 、142)只能按地址读出信息,而不能写入信息的存储器为 。

bA 、 RAMB 、ROMC 、 PROMD 、EPROM3)一片ROM 有n 根地址输入,m 根位线输出,则ROM 的容量为 。

a A 、m n⨯2 B 、n m ⨯ C 、mn 22⨯ D 、n m⨯24)一个6位地址码、8位输出的ROM ,其存储矩阵的容量为 。

A 、46B 、64C 、512D 、256 5)为构成4096×8的RAM ,需要 片2024×2的RAM ,并需要有 位地址译码以完成寻址操作。

A 、8 ,15B 、16,11C 、10,12D 、8,12 6)PAL 是一种的 可编程逻辑器件。

A 、与阵列可编程,或阵列固定B 、与阵列列固,或阵可编程定C 、与阵列、或阵列固定D 、与阵列、或阵列可编程7.2 试写出如图7-27所示阵列图的逻辑函数表达式和真值表,并说明其功能。

1F 2F 3图6-1 例6-1逻辑图图7-27 题7.2图解:根据与阵列的输出为AB 的最小项和阵列图中有实心点“·”为1,无“·”为0,可以写出:AB W F ==30B A AB B A B A W W W F +=++=++=3211B A B A B A F ⊕=+=2AB B A B A B A B A W W W F =+=++=++=2103从上述逻辑表达式可以看出,图7-1所示阵列图实现了输入变量A 、B 的四种逻辑运算:与、或、异或和与非。

列出真值表如表7-1所示。

7.3 若存储器芯片的容量为128K×8位,求:表7-1 例7-1真值表1)访问芯片需要多少地址?2)假定该芯片在存储器中首地址为A00000H ,末地址为多少? 解:存储器容量=字数×位数=m n⨯21)128K×8=8282217107⨯=⨯⨯,所以需要17根地址。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

思考题与习题7.1 选择题7.14 选择题1)存储容量为8K×8位的ROM 存储器,其地址线为 条。

CA 、8B 、12C 、13D 、142)只能按地址读出信息,而不能写入信息的存储器为 。

bA 、 RAMB 、ROMC 、 PROMD 、EPROM3)一片ROM 有n 根地址输入,m 根位线输出,则ROM 的容量为 。

a A 、m n⨯2 B 、n m ⨯ C 、mn 22⨯ D 、n m⨯24)一个6位地址码、8位输出的ROM ,其存储矩阵的容量为 。

A 、46B 、64C 、512D 、256 5)为构成4096×8的RAM ,需要 片2024×2的RAM ,并需要有 位地址译码以完成寻址操作。

A 、8 ,15B 、16,11C 、10,12D 、8,12 6)PAL 是一种的 可编程逻辑器件。

A 、与阵列可编程,或阵列固定B 、与阵列列固,或阵可编程定C 、与阵列、或阵列固定D 、与阵列、或阵列可编程7.2 试写出如图7-27所示阵列图的逻辑函数表达式和真值表,并说明其功能。

1F 2F 3图6-1 例6-1逻辑图图7-27 题7.2图解:根据与阵列的输出为AB 的最小项和阵列图中有实心点“·”为1,无“·”为0,可以写出:AB W F ==30B A AB B A B A W W W F +=++=++=3211B A B A B A F ⊕=+=2AB B A B A B A B A W W W F =+=++=++=2103从上述逻辑表达式可以看出,图7-1所示阵列图实现了输入变量A 、B 的四种逻辑运算:与、或、异或和与非。

列出真值表如表7-1所示。

7.3 若存储器芯片的容量为128K×8位,求:表7-1 例7-1真值表1)访问芯片需要多少地址?2)假定该芯片在存储器中首地址为A00000H ,末地址为多少? 解:存储器容量=字数×位数=m n⨯21)128K×8=8282217107⨯=⨯⨯,所以需要17根地址。

2)由于8217⨯=172=(100000000000000000)2字节=20000H 字节。

也就是说8217⨯的芯片包含20000H 个字节,每个字节占用一个地址,则需要占用20000H 个地址。

因此,若该芯片在存储器中的首地址为A00000H ,则末地址为:A00000H+20000H-1H= A00000H+1FFFF=BFFFFH7.4 试用ROM 实现下列各函数解:本题是组合逻辑函数的实现,分析步骤如下:(1)写出各函数的标准与或表达式:按A 、B 、C 、D 顺序排列变量,将Y1、Y2、Y4扩展成 为四变量逻辑函数。

(2)选用16×4位ROM ,画存储矩阵连线图:CABC Y +=2BCDACD ABD ABC Y +++=4),,,,(),,,,,(),,,,,(),,,,,,,(15141311715129630151411107615149854324321m m m m Y Y Y Y ∑=∑=∑=∑=7.5 试用ROM 构成能实现函数y=x 2的运算表电路,x 的取值范围为0~15的正整数。

解:本题是ROM 的应用,分析如下: (1)分析要求、设定变量自变量x 的取值范围为0~15的正整数,对应的4位二进制正整数,用B =B 3B 2B 1B 0表示。

根据y =x 2的运算关系,求出y 的最大值是152=225,可以用8位二进制数Y =Y 7Y 6Y 5Y 4Y 3Y 2Y 1Y 0表示。

(2)列真值表—函数运算表(3)写标准与或表达式⎪⎪⎪⎪⎪⎪⎩⎪⎪⎪⎪⎪⎪⎨⎧========∑∑∑∑∑∑∑)15,13,11,9,7,5,3,1(0)14,10,6,2()13,11,5,3()12,11,9,7,5,4()15,13,11,10,7,6()15,14,11,10,9,8()15,14,13,12(01234567m Y Y m Y m Y m Y m Y m Y m Y(4)画ROM存储矩阵结点连接图为做图方便,我们将ROM矩阵中的二极管用节点表示。

7.6 用一片GAL16V8设计一个带进位的同步64进制计数器,要求该计数器具有复位(清零)和使能功能。

画出引脚配置图。

解:根据教材实现N位任意进制计数器设计说明,得到64进制计数器的逻辑图如图7-3所示。

图7-3 64进制计数器逻辑图0Q123441234567891020191817161514131211CLKCRENCNCNCNCNCNCGNDV CCNCQ5Q4Q3Q2Q1Q0Q COEGAL16V8图7-4 引脚配置图根据逻辑图,画出GAL16V8的引脚配置图,如图所示。

7.7 将1K*4的RAM芯片扩展为2K*4的存储器系统。

解:第一片的存储容量为1K*4地址范围是A10 A9 A8 A7…A00 0 0 00000000 000H0 1 1 11111111 3FFH第二片的存储容量为1K*4地址范围是A10 A9 A8 A7…A01 0 0 00000000 400H1 1 1 11111111 7FFH7.8 试用EPROM 实现一组逻辑函数:Y ABC ABD ACD BCDY ABC ABD ACD BCD Y ABCD ABCD Y ABCD1234=+++=+++=+=指出需要多大容量的EPROM ,并且列出存储矩阵的存储内容表。

解:需要424⨯位,即16×4位容量的EPROM 。

经过函数变换,可得:ABCDY D C B A ABCD Y D C B A D C B A D C B A D C B A D C B A D C B D C A D B A C B A Y ABCD D ABC D C AB CD B A BCD A BCD ACD ABD ABC Y =+=++++=+++=++++=+++=43217.9 由16×4位ROM 和4位二进制加法计数器74LS161组成的脉冲分配电路如图7-28所示,ROM 输入、输出关系如表7-8所示。

试画出在CP 信号作用下D 3、D 2、D 1、D 0的波形。

1图6-9 计数器和ROM 构成的逻辑图输出图7-28 题7.9图表7-8 ROM 的输入输出关系 地址输入数据输出A 0A 1A 2A 3D 0D 1D 2D 300000001001000110100010101100111100010011010101111001111000000110100010110101001100011111100000100100001110111101111010001110表6-3 ROM 输入输出关系解:题中给定的逻辑图可见,4位二进制计数器74LS161的数据输入端D 3D 2D 1D 0为0001,进位输出C 通过非门送给预置数端D L ,构成了15进制计数器。

根据给定的表6-3数据输出和地址输入之间的关系可以画出在CP 脉冲作用下D 3、D 2、D 1、D 0的波形图如图所示。

CPA0A1A2A3D0D1D2D3图6-10 题6-10的波形图7.10 试用EPROM设计一个能将四位二进制数转换位循环码的代码转换电路,要求列出代码转换电路的真值表,画出阵列图。

解:四位二进制码转换成四位循环码的真值表,如表6-2所示。

由于输入变量和输出变量均为四位,故EPROM须有四个地址输入端和四条数据线。

所以选用16×4的EPROM。

因为与、或阵列的输出均为最小项和其表达式,所以用ROM设计组合逻辑电路无需化简。

由真值表画出阵列图比较直观。

逻辑图如图7-3所示。

表7-3 例7-3真值表B B B B 与 门 阵 列地 址 译 码 器G 3G 2G 1G 0图6-2 例6-2 逻辑图7.11 试用EPROM 实现Y=X 的转换(精确到个位)。

式中X的范围为0~2047,Y的范围为0~45,要求画出电路图,并列出从000H ~01FH 以及7E0H ~7FFH 的存储器真值表(000H 之后的H 表示000为十六进制数)。

解:可选用EPROM 27C16(2K ×8位)来实现。

输入X 的范围为0~2047,转换为二进制后为000H ~7FFH (用十六进制数表示),共11位,而27C16有11根地址输入线,正好可以将输入X 所对应的二进制数作为地址信号10A ~0A 。

输出Y 的范围为0~45,27C16的字长为8位,可表示两位十进制数(用8421BCD 码表示),范围为00~99,满足输出Y 的要求。

所以,我们设计为输出为两位十进制数的8421BCD 码。

当然,输出也可以设计为输出二进制数,这样,输出只用其中的6位0D ~5D ,6D 和7D 不用。

000H ~01FH 的存储器真值表如下表(输出精确到个位,十分位四舍五入)。

7E0H~7FFH的存储器真值表如下表(输出精确到个位,十分位四舍五入)。

7.12 把1024*4的RAM扩展为1024*8的 RAM解:7.13ROM和RAM有什么相同和不同之处?ROM写入信息有几种方式?解:ROM和RAM都是存储器,可以用来写入二进制信息。

不同之处是ROM写入之后不能擦除(只能通过特殊方法擦除);RAM可以随机存取信息。

ROM写入信息有以下几种方式:固定ROM由厂家写入;可编程ROM由用户将熔丝通过大电流写入信息;可擦可编程ROM可以多次写入和擦除信息,但需要经过专门的编程器,实现光和电擦除等。

7.14下列RAM各有多少条地址线?⑴512×2位⑵1K×8位⑶2K×1位⑷16K×1位⑸256×4位⑹64K×1位解:⑴512×2位:512=29,故有9个地址输入端。

⑵1K×8位:1K=1024=210,故有10个地址输入端。

⑶2K×1位:2K=2048=211,故有11个地址输入端。

⑷16K×1位:16K=214,故有14个地址输入端。

⑸256×4位:256=28,故有8个地址输入端。

⑹64K×1位:64K=216,故有16个地址输入端。

7.15 可编程逻辑器件是如何进行分类的?解:⑴根据芯片的集成度和结构复杂度分类分为:①简单可编程逻辑器件SPLD②复杂可编程逻辑器件CPLD③现场可编程逻辑门阵列FPGA。

⑵按制造技术和编程方式进行分类①双极熔丝制造技术的可编程ASIC(Lattice的PAL系列)②EECMOS制造技术的可编程ASIC(Lattice的GAL和ispLSI / pLSI)③SRAM制造技术的可编程ASIC(Xilinx 的FPGA,Altera的FPGA)④反熔丝制造技术的可编程ASIC(Actel的FPGA)。