数字逻辑第三次大作业

白中英数字逻辑习题答案

T2.1 分析下图所示的逻辑电路,写出表达式并进行简化。

A B

F

F = AB + B = AB

A

B

F

C

F = AB BABC CABC = AB + AC + BC + BC = AB + BC + BC

T2.2 分析下图所示的逻辑电路,写出表达式并进行简化。

A

AD

BD

B

BD

F

BC

C CD

D

[解]

T2.5 右图所示为数据总线上的一种判零电路,写出F的逻辑表达式, 说明该电路的逻辑功能。

A0

A3 A4

A7

F

A8

A11 A12

A15

[解]

F= A0A1A2A3+A4A5A6A7+A8A9A10A11+A12A13A14A15 = A0A1A2A3A4A5A6A7A8A9A10A11A12A13A14A15

[解] 先由 F→ F’,在由 F’→ F,得: F = A + B+C

(2) F(A,B,C,D) = Σ(0,1,5,7,10,11,12,13,14,15)

AB CD 00 01 11 10

00 1

1

01 1 1 1

[解1] F = A B C + AB + BD + AC = A+B+C + A+B + B+D + A+C

AB CD 00 01 11 10

00

111

01 1 1

1

11 1

1

10

1

ABCD F

数字逻辑大作业

数字逻辑大作业汽车尾灯控制器实验要求设计一个汽车尾灯控制器。

汽车尾部左右两侧各有3个指示灯。

根据汽车运行情况,指示灯有4种显示模式:(1)汽车正向行驶,所有指示灯全部熄灭。

(2)汽车右转弯,右侧的三个指示灯按右循环模式顺序点亮。

(3)汽车左转弯,左侧的三个指示灯按左循环模式顺序点亮。

(4)临时刹车,左右两侧的指示灯同时处于闪烁状态。

总体流程具体设计1.尾灯状态表2.电路各模块3.计数器因为考虑到转向时是三个灯一组循环点亮,所以决定构造三进制计数器。

构造三进制计数器的方法很多,我们采用了十进制可逆计数器74LS192芯片对于74LS192来说,置数端LDN接高电平置数无效,减计数脉冲触发信号DN接高电平,加计数脉冲触发信号UP接收时钟脉冲信号。

A B C D无需输入信号,接地避免悬空,当电路从00(0)计数到11(3)时,QA,QB通过一个与门,使得CLR清零端为1,计数器又从00开始计数。

由此,计数器共有00,01,10,11(00)三个状态,三进制计数器构建完成。

因为计数器有两个输出端,在加上一个选择开关的信号,共有三个输入,所以采用了74LS138 3线-8线译码器。

选择000,001,010作为一组转向,100,101,110作为另一组转向,两个低位正好符合计数器的输出,高位正好可以看成其中一个开关是否打开。

选通端G1接高电平时,所有输出均为高电平,正好可以对其处理,使之配合时钟信号进行闪烁操作。

5.开关控制电路通过如图所示的输入电路,i1直接接到74LS138译码器的C输入端,i2与i1通过一个异或门与74LS138的选通端G1相连,G=i1 ⊕i2,时钟,i1,i2 通过一个三输入与非门相连,其输出作用于灯泡输入,保证时钟信号的传递,来实现灯随时钟信号闪灭。

当i1=i2=0时,所有与非门都是低电平,此时所有的发光二极管都不会发亮,符合汽车正常行驶时的状态。

当i1=i1=1时,输入均处于无效状态,Y0N~Y7N都输出高电平,此时三输入与非门能输出时钟脉冲,所有灯泡就可以随着时钟脉冲闪灭。

2020秋西安电子科技大学《数字逻辑电路》大作业期末试题及答案

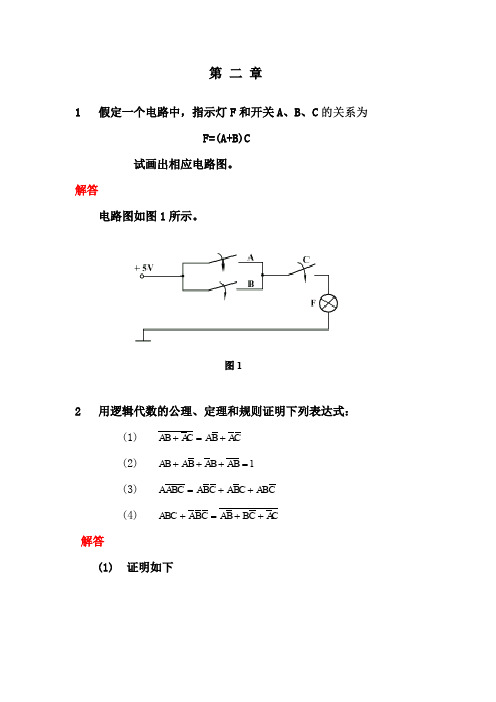

学习中心/函授站_姓名学号西安电子科技大学网络与继续教育学院2020 学年下学期《数字逻辑电路》期末考试试题(综合大作业)题号一二三四总分题分30 10 30 30得分考试说明:1、大作业试题于2020 年10 月15 日公布:(1)毕业班学生于2020 年10 月15 日至2020 年11 月1 日在线上传大作业答卷;(2)非毕业班学生于2020 年10 月22 日至2020 年11 月8 日在线上传大作业答卷;(3)上传时一张图片对应一张A4 纸答题纸,要求拍照清晰、上传完整;2、考试必须独立完成,如发现抄袭、雷同均按零分计;3、答案须用《西安电子科技大学网络与继续教育学院标准答题纸》手写完成,要求字迹工整、卷面干净。

一、单项选择题(每小题2 分,共40 分)1、下列各数中与十进制数101 不相等的数是( D )。

A.(0100 0011 0100)余3BCD B.(141)8C.(1100101)2D.(66)162、八进制数(35)8的8421BCD 是( B )。

A.0011 1000B.0010 1001C.0011 0101D.0010 11003、为使与非门输出为1 则输入( A )。

A.只要有0 即可B.必须全为0C.必须全为1D.只要有1 即可4、函数F AC BC AB与其相等的表达式是( B )。

A.BC B.C+AB C.AC AB D.AB5、使函数F AB AC BC 等于 0 的输入 ABC 的组合是( C )。

A .ABC=111 B .ABC=110 C .ABC=100 D .ABC=0116、四变量的最小项ABCD 的逻辑相邻项是( A )。

A .ABCDB .ABCDC .ABCD D .ABCD 7、函数 F ABC B .C (A D )BC 的对偶式是( C )。

A .G (A B C )(B C )(AD B C )B .G A BC (B C )ADB CC .G A B C (B C )(AD B C )D .G A BC (B C )AD B C8、FA B C ADE BDE ABC 的最简式为( A )。

数字逻辑第3章习题参考解答

3.68

分析图 3-37 所示反相器的下降时间,设 RL=900Ω ,VL=2V。

解:该电路图可以等效为下列带开关的一阶电路图。当输出从高态转 为低态时,可以等效为开关 K 从位置 1 转到位置 2。

按照一阶电路三要素法的分析方法,对于电容上的电压分析如下: 初态:VH=4.45V 终态:VL=0.2V

VOUT VL VH VL (1 e t / )

由上式可以得出从 1.5V 到 3.5V 的上升时间为:

t ln VH 1.5 19ns VH 3.5

可以驱动。

I=(3.84-2.03)/0.487 = 3.72 < 4mA

可以驱动。

3.40 一个发光二极管导通时的电压降约为 2.0V,正常发光时需要约 5mA 的电流。当发光二极管如图 3-54(a)那样连接时,确定上拉电 阻的适当值。 解:根据 3.7.5 所给的条件,低态输出电平 VOLmax=0.37V。 对应等效 电路如下:

13 画出 NOR3 对应的电路图。 解:3 输入端或非门结构应为:上部 3 个 P 管串联,下部 3 个 N 管并 联,结构如图所示。

3.15 画出 OR2 所对应的电路图。 解:在 NOR2 电路的输出端后面级联一个 INV。

3.59 解:

画出图 X3.59 逻辑图所对应的电路图。

3.21 若输出低电平阈值和高电平阈值分别设置为 1.5V 和 3.5V,对 图 X3.21 所示的反相器特性,确定高态与低态的 DC 噪声容限。 解:由图中可以看到,输出 3.5V 对应的输入为 2.4V,输出 1.5V 对应 的输入为 2.5V; 所以,高态噪声容限为:3.5-2.5=1 V ;低态噪声 容限为:2.4-1.5=0.9 V。

数字逻辑大作业

数字逻辑大作业报告设计题目:电子密码锁班级: 1203105组员:任课教师:张彦航计算机科学与技术学院目录1. 设计目的及要求2. 设计意义3. 工作原理框图4. 各模块的设计5. 调试过程6. 设计结论7. 设计心得与总结8. 参考文献9. 附录一:总体器件表及相关器件的功能表、管脚分布附录二:总体设计图附录三:仿真结果1.设计目的及要求(1)设计一个开锁密码至少为4位数字(或更多)的密码锁。

(2)当开锁按扭开关(可设置8位或更多,其中只有4位有效,其余位为虚设)的输入代码等于所设密码时启动开锁控制电路,并且用绿灯亮、红灯灭表示开锁状态。

(3)从第一个按扭触动后的5秒内若未能将锁打开,则电路自动复位并发出报警信号,同时用绿灯灭、红灯亮表示关锁状态。

(4)密码锁上带有数字时钟,当操作者开始按动按钮能进行倒计时显示。

2.设计意义随着社会的发展,人们对日常生活中的隐私保护越来越重视,传统的机械式钥匙开锁显然已经不能满足人们的要求,所以,为了满足人们的这一要求,增加安全性,用密码锁来代替钥匙的机械锁应运而生。

就密码锁而言,它具有更佳的安全性,保密性更好,同时密码也是可变的,使用起来更加的灵活,而且易于操作,在现实生活中得到了广泛的应用。

3.原理框图如上。

系统分为四个主要部分,其中键盘输入接受用户的输入S1---s9操作,移位寄存器记忆用户的输入状态,并给计数器一个输入开始信号,令其开始5cp时钟沿的计时。

如果用户输入正确,则计时器停止计数,结果显示执行输入正确的操作,如果5cp时钟沿内没有输入正确的密码,则电路复位。

输入s10,进行修改密码操作,并将密码保存在移位寄存器中。

4.各模块的设计编码器,将1---9转换为BCD码模块:输入由9个PB_DPST开关构成,用户按下开关时产生一个上升沿信号,通过自行设计的编码器将其转化为BCD码(输出在右上方)。

S1—s9作为密码输入按钮,s10作为密码修改的开关。

数字逻辑第3章答案

F, A B[(C D)E G]

5 (1) 如果已知 X + Y 和 X + Z 的逻辑值相同,那么 Y 和 Z 的逻

辑值一定相同。正确吗?为什么? (2) 如果已知 XY 和 XZ 的逻辑值相同,那么那么 Y 和 Z 的逻辑值

一定相同。正确吗?为什么? (3)如果已知 X + Y 和 X + Z 的逻辑值相同,且 XY 和 XZ 的逻辑

(1) F(A, B,C, D) BD AD CD CD ACD ABD

(2) F(A, B,C, D) (AB AB) C (AB AB) C

解答

G(A, B,C, D) AB BC AC (A B C) ABC

(1) 当 b a 时,令 a=1,b=0 能得到最简“与-或”表达式: F BC CD ACD (3 项)

(2) 当 a=1,b=1 时,能得到最简的“与-或”表达式:

F BC CD AC (3 项)

11 用列表法化简逻辑函数

F(A, B,C, D) m(0,2,3,5,7,8,10,11,13,15)

10

0

0

01 0 0 1 1

1

1

10 0 0 1 1

1

1

11 0 1 0 1

0

0

4 求下列函数的反函数和对偶函数: (1) F AB AB

(2) F A B A C C DE E

(3) F (A B)(C DAC)

(4) F A B CD E G

值相同,那么 Y = Z。正确吗?为什么? (4) 如果已知 X+Y 和 X·Y 的逻辑值相同,那么 X 和 Y 的逻辑值

数字逻辑课程三套作业及答案资料

数字逻辑课程作业A、单选题。

1.(4 分)如图xl-229某一译码器的输出端共有臼种不的组颌U其输入端備几个输入线? (A)3;(B J4;(0)5; 1D16A.(A)B.(B)C.(C)D.(D)知识点:第五章解析第五章译码器2.(4 分)如图xl-82F图所示河一逻辑电路,八"是输入端,F是输出端,则其输出与输入关系式是,{AiiA+B}iC+ DiE; .B^A+B+C+p-FE); iC) (A +云)QO+童);(D)AB[CD+Ei(C )A.(A)B.(B)C.(C)D.(D)知识点:第二章解析第二章其他复合逻辑运算及描述3.(4分)N个触发器可以构成最大计数长度(进制数)为(A.NB.2NC.N2次方D.2N次方知识点:第九章解析第九章计数器4.(4分)n个触发器构成的扭环型计数器中,无效状态有(B. B.2nC.C. 2n —1D. D . 2n-2n知识点:第九章解析第九章集成计数器5.(4 分)如图X1-293D )的计数器。

D )个。

在数字系统中其信号系仅貝E与即高电位与低电位两种: 迢】依电压犬小不等而定;依电流大小不等而定;①〕看需要而定A.(A)B.(B)C.(C)D.(D)知识点:第十一章解析第十一章数字系统概述6.(4 分)如图X1-317和项#只式的基本架构矢何?| A A'A ND—MAXD • IB i A XD—OR;(Q AND ―A.(A)B.(B)C.(C)D.(D)知识点:第二章解析第二章其他复合逻辑运算及描述7.(4 分)EPROM 是指( C )A.A、随机读写存储器B. B、只读存储器C.C、光可擦除电可编程只读存储器R? (DiO罠一AND(D )D.D、电可擦可编程只读存储器知识点:第十章解析第十章只读存储器8.(4 分)如图xl-407属于近似的不连续表示法丸?〔A]模拟表示法;|空数字表示法;1匚凰寸数表示法;|=>线性系统)°A.(A)B.(B)C.(C)D.(D)知识点:第十一章解析第十一章数字系统概述9.(4分)为实现将JK触发器转换为D触发器,应使( A )A.J=D,K=D 非B. B. K=D,J=D 非C. C.J=K=DD. D.J=K=D 非知识点:第六章解析第六章各种触发器的比较10.(4分)一位8421BCD码计数器至少需要(B )个触发器。

数字逻辑课程三套作业与答案

数字逻辑课程作业_A一、单选题。

1.(4分)如图x1-229(D)。

A. (A)B. (B)C. (C)D. (D)知识点:第五章解析第五章译码器2.(4分)如图x1-82(C)。

A. (A)B. (B)C. (C)D. (D)知识点:第二章解析第二章其他复合逻辑运算及描述3.(4分)N个触发器可以构成最大计数长度(进制数)为(D)的计数器。

A. NB. 2NC. N2次方D. 2N次方知识点:第九章解析第九章计数器4.(4分)n个触发器构成的扭环型计数器中,无效状态有(D)个。

A. A.nB. B.2nC. C.2n-1D. D.2n-2n知识点:第九章解析第九章集成计数器5.(4分)如图x1-293(A)。

A. (A)B. (B)C. (C)D. (D)知识点:第十一章解析第十一章数字系统概述6.(4分)如图x1-317(D)。

A. (A)B. (B)C. (C)D. (D)知识点:第二章解析第二章其他复合逻辑运算及描述7.(4分)EPROM是指(C)。

A. A、随机读写存储器B. B、只读存储器C. C、光可擦除电可编程只读存储器D. D、电可擦可编程只读存储器知识点:第十章解析第十章只读存储器8.(4分)如图x1-407(B)。

A. (A)B. (B)C. (C)D. (D)知识点:第十一章解析第十一章数字系统概述9.(4分)为实现将JK触发器转换为D触发器,应使(A)。

A. J=D,K=D非B. B. K=D,J=D非C. C.J=K=DD. D.J=K=D非知识点:第六章解析第六章各种触发器的比较10.(4分)一位8421BCD码计数器至少需要(B)个触发器。

A. 3B. B.4C. C.5D. D.10知识点:第九章解析第九章计数器11.(4分)为把50Hz的正弦波变成周期性矩形波,应当选用(A)。

A. A、施密特触发器B. B、单稳态电路C. C、多谐振荡器D. D、译码器知识点:第六章解析第六章集成触发器12.(4分)下列描述不正确的是(A)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Project3---- 带使能控制的4-16译码器设计许言

14051203

一.设计需求:

采用逻辑门和HDL,分别设计“仅有一个高有效使能端且高有效译码输出的4-16译码器”。

二.功能表与表达式:

(2)表达式:

三.在LogicSim中,采用原理图设计方法,画电路图,设定I/O,对所设计的电路进行模拟验证

首先根据表达式,在LogicSim中设计电路图。

电路图及模拟结果如下:

如上图,en=0,此时无论如何改变ABCD的输入,与门输出均为0,此时电路输

出0000000000000000,即译码器不工作。

改变en=1时,译码器开始工作。

调整DCBA由0000-1111。

当与门输入均为高有

效(浅绿色线)时,输出为1,否则输出为0。

经模拟验证无误。

DCBA=0000

输出Y0=1,

其余为0。

DCBA=0001

输出Y1=1,

其余为0。

……

(此处不一一举例)

DCBA=1111

输出Y15=1,

其余为0。

四.在Quartus中,建立工程,采用HDL设计方法,编写Verilog HDL 模块,编译纠错,并对所设计的电路进行功能仿真:

(1) HDL设计电路:

module decoder4_16(en,in,out);

input en;//en代表使能端输入EN

input [4:1]in;//定义4位宽in代替ABCD四个1位宽输入信号

output [16:1]out;//定义16位宽out位输出信号

reg [16:1]out; //out为reg型

always@(en or out)

if(en==1) //使能端高有效

case(in)

4'b0000:out=16'b0000000000000001;

4'b0001:out=16'b0000000000000010;

4'b0010:out=16'b0000000000000100;

4'b0011:out=16'b0000000000001000;

4'b0100:out=16'b0000000000010000;

4'b0101:out=16'b0000000000100000;

4'b0110:out=16'b0000000001000000;

4'b0111:out=16'b0000000010000000;

4'b1000:out=16'b0000000100000000;

4'b1001:out=16'b0000001000000000;

4'b1010:out=16'b0000010000000000;

4'b1011:out=16'b0000100000000000;

4'b1100:out=16'b0001000000000000;

4'b1101:out=16'b0010000000000000;

4'b1110:out=16'b0100000000000000;

4'b1111:out=16'b1000000000000000;

endcase

else out=16'b0000000000000000;

endmodule

第一次编译未通过(1 error,0 warning),显示

Top-level design entity 4_16is undefined

上网查阅相关资料,原因是在建立工程的时候,我所填写顶层设计实体名(工程名)和后续代码中的模块名必须一致。

可以在Assignments—setting中修改顶层设计实体名或者在代码中更改module后的模块名。

更改后第二次编译通过。

如图所示:

0-700ns内,使能端en输入为1,in从0递增,对应out输出信号符合要求。

700ns-900ns内,另是恩呢高端en输入为0,则译码器处于非工作状态,out输

出均为0。

900ns之后,en回到1,译码器又一次开始工作,in分别输入1110、1111,out

输出为对应信号。

即之前为输出过得两个信号。

五.若要求译码输出为低有效,解决方案:

(1)对于逻辑门设计:

在输出端前均添加非门(图为输入1111时状态图)

(2)对于HDL设计:

重新编写“case(in)”,将“out=16'b”后的码按位取反。

六.小结:

深入理解了译码器的工作原理。

首次在LogicSim中进行逻辑图设计,体会到了与Quartus的区别。

感觉前

者对于输入信号的改变很快捷,不需要一次次重新编译,查看不同输入的时候电

路工作情况很方便。

Quartus虽然仿真功能操作起来较为繁琐,不过波形图能一

次性更全面、直观的看出仿真结果。

各有利弊吧。

至于HDL设计,这次的编译错误还真是头一次见到,之前没注意过。

以后会

警醒些。

译码器不

工作时,输

出为0。