集成电路工艺和版图设计_供课下参考

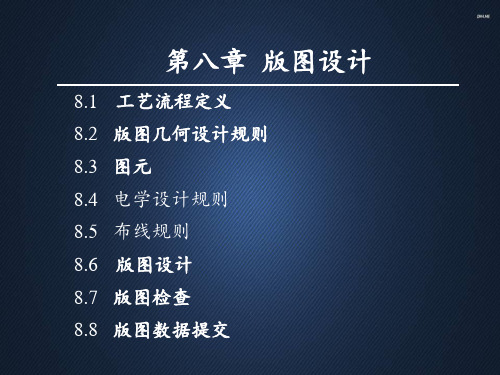

集成电路设计3-版图设计

版图设计的重要性

1

版图设计是集成电路制造过程中的关键环节,它 决定了集成电路的性能、功能和可靠性。

2

通过版图设计,可以将电路设计转化为实际制造 的物理结构,从而实现电路设计的目标。

3

版图设计的精度和质量直接影响到集成电路的性 能和制造良率,因此需要高度的专业知识和技能。

在芯片内部加入自测试模块,实现自动测试和 故障诊断。

可测性增强

通过增加测试访问端口和测试控制逻辑,提高芯片的可测性。

05

集成电路版图设计的挑 战与解决方案

设计复杂度挑战

总结词

随着集成电路规模不断增大,设计复杂 度呈指数级增长,对设计效率提出巨大 挑战。

VS

详细描述

随着半导体工艺的不断进步,集成电路设 计的规模越来越大,晶体管数量成倍增加 ,导致设计复杂度急剧上升。这不仅增加 了设计时间和成本,还对设计精度和可靠 性提出了更高的要求。

03

还需要考虑存储器的功耗和散热问题,以确保在各种应用场景下的稳 定运行。

04

高密度存储器版图设计需要具备高容量、高速、低功耗和高可靠性等 特点,以满足大数据、云计算等领域的需求。

THANKS FOR WATCHING

感谢您的观看

04

还需要考虑散热设计,以确保在高负载情况下CPU的 稳定运行。

案例二:低功耗MCU版图设计

低功耗MCU版图设计需要重点 关注功耗优化,采用低功耗工 艺和电路技术,如CMOS工艺

、低功耗逻辑门等。

还需要考虑低电压供电和电源 管理设计,以确保MCU在各种 应用场景下的稳定运行。

设计过程中需要优化芯片内部 结构和电路布局,降低芯片的

集成电路工艺基础及版图设计

氧化环境中使硅表面发生氧化, 生成SiO2 薄膜。

滤气 球 O2

流量 控制

二通

温度 控制

硅片 氧化 炉

石英 管 温度 控制

图2 - 1 热氧化示意图

❖

根据氧化环境的不同, 又可把热

氧化分为干氧法和湿氧法两种。 如果氧

化环境是纯氧气, 这种生成SiO2薄膜的 方法就称为干氧法。 干氧法生成SiO2薄 膜的机理是: 氧气与硅表面的硅原子在

(2 -4)

SiH4+2O2→SiO2↓+2H2O

❖ 2.2.2 掺杂工艺

❖

集成电路生产过程中要对半导体

基片的一定区域掺入一定浓度的杂质元

素, 形成不同类型的半导体层, 来制作

各种器件, 这就是掺杂工艺。 由此可见,

掺杂工艺也是一种非常重要的基础工艺。

掺杂工艺主要有两种: 扩散工艺和离子

注入工艺。

间测试之前的所有工序。 前工序结束时,

半导体器件的核心部分——管芯就形成了。

前工序中包括以下三类工艺:

❖

(1) 薄膜制备工艺: 包括氧化、工艺: 包括离子注入和

扩散。

❖

(3) 图形加工技术: 包括制版和

❖

2) 后工序

❖

后工序包括从中间测试开始到器

❖

1. 扩散工艺

❖

物质的微粒总是时刻不停地处于

❖

扩散的机理有两种: 替位扩散和

填隙扩散。 在高温的情况下, 单晶固体

中的晶格原子围绕其平衡位置振动, 偶

然也可能会获得足够的能量离开原来的

位置而形成填隙原子, 原来的位置就形

成空位, 而邻近的杂质原子向空位迁移,

这就是杂质的替位扩散方式。 杂质原子

集成电路版图设计 ppt课件

(b)

图8.3 交叠的定义

表8.5 TSMC_0.35μm CMOS工艺版图各层图形之间最小交叠

表 16.5 T SM C _0.35μ m C M O S 工 艺 版 图 各 层 图 形 之 间 最 小 交 迭

N _ w e ll A c tiv e P o ly P _ l\p lu s_ se le c t/N _ p lu s_ se l ect C o n ta c t M e ta l1 V ia 1 M e ta l2 E le c tro d e V ia 2 M e ta l3

MOS管的可变参数为:栅长(gate_length)、栅宽(gate_width) 和栅指数(gates)。

栅长(gate_length)指栅极下源区和漏区之间的沟道长度,最 小值为2lambda=0.4μm。

栅宽(gate_width)指栅极下有源区(沟道)的宽度,最小栅宽为 3 lambda=0.6μm。

201010233636cmos差动放大器单元电路设计版图的过程vinvinqr1r2vddmn1mn2mps2mcs2mgcsmcf1mcf2msf1msf2outout图716画l型金属线作地线图717画出两只mcs3并将它们的栅漏和源极互连201010233737vinvinqr1r2vddmn1mn2mps2mcs2mgcsmcf1mcf2msf1msf2outout图718画出两只mn1并将它们的栅漏和源极互连cmos差动放大器单元电路设计版图的过程201010233838图719依次画出r1并联的两只msf1和并联的两只mcf1以及偏压等半边电路版图vinvinqr1r2vddmn1mn2mps2mcs2mgcsmcf1mcf2msf1msf2outoutcmos差动放大器单元电路设计版图的过程201010233939cmos差动放大器单元电路设计版图的过程vinvinqr1r2vddmn1mn2mps2mcs2mgcsmcf1mcf2msf1msf2outout图720通过对图819中半边版图对x轴作镜像复制形成的完整版图201010234040在正式用cadence画版图之前一定要先构思也就是要仔细想一想每个管子打算怎样安排管子之间怎样连接最后的电源线地线怎样走

本科生课-集成电路版图设计-实验报告

西安邮电大学集成电路版图设计实验报告学号:XXX姓名:XX班级:微电子XX日期:20XX目录实验一、反相器电路的版图验证1)反相器电路2)反相器电路前仿真3)反相器电路版图说明4)反相器电路版图DRC验证5)反相器电路版图LVS验证6)反相器电路版图提取寄生参数7)反相器电路版图后仿真8)小结实验二、电阻负载共源放大器版图验证9)电阻负载共源放大器电路10)电阻负载共源放大器电路前仿真11)电阻负载共源放大器电路版图说明12)电阻负载共源放大器电路版图DRC验证13)电阻负载共源放大器电路版图LVS验证14)电阻负载共源放大器电路版图提取寄生参数15)电阻负载共源放大器电路版图后仿真16)小结实验一、反相器电路的版图验证1、反相器电路反相器电路由一个PMOS、NPOS管,输入输出端、地、电源端和SUB 端构成,其中VDD接PMOS管源端和衬底,地接NMOS管的漏端,输入端接两MOS管栅极,输出端接两MOS管漏端,SUB端单独引出,搭建好的反相器电路如图1所示。

图1 反相器原理图2、反相器电路前仿真通过工具栏的Design-Create Cellview-From Cellview将反相器电路转化为symbol,和schemetic保存在相同的cell中。

然后重新创建一个cell,插入之前创建好的反相器symbol,插入电感、电容、信号源、地等搭建一个前仿真电路,此处最好在输入输出网络上打上text,以便显示波形时方便观察,如图2所示。

图2 前仿真电路图反相器的输入端设置为方波信号,设置合适的高低电平、脉冲周期、上升时间、下降时间,将频率设置为参数变量F,选择瞬态分析,设置变量值为100KHZ,仿真时间为20u,然后进行仿真,如果仿真结果很密集而不清晰可以右键框选图形放大,如图3所示。

图3 前仿真结果3、反相器电路版图说明打开之前搭建好的反相器电路,通过Tools-Design Synthesis-Laout XL新建一个同cell目录下的Laout文件,在原理图上选中两个MOS管后在Laout中选择Create-Pick From Schematic从原理图中调入两个器件的版图模型。

集成电路版图设计(适合微电子专业)

①了解工艺现状,确定工艺路线

确定选用标准pn结隔离或对通隔离工艺或等平面 隔离工艺。由此确定工艺路线及光刻掩膜版的块数。 由制版和光刻工艺水平确定最小接触孔的尺寸和 光刻套刻精度。光刻工艺的分辨率,即能刻蚀图形的 最小宽度,受到掩膜分辨率、光刻胶分辨率、胶膜厚 度、横向腐蚀等多因素的限制。套刻精度与光刻机的 精度和操作人员的熟练程度关系密切。

功能设计 设 计 逻辑设计 电路设计 功能图 逻辑图 电路图 符号式版图 , 版图

图

版图设计

12

举例:

功能描述 x=a’b+ab’ 的逻辑图

13

CMOS与非门的电路图

14

场SiO2

栅SiO2 栅SiO2

CMOS反相器的掩膜版图

15

版图设计就是按照线路的要求和一定 的工艺参数,设计出元件的图形并进行排 列互连,以设计出一套供IC制造工艺中使 用的光刻掩膜版的图形,称为版图或工艺 复合图。 版图设计是制造IC的基本条件,版图 设计是否合理对成品率、电路性能、可靠 性影响很大,版图设计错了,就一个电路 也做不出来。若设计不合理,则电路性能 和成品率将受到很大影响。版图设计必须 与线路设计、工艺设计、工艺水平适应。 版图设计者必须熟悉工艺条件、器件物理、 电路原理以及测试方法。 16

23

要了解采用的管壳和压焊工艺。封 装形式可分为金属圆筒塑(TO-5型)、扁 平封装型和双列直插型(DIP)等多种,管 芯压点分布必须和管壳外引脚排列相吻 合。当采用热压焊时,压焊点的面积只 需70μm×70μm,超声压焊需 100μm×100μm ~125μm×25μm,金丝 球焊需125μm ×125μm,金丝球焊牢固 程度高,金丝在靠近硅片压点处是垂直 的,可压到芯片纵深处(但必须使用温度 SiO2纯化层),使用起来很灵活。

制造工艺-CMOS集成电路原理图及版图

硅芯片上的电子世界—晶体管

• 三级管:pnp,npn • 硅芯片上的三极管:

2012年春季

P+ …N…+. P+

N阱

P型衬底

28中北大学

三极管的设计

CMOS工艺下可以做双极晶体管。 以N阱工艺为例说明PNP, NPN如何形成。

PNP

注:

薄氧

由于P衬底接最低电位vss/gnd

因此,VPNP集电极也必须接

C

N+

N–-epi

钝化层

SiO2

P+

P-Sub

2012年春季

N+埋层

P P(G- ND)

N+

Sub

EB C

N+ P

N+

P+

N–-epi

60

60中北大学

版图设计

• 电子设计 + 绘图艺术 • 仔细设计,确保质量

2012年春季

61中北大学

MOS管的版图设计

沟道宽

沟道长

当多晶硅穿过有源区时,就形成了一个管子。在图中当 多晶硅穿过N型有源区时,形成NMOS,当多晶硅穿过P型有 源区时,形成PMOS。

MIM 上电级

第n-1层金属

电容区的下方不要走线;

2012年春季

20中北大学

多层金属制作的平板电容和侧壁电容

多层平板电容(MIM) •增加单位面积电容; •精度高,匹配性好;

2012年春季

侧壁电容: •单位面积电容值可比左边的大; •精度较高,匹配性较好;

21中北大学

MOS电容

CGS

累积区

强反型

vss/gnd 。

C

B

半导体集成电路第4章版图设计与举例课件

计线宽。 前者表示所能达到的工艺水平,后者表示保

证一定成品率前提下所能达到的工艺水平。 最小掩模线宽可根据实际的工艺确定。 对TTL一般4~10um

•半导体集成电路第4章版图设计与举例

•10

二、掩膜图形最小间距

版图设计时,版图上各相邻图形间的 最小间距。 显然,制作到Si平面时,图形的实际位置将与

•

设计中常用BC短•半接导体及集成单电路第独4章B版图C设计结与举两例 种结构。

•25

二、SBD

SBD在集成电路中可作为二极管独立使

用,也可以与晶体管组合构成抗饱和晶体管。

1、SBD版图设计考虑

要求:面积小 ,减小结电容;

串连电阻小,提高钳位效果;

反向击穿电压高。

在设计中,由于rSBD 与结电容的要求相

•

△WMAT-2-0.8xjc+Wdc-B+Gmin

7、DB-I 基区窗口到隔离窗口间距

•

△WMAT+0.8xjc-0.8xjI+Wdc-c+WdI-C+Gmin

•

XjI~125%Wepi-MAX

8、Dc-B n+集电极窗口到基区窗口间距

△WMAT+0.8xjc+0.8xje+Wdc-c+Gmin

9.Wc孔 集电极n+孔宽

目的:实现电路中各个元件的电隔离

规则:

1、集电极等电位的NPN管可共用一个隔离区(基极

等电位的PNP管可共用一个隔离区)

2、二极管按晶体管原则处理。

3、原则上,所有硼扩散电阻可共用同一隔离区。

4、当集电极电位高于硼扩散电阻的电位时,晶体管

集成电路版图设计

《集成电路版图设计》课内实验学院:信息学院专业班级:学号:学生姓名:指导教师:模拟集成电路版图设计集成电路版图是电路系统与集成电路工艺之间的中间环节,是一个不可少的重要环节。

通过集成电路的版图设计,可以将立体的电路系统变为一个二维的平面图形,再经过工艺加工还原于基于硅材料的立体结构。

因此,版图设计是一个上承的电路系统,下接集成电路芯片制造的中间桥梁,其重要性可见一斑。

但是,集成电路版图设计是一个令设计者感到困惑的一个环节,我们常常感到版图设计似乎没有什么规矩,设计的经验性往往掩盖了设计的科学性,即使是许多多年版设计经验的人有时候也说不清楚为何要这样或者那样设计。

在此,集成电路版图设计是一门技术,它需要设计者具有电路系统原理与工艺制造方面的基础知识。

但它更需要设计者的创造性,空间想象力和耐性,需要设计者长期工作的经验和知识的积累,需要设计者对日异月新的集成电路发展密切关注和探索。

一个优秀的版图设计者对于开发超性能的集成电路是极其关键的。

在版图的设计和学习中,我们一直会面临匹配技术降低寄生参数技术熟悉电路作用(功能,频率)电流密度的计算(大电流和小电流的电流路径以及电流流向)等这些基本,它们也是最重要的问题。

版图的设计,从半导体制造工艺,到最后的后模拟过程都是非常关键的,里面所涉及的规则有1500——2000条,一些基本问题的解决方法和设计的调理化都将在下面提及。

模拟集成电路版图设计流程:阅读研究报告理解电路原理图了解电路的作用熟悉电流路径晶大小知道匹配器件明白电路中寄生,匹配,噪声的产生及解决方案对版图模块进行平面布局对整个版图进行平面布局熟练运用cadence软件进行版图绘制Esd的保护设计进行drc与lvs检查整理整个过程中的信息时刻做记录注意在设计过程中的交流集成电路制造工艺双极工艺:Cmos(p阱)工艺:版图设计经验总结:1 查看捕捉点设置是否正确.08工艺为0.1,06工艺为0.05,05工艺为0.025.2 Cell名称不能以数字开头.否则无法做DRACULA检查.3 布局前考虑好出PIN的方向和位置4 布局前分析电路,完成同一功能的MOS管画在一起5 对两层金属走向预先订好。

集成电路与工艺版图设计

DC-DC 变换器中误差放大器AMP 模块版图设计1 DC —DC 变换器中误差放大器AMP 模块电路误差放大器是整个变换器电路的核心,从原理上说,误差放大电路内部实质上是一个具有高放大倍数的多级直接耦合放大电路。

误差放大器的电路结构如下:V I NR40V1DC = 3VR5误差放大器的原理图如下:L = 2u版图是集成电路从设计走向制造的桥梁,它包含了集成电路尺寸,电阻电容大小等器件相关的物理信息数据。

版图设计是创造工程制图(网表)的精确的物理描述过程,即定义各工艺层图形的形状,尺寸以及不同工艺层的相对位置的过程。

其设计目标有以下三方面:1. 满足电路功能,性能指标,质量要求;2. 尽可能节省面积,以提高集成度,降低成本;3. 尽可能缩短连线,以减少复杂度,缩短延时,改善可能性。

下面是我对误差放大器AMP模块版图设计及仿真的过程。

2DC—DC变换器中误差放大器AMP模块版图设计及仿真2.1版图设计的前仿真2.1.1替换及其他基本设置此次版图所用工艺为MOSIS/ORBIT 1.2u SCNA。

(设置替换路径为:C:\program files\Tanner EDA\Tanner Tools v13.1\L-Edit andLVS\Tech\Mosis\morbn12)替换设置后,将设置-设计-technology下的technology to micro map 改为:1 Lambda=microns。

2.1.2版图的基本绘制下面为常用的CMOS工艺版图与工艺的关系:(1)N阱:做N阱的封闭图形处,窗口注入形成P管的衬底(2).有源区:做晶体管的区域(G,D,S,B区),封闭图形处是氮化硅掩蔽层,该处不会长场氧化层(3).多晶硅:做硅栅和多晶硅连线。

封闭图形处,保留多晶硅。

(4).有源区注入:P+,N+区。

做源漏及阱或衬底连接区的注入(5).接触孔:多晶硅,扩散区和金属线1接触端子。

(6).金属线1:做金属连线,封闭图形处保留铝(7).通孔:两层金属连线之间连接的端子(8).金属线2:做金属连线,封闭图形处保留铝①NMOS与PMOS的绘制绘制NMOS要用到的图层有Active、N Select、Poly、Active Contact、Metal1,而PMOS管的版图绘制需要用到N Well、Active、P Select、Poly、Active Contact、Metal1,其中Poly的长度就是晶体管的L,Active的高度就是晶体管的W。

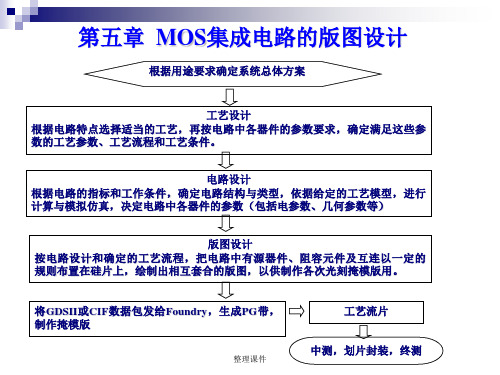

集成电路原理-MOS集成电路的版图设计

1.08(ns)

整理课件

0.0330.001

2、导电层的选择

(1)VDD、VSS尽可能选用金属导电层,并适当增加连线宽 度,只有在连线交叉“过桥”时,才考虑其他导电层。 (2)多晶硅不宜用作长连线,一般也不用于VDD、VSS电源 布线。 (3)通常应使晶体管等效电阻远大于连线电阻,以避免出 现电压的“分压”现象,影响电路正常工作。

若要形成耗尽型NMOS器件,只需在第(5)、(6)步之间加 一道掩模版,进行沟道区离子注入。

NMOS工艺流程的实质性概括: P型掺杂的单晶硅片上生长一层厚SiO2。 MK1—刻出有源区或其他扩散区(薄氧化版/扩散版)。 MK2—形成耗尽型器件时,刻出离子注入区。 MK3—刻多晶硅图形(栅、多晶硅连线)。

以多晶硅栅为掩模,进行D、S的自对准扩散。 MK4—刻接触孔。 MK5—反刻 Al。 MK6—刻钝化孔(压焊点窗口)

共用到6道掩模版 整理课件

3、硅栅CMOS工艺 (1)P阱CMOS工艺流程 • MK1—P阱版,确定P阱深扩散区域(阱注入剂量11013cm-2,

能量60KeV) • MK2—确定薄氧化区,即有源区。 • MK3—多晶硅版。 • MK4—P+版,和MK2一起确定所有的P+扩散区域 (一般为B注入,41014cm-221015cm-2,6080KeV)。 • MK5—N+版,确定所有的N+区域

(4)通过掩模版MASK对光刻胶曝光 正胶被 UV曝光的部分分解, 影被 掉显 。 负胶曝光部分聚合 ,硬 不化 被显影掉。

整理课件

(5)刻有源区。 掩模版掩蔽区域下未被曝光的光刻胶 被显影液洗掉;再将下面的SiO2用HF 刻蚀掉,露出硅片表面。

(6)淀积多晶硅 除净曝光区残留的光刻胶(丙酮), 在整个硅片上生长一层高质量的SiO2 (约1000Å),即栅氧,然后再淀积 多晶硅(12m)。

《集成电路版图设计》课件

了解各种元器件的工作原理是进行版图设计的基础,如晶 体管的工作原理涉及到载流子的运动和电荷的积累等。

元器件版图设计规则

在进行元器件版图设计时,需要遵循一定的设计规则,如 电阻的阻值计算、电容的容量计算等,以确保设计的准确 性和可靠性。

集成电路工艺

01 02

集成电路工艺流程

集成电路的制造需要经过多个工艺步骤,包括薄膜制备、光刻、刻蚀、 掺杂等,这些工艺步骤的参数和条件对集成电路的性能和可靠性有着重 要影响。

学生需要按照指导要求,完成集成电路版图设计实践任务,并

提交实践报告。

集成电路版图设计实践图设计

案例四

某混合信号集成电 路版图设计

案例一

某数字集成电路版 图设计

案例三

某射频集成电路版 图设计

案例五

某可编程逻辑集成 电路版图设计

集成电路版图设计实践经验总结

实践经验总结的重要性

特点

集成电路版图设计具有高精度、 高复杂度、高一致性的特点,需 要综合考虑电路功能、性能、可 靠性以及制造工艺等多个方面。

集成电路版图设计的重要性

01

02

03

实现电路功能

集成电路版图设计是将电 路设计转化为实际产品的 关键环节,是实现电路功 能的重要保障。

提高性能和可靠性

合理的版图设计可以提高 集成电路的性能和可靠性 ,确保产品在长期使用中 保持稳定。

DRC/LVS检查

进行设计规则检查和版图验证 ,确保版图设计的正确性和可 制造性。

布图输出

将版图数据输出到制造环节, 进行硅片的制作。

02

集成电路版图设计基础知识

半导体材料

半导体材料分类

半导体材料分为元素半导体和化合物半导体两大类,元素半导体包括硅和锗,化合物半导 体包括三五族化合物(如砷化镓、磷化镓等)和二六族化合物(如硫化镉、硒化镉等)。

第3章CMOS集成电路工艺与版图

英特尔65纳米双核处理器的扫描电镜(SEM)截面图

常用图层 版图图层名称 Nwell Active Pselect Nselect Poly cc Metal1 Metal2 Via 含义 N阱 有源扩散区 P型注入掩膜 N型注入掩膜 多晶硅 引线孔 第一层金属 第二层金属 通孔

注意:

不同软件对图层名称定义不同; 严格区分图层作用。

“混合棒状图”法:

矩形代表有源区(宽度不限); 实线代表金属; 虚线代表多晶硅;

“×”代表引线孔。其它层次不画,

通常靠近电源vdd的是P管,靠近地线gnd 的是N管。

反相器棒状图

电路图-棒状图-版图

a

b

练习

三输入与非门、或非门棒状图

8、MOS管阵列的版图实现

(1) MOS管的串联。 N1的源、漏区为X和Y,N0的源、漏区为Y和Z。 利用源漏共用,得到两个MOS管串联连接的版图。 电路图

N1和N0串联版图

N1、 N0版图

任意个MOS管串联。 例如3个MOS管串联的版图。

电路图

版图

(2)MOS管并联(并联是指它们的源和源连 接,漏和漏连接,各自的栅还是独立的。) 栅极水平放置

对管

缓冲器中的一级反相器

运放对管

大尺寸器件存在的问题: 寄生电容; 栅极串联电阻

大面积的栅极与衬底之间有氧化 层隔绝,形成平板电容

栅电压降低

细长的栅极存在串联电阻,导 致栅极两端电压不同

MOS管寄生电容值

C W L C0

MOS管栅极串联电阻值

R W / L R

S G

衬底材料导电性较差,为了保证接触的效 果,需要在接触区域制作一个同有源区类 似的掺杂区域降低接触电阻,形成接触区。 衬底半导体材料要与电极接触,同样需要 引线孔(CC);

集成电路版图与工艺课程设计之用CMOS实现Y=AB+C电路与版图

集成电路版图与⼯艺课程设计之⽤CMOS实现Y=AB+C电路与版图1 绪论1.1 设计背景集成电路设计(Integrated circuit design, IC design),亦可称之为超⼤规模集成电路设计(VLSI design),是指以集成电路、超⼤规模集成电路为⽬标的设计流程。

集成电路设计涉及对电⼦器件(例如晶体管、电阻器、电容器等)、器件间互连线模型的建⽴。

所有的器件和互连线都需安置在⼀块半导体衬底材料之上,这些组件通过半导体器件制造⼯艺(例如光刻等)安置在单⼀的硅衬底上,从⽽形成电路。

近些年来,集成电路技术发展迅猛,促使半导体技术不断地发展,半导体技术正在进⼊将整个系统整合在单⼀晶⽚上的时代。

故对VLSI的版图设计的要求也越来越⾼。

Tanner软件可提供完整的集成电路设计环境,帮助初学者进⼊VLSI设计领域。

本设计采⽤Tanner Tools Pro ⼯具,对逻辑为Y=AB+C进⾏电路设计与仿真、版图设计与仿真,在报告中给出电路图、版图与仿真结果。

1.2 设计⽬标设计⽬标逻辑:Y=AB+C⽤CMOS⼯艺设计逻辑为Y=AB+C的电路和版图。

因为CMOS是天然的反逻辑输出,所以需要先设计出逻辑为/Y=/(AB+C)的电路,再将输出接⼊⼀个CMOS反相器实现逻辑功能。

设计电路图(Schematic)时,N⽹络A与B串联且与C并联,P⽹络A与B并联且与C串联,在N和P⽹络的交界节点接⼊反相器后引出输出Y。

设计版图(Layout)时,在P型衬底(P-Sub)上进⾏制作,所以N-MOS管可以直接掺杂制作,⽽P-MOS管需要先制作⼀个N阱(N-Well),并在N阱⾥制作P-MOS管。

整个设计⽐较简单,仅仅使⽤单层⾦属布线(Meteal)。

导出电路和版图⽹表(spice)⽂件,⽤Tspice软件进⾏仿真波形,分析电路和版图是否设计正确性以及其性能如何。

在LVS验证中匹配电路原理图和版图逻辑和尺⼨匹配性,完成整个设计过程。

《集成电路版图设计》课件

布局原则

在布局时,应遵循一些基本原则,如模块化、层次化、信号流向清晰等,以提高 布局的可读性和可维护性。

优化方法

可以采用一些优化方法来提高布局的效率和可读性,如使用自动布局算法、手动 调整布局、考虑布线约束等。

布线优化

布线原则

在布线时,应遵循一些基本原则,如 避免交叉、减少绕线、保持线宽一致 等,以提高布线的可靠性和效率。

04

集成电路版图设计技巧与优化

布图策略与技巧

布图策略

根据电路功能和性能要求,选择合适的布图策略,如层次化、模块化、对称性 等,以提高布图的效率和可维护性。

技巧

在布图过程中,可以采用一些技巧来提高布图的效率和可读性,如使用标准单 元、宏单元等模块化设计,以及合理利用布局空间、避免布线拥堵等。

布局优化

用于实现电路中的电阻功能,调节电流和电 压。

电感器

用于实现电路中的电感功能,用于产生磁场 和感应电流。

版图设计规则

几何规则

规定了各种几何元素的使用方法和尺寸 ,以确保版图的准确性和一致性。

器件规则

规定了各种器件的尺寸、形状和排列 方式,以确保器件的性能和可靠性。

连线规则

规定了各种连线元素的宽度、间距和 连接方式,以确保电路的可靠性和稳 定性。

直线

用于连接集成电路中的不同部 分,实现电路的导通。

弧线

用于表示不同层之间的过渡, 以平滑电路。

折线

用于表示复杂电路中的分支或 连接点。

点

用于表示电路中的节点或连接 点。

ቤተ መጻሕፍቲ ባይዱ 器件元素

晶体管

用于实现电路中的逻辑功能,是集成电路中 的基本元件。

电容器

用于实现电路中的电容功能,用于存储电荷 和过滤信号。

《集成电路设计》课件

掺杂与刻蚀

在晶圆表面进行掺杂和刻蚀, 形成电路元件和互连结构。

晶圆制备

将高纯度硅晶棒进行切片,得 到晶圆片,作为集成电路制造 的基础材料。

图案转移

将设计好的电路图案通过光刻 技术转移到晶圆表面,形成电 路图形。

金属化与封装

在晶圆表面沉积金属,形成电 路的互连线路,并将单个芯片 封装成最终的产品。

集成电路工艺材料

详细描述

数字集成电路设计案例通常包括门电路设计、触发器设计、寄存器设计等,这些基本单元是构成复杂数字系统的 基石。此外,数字系统级的设计案例包括微处理器、微控制器、数字信号处理器等,这些系统级芯片广泛应用于 计算机、通信、控制等领域。

模拟集成电路设计案例

总结词

模拟集成电路设计案例主要涉及放大器、滤波器、比较器等模拟电路单元的设计,以及模拟系统级的 设计。

电视、音响、游戏机 等。

工业控制

PLC、DCS、机器人 等。

汽车电子

发动机控制、ABS、 ESP等。

02

集成电路设计基础

集成电路设计流程

需求分析

对产品需求进行调研,明确设计目标、性能 指标和限制条件。

规格制定

根据需求分析结果,制定出具体的规格说明书 ,包括芯片功能、性能参数等。

架构设计

根据规格说明书,设计出芯片的总体结构,包括 各个模块的组成和相互关系。

电路仿真工具

用于模拟电路的行为和性能, 常用的有ModelSim和 Matlab Simulink。

物理设计工具

用于将电路设计转换为版图, 常用的有Cadence和 Synopsys。

测试工具

用于测试芯片的性能和功能, 常用的有JTAG和Boundary Scan。

集成电路版图设计习题答案第二章集成电路制造工艺

集成电路版图设计习题答案第2章 集成电路制造工艺【习题答案】1.硅片制备主要包括(直拉法)、(磁控直拉法)和(悬浮区熔法)等三种方法。

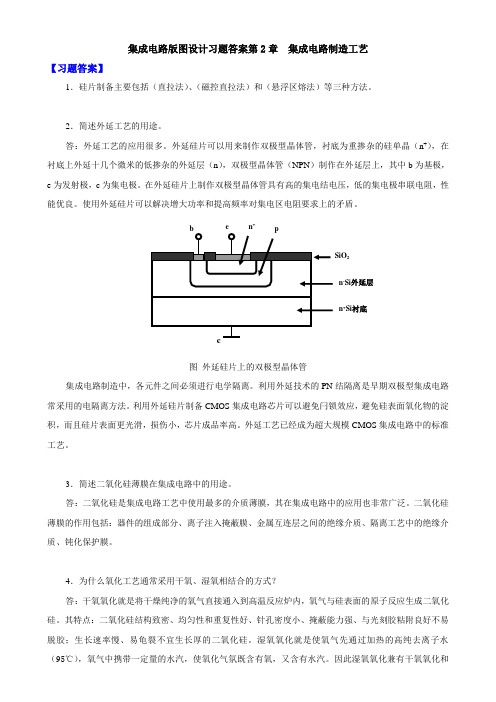

2.简述外延工艺的用途。

答:外延工艺的应用很多。

外延硅片可以用来制作双极型晶体管,衬底为重掺杂的硅单晶(n +),在衬底上外延十几个微米的低掺杂的外延层(n ),双极型晶体管(NPN )制作在外延层上,其中b 为基极,e 为发射极,c 为集电极。

在外延硅片上制作双极型晶体管具有高的集电结电压,低的集电极串联电阻,性能优良。

使用外延硅片可以解决增大功率和提高频率对集电区电阻要求上的矛盾。

图 外延硅片上的双极型晶体管集成电路制造中,各元件之间必须进行电学隔离。

利用外延技术的PN 结隔离是早期双极型集成电路常采用的电隔离方法。

利用外延硅片制备CMOS 集成电路芯片可以避免闩锁效应,避免硅表面氧化物的淀积,而且硅片表面更光滑,损伤小,芯片成品率高。

外延工艺已经成为超大规模CMOS 集成电路中的标准工艺。

3.简述二氧化硅薄膜在集成电路中的用途。

答:二氧化硅是集成电路工艺中使用最多的介质薄膜,其在集成电路中的应用也非常广泛。

二氧化硅薄膜的作用包括:器件的组成部分、离子注入掩蔽膜、金属互连层之间的绝缘介质、隔离工艺中的绝缘介质、钝化保护膜。

4.为什么氧化工艺通常采用干氧、湿氧相结合的方式?答:干氧氧化就是将干燥纯净的氧气直接通入到高温反应炉内,氧气与硅表面的原子反应生成二氧化硅。

其特点:二氧化硅结构致密、均匀性和重复性好、针孔密度小、掩蔽能力强、与光刻胶粘附良好不易脱胶;生长速率慢、易龟裂不宜生长厚的二氧化硅。

湿氧氧化就是使氧气先通过加热的高纯去离子水(95℃),氧气中携带一定量的水汽,使氧化气氛既含有氧,又含有水汽。

因此湿氧氧化兼有干氧氧化和en +SiO 2n -Si 外延层 n +Si 衬底水汽氧化的作用,氧化速率和二氧化硅质量介于二者之间。

实际热氧化工艺通常采用干、湿氧交替的方式进行。

集成电路工艺和版图设计参考

06.10.2023

Jian Fang

7

Another view of one of the Fab Two Photolithography areas.

06.10.2023

Jian Fang

8

Here we see a technician loading 300mm wafers into the SemiTool. The wafers are in a 13 wafer Teflon cassette codesigned by Process Specialties and SemiTool in 1995. Again these are the world's first 300mm wet process cassettes (that can be spin rinse dried).

Jian Fang

23

VDD

S

D

P+

P+

N-Si

VG

Vo

D n+

S

VSS

n+

P-阱

CMOS倒相器截面图

06.10.2023

Jian Fang

CMOS倒相器版图

24

omicontact

A NMOS Example

metal

pwell

P+

implant

06.10.2023

active

Jian Fang

06.10.2023

Jian Fang

4

பைடு நூலகம்

生产工厂简介

PSI

06.10.2023

Jian Fang

5

06.10.2023

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Accuracy in metrology is never an issue at Process Specialties. We use the most advanced robotic laser ellipsometers and other calibrated tools for precision thin film, resistivity, CD and step height measurement. Including our new Nanometrics 8300 full wafer 300mm thin film measurement and mapping tool. We also use outside laboratories and our excellent working relationships with our Metrology tool customers, for additional correlation and calibration.

Fab Two was completed January 2, 1996 and is a "State of the Art" facility. This 2,200 square foot facility was constructed using all the latest materials and technologies. In this set of cleanrooms we change the air 390 times per hour, if you do the math with ULPA filtration this is a Class One facility. We have had it tested and it does meet Class One parameters (without any people working in it). Since we are not making microprocessors here and we don't want to wear "space suits", we run it as a class 10 fab. Even though it consistently runs well below Class Ten.

集成电路工艺和版图设计

概述

Jian Fang IC Design Center, UESTC

2011-11-24

Jian Fang

1

微电子制造工艺

2011-11-24

Jian Fang

2

IC常用术语

园片:硅片 芯片(Chip, Die): 6″、8 ″:硅(园)片直径:1 ″=25.4mm 6″≅150mm; 8″≅200mm; 12″≅300mm; 亚微米<1µm的设计规范 深亚微米<=0.5 µm的设计规范 0.5 µm 、 0.35 µm -设计规范(最小特征尺寸) 布线层数:金属(掺杂多晶硅)连线的层数。 集成度:每个芯片上集成的晶体管数

2011-11-24

Jian Fang

7

Another view of one of the Fab Two Photolithography areas.

2011-11-24

Jian Fang

8

Here we see a technician loading 300mm wafers into the SemiTool. The wafers are in a 13 wafer Teflon cassette codesigned by Process Specialties and SemiTool in 1995. Again these are the world's first 300mm wet process cassettes (that can be spin rinse dried).

2011-11-24 Jian Fang 18

集成电路( 集成电路(Integrated Circuit, IC):半导体 ,膜IC,混合 ) 半导体IC, ,混合IC 半导体IC:指用半导体工艺把电路中的有源器件、 半导体 :指用半导体工艺把电路中的有源器件、无源元件及 互联布线等以相互不可分离的状态制作在半导体上, 互联布线等以相互不可分离的状态制作在半导体上,最后封装在 一个管壳内,构成一个完整的、具有特定功能的电路。 一个管壳内,构成一个完整的、具有特定功能的电路。 双极IC 双极 NMOS IC 半导体IC 半导体 MOSIC PMOS IC CMOS IC BiCMOS

2011-11-24 Jian Fang 9

As we look in this window we see the World's First true 300mm production furnace. Our development and design of this tool began in 1992, it was installed in December of 1995 and became fully operational in January of 1996.

2011-11-24 Jian Fang 6

Here in the Fab Two Photolithography area we see one of our 200mm .35 micron I-Line Steppers. this stepper can image and align both 6 & 8 inch wafers.

2011-11-24 Jian Fang

反型层 源(Source)S 漏(Drai) MOS(PMOS)

场氧化层 栅氧化层

源

p+

栅

p+ 沟道 N-衬底

漏

D G S

-

VT

+VGS

VDS < 0

ID

• N型衬底,施主杂质,电子导电; • 栅上加负电压,表面吸引空穴,反型,空穴通道; • 漏加负电压,空穴从源区经P沟道到达漏区,器件开通。

C

CMOS传输门

23

VG VDD S P+ D P+ Vo D n+ n+ S VSS

P-阱 N-Si

CMOS倒相器截面图

CMOS倒相器版图

2011-11-24 Jian Fang 24

A NMOS Example

omicontact metal

2011-11-24 Jian Fang 3

IC工艺常用术语

净化级别:Class 1, Class 10, Class 10,000 每立方米空气中含灰尘的个数 去离子水 氧化 扩散 注入 光刻 …………….

2011-11-24 Jian Fang 4

生产工厂简介

PSI

2011-11-24 Jian Fang 5

2011-11-24 Jian Fang 15

One of two SEM Labs located in our facility. In this one we are using a field emission tool for everything from looking at photoresist profiles and measuring CD's to double checking metal deposition thicknesses. At the helm, another one of our process engineers you may have spoken with Mark Hinkle.

2011-11-24 Jian Fang 19

MOS IC及工艺

MOSFET — Metal Oxide Semiconductor Field Effect Transistor . — 金属氧化物半导体场效应晶体管

MOS(MIS)结构

金属 氧化物(绝缘层、SiO2) Si

半导体

2011-11-24

2011-11-24 Jian Fang 10

Here we can see the loading of 300mm wafers onto the Paddle.

2011-11-24

Jian Fang

11

Process Specialties has developed the world's first production 300mm Nitride system! We began processing 300mm LPCVD Silicon Nitride in May of 1997.

2011-11-24 Jian Fang 16

Here we are looking at the Incoming material disposition racks

2011-11-24 Jian Fang 17

Above you are looking at a couple of views of the facilities on the west side of Fab One. Here you can see one of our 18.5 Meg/Ohm DI water systems and one of four 10,000 CFM air systems feeding this fab (left picture), as well as one of our waste air scrubber units (right picture). Both are inside the building for easier maintenance, longer life and better control.