Lm3s6432&8962网络开发笔记8_数据采集

【1】EDC的M3资源介绍_讲稿

项目型号

产品名称

产品型号

LSD-S2E21-01 串口转以太网转换板(独立模块) LSD-S2E21-01

嵌入式GPRS数据传输模块

简介:

嵌入式GPRS数据传输模块是利尔达公司自行设计研发的基于 Cortex M3内核的远程数据传输模块,具有使用方便,配置简单 ,传输高效,性能稳定等优点。该模块提供RS232和RS485两路串 口进行数据传输和配置接口,模块接到数据后通过GPRS网络将数 据传输到远程服务器上,在电力系统,工业自动化、设备监控、 金融、交通管理、环保监测、气象、煤矿等行业广泛应用。

项目型号

LSD-TEST3S3748

产品名称

产品型号

嵌入式LM3S3748学习板 LSD-TEST3S3748

嵌入式LM3S8962学习板

简介: 该学习板支持Ethernet+CAN LM3S8962和CANLM3S2110,可实现 完整CAN网络。包含开源FreeRTOS操作系统以及LwIP和uIP以太 网协议栈的嵌入式Web服务器。板载FTDI仿真器,提供对外仿 真的功能。 特点: 一体化全功能Ethernet+CAN,包含完整实例程序 LM3S8962 Ethernet主板和LM3S2110 CAN设备板 集成10/100(MAC+PHY)以太网控制器 两块Stellaris器件都全面集成了CAN的MAC层 USB线缆提供串行通信、调试功能和电源 128X64像素分辨率和16级灰度的OLED图形显示屏 用户LED、导航开关、选择按钮和电磁扬声器 所有LM3S8962的I/O段口外扩 输入和输出的标准ARM20引脚JTAG/SWD调试连接器 MicroSD卡插槽支持FAT32文件系统

特点:

基于LM3S6432的串口以太网转换器的设计与实现

基于LM3S6432的串口以太网转换器的设计与实现

罗彩洪;陈晓敦

【期刊名称】《电脑知识与技术》

【年(卷),期】2013(000)002

【摘要】对于当前物联网的应用及需求,以Cortex-M3芯片为模版,实现串口与以太网之间的数据转换与传送,该文简要介绍了转换设备的硬件与软件设计,通过实际应用验证其的可行性.

【总页数】5页(P252-256)

【作者】罗彩洪;陈晓敦

【作者单位】福州大学,福建福州350100;福州大学,福建福州350100

【正文语种】中文

【中图分类】TP393

【相关文献】

1.基于LWIP的串口/以太网协议转换器的设计与实现 [J], 杨玉佳;李广军;郭志勇

2.串口到以太网的协议转换器的设计与实现 [J], 唐琳;廖先莉;程皓

3.基于LM3S6432的嵌入式以太网转串口模块设计 [J], 吴春锐;张志凯

4.串口-以太网转换器的设计与实现 [J], 苑玮琦;莫云鹏

5.一种RS232串口与RJ45以太网接口转换器的设计与实现 [J], 陈传虎

因版权原因,仅展示原文概要,查看原文内容请购买。

LM3S8962产品说明

■ 带有SPI、MICROWIRE或是 TI 同步串行主从 模式的同步串行接口(SSI) ■ I2C 接口(主从) ■ 两个完全可编程的带IrDA 支持的16C550型 UARTs

模数转换器 (ADC)

■ 单分和差分输入配置 ■ 用作单端输入时,有4个10位通道(输入) ■ 每秒500000样本的采样率

GPIOs

■ 5-42 GPIOs,根据配置而定 ■ 输入/输出端口可承受5V电压 ■ 可编程的中断产生 ■ 每两个时钟周期改变一次的快速触发能力 ■ 可启动一个ADC采样序列 ■ 可编程驱动能力和转换速率控制

电源

■ 片上的低压差稳压器(LDO) ■ 带RTC和256字节的非易失性存储器的备用电 池睡眠模块 ■ 提供3.3V电源掉电检测

模拟比较器

■ 一个独立集成的模拟比较器 ■ 输出配置目的: 驱动输出引脚,产生中断或启动 一个ADC采样序列 ■ 外部引脚输入与外部引脚输入相比较或外部引 脚输入与内部可编程基准电压相比较

I2C 接口

■ 主从收发操作,标准模式下传输速率达100Kbps, 快速模式下传输速率达400 Kbps ■ 产生中断 ■ 带仲裁和时钟同步的主设备,支持多主和7位寻 址模式

订购须知

可订购的部件号

描述

LM3S8962-IQC50 LM3S8962-IQC50(T)a

Stellaris LM3S8962 微控制器 Stellarisٛ LM3S8962 微控制器

Luminary Micro 公司的 Stellaris® LM3S8962 以太 网和 CAN 评估套件提供了硬件和软件工具来提高 开发速度,这些开发使用 LM3S8962 微控制器的完 整的 CAN 和 10/100 以太网控制器。咨询 Luminary Micro 公司发行人获取部件号 EKK-LM3S8962 (ARM RealView®MDK 开发工具),

基于TMS320C642电子稳像的实现

基于TMS320C642电子稳像的实现 电子稳像集合了计算机、数字图像处理和数字信号处理等技术为一体的新一代实现图像序列稳定的综合性技术。

实时性和准确性是衡量电子稳像系统的两个重要指标。

因此,电子稳像算法要体现其优越性,就要满足实时性和准确性。

1 基于灰度投影的电子稳像算法 1.1 电子稳像基本原理 电子稳像(Electronic Image StabilizaTIon,EIS)是集电子技术、计算机、数字信号处理、视频图像处理等为一体的实现数字图像序列稳定的技术。

电子稳像技术中最基本的是像移补偿技术是直接从像面上通过检测参考图像和被比较图像的运动矢量,然后利用算法进行补偿的技术。

稳像的基本原理:(1)根据图像序列或视频的各种信息进行局部运动估计。

(2)进行全局运动估计。

(3)经过运动估计后取得运动参数,然后进行综合评价。

(4)根据综合评价的结果进行运动补偿,并最终取得稳定的输出序列。

由此可知,获得图像的全局运动矢量是电子稳像的前提条件。

基本流程如图1所示。

对于全局运动矢量可以通过灰度投影算法获得。

1.2 灰度投影算法 灰度投影算法(ProjecTIon Algorithm,PA)是利用图像灰度分布变化的特点得到图像帧间运动矢量。

对于灰度细节丰富、直方图无明显特征、对比度差的图像难以识别特征量,寻找特征量不仅无法保证所需的稳像精度,更难以满足稳像的实时性要求。

针对此种图像序列,用灰度投影法来实现图像运动矢量的准确获取,从而达到稳定图像序列的目的。

视频图像序列是图像的灰度发生变化的图像序列,各种运动矢量估计算法均是以灰度变化为依据。

投影算法能充分利用图像的灰度变化这一特点,较准确地估计出图像的运动矢量。

此算法的优点是:灰度曲线匹配速度快,从而提高了稳像速度,适用于图像照度变化导致的灰度变化的情况。

灰度投影算法是实现只含平移运动或旋转运动较小的图像序列电子稳像的较理想算法。

(1)灰度映射。

灰度映射就是把每一帧输入的初始的二维图像信息映射成为两个独立的一维波形,如下为列投影的映射方法 式(1)~式(3)中,Colk(j)为第k帧图像第j列的灰度值;Curk(i,j)是第k帧图像上(i,j)位置上的像素值;NC是列数,ColProjk(j)是第k帧图像第j列修正后的投影值。

国半推出全新高亮度发光二极管驱动器(精)

国半推出全新高亮度发光二极管驱动器

美国国家美国国家半导体新推出的 LM3402 发光二极管驱动器有两个不同的版本,两者的输入电压都极为广阔 (6V 至 42V 或 6V 至

75V),而且两个版本都可驱动 1W 的发光二极管。

LM3404 及 LM3405 两款芯片则可输出更强大的驱动电流,因此最适宜用来驱动 3W 及 5W 的发光二极管。

发光二极管驱动器的技术规格

LM3402 芯片是一款体积小巧的恒流降压稳压器,效率高达 95%,可以输出高达 525mA 的驱动电流。

采用迷你型的 8 引脚 SOIC 封装,其中的一条允许引脚可以利用脉冲宽度调制 (PWM) 输入信号LM3404 与 LM3404HV 芯片均采用 8 引脚的窄型 SOIC 封装,其功能与 LM3402 及 LM3402HV 芯片无异,但LM3404 及 LM3404HV 芯片则可输出高达 1.2A 的驱动电流。

这两款产品可为

3W 及 5W 发光二极管提供 700mA 或 1A 的驱动电流。

LM3405 恒流降压稳压器有 8 引脚的迷你型 SOIC 封装及小型的 6 引脚SOT-23 封装可供选择,特色是可以输出高达 1A 的电流,以驱动 3W 或 5W 的发光二极管。

不但可以利用 0.2V 的参考电压提供恒流反馈控制功能,而且

价格及供货情况

LM3402 及 LM3402HV 芯片已开始有大量现货供应。

上述几款发光二极管驱动器全部以 1,000 颗为采购单位,LM3402 芯片的单颗价为 1.35 美元,

LM3402HV 芯片的单颗价则为 1.65 美元。

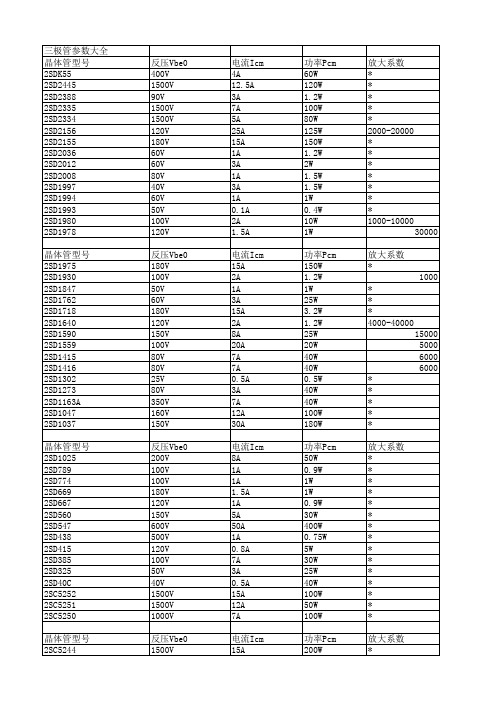

三极管参数大全

15A 10A 15A 16A 10A 10A 10A 7A 2A 6A 8A 10A 0.2A 7A 电流Icm 10A 6A 6A 14A 10A 8A 6A 5A 4A 3A 10A 8A 6A 5A 3A 电流Icm 6A 5A 3.5A 7A 6A 5A 3.5A 7A 6A 6A 5A 3.5A 2.5A 6A 5A 电流Icm 3.5A 5A 4A 5A

反压Vbe0 400V 1500V 90V 1500V 1500V 120V 180V 60V 60V 80V 40V 60V 50V 100V 120V 反压Vbe0 180V 100V 50V 60V 180V 120V 150V 100V 80V 80V 25V 80V 350V 160V 150V 反压Vbe0 200V 100V 100V 180V 120V 150V 600V 500V 120V 100V 50V 40V 1500V 1500V 1000V 反压Vbe0 1500V

10A 8A 7A 6A 6A 5A 3.5A 6A 电流Icm 5A 3.5A 5A 5A 2A 7.5A 6A 5A 5A 5A 5A 5A 3A 2A 0.1A 电流Icm 0.1A 2A 0.07A 0.015A 0.15A 1A 0.02A 0.2A 0.2A 0.05A 0.02A 0.1A 0.1A 7A 4A 电流Icm 0.05A 0.05A 1.5A 5A 0.1A 1.5A 0.7A 7A 0.1A 3A

2SC5243 2SC5207 2sc5200 2sc5132 2sc5088 2sc5086 2sc5068 2sc5020 2sc4953 2sc4941 2sc4927 2sc4924 2sc4913 2sc4769 晶体管型号 2sc4747 2sc4745 2sc4742 2sc4706 2SD1887 2SD1886 2SD1885 2SD1884 2SD1883 2SD1882 2SD1881 2SD1880 2SD1879 2SD1878 2SD1876 晶体管型号 2SD1739 2SD1738 2SD1737 2SD1732 2SD1731 2SD1730 2SD1729 2SD1711 2SD1710 2SD1656 2SD1655 2SD1654 2SD1653 2SD1652 2SD1651 晶体管型号 2SD1650 2SD1635 2SD1632 2SD1577

LED恒流IC芯片大盘点模板

LED恒流IC芯片大盘点模板在现代电子产品中,LED光源被广泛应用于照明、显示、通信和传感等领域。

为了保证LED光源的稳定工作和延长寿命,需要使用LED恒流IC芯片控制LED电流的大小。

本文将对LED恒流IC芯片进行大盘点,介绍常用的IC芯片以及其特点和应用领域。

一、LM3414是一款高效率、非同步降压转换器,主要用于LED驱动器。

其具有输入电压范围广泛、恒定电流输出、频率可调等特点,适用于照明和背光系统等领域。

二、LT3762是一款高效的双级LED恒流驱动器,适用于大功率LED照明应用。

它具有宽输入电压范围、高电流精度、PWM和直流调光功能等特点,适用于室内和室外照明系统。

五、AL8810是一款高效的LED恒流驱动器,可用于大功率LED照明应用。

它具有高精确度、宽输入电压范围、过热保护和短路保护等特点,适用于室内照明和汽车照明等领域。

六、BD1835是一款高效的恒流LED驱动器,适用于背光和照明系统。

它具有高效率、电流精确度、PWM和直流调光功能等特点,适用于电视、显示屏和照明灯具等应用。

以上仅是LED恒流IC芯片中的一部分,还有许多其他品牌和型号可供选择。

在选择LED恒流IC芯片时,需要根据具体应用需求来确定合适的芯片型号,包括输入电压范围、输出电流范围、调光功能以及保护功能等。

此外,还需要考虑芯片的可靠性、稳定性和供应商的售后服务等因素。

总结起来,LED恒流IC芯片在LED照明应用中起到了至关重要的作用。

选择合适的芯片可以提高LED光源的效率和稳定性,延长LED的使用寿命。

随着LED照明技术的不断发展,LED恒流IC芯片也将变得更加智能化和高效化,为LED照明行业的发展提供更多可能性。

基于以太网通讯的BC—NET模块简介

基于以太网通讯的BC—NET模块简介作者:李幸生来源:《科技视界》2017年第18期【摘要】随着科技进步,plc已经成为国内自动化行业的主角,大大小小的工厂都遍布着不同品牌的plc站点,诸如西门子,欧姆龙,施耐德等等,目前使用最广泛的还是德国西门子系列plc,包括200,300,400,1500等,其中西门子是最基础的plc,也是初学者最先开始接触的plc。

实际生产生活中,重中之重还是plc与上位机通讯的问题。

本文在讨论传统通讯方法的基础上,探讨其弊端以及提出一种新型通讯方法-使用BC-NET模块进行通讯。

【关键词】plc;以太网通讯;BC-NET模块1 传统以太网通讯方法及其弊端目前西门子200plc与上位机通讯一般是采用以太网通讯模块CP243-1或者CP243-2。

第一步,在PC端打开STEP7 Micro/WIN SP9软件,然后用西门子专用下载线连接西门子200CPU 与PC;第二步,点击设置PG/PC接口,弹出如下对话框:图1 设置PG/PC接口选择PC Adapter(PPI),点击确定。

然后在项目栏中点工具,在下拉菜单中选择以太网向导来配置CP243-1。

点击下一步,弹出如下对话框:图2 以太网向导在上图中输入上位机组态中设置的IP地址,点击下一步,因为西门子以太网模块最多允许8台设备与之连接(这也是西门子设备的弊端之一)所以连接数目选择8,之后再对每个连接进行TSAP设置,将以太网模块作为服务器,将上位机作为客户机,以实现上位机对西门子200plc的通讯请求.然后在上位机组态软件中设置相应西门子200plc的TSAP,上位机上就能读取200plc中的数据。

这是最常见的西门子200通讯办法,但是这种方法也不是万能的,假如由于特殊原因,比如更换上位机,再次通讯时需要重新上载程序并设置以太网模块,这时如果程序加密而你又不知道密码,这种情况下就比较难办了。

这里就要谈到我们的主角-BC-NET以太网通讯模块。

脉宽调制开关电源控制IC汇总

脉宽调制开关电源控制IC开关电源这个名字我们大家都不会感到很陌生。

常见的计算系统电源录象机、电视机电源都使用了这种电源技术。

但是常常会觉得这种电源技术好象很复杂根本不可能自已制作此类电源,当然早期的开关电源控制部份集成电路使得开关电源的外围变得如此简单以至于简单过一线性稳压电源。

这里介绍的是 sgs T开关电源这个名字我们大家都不会感到很陌生。

常见的计算系统电源录象机、电视机电源都使用了这种电源技术。

但是常常会觉得这种电源技术好象很复杂根本不可能自已制作此类电源,当然早期的开关电源控制部份集成电路使得开关电源的外围变得如此简单以至于简单过一线性稳压电源。

这里介绍的是 sgs Thomson 公司生产的新型系列集成稳压IC:UCX84X 之中的 UC1842 与系列中的其它 IC 相比,它们的内部电路结构基本上是一致的,只在某些参数如工作环境温度内部基准电压精度,最大占空比系数等方面有所区别所以原则上此类IC的外围电路是可以通用的。

UC1842 为脉冲调制 (PCM) 的开关电源控制 IC。

其封装为 8 脚,可谓简洁说明了。

其内部方框图如下:现介绍各脚功能:1脚为内部误差放大器输出端;2脚为误差放大输入端;1与2 脚之间接有反馈网络以确定反馈放大器增益与频响;2脚输入的反馈电压将与基准2.5V电压比较以产生控制电压;3脚为电流传感器输入引脚,当由电流传感器送来的电压超过1V时及当开关管过流时调宽脉冲就停止输出这样就保护了开关管防止意外损坏。

4脚为接定时电阻电容端口。

由外接的电容电阻决定内部振荡器振荡频率:f=1.8/Rt*Ct;5脚为接地端;6脚为输出调宽脉冲端口,输出的脉冲是推动后的开关管。

其驱动很强,达到 +1A 或 -1A 。

在负载叫容为 1000pF 时上升下降时间仅为 500S,所以很适合于推动VMOS管7脚为电源电压输入端,供电电压可在10V-30V,当电压低于10V时停止工作,工作电流 15mA,功耗是非常小的,因此工作稳定。

基于单片机的串口转以太网设计

基于单片机的串口转以太网设计摘要:随着计算机通信技术和网络技术的发展,在嵌入式系统中集成以太网口实现与其它计算机设备之间的高速数据传输就显得尤为重要。

本文结合以太网接口芯片W5500的主要特点、芯片引脚定义、内部寄存器使用说明,设计了一款基于STM32芯片与W5500高速以太网控制芯片的嵌入式以太网系统,充分发挥了STM32 芯片的Cortex-M3 内核低成本低功耗的特性,同时该设计直接使用W5500固化的TCP/IP协议站,提高了系统的性能。

关键词:以太网以太网接口W5500芯片随着嵌入式系统与网络的密切关系和TCP-IP网络的迅速普及,TCP-IP网络在工业领域具有良好的应用前景。

与过去工业领域广泛使用的串行传输相比,TCP/IP连接器网络具有更宽的带宽、更快的传输速度、更远的传输距离和更广泛的通信服务等特点[1]。

由于TCP和IP通信环境的多样性,很难根据其基本IP环境自动纠正数据传输错误。

由于串行通信的传输方式容易受到普通模式的干扰,因此抗干扰能力差,传输容易出错。

在实际应用中,如果不超过最大传输长度,串行端口的最大传输速度为115200比特/秒[2]。

本文设计的以太网系统允许设备使用串口进行数据传输访问网络,包括串口通信、内置微控制器驱动程序、协议移植和服务器构建。

1系统硬件设计本系统设计采用STM32F103C8T6微控制器和W5500芯片搭建的网络系统,串口转网络硬件系统主要包括微处理器模块、以太网控模块、电源模块、电平转换、网口设计等。

其中,以太网芯片W5500与微控制器芯片STM32F103C8T6之间采用SPI接口,电源电路包含了微控制器芯片STM32F103C8T6所引出的两个串口。

2系统软件设计系统软件设计包含串口相关配置、TCP通信的实现、UDP通信的实现等。

由于W5500强化了协议,所以需要设计与套接字的接口。

这不仅简化了设计过程,还降低了微控制器的处理能力和系统资源的使用。

基于LM3S6432的嵌入式以太网转串口模块设计

片 ,外加 简单 的外 围电路 即可完 成此模块 的设计 。上述传 统 的单 片机 系统便 可以 T P客户端 、服务器 、U P广播 的方 式 C D 与 网络中 的任 何一 台 P C或 主控终 端设 备进行 信息交 换与 共

享 。通过 以太 网用 户可 以远距离 向 串口设 备发送 数据 ,即可

远程终端控 制这是一个瓶 颈。如果 以太 网和 R 一 3 S 2 2串 口通过 某种方式 可 以交换数 据 ,即可实 现这种局 面 。本 文介绍基 于 L S 4 2的嵌入式 以太 网转 串 口模块设计 可实 现这种功 能 , M36 3 在成本 上只需 几十元 R MB的情况下 ,利用 T 公 司以 A M@ I R

W U u r i. Ch n u ZHANG h k i Z i a

(e a owadEet n eh o g o, t.H 'a Z eg h u4 0 0 ) H n nF r r lc o i T cn l yC .Ld, en n, h n zo 50 0 r c o

Ab t a t h u rn x e s e u e o n e n ttc n lg n e n , a e n E h r e n - 3 e ilc mmu ia sr c :T e c re te t n i s fI t r e e h oo y a d d ma d b s d o t e n ta d RS 2 2 s ra o v nc -

电脑编程技巧与维护

基于 L S 4 2的嵌入式 以太 网转 串 口模 块设计 M3 6 3

吴 春锐 ,张 志凯

( 河南正向电子科技有 限公 司,郑州 4 0 0 ) 500

摘 要 :针对 当前互联 网技 术的广泛应 用和 需求,立足 于 实现 以太 网与R 一 3 S 2 2串口接 1数据转换通信 的嵌 入式模 3 '

MEMORY存储芯片TMS320DM642GNZ中文规格书

8TMS320C6745,TMS320C6747SPRS377F –SEPTEMBER 2008–REVISED JUNE 2014Submit Documentation FeedbackProduct Folder Links:TMS320C6745TMS320C6747Device Overview Copyright ©2008–2014,Texas Instruments Incorporated3Device Overview3.1Device CharacteristicsTable 3-1provides an overview of the C6745/6747low power digital signal processor.The table shows significant features of the device,including the capacity of on-chip RAM,peripherals,and the package type with pin count.Table 3-1.Characteristics of the C6745/C6747ProcessorHARDWARE FEATURESC6745C6747PeripheralsNot all peripherals pinsare available at the same time (for moredetail,see the Device Configurations section).EMIFB16bit,up to 128MB SDRAM 16/32bit,up to 256MB SDRAM EMIFAAsynchronous (8-bit bus width)RAM,Flash,NOR,NAND Asynchronous (8/16-bit bus width)RAM,Flash,16bit up to 128MB SDRAM,NOR,NAND Flash Card InterfaceMMC and SD cards supported.EDMA332independent channels,8QDMA channels,2Transfer controllers Timers264-Bit General Purpose (each configurable as 2separate 32-bit timers,1configurable as Watch Dog)UART3(one with RTS and CTS flow control)SPI2(each with one hardware chip select)I 2C2(both Master/Slave)Multichannel AudioSerial Port [McASP]2(each with transmit/receive,FIFO buffer,16/9serializers)3(each with transmit/receive,FIFO buffer,16/9serializers)10/100Ethernet MAC with Management Data I/O 1(RMII Interface)eHRPWM 6Single Edge,6Dual Edge Symmetric,or 3Dual Edge Asymmetric Outputs eCAP 332-bit capture inputs or 332-bit auxiliary PWM outputs eQEP232-bit QEP channels with 4inputs/channel UHPI-1(16-bit multiplexed address/data)USB 2.0(USB0)Full Speed Host Or Device with On-Chip PHY High-Speed OTG Controller with on-chip OTG PHY USB 1.1(USB1)-Full-Speed OHCI (as host)with on-chip PHY General-PurposeInput/Output Port8banks of 16-bit LCD Controller-1RTC-1(32KHz oscillator and seperate power trail.Provides time and date tracking and alarm capability.)PRU Subsystem(PRUSS)2Programmable PRU Cores On-Chip Memory Size (Bytes)320KB RAM 448KB RAMOrganization DSP 32KB L1Program (L1P)/Cache (up to 32KB)32KB L1Data (L1D)/Cache (up to 32KB)256KB Unified Mapped RAM/Cache (L2)DSP Memories can be made accessible to EDMA3,and other peripherals.-ADDITIONAL MEMORY128KB RAMC674x CPU ID +CPU Rev ID Control Status Register (CSR.[31:16])0x1400C674x MegamoduleRevision Revision ID Register (MM_REVID[15:0])0x000051TMS320C6745,TMS320C6747SPRS377F –SEPTEMBER 2008–REVISED JUNE 2014Submit Documentation FeedbackProduct Folder Links:TMS320C6745TMS320C6747Device Overview Copyright ©2008–2014,Texas Instruments Incorporated Table 3-25.General Purpose Input Output Terminal Functions (continued)SIGNAL NAME PIN NOTYPE (1)PULL (2)MUXED DESCRIPTIONPTPZKB GP4USB0_DRVVBUS/GP4[15]-E4O IPD USB0GPIO Bank 4AMUTE1/EPWMTZ/GP4[14]132D4O IPD McASP1,eHRPWM0,eHRPWM1,eHRPWM2AFSR1/GP4[13]166L3I/O IPD McASP1ACLKR1/ECAP2/APWM2/GP4[12]165L2I/O IPD McASP1,eCAP2AHCLKR1/GP4[11]-L1I/O IPD McASP1AFSX1/EPWMSYNCI/EPWMSYNCO/GP4[10]163K4I/O IPD McASP1,eHRPWM0AXR1[9]/GP4[9]-M1I/O IPD McASP1AXR1[8]/EPWM1A/GP4[8]168M2I/O IPD McASP1,eHRPWM1A AXR1[7]/EPWM1B/GP4[7]169M3I/O IPD McASP1,eHRPWM1B AXR1[6]/EPWM2A/GP4[6]170M4I/O IPD McASP1,eHRPWM2A AXR1[5]/EPWM2B/GP4[5]171N1I/O IPD McASP1,eHRPWM2B AXR1[4]/EQEP1B/GP4[4]173N2I/O IPD McASP1,eQEP AXR1[3]/EQEP1A/GP4[3]174P1I/O IPD AXR1[2]/GP4[2]175P2I/O IPD McASP1AXR1[1]/GP4[1]176R2I/O IPD AXR1[0]/GP4[0]1T3I/O IPD GP5EMB_WE_DQM[0]/GP5[15]60K14O IPU EMIFB GPIOBank 5EMB_WE_DQM[1]/GP5[14]85C15O IPU SPI1_SCS[0]/UART2_TXD/GP5[13]8P4O IPU SPI1,UART2SPI1_ENA/UART2_RXD/GP5[12]7R4I IPU AXR1[11]/GP5[11]6T4I/O IPU McASP1AXR1[10]/GP5[10]4N3I/O IPU UART0_TXD/I2C0_SCL/TM64P0_OUT12/GP5[9]/BOOT[9]2R3I IPU UART0,I2C0,BOOT UART0_RXD/I2C0_SDA/TM64P0_IN12/GP5[8]/BOOT[8]3P3O IPU SPI1_CLK/EQEP1S/GP5[7]/BOOT[7]16T6I IPD SPI1,eQEP1,BOOT SPI1_SIMO[0]/I2C1_SDA/GP5[6]/BOOT[6]14N5I/O IPU SPI1,I2C1,BOOT SPI1_SOMI[0]/I2C1_SCL/GP5[5]/BOOT[5]13P5I/O IPU SPI0_SCS[0]/UART0_RTS/EQEP0B/GP5[4]/BOOT[4]9N4I IPU SPI0,UART0,eQEP0,BOOT SPI0_ENA/UART0_CTS/EQEP0A/GP5[3]/BOOT[3]12R5I IPU SPI0_CLK/EQEP1I/GP5[2]/BOOT[2]11T5I IPD SPI0,eQEP1,BOOT SPI0_SIMO[0]/EQEP0S/GP5[1]/BOOT[1]18P6I IPD SPI0,eQEP0,BOOT SPI0_SOMI[0]/EQEP0I/GP5[0]/BOOT[0]17R6I IPD。

一种基于TMS320DM642的多参数火灾探测系统

d yih m n lo o u n rA d ih sab t ra tj m n e o ma c . edsr ue tlg n a l ta pa dac h l r e. n a et ni a mig r r n e T i i tdi el e t g l b t e - p f h tb n i

a dt nf re . tsv r e eep r n a i sse a it g ih r o us n ec u e n a s rd I e i di t x ei th ths y tm c ndsi us e r m n i c a s db r e i i f nh me t t n i f f a y

酒 精灯 的开 关 引起 的干扰 ,具有 较强 的抗 干扰 性 。 同时 ,该探 测 系统 可 以组 网构建 分布 式智 能化 的火 灾监 控系 统 ,具有 良好 的应 用前景 。

关键 词 :T 3 0 M6 2芯 片 数 据采 集 火灾 图像 MS 2 D 4

中图分类 号: P 1 T 37

德州仪器(TI)LM3S1960系列 规格书,Datasheet 资料

S T E L L A R I S E R R A T AStellaris ®LM3S1960RevA2ErrataThis document contains known errata at the time of publication for the Stellaris LM3S1960microcontroller.The table below summarizes the errata and lists the affected revisions.See the data sheet for more details.See also the ARM®Cortex™-M3errata,ARM publication number PR326-PRDC-009450v2.0.Table 1.Revision HistoryDescription Revision Date ■Added issue “Standard R-C network cannot be used on RST to extend POR timing”on page 5.■Clarified issue “General-purpose timer 16-bit Edge Count or Edge Time mode does not load reload value”on page 8to include Edge-Time mode.3.0August 2011■Added issue “Hibernation module does not operate correctly”on page 6,replacing previous Hibernation module errata items.■Minor edits and clarifications.2.10September 2010■Added issue “The RTRIS bit in the UARTRIS register is only set when the interrupt is enabled”on page 9.2.9July 2010■Added issue “External reset does not reset the XTAL to PLL Translation (PLLCFG)register”on page 5.2.8June 2010■Removed issue "Hibernation Module 4.194304-MHz oscillator supports a limited range of crystal load capacitance values"as it does not apply to this part.■Minor edits and clarifications.2.7May 2010■Removed issue "Writes to Hibernation module registers sometimes fail"as it does not apply to this part.■Added issue "Hibernation Module 4.194304-MHz oscillator supports a limited range of crystal load capacitance values."■Minor edits and clarifications.2.6April 2010■Removed issue "Setting Bit 7in I2C Master Timer Period (I2CMTPR)register may have unexpected results".The data sheet description has changed such that this is no longer necessary.■Minor edits and clarifications.2.5April 2010■Added issue “The General-Purpose Timer match register does not function correctly in 32-bit mode”on page 8.■Added issue "Setting Bit 7in I2C Master Timer Period (I2CMTPR)register may have unexpected results".2.4February 2010■"Hard Fault possible when waking from Sleep or Deep-Sleep modes and Cortex-M3Debug Access Port (DAP)is enabled"has been removed and the content added to the LM3S1960data sheet.2.3Jan 2010Started tracking revision history.2.2Dec 2009Stellaris LM3S1960A2Errata Table2.List of ErrataStellaris LM3S1960A2Errata1JTAG and Serial Wire Debug1.1JTAG pins do not have internal pull-ups enabled at power-on resetDescription:Following a power-on reset,the JTAG pins TRST,TCK,TMS,TDI,and TDO(PB7and PC[3:0])donot have internal pull-ups enabled.Consequently,if these pins are not driven from the board,twothings may happen:■The JTAG port may be held in reset and communication with a four-pin JTAG-based debugger may be intermittent or impossible.■The receivers may draw excess current.Workaround:There are a number of workarounds for this problem,varying in complexity and impact:1.Add external pull-up resistors to all of the affected pins.This workaround solves both issues ofJTAG connectivity and current consumption.2.Add an external pull-up resistor to TRST.Firmware should enable the internal pull-ups on theaffected pins by setting the appropriate PUE bits of the appropriate GPIO Pull-Up Select(GPIOPUR)registers as early in the reset handler as possible.This workaround addresses theissue of JTAG connectivity,but does not address the current consumption other than to limitthe affected period(from power-on reset to code execution).3.Pull-ups on the JTAG pins are unnecessary for code loaded via the SWD interface or via theserial boot loader.Loaded firmware should enable the internal pull-ups on the affected pins bysetting the appropriate PUE bits of the appropriate GPIOPUR registers as early in the resethandler as possible.This method does not address the current consumption other than to limitthe affected period(from power-on reset to code execution).Silicon Revision Affected:A21.2JTAG INTEST instruction does not workDescription:The JTAG INTEST(Boundary Scan)instruction does not properly capture data.Workaround:None.Silicon Revision Affected:A2Stellaris LM3S1960A2Errata2System Control2.1Clock source incorrect when waking up from Deep-Sleep mode insome configurationsDescription:In some clocking configurations,the core prematurely starts executing code before the main oscillator(MOSC)has stabilized after waking up from Deep-Sleep mode.This situation can cause undesirablebehavior for operations that are frequency dependent,such as UART communication.This issue occurs if the system is configured to run off the main oscillator,with the PLL bypassedand the DSOSCSRC field of the Deep-Sleep Clock Configuration(DSLPCLKCFG)register set touse the internal12-MHz oscillator,30-KHz internal oscillator,or32-KHz external oscillator.Whenthe system is triggered to wake up,the core should wait for the main oscillator to stabilize beforestarting to execute code.Instead,the core starts executing code while being clocked from thedeep-sleep clock source set in the DSLPCLKCFG register.When the main oscillator stabilizes,theclock to the core is properly switched to run from the main oscillator.Workaround:Run the system off of the main oscillator(MOSC)with the PLL enabled.In this mode,the clocksare switched at the proper time.If the main oscillator must be used to clock the system without the PLL,a simple wait loop at thebeginning of the interrupt handler for the wake-up event should be used to stall thefrequency-dependent operation until the main oscillator has stabilized.Silicon Revision Affected:A22.2PLL may not function properly at default LDO settingDescription:In designs that enable and use the PLL module,unstable device behavior may occur with the LDOset at its default of2.5volts or below(minimum of2.25volts).Designs that do not use the PLLmodule are not affected.Workaround:Prior to enabling the PLL module,it is recommended that the default LDO voltage setting of2.5Vbe adjusted to2.75V using the LDO Power Control(LDOPCTL)register.Silicon Revision Affected:A22.3I/O buffer5-V tolerance issueDescription:GPIO buffers are not5-V tolerant when used in open-drain mode.Pulling up the open-drain pinabove4V results in high current draw.Stellaris LM3S1960A2ErrataWorkaround:When configuring a pin as open drain,limit any pull-up resistor connections to the3.3-V power rail.Silicon Revision Affected:A22.4PLL Runs Fast When Using a3.6864-MHz CrystalDescription:If the PLL is enabled,and a3.6864-MHz crystal is used,the PLL runs4%fast.Workaround:Use a different crystal whose frequency is one of the other allowed crystal frequencies(see thevalues shown for the XTAL bit in the RCC register).Silicon Revision Affected:A22.5External reset does not reset the XTAL to PLL Translation(PLLCFG)registerDescription:Performing an external reset(anything but power-on reset)reconfigures the XTAL field in theRun-Mode Clock Configuration(RCC)register to the6MHz setting,but does not reset the XTALto PLL Translation(PLLCFG)register to the6MHz setting.Consider the following sequence:1.Performing a power-on reset results in XTAL=6MHz and PLLCFG=6MHz2.Write an8MHz value to the XTAL field results in XTAL=8MHz and PLLCFG=8MHz3.RST asserted results in XTAL=6MHz and PLLCFG=8MHzIn the last step,PLLCFG was not reset to its6MHz setting.If this step is followed by enabling thePLL to run from an attached6-MHz crystal,the PLL then operates at300MHz instead of400MHz.Subsequently configuring the XTAL field with the8MHz setting does not change the setting ofPLLCFG.Workaround:Set XTAL in PLLCFG to an incorrect value,and then to the desired value.The second changeupdates the register correctly.Do not enable the PLL until after the second change.Silicon Revision Affected:A22.6Standard R-C network cannot be used on RST to extend POR timingDescription:The standard R-C network on RST does not work to extend POR timing beyond the10ms on-chipPOR.Instead of following the standard capacitor charging curve,RST jumps straight to3V at powerStellaris LM3S1960A2Errataon.The capacitor is fully charged by current out of the RST pin and does not extend or filter thepower-on condition.As a result,the reset input is not extended beyond the POR.Workaround:Add a diode to block the output current from RST.This helps to extend the RST pulse,but alsomeans that the R-C is not as effective as a noise filter.Silicon Revision Affected:A23Hibernation Module3.1Hibernation module does not operate correctlyDescription:The Hibernation module on this microcontroller does not operate correctly.Workaround:This errata item does not apply to many Stellaris devices,including the LM3S1166,LM3S1636,LM3S1969,and LM3S2919.Refer to the Stellaris Product Selector Guide(/stellaris_search)and Errata documents to find an alternative microcontroller that meetsthe design requirements for your application.Silicon Revision Affected:A24Flash Controller4.1MERASE bit of the FMC register does not erase the entire FlasharrayDescription:The MERASE bit of the Flash Memory Control(FMC)register does not erase the entire Flash array.If the contents of the Flash Memory Address(FMA)register contain a value less than0x20000,only the first128KB of the Flash array are erased.If bit17(value of0x20000)is set,then only theupper address range of Flash(greater than128KB)is erased.Workaround:If the entire array must be erased,the following sequence is recommended:1.Write a value of0x00000000to the FMA register.2.Write a value of0xA4420004to the FMC register,and poll bit2until it is cleared.3.Write a value of0x00020000to the FMA register.4.Write a value of0xA4420004to the FMC register,and poll bit2until it is cleared.The entire array can also be erased by individually erasing all of the pages in the array.Stellaris LM3S1960A2ErrataSilicon Revision Affected:A25GPIO5.1GPIO input pin latches in the Low state if pad type is open drainDescription:GPIO pins function normally if configured as inputs and the open-drain configuration is disabled.Ifopen drain is enabled while the pin is configured as an input using the GPIO Alternate FunctionSelect(GPIOAFSEL),GPIO Open Drain Select(GPIOODR),and GPIO Direction(GPIODIR)registers,then the pin latches Low and excessive current(into pin)results if an attempt is made todrive the pin High.The open-drain device is not controllable.A GPIO pin is not normally configured as open drain and as an input at the same time.A user maywant to do this when driving a signal out of a GPIO open-drain pad while configuring the pad as aninput to read data on the same pin being driven by an external device.Bit-banging a bidirectional,open-drain bus(for example,I2C)is an example.Workaround:If a user wants to read the state of a GPIO pin on a bidirectional bus that is configured as anopen-drain output,the user must first disable the open-drain configuration and then change thedirection of the pin to an input.This precaution ensures that the pin is never configured as an inputand open drain at the same time.A second workaround is to use two GPIO pins connected to the same bus signal.The first GPIOpin is configured as an open-drain output,and the second is configured as a standard input.Thisway the open-drain output can control the state of the signal and the input pin allows the user toread the state of the signal without causing the latch-up condition.Silicon Revision Affected:A25.2GPIO pins may glitch during power supply ramp upDescription:Upon completing a POR(power on reset)sequence,the GPIO pins default to a tri-stated inputcondition.However,during the initial ramp up of the external V DD supply from0.0V to3.3V,theGPIO pins are momentarily configured as output drivers during the time the internal LDO circuit isalso ramping up.As a result,a signal glitch may occur on GPIO pins before both the external V DDsupply and internal LDO voltages reach their normal operating conditions.This situation can occurwhen the V DD and LDO voltages ramp up at significantly different rates.The LDO voltage ramp-uptime is affected by the load capacitance on the LDO pin,therefore,it is important to keep this loadat a nominal1µF value as recommended in the data sheet.Adding significant more capacitanceloading beyond the specification causes the time delay between the two supply ramp-up times togrow,which possibly increases the severity of the glitching behavior.Workaround:Ensuring that the V DD power supply ramp up is a fast as possible helps minimize the potential forGPIO glitches.Follow guidelines for LDO pin capacitive loading documented in the electrical sectionStellaris LM3S1960A2Errataof the data sheet.System designers must ensure that,during the V DD supply ramp-up time,possibleGPIO pin glitches can cause no adverse effects to their systems.Silicon Revision Affected:A26General-Purpose Timers6.1General-purpose timer Edge Count mode count error when timeris disabledDescription:When a general-purpose timer is configured for16-Bit Input Edge Count Mode,the timer(A or B)erroneously decrements by one when the Timer Enable(TnEN)bit in the GPTM Control(GPTMCTL)register is cleared(the timer is disabled).Workaround:When the general-purpose timer is configured for Edge Count mode and software needs to“stop”the timer,the timer should be reloaded with the current count+1and restarted.Silicon Revision Affected:A26.2General-purpose timer16-bit Edge Count or Edge Time mode doesnot load reload valueDescription:In Edge Count or Edge Time mode,the input events on the CCP pin decrement the counter until thecount matches what is in the GPTM Timern Match(GPTMTnMATCHR)register.At that point,aninterrupt is asserted and then the counter should be reloaded with the original value and countingbegins again.However,the reload value is not reloaded into the timer.Workaround:Rewrite the GPTM Timern Interval Load(GPTMTnILR)register before restarting.Silicon Revision Affected:A26.3The General-Purpose Timer match register does not functioncorrectly in32-bit modeDescription:The GPTM Timer A Match(GPTMTAMATCHR)register triggers a match interrupt when the lower16bits match,regardless of the value of the upper16bits.Workaround:None.Stellaris LM3S1960A2ErrataSilicon Revision Affected:A27UART7.1The RTRIS bit in the UARTRIS register is only set when the interruptis enabledDescription:The RTRIS(UART Receive Time-Out Raw Interrupt Status)bit in the UART Raw Interrupt Status(UARTRIS)register should be set when a receive time-out occurs,regardless of the state of theenable RTIM bit in the UART Interrupt Mask(UARTIM)register.However,currently the RTIM bitmust be set in order for the RTRIS bit to be set when a receive time-out occurs.Workaround:For applications that require polled operation,the RTIM bit can be set while the UART interrupt isdisabled in the NVIC using the IntDisable(n)function in the StellarisWare Peripheral Driver Library,where n is21,22,or49depending whether UART0,UART1or UART2is used.With thisconfiguration,software can poll the RTRIS bit,but the interrupt is not reported to the NVIC.Silicon Revision Affected:A28PWM8.1PWM pulses cannot be smaller than dead-band timeDescription:The dead-band generator in the PWM module has undesirable effects when receiving input pulsesfrom the PWM generator that are shorter than the dead-band time.For example,providing a4-clock-wide pulse into the dead-band generator with dead-band times of20clocks(for both risingand falling edges)produces a signal on the primary(non-inverted)output that is High except for40clocks(the combined rising and falling dead-band times),and the secondary(inverted)output isalways Low.Workaround:User software must ensure that the input pulse width to the dead-band generator is greater thanthe dead-band delays.Silicon Revision Affected:A28.2PWM interrupt clear misses in some instancesDescription:It is not possible to clear a PWM generator interrupt in the same cycle when another interrupt fromthe same PWM generator is being asserted.PWM generator interrupts are cleared by writing a1to the corresponding bit in the PWM Interrupt Status and Clear(PWMnISC)register.If a write toclear the interrupt is missed because another interrupt in that PWM generator is being asserted,Stellaris LM3S1960A2Erratathe interrupt condition still exists,and the PWM interrupt routine is called again.System problemscould result if an interrupt condition was already properly handled the first time,and the softwaretries to handle it again.Note that even if an interrupt event has not been enabled in the PWMInterrupt and Trigger Enable(PWMnINTEN)register,the interrupt is still asserted in the PWMRaw Interrupt Status(PWMnRIS)register.Workaround:In most instances,performing a double-write to clear the interrupt greatly decreases the chancethat the write to clear the interrupt occurs on the same cycle as another interrupt.Because eachgenerator has six possible interrupt events,writing the PWMnISC register six times in a rowguarantees that the interrupt is cleared.If the period of the PWM is small enough,however,thismethod may not be practical for the application.Silicon Revision Affected:A28.3PWM generation is incorrect with extreme duty cyclesDescription:If a PWM generator is configured for Count-Up/Down mode,and the PWM Load(PWMnLOAD)register is set to a value N,setting the compare to a value of1or N-1results in steady state signalsinstead of a PWM signal.For example,if the user configures PWM0as follows:■PWMENABLE=0x00000001–PWM0Enabled■PWM0CTL=0x00000007–Debug mode enabled–Count-Up/Down mode–Generator enabled■PWM0LOAD=0x00000063–Load is99(decimal),so in Count-Up/Down mode the counter counts from zero to99and back down to zero(200clocks per period)■PWM0GENA=0x000000b0–Output High when the counter matches comparator A while counting up–Output Low when the counter matches comparator A while counting down■PWM0DBCTL=0x00000000–Dead-band generator is disabledIf the PWM0Compare A(PWM0CMPA)value is set to0x00000062(N-1),PWM0should output a2-clock-cycle long High pulse.Instead,the PWM0output is a constant High value.If the PWM0CMPA value is set to0x00000001,PWM0should output a2-clock-cycle long negative(Low)pulse.Instead,the PWM0output is a constant Low value.Stellaris LM3S1960A2ErrataWorkaround:User software must ensure that when using the PWM Count-Up/Down mode,the compare valuesmust never be1or the PWMnLOAD value minus one(N-1).Silicon Revision Affected:A28.4PWMINTEN register bit does not function correctlyDescription:In the PWM Interrupt Enable(PWMINTEN)register,the IntPWM0(bit0)bit does not functioncorrectly and has no effect on the interrupt status to the ARM Cortex-M3processor.This bit shouldnot be used.Workaround:PWM interrupts to the processor should be controlled with the use of the PWM0-PWM2Interruptand Trigger Enable(PWMnINTEN)registers.Silicon Revision Affected:A28.5Sync of PWM does not trigger"zero"actionDescription:If the PWM Generator Control(PWM0GENA)register has the ActZero field set to0x2,then theoutput is set to0when the counter reaches0,as expected.However,if the counter is cleared bysetting the appropriate bit in the PWM Time Base Sync(PWMSYNC)register,then the"zero"actionis not triggered,and the output is not set to0.Workaround:None.Silicon Revision Affected:A28.6PWM"zero"action occurs when the PWM module is disabledDescription:The zero pulse may be asserted when the PWM module is disabled.Workaround:None.Silicon Revision Affected:A2August04,2011/Rev.3.011Texas Instruments9QEI 9.1QEI index resets position when index is disabledDescription:When the QEI module is configured to not reset the position on detection of the index signal (thatis,the ResMode bit in the QEI Control (QEICTL)register is 0),the module resets the position whenthe index pulse occurs.The position counter should only be reset when it reaches the maximumvalue set in the QEI Maximum Position (QEIMAXPOS)register.Workaround:Do not rely on software to disable the index pulse.Do not connect the index pulse if it is not needed.Silicon Revision Affected:A29.2QEI hardware position can be wrong under certain conditionsDescription:The QEI Position (QEIPOS)register can be incorrect if the QEI is configured for quadrature phasemode (SigMode bit in QEICTL register =0)and to update the position counter of every edge ofboth PhA and PhB (CapMode bit in QEICTL register =1).This error can occur if the encoder isstepped in the reverse direction,stepped forward once,and then continues in the reverse direction.The following sequence of transitions on the PhA and PhB pins causes the error:PhBAssuming the starting position prior to the above PhA and PhB sequence is 0,the position after thefalling edge on PhB should be -3,however the QEIPOS register will show the position to be -1.Workaround:Configure the QEI to update the position counter on every edge on PhA only (CapMode bit in QEICTLregister =0).The effective resolution is reduced by 50%.If full resolution position detection is requiredby updating the position counter on every edge of both PhA and PhB ,no workaround is available.Hardware and software must take this into account.Silicon Revision Affected:A2August 04,2011/Rev.3.0Texas Instruments12Stellaris LM3S1960A2ErrataCopyright©2007-2011Texas Instruments Incorporated All rights reserved.Stellaris and StellarisWare are registered trademarks of Texas Instruments Incorporated.ARM and Thumb are registered trademarks and Cortex is a trademark of ARM Limited.Other names and brands may be claimed as the property of others.Texas Instruments Incorporated108Wild Basin,Suite350Austin,TX78746/stellaris/sc/technical-support/product-information-centers.htmAugust04,2011/Rev.3.0Texas Instruments13IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements,improvements, and other changes to its products and services at any time and to discontinue any product or service without notice.Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right, or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use. TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use any non-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements.Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAudio /audio Communications and Telecom /communicationsAmplifiers Computers and Peripherals /computersData Converters Consumer Electronics /consumer-appsDLP®Products Energy and Lighting /energyDSP Industrial /industrialClocks and Timers /clocks Medical /medicalInterface Security /securityLogic Space,Avionics and Defense /space-avionics-defense Power Mgmt Transportation and Automotive /automotiveMicrocontrollers Video and Imaging /videoRFID OMAP Mobile Processors /omapWireless Connctivity /wirelessconnectivityTI E2E Community Home Page Mailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2011,Texas Instruments Incorporated。

三极管丝印代码查询表格

HSMS-286B HSMS-286B fT fT fT 1.1GHz 1.1GHz 1.1GHz

dual

HSMS-286B

T4 T4 T42 T42 T43 T43 T44 T44 T5 T5 T5 T52 T53 T55 T6 T6 T6661 T7 T7 T7 T71 T71 T72 T72 T73 T73 T74 T74 T75 T75 T76 T76 T76 T77 T7p T7t T8 T8 T8 T81 T81 T82 T82 T83

SOT23 SOT23 SOT23 SOT23 SOT23R

BCX18 BCX18 HSMS-2862 TN2460T HSMS-286C PDTA114TU PDTC114TU MMFT2406T1 PMBT3906 PMST3906 PMBT2907 PMBTA92 PMSTA92 PMBTA93 PMSTA93 PMBT2907A PMBT2907A PMBTA56 PMSTA56 PMBTA55 PMSTA55 PMBT5401 PMST5401 BCX18 BCX18 PMBT4403 PMST4403 PMBTA63 PMBTA64 PMBT4401 PMST4401 BSS63 BSS63 HSMS-2863 HSMS-286E MMFT3166T1 2SC4182 2SC4182 2SC4182 BSR20 BSR20A BCX17R HSMS-2864 BCX17R

SOT23 SOT23 SOT23 SOT23 SOT323 SOT323 SOT323 SOT223 SOT23 SOT323 SOT23 SOT23 SOT323 SOT23 SOT323 SOT23 SOT323 SOT23 SOT323 SOT23 SOT323 SOT23 SOT323 SOT23 SOT23 SOT23 SOT323 SOT23 SOT23 SOT23 SOT323 SOT23 SOT23 SOT23 SOT323 SOT223

基于LM3S6432 的串口以太网转换器的设计与实现

基于LM3S6432 的串口以太网转换器的设计与实现作者:罗彩洪陈晓敦来源:《电脑知识与技术》2013年第02期摘要:对于当前物联网的应用及需求,以Cortex-M3芯片为模版,实现串口与以太网之间的数据转换与传送,该文简要介绍了转换设备的硬件与软件设计,通过实际应用验证其的可行性。

关键词:LM3S6432、Cortex-M3、串口、以太网中图分类号:TP393 文献标识码:A 文章编号:1009-3044(2013)02-0252-05近几年来,随着物联网的推广,越来越多的设备需要联入网路工作,通过现有的精简的TCP/IP协议栈来实现网路通信。

对于现有的32位的ARM芯片来说,集成这样的一个带有TCP/IP协议的通信系统,是件很容易的事。

但是对于8位的单片机来说却是件难事,固有的FLASH空间限制了其使用,那么使用8位单片机的产品就不能实现网路通信了吗?答案是否定的。

串口以太网转换器就是将得到的8位单片机的串口,通过内部转换以网络帧的形式进行通信,以达到网络通信的目的,大大增加了原串口设备的远程控制收发的功能。

1 转换器的硬件规划与设计转换器在MCU的选择上,根据功耗、存储空间,硬件特点等方面,我们选择TI公司的LM3S6432 作为转换器的主芯片。

如果说软件设计是系统的思想的话,那么硬件设计就是整个系统的躯干了。

整个转换器在硬件设计上由核心板+底板+ 接线板构成,核心板可用于后期的芯片升级和更换,接主板提供了主要的供电和IO接口,接线板方便后期的线材链接。

电源部分采用DC-DC电路作为系统电源部份,输入电压12V,输出为5V和3.3V两路。

本系统MCU芯片LM3S6432是LuminaryMicro(TI)公司推出的基于ARMCortex-M3嵌入式内核的微控制器。

该微控制器包括以下特性:32位ARMCortexTM-M3V7M架构;工作频率为50-MHz;96KB单周期Flash,32KB单周期访问的SRAM;3个通用定时器模块(GPTM),每个提供2个16-位定时器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

网络开发笔记之数据采集――云*飞扬2010-11-6一TCP Socket (1)二打开TCP连接 (1)三TCP主动打开 (1)四TCP被动打开 (1)五发送TCP数据 (2)六数据的采集与发送(开发板客户端) (2)七数据的接收(PC服务器端) (5)八数据采集效果图 (7)一TCP Socket传输控制协议(TCP)在因特网协议(IP)之上运行。

TCP是一种面向连接的可靠的字节流服务。

面向连接是指两个应用程序使用TCP时,须在它们交换数据之前建立TCP连接。

TCP是一个双工通信协议,就是说每一个TCP连接支持一对字节流,收发双方各一个。

它对每一个由于错误没有到达目标文件的数剧进行重传。

如果接收数据损坏,它也进行重发。

当数据被传送时,TCP协议按相同的序列依次传递数据。

二打开TCP连接RL-TCPnet是基于客户/服务器模式的操作,并且TCP连接的设置也是基于此。

客户和服务器模式都是通过一个打开操作来准备连接。

然而,有两种打开方式:主动打开:客户机使用TCP扮演“积极角色”,处理并通过发送TCP信息来启动并初始化连接(SYN信息)。

被动打开:一个服务器进程,设计成使用TCP,使用一个更加宽松的方法。

它通过被动方式打开TCP连接,就像说“我在这,我在等待希望与我交谈并通过下面的端口号发送信息给我的客户机”。

这种打开方式称为被动,是因为除了指示进程以外,服务器没有做任何事。

被动打开方式,事实上,是服务器在等待一个来自一特殊客户的主动打开。

然而,不是所有的RL-TCPnet APIs支持该能力。

三TCP主动打开当试着连接一个远程服务器时,嵌入式应用程序使用TCP Active Open,例如发送邮件。

这种情况下,TCPnet系统是TCP连接的发起者.打开活动的TCP连接,须以下几步:在Net_Config.c配置文件中打开TCP socket。

使用tcp_get_socket()函数分配TCP socket。

通过调用tcp_connect()函数初始化TCP连接。

四TCP被动打开当运行服务器应用程序时TCP被以被动方式打开,例如WEB浏览器。

TCP Socket以被动方式打开,并等待输入连接。

按以下步骤被动打开TCP连接:在net_config.c配置文件中允许TCP Socket。

调用tcp_get_socket()函数,分配一闲置的TCP Socket。

调用tcp_listen()函数,允许TCP Socket的监听模式。

五发送TCP数据TCP协议是一种字节流服务。

它不关心发送的数据的格式。

只是简单的接收数据,将其压缩成TCP包,并发送给远程对等体。

之后TCP Socket把最后的包保存在内存里,并等待远程对等体的响应回复。

如果时间超出之后,发送的包仍没有得到对等体的响应,将会重新发送该包。

在包得到响应或Socket连接失败之前,该过程将重复多次。

为了让协议实现尽可能的小一些、不致出现资源短缺。

TCP Socket不能让大量的数据在缓冲中而等待响应回复。

它只将最后的包的发送保存在内存中,直到其被响应。

当被响应以后,释放内存空间。

六数据的采集与发送(开发板客户端)我现模似一下数据的采集,着重于在数据的发送上。

我以tcp客服端为例。

#include<RTL.h>#include<stdio.h>#include<LM3Sxxxx.H>#include<string.h>//IP等配置信息//--------<<<Use Configuration Wizard in Context Menu>>>-----------------//<h>Remote IP Address//====================////<o>IP1:Address byte1<0-255>//<i>Default:192#define IP1192//<o>IP2:Address byte2<0-255>//<i>Default:168#define IP2168//<o>IP3:Address byte3<0-255>//<i>Default:0#define IP314//<o>IP4:Address byte4<0-255>//<i>Default:100#define IP48//</h>//<o>Remote Port<1-65535>//<i>Do not set number of port too small,//<i>maybe it is already used.//<i>Default:1001#define PORT_NUM1001//<o>Communication Protocol<0=>TCP<1=>UDP//<i>Selecet a protocol for sending data.#define PROTOCOL1//<o>LED Blinking speed<1-100>//<i>Blinking speed=SPEED*100ms//<i>Default:2#define SPEED2//-------------<<<end of configuration section>>>-----------------------#define BLINKLED0x01/*Command for blink the leds on board*/#define SENDLEN2/*Number of bytes to send*/#define TCP1BOOL tick;U8socket_tcp;U8Rem_IP[4]={IP1,IP2,IP3,IP4};static void init(){//初始化SysCtlClockSet(SYSCTL_SYSDIV_4|SYSCTL_USE_PLL|SYSCTL_OSC_MAIN|SYSCTL_XTAL_8MHZ); SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOF);GPIOPadConfigSet(GPIO_PORTF_BASE,GPIO_PIN_0, GPIO_STRENGTH_2MA,GPIO_PIN_TYPE_STD);GPIODirModeSet(GPIO_PORTF_BASE,GPIO_PIN_0, GPIO_DIR_MODE_OUT);SysTickPeriodSet(SysCtlClockGet()/10);SysTick Enable();}static void timer_poll(){//RL-TCPnet时钟if((HWREG(NVIC_ST_CTRL)>>16)&1){/*Timer tick every100ms*/timer_tick();tick=__TRUE;}}U16tcp_callback(U8soc,U8evt,U8*ptr,U16par){//TCP回调函数soc=soc;par=par;evt=evt;ptr=ptr;return(0);}void send_data(U8p2val){//发送数据U8*sendbuf;static U16p2=0;U8*buf;if(socket_tcp!=0){switch(tcp_get_state(socket_tcp)){case TCP_STATE_FREE:case TCP_STATE_CLOSED:tcp_connect(socket_tcp,Rem_IP,PORT_NUM,0);//连接服务器break;case TCP_STATE_CONNECT:if(tcp_check_send(socket_tcp)==__TRUE){buf=tcp_get_buf(20);//分配bufp2++;//模拟发送数据if(p2>10000)p2=0;sprintf(buf,”%6d”,p2);tcp_send(socket_tcp,buf,strlen((char*)buf)+1);//发送数据,多发一字//节,便于存结束符。

}break;}}}int main(void){U8p2val,cnt,lshf;U8protocol;init();init_TcpNet();socket_tcp=tcp_get_socket(TCP_TYPE_CLIENT,0,10,tcp_callback); p2val=1;cnt=0;lshf=1;while(1){timer_poll();main_TcpNet();if(tick==__TRUE){if(++cnt==SPEED){GPIOPinWrite(GPIO_PORTF_BASE,GPIO_PIN_0,p2val&1);send_data(p2val);p2val=lshf?(p2val<<1):(p2val>>1);if(p2val==0x80)lshf=0;if(p2val==0x01)lshf=1;cnt=0;}tick=__FALSE;}}}七数据的接收(PC服务器端)用MFC WINSOC编程,这里只是一个简单的DOS环境程序。

#include<WINSOCK2.H>//包含WinSock#include<stdio.h>void main(void)WORD wVersionRequested;WSADATA wsaData;int err;int sockSrv;int sockClient;SOCKADDR_IN addrSrv;SOCKADDR_IN addrClient;int len;char buf[20];wVersionRequested=MAKEWORD(1,1);//WinSock版本err=WSAStartup(wVersionReq uested,&wsaData);//提供WinSock环境if(err!=0){return;}if(LOBYTE(wsaData.wVersion)!=1||HIBYTE(wsaData.wVersion)!= 1){WSACleanup();return;}sockSrv=socket(AF_INET,SOCK_STREAM,0);//创建一个WinSockaddrSrv.sin_addr.S_un.S_addr=htonl(INADDR_ANY);addrSrv.sin_family=AF_INET;addrSrv.sin_port=htons(1001);bind(sockSrv,(SOCKADDR*)&addrSrv,sizeof(SOCKADDR));//绑定Winsock listen(sockSrv,2);//监听len=sizeof(SOCKADDR);while(1){sockClient=accept(sockSrv,(SOCKADDR*)&addrClient,&len);//接受连接recv(sockClient,buf,20,0);//接收数据closesocket(sockClient);//关闭winsockprintf(buf);printf("\r\n");}closesocket(sockSrv);WSACleanup();//清除WinSock环境八数据采集效果图。