Cadence设计工具通过台积电16nm FinFET制程认证

ASIC与CPU、GPU、FPGA区别?

ASIC与CPU、GPU、FPGA区别?继4月初联发科宣布扩大ASIC产品阵线,推出业内首个7nm 56G PAM4 SerDes IP之后,4月24日,在联发科深圳办公室,联发科举行了一场小型的媒体会,联发科副总经理暨智能设备事业群总经理游人杰及联发科智能显示暨客制化芯片事业部行销处处长彭建凯首次揭秘了联发科的ASIC业务。

什么是ASIC芯片?近年随着以比特币为代表的虚拟货币市场的火爆,催生了一大批生产“挖掘”虚拟货币设备的“矿机”厂商,其中最为知名的要属比特大陆了。

而比特大陆之所以能够在矿机市场异军突起,则主要得益于其自主设计的针对比特币矿机的ASIC芯片。

因为相对于CPU、GPU来说,采用专用的ASIC芯片来“挖矿”更具效率。

以比特大陆的Antminer S9矿机为例,其内部集成了189个ASIC芯片(BM1387),而且采用的是台积电16nm FinFET制程。

同样,目前主流的矿机厂商都采用的是定制的ASIC芯片。

这也使得ASIC芯片开始被大众所熟知。

但是ASIC芯片并不仅仅能被用于“挖矿”,还被用于包括人工智能在内等众多领域。

那么什么才是ASIC芯片?它与我们常见的CPU、GPU等通用型芯片相比又有何不同?早在1981年3月,Sinclair公司推出了一款8位个人电脑ZX81,其所采用的Z80处理器则被认为是最早的ASIC原型。

实际上ASIC是Application-Specific In te grated Circuit(应用型专用集成电路)的缩写,是一种专用芯片,是为了某种特定的需求而专门定制的芯片的统称。

比如专用的音频、视频处理器,同时目前很多专用的AI芯片业可以看作是ASIC 的一种。

与CPU、GPU、FPGA相比如何?CPU与GPU都是我们常见的通用型芯片,它们在各自领域都可以高效地完成任务,但当同样应用于通用基础计算领域时,设计架构的差异直接导致了两种芯片性能的差异。

CPU作为通用处理器,除了满足计算要求,为了更好的响应人机交互的应用,它要能处理复杂的条件和分支,以及任务之间的同步协调,所以芯片上需要很多空间来进行分支预测与优化(control),保存各种状态(cache)以降低任务切换时的延时。

【金立S10体验测评】金立f6特殊功能在哪里

【金立S10体验测评】金立f6特殊功能在哪里5月26日,金立正式公布了新一代的拍照手机金立S10。

官方介绍,金立S10大幅优化了拍摄硬件,实现了硬件级的实时虚化,四摄拍照能够给消费者带来单反级的摄影体验。

那么金立S10是否像其所说的一样出色呢?小编拿到了金立S10真机,并第一时间为您带来使用体验。

金立S10体验测评小编拿到的是金立S10的工程样机,所有的测评体验均基于该样机,因此在部分地方还和正式量产零售机会有所区别。

外观金立S10一共拥有樱花金、暗夜黑、靛灰蓝、樱草绿这四种颜色,小编拿到的是樱草绿款。

草绿色的机身倒是符合目前春天万物复苏的气候,给人以一种舒适的感觉。

或许有人会将这款手机后背的金立LOGO错认为是后置指纹,但其实并非如此。

这仅仅是一颗圆形的金立LOGO,这颗笑脸经过黑色处理后显得非常低调,与背面所有元素都融合在了一起,几乎没有其他元素的干扰。

金立S10前置指纹设计,采用的是不可按压式指纹模块。

金立S10机型圆润,实际摸起来的手感、握持感均比较不错的。

有关于金立S10的其他外观细节,小编已经在前面发布的金立S10开箱文章中说明。

和其他满满商务气息的手机相比,金立S10更加符合年轻人的口味,无论是从配色还是手机布局,显得更加青春活泼。

一款手机外观很重要,但更核心的还是其内在配置和系统。

而金立S10在这方面表现如何呢?系统:抛弃商务气息,更加青春和活泼与金立M系列不同,由于金立S10定位于年轻人,因此整个手机也不再具有商务气息,而金立S10内置的amigo OS也是一样,抛弃了商务手机的严肃感,给消费者带来的是一股清新活泼的气息。

金立S10搭载了最新的基于安卓7.0开发amigo OS 4.0系统,相比较于上一代的amigo OS系统,amigo OS 4.0更加地流畅。

或许是为了迎合年轻用户群体的感官体验、操作体验,金立S10的amigo OS 4.0系统UI设计和iOS高度相似,仅看界面截图,不仔细分辨的话,还以为我们拿到了一个安装着iOS系统的金立S10手机。

1+X集成电路理论练习题含参考答案

1+X集成电路理论练习题含参考答案一、单选题(共40题,每题1分,共40分)1、在电子产品测试中需保证测试环境稳定,其中使用环境稳定是指()。

A、使用人员操作得当B、硬件的工作参数稳定C、软件的工作参数稳定D、模拟真实用户使用时的场景正确答案:D2、以全自动探针台为例,关于上片的步骤,下列所述正确的是:( )。

A、打开盖子→花篮放置→花篮下降→花篮到位→花篮固定→合上盖子B、打开盖子→花篮放置→花篮到位→花篮下降→花篮固定→合上盖子C、打开盖子→花篮放置→花篮下降→花篮固定→花篮到位→合上盖子D、打开盖子→花篮放置→花篮固定→花篮下降→花篮到位→合上盖子正确答案:D答案解析:以全自动探针台为例,上片的步骤为:打开盖子→花篮放置→花篮固定→花篮下降→花篮到位→合上盖子。

3、转塔式分选机设备进行编带后,进入( )环节。

A、上料B、测试C、外观检查D、真空包装正确答案:C答案解析:转塔式分选机设备芯片检测工艺的操作步骤一般为:上料→测试→编带→外观检查→真空包装。

4、通常情况下,一个内盒中装入的DIP管装芯片( )颗。

A、3000B、1000C、5000D、2000正确答案:D答案解析:一般情况下,一个内盒中装入的DIP管装芯片2000颗。

5、元器件的引线直径与印刷焊盘孔径应有()的合理间隙。

A、0.1~0.4mmB、0.2~0.3mmC、0.1~0.3mmD、0.2~0.4mm正确答案:D6、在电子电路方案设计中最简单的显示平台是()。

A、OLEDB、LCDC、LEDD、数码管正确答案:C7、平移式分选机进行料盘上料时,在上料架旁的红色指示灯亮的含义是( )。

A、上料机构故障B、上料架上有料盘C、上料架上有空料盘D、上料架上没有料盘正确答案:B答案解析:平移式分选机进行料盘上料时,上料架上是否有料盘可以通过上料架旁的传感器进行检测。

当传感器指示灯为红色时,表明上料架上还有料盘,可以继续进行上料,当传感器指示灯为绿色时,表明上料架上无料盘,停止上料。

Mentor 扩展解决方案以支持 TSMC 5nm FinFET 和 7nm FinFET Plus 工艺技术

Mentor 扩展解决方案以支持TSMC 5nm FinFET 和7nm FinFET Plus 工艺技术Mentor, a Siemens business 今日宣布Mentor Calibre® nmPlatform 和Analog FastSPICE™(AFS™) Platform 获得TSMC 的7nm FinFET Plus 和最新版本的5nm FinFET 工艺的认证。

此外,Mentor 还继续扩展Xpedition™Package Designer 和Xpedition Substrate Integrator 产品的功能,以支持TSMC 的高级封装产品。

TSMC 设计基础架构营销部高级总监Suk Lee 说道:“TSMC与Mentor 展开密切合作,Mentor 为其EDA 解决方案提供了更多功能,以便支持我们的全新5nm 和7nm FinFET Plus 工艺,从而继续增加其对TSMC 生态系统的价值。

多年以来,Mentor 一直都是我们的战略合作伙伴,Siemens 将继续在Mentor 的电子设计自动化(EDA) 技术领域进行战略投资,他们正帮助双方的共同客户取得更大成功,向市场推出新一代令人惊叹的IC 创新产品。

”适用于TSMC 5nm 和7nm FinFET Plus 的Mentor Calibre nmPlatformMentor 针对TSMC 的7nm FinFET Plus 工艺和最新版本的5nm FinFET 工艺增强了Calibre nmDRC™和Calibre nmLVS™工具。

Mentor 将继续为TSMC 客户提供实现其制造要求所需的功能和性能。

Calibre nmDRC和Calibre nmLVS 工具为云就绪产品,目前已被众多客户部署在CPU 量数以千计的服务器解决方案中。

Mentor 的Caliber YieldEnhancer 工具已获得认证,可用于TSMC 的5nm 和7nm FinFET Plus 工艺。

FinFET工艺论文.

微电子前沿(4)姓名:学号:签名:微电子前沿------ FinFET技术引言:2015年,这是一个FinFET的时代,FinFET器件纷纷进入移动市场,苹果,三星,华为纷纷推出自己的使用了FinFET工艺的芯片。

在16nm以及14nm制程时代,只有FinFET工艺才能稳定发展,三星、台积电目前的14nm/16nm都极其依赖于FinFET技术。

而在2015年12月24日这一天,美国公布了9名国家科学奖获得者和8名国家技术和创新奖获得者的名单,美籍华人科学家胡正明荣获年度国家技术和创新奖,没错就是鳍式场效晶体管(FinFET)的发明者。

为什么现在FinFET能主宰微电子前沿领域,没有使用这个技术的芯片只能落后于这个时代?因为,早期的IC制程基本都是基于传统的平面型晶体管结构,平面型晶体管指的是MOSFET的源极、漏极、栅极和沟道的横截面处于同一平面上的晶体管。

虽然平面型晶体管技术发展至今已经相当的成熟,成本也日趋低廉,但随着特征尺寸的不断缩小,漏电流和短沟效应对性能的严重影响使得平面晶体管技术已达到瓶颈阶段。

而FinFET器件在抑制亚阈值电流和栅极漏电流方面有着绝对的优势,可以实现平面工艺无法达到的界限。

这样,在这个超级集成度的芯片时代,使用FinFET技术无可避免。

1FinFET概述FinFET称为鳍式场效晶体管(Fin Field-Effect Transistor;FinFET)是一种新的互补式金氧半导体(CMOS)晶体管。

Fin是鱼鳍的意思,FinFET命名根据晶体管的形状与鱼鳍的相似性。

闸长已可小于25纳米,未来预期可以进一步缩小至9纳米,约是人类头发宽度的1万分之1。

由于在这种导体技术上的突破,未来芯片设计人员可望能够将超级计算机设计成只有指甲般大小。

FinFET源自于传统标准的晶体管—场效晶体管(Field-Effect Transistor;FET)的一项创新设计。

在传统晶体管结构中,控制电流通过的闸门,只能在闸门的一侧控制电路的接通与断开,属于平面的架构。

Cadence试产14nm测试芯片

Cadence试产14nm测试芯片近日,Cadence 宣布,运用IBM FinFET 制程技术所设计的ARM Cortex-M0 处理器14nm 测试晶片已投入试产。

成功投产14nmSOI FinFET 技术归功于三家厂商携手建立的生态体系,在以FinFET 为基础的14nm 设计流程中,克服从设计到制造的各种新挑战。

14nm 生态系统与晶片是ARM、Cadence 与IBM 合作在14nm 以上的先进制程开发系统晶片(SoCs)之多年期协议的重大里程碑。

运用FinFET 技术的14nm 设计SoC 实现了大幅减少耗电的承诺。

这个晶片代表着先进制程技术的重大里程碑,这是三家公司的专家们通力协作的成果。

Cadence 益华电脑晶片实现事业群资深副总裁徐季平表示:FinFET 设计为设计社群提供了重大的优势,但也需要先进晶圆厂、IP 与EDA技术的支持,以克服可观的挑战。

Cadence、IBM 与ARM 通力合作克服了这些挑战,也为各种生产设计而发展出能够支援14nmFinFET 开发的生态系统。

这个晶片之所以开发,是为了要验证14nm 设计专属基础IP 的建构基块。

除了ARM 处理器、SRAM 记忆体区块之外,还包含了其他区块,为以FinFET 为基础的ARM Artisan 实体IP 的基础IP 开发工作提供不可或缺的特性资料。

每当SoC 往更小的面积进行设计时,就会带来新的挑战,这些挑战需要SoC 设计产业链中的领导厂商通力合作,一起来解决。

ARM 副总裁暨实体IP事业部总经理Dipesh Patel 表示:在14nm 的设计上,多数的挑战来自于FinFET 技术,而我们与Cadence 和IBM 的合作就是专注于实现14nmFinFET 技术在设计与经济成本上的可行性,克服这些挑战。

」ARM 设计工程师们运用建立在IBM 的绝缘层上覆矽(silicon-on- insulator,SOI)技术之上的14nmFinFET 技术的ARM Cortex-M0 处理器,提供。

五分钟让你看懂finfet及未来7nm制程

五分钟让你看懂 FinFET打开这一年来半导体最热门的新闻,大概就属FinFET了,例如:iPhone 6s 内新一代A9应用处理器采用新电晶体架构很可能为鳍式电晶体(FinFET),代表FinFET开始全面攻占手机处理器、三星与台积电较劲,将10 纳米 FinFET 正式纳入开发蓝图、联电携 ARM,完成 14 纳米 FinFET 制程测试。

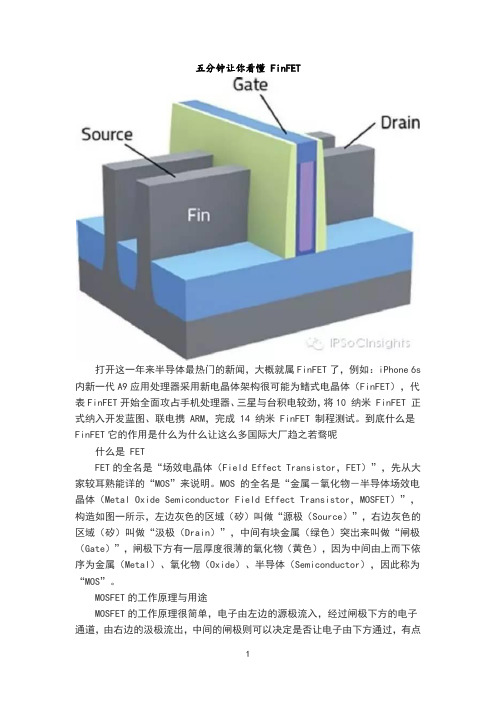

到底什么是FinFET它的作用是什么为什么让这么多国际大厂趋之若骛呢什么是 FETFET的全名是“场效电晶体(Field Effect Transistor,FET)”,先从大家较耳熟能详的“MOS”来说明。

MOS 的全名是“金属-氧化物-半导体场效电晶体(Metal Oxide Semiconductor Field Effect Transistor,MOSFET)”,构造如图一所示,左边灰色的区域(矽)叫做“源极(Source)”,右边灰色的区域(矽)叫做“汲极(Drain)”,中间有块金属(绿色)突出来叫做“闸极(Gate)”,闸极下方有一层厚度很薄的氧化物(黄色),因为中间由上而下依序为金属(Metal)、氧化物(Oxide)、半导体(Semiconductor),因此称为“MOS”。

MOSFET的工作原理与用途MOSFET的工作原理很简单,电子由左边的源极流入,经过闸极下方的电子通道,由右边的汲极流出,中间的闸极则可以决定是否让电子由下方通过,有点像是水龙头的开关一样,因此称为“闸”;电子是由源极流入,也就是电子的来源,因此称为“源”;电子是由汲极流出,看看说文解字里的介绍:汲者,引水于井也,也就是由这里取出电子,因此称为“汲”。

当闸极不加电压,电子无法导通,代表这个位是 0,如图一(a)所示;当闸极加正电压,电子可以导通,代表这个位是 1,如图一(b)所示。

MOSFET是目前半导体产业最常使用的一种场效电晶体(FET),科学家将它制作在矽晶圆上,是数码讯号的最小单位,一个 MOSFET 代表一个 0 或一个 1,就是电脑里的一个“位(bit)”。

Cadence数字与定制-模拟工具获台积电认证 合作开发FinFET新工艺

Cadence 数字与定制/模拟工具获台积电认证合作开发FinFET 新工艺美国加州圣何塞(2014 年9 月26 日)-全球知名电子设计创新领先公司Cadence 设计系统公司(NASDAQ:CDNS)今日宣布,其数字和定制/ 模拟分析工具已通过台积电公司16FF+制程的V0.9 设计参考手册(Design Rule Manual,DRM)与SPICE 认证,相比于原16 纳米FinFET 制程,可以使系统和芯片公司通过此新工艺在同等功耗下获得15%的速度提升、或者在同等速度下省电30%。

目前16FF+ V1.0 认证正在进行中,计划于2014 年11 月实现。

Cadence 也和台积电合作实施了16FF+ 制程定制设计参考流程的多处改进。

此外,Cadence 也在与TSMC 台积电合作10 纳米FinFET 制程,Cadence 的技术已经为支持早期投入10 纳米的定制设计做好准备。

Cadence 定制/模拟和数字设计实现和签收工具已获得台积电验证,客户通过高性能的参考设计流程能实现最快速的设计收敛。

通过16FF+认证的Cadence 工具包括:Encounter® 数字设计实现系统(Digital ImplementaTIon System)、Tempus™ 时序Signoff 解决方案、Voltus™ IC 电源完整性解决方案、Quantus™寄生参数提取解决方案(Quantus™ QRC ExtracTIon SoluTIon)、Virtuoso® 定制设计平台、Spectre®仿真平台、物理验证系统、Litho 物理分析仪和CMP 预报器。

Cadence物理验证系统通过FinFET制程认证

Cadence物理验证系统通过FinFET制程认证重点:-认证确保精确性方面不受影响,并包含用于65纳米至14纳米FinFET制程的物理验证签收的先进技术-双方共同的客户可通过它与CadenceVirtuoso及Encounter平台的无缝集成进行版图设计和验证版图全球电子设计创新领先企业Cadence设计系统公司今天宣布Cadence®PhysicalVerificationSystem(PVS)通过了GLOBALFOUNDRIES的认证,可用于65纳米至14纳米FinFET制程技术的定制/模拟、数字和混合信号设计物理签收。

该认证明确了CadencePVS物理验证规则文件,可以用于CadenceVirtuoso®IntegratedPhysicalVerificationSystem、CadenceEncounter&r eg;DigitalImplementationSystem及全芯片签收。

经过认证的CadencePVS规则文件,对客户充分利用Cadence模拟和数字流程中在线的物理验证,和完成全芯片物理签收都是非常重要的。

客户可以访问GLOBALFOUNDRIES客户门户global-foundryview获取PVS规则文件。

当领先的设计厂商转向这些更小的几何尺寸后,他们寻求能跟上他们不断变化需求的工具,GLOBALFOUNDRIES设计解决方案设计方法学总监RichardTrihy博士表示,明确了Cadence的PhysicalVerificationSystem能对65纳米至14纳米技术节点的支持以后,我们共同客户就能够获益于Virtuoso和Encounter流程的设计过程中在线的物理验证方法。

双方共同客户现能采用PVS作为标准,通过与CadenceVirtuoso定制IC设计平台和EncounterDigitalImplementationSystem的完美集成进行在线的设计签收,然后进行全芯片签收。

五分钟让你看懂finfet及未来7nm制程

五分钟让你看懂FinFETGate打开这一年来半导体最热门的新闻,大概就属FinFET 了,例如:iPhone6s 内新一代A9应用处理器采用新电晶体架构很可能为鳍式电晶体(FinFET),代表FinFET开始全面攻占手机处理器、三星与台积电较劲,将10纳米FinFET正式纳入开发蓝图、联电携ARM,完成14纳米FinFET制程测试。

到底什么是 FinFET 它的作用是什么为什么让这么多国际大厂趋之若骛呢什么是FETFET的全名是“场效电晶体(Field Effect Transistor,FET)”,先从大家较耳熟能详的“MOS”来说明。

MOS的全名是“金属一氧化物一半导体场效电晶体(Metal Oxide Semiconductor Field Effect Transistor, MOSFET)”,构造如图一所示,左边灰色的区域(矽)叫做“源极Source)”,右边灰色的区域(矽)叫做“汲极(Drain)”,中间有块金属(绿色)突出来叫做“闸极(Gate)”,闸极下方有一层厚度很薄的氧化物(黄色),因为中间由上而下依序为金属(Metal)、氧化物(Oxide)、半导体(Semiconductor),因此称为“MOS”。

MOSFET的工作原理与用途MOSFET的工作原理很简单,电子由左边的源极流入,经过闸极下方的电子通道,由右边的汲极流出,中间的闸极则可以决定是否让电子由下方通过,有点像是水龙头的开关一样,因此称为“闸”;电子是由源极流入,也就是电子的来 源,因此称为“源”;电子是由汲极流出,看看说文解字里的介绍:汲者,引水 于井也,也就是由这里取出电子,因此称为“汲”。

置一MOSFET 代表一恒0或一旭1 ।就是盘藤理的一周「位元[uit ) _。

当闸极不加电压,电子无法导通,代表这个位是0,如图一(a )所示;当 闸极加正电压,电子可以导通,代表这个位是1,如图一(b )所示。

MOSFET 是目前半导体产业最常使用的一种场效电晶体(FET ),科学家将它 制作在矽晶圆上,是数码讯号的最小单位,一个MOSFET 代表一个0或一个1, 就是电脑里的一个“位(bit )"。

仿生处理器是什么_a11仿生处理器能干嘛

仿生处理器是什么_a11仿生处理器能干嘛仿生处理器iPhone X 一发布就引发了世界范围的大规模关注,普通用户关注的无非就是外形和功能。

如果有一方面不如人意,那么苹果药丸的陈词滥调就甚嚣尘上。

而慧眼识英雄的用户往往不仅仅拘泥于iPhone X 所谓逼死强迫症的刘海,而是看到它外形之下低调有内涵的芯。

当然,看外观无可厚非,毕竟哎妹也是一个以貌取人的主,不过我们不妨来探究一下搭载在三款iPhone 新品上的A11 仿生芯片到底是怎样的存在。

作为处理器的组成部分,除了通讯基带,A11 的CPU 、GPU 、性能控制器、神经网络引擎、ISP 等基本都是自主研发。

自主设计的CPU 内核=六个核心=2个高性能核心+4个高效能核心,搭配第二代性能控制器,既保证运行速度,又保证续航能力。

6核A11 仿生CPU 在性能上超越自家的A10 Fusion 毫无悬念,而且无情碾压安卓旗舰芯Exynos 8895 和高通骁龙835(均由三星Galaxy S8 搭载)。

至于前几天刚刚发布的麒麟970,其提升点并不在于性能,而在于神经处理单元NPU ,所以即便搭载了麒麟970的华为Mate10 尚未发布,仍可预见在性能方面A11 仿生芯片应该也是完胜。

iPhone X 单核在Geekbench4 上跑分达到4188分,三星Galaxy S8 仅为1991分。

iPhone X 多核跑分达到10069分,远超过Galaxy Note8 和Galaxy S8 。

在GPU 上,iPhone X 弃用了之前一直使用的ImaginaTIon Technologies 公司设计的GPU 图形处理单元,而改用了自主研发的GPU 。

这款GPU 不仅在性能上较上一代GPU 提升了30%,而且针对机器学习技术,沉浸式3D 游戏和AR 都做了优化。

很多人都想知道A11 仿生芯片中的仿生是什么意思,其实就是指该芯片集成了神经网络引擎。

GPU 专注于图形显示相关的数据处理,同理神经网络引擎专注于机器学习所需的高速运算。

赛灵思16nm新品采用台积电制造技术

龙源期刊网

赛灵思16nm新品采用台积电制造技术

作者:晓文

来源:《中国电子报》2015年第13期

本报讯近日,赛灵思公司发布16nm UltraScale+系列FPGA、3D IC和MPSoC。

为实现更高的性能和集成度,UltraScale+系列还采用了全新的互联优化技术——SmartConnect。

这些新的器件进一步扩展了赛灵思的UliraScale产品系列,同时利用台积电公司的16FF+FInFET 3D

晶体管技术大幅提升了性能功耗比。

通过系统级的优化,UltraScale+提供的价值远远超过了传统工艺节点移植所带来的价值,系统级性能功耗比相比28nm器件提升了2至5倍,还实现了遥遥领先的系统集成度和智能化,以及最高级别的安全性。

新扩展的赛灵思UliraScale+FPGA系列包括赛灵思Kintex Ul-traScale+FPGA和Virtex Ultra-Scale+FPGA以及3D IC系列,而Zynq UltraScale+系列则包含业界首款全可编程MPSoC。

凭借这些新的产品组合,赛灵思能够满足各种下一代应用需求,包括LTE Ad- vanced、早期5G无线、TB级有线通信、汽车驾驶员辅助系统,以及工业物联网应用等。

据悉,针对所有UltraScale+产品系列的早期客户参与计划正在进行中。

首个流片和设计工具的早期试用版本预计将于2018年第二季度推出。

首款发货预计在2015年第四季度。

16纳米-14纳米FinFET技术:最新最前沿的电子技术

16纳米/14纳米FinFET技术:最新最前沿的电子技术FinFET 技术是电子行业的下一代前沿技术,是一种全新的新型的多门3D 晶体管。

和传统的平面型晶体管相比,FinFET 器件可以提供更显著的功耗和性能上的优势。

英特尔已经在22nm 上使用了称为三栅的FinFET 技术,同时许多晶圆厂也正在准备16 纳米或14 纳米的FinFET 工艺。

虽然该技术具有巨大的优势,但也带来了一些新的设计挑战,它的成功,将需要大量的研发和整个半导体设计生态系统的深层次合作。

FinFET 器件是场效应晶体管(FET),名字的由来是因为晶体管的栅极环绕着晶体管的高架通道,这称之为鳍。

比起平面晶体管,这种方法提供了更多的控制电流,并且同时降低漏电和动态功耗。

比起28 纳米工艺,16 纳米/14 纳米FinFET 器件的进程可以提高40-50%性能,或减少50%的功耗。

一些晶圆厂会直接在16 纳米/14 纳米上采用FinFET 技术,而一些晶圆厂为了更容易地整合FinFET 技术,会在高层金属上保持在20nm 的工艺。

那么20 纳米的平面型晶体管还有市场价值么?这是一个很好的问题,就在此时,在2013 年初,20nm 的平面型晶体管技术将会全面投入生产而16 纳米/14 纳米FinFET 器件的量产还需要一到两年,并且还有许多关于FinFET 器件的成本和收益的未知变数。

但是随着时间的推移,特别是伴随着下一代移动消费电子设备发展,我们有理由更加期待FinFET 技术。

和其他新技术一样,FinFET 器件设计也提出了一些挑战,特别是对于定制/模拟设计。

一个挑战被称为宽度量化,它是因为FinFET 元件最好是作为常规结构放置在一个网格。

标准单元设计人员可以更改的平面晶体管的宽度,但不能改变鳍的高度或宽度的,所以最好的方式是提高驱动器的强度和增加鳍的个数。

增加的个数必须为整数- 你不能添加四分之三的鳍。

中芯国际采用Cadence公司 DFM 和低功耗硅技术

中芯国际采用Cadence公司DFM 和低功耗硅技术 全球电子设计创新领先企业Cadence设计系统公司,今天宣布中国最大的半导体晶圆厂中芯国际集成电路制造有限公司,已经将Cadence® Silicon Realization产品作为其65纳米参考流程4.1版本(Reference Flow 4.1)可制造性设计(DFM)以及低功耗技术的核心。

以Cadence Encounter Digital Implementation System为基础,两家公司合作为65纳米系统级芯片(SoC)设计提供了一个完整的端到端的Silicon Realization流程。

经过严格评估,中芯国际选择了Cadence Silicon Realization产品,基于其强大的层次化流程(hierarchical flow),应用于大规模和高质量的设计。

中芯国际认为此紧凑结合了功能性、物理和电气领域的整合流程,可用于评估、逻辑设计、验证、物理实现与设计内签收,并大大提高设计师的效率、易用性,及获得更具确定性的结果(deterministic results)。

中芯国际流程中包含的Cadence Silicon Realization技术包括Incisive® Enterprise Simulator、Encounter® RTL Compiler、Encounter Test、Encounter Conformal® Low Power、Encounter Conformal Equivalence Checker、Encounter Digital Implementation System、QRC Extraction、Encounter Timing System、Encounter Power System、Litho Physical Analyzer、Litho Electrical Analyzer、Cadence CMP Predictor 和Assura® Physical Verification。

Apple Pay

iPhone 6 和Apple Watch 发布会上,苹果还正式公布了Apple Pay 移动支付服务。

Apple Pay 也将成为苹果替代钱包计划的第一步,这项服务被描述为“简单、安全和隐私”。

Apple Pay 包含各种不同的功能,能比传统信用卡更安全,包括设备账户码取代信用卡号,动态安全码实现支付以及使用Touch ID 实现生物支付验证系统。

TUAW 网站的Yoni Heisler 详细研究了Apple Pay 支付服务背后的安全功能。

虽然Apple Pay 服务基于NFC 技术,但Heisler 的研究显示,Apple Pay 是第一个完成EMVCo 令牌标准的服务,这是一种全新的安全框架,设计的目的就是帮助新兴支付。

根据前任信用卡高管Tim Noyes,这种标准是“世界上最安全的支付解决方案”。

就像之前传言的一样,Apple Pay 使用“令牌”技术,苹果将这种技术称为设备账户码,用来取代用户已经拥有的信用卡账户。

设备账户码时随机的16位数字,这也确保了商家无法获得用户信用卡号,保护消费者不受侵害。

根据TUAW 的研究,随机码无法被破解,与信用卡号没有联系。

设备账户码,或者说是令牌可以动态生成,使用一次后立刻作废。

设备账户码用来替代信用卡的CVV 码。

设备账户码没有一次性密码电文时不能进行交易,密码电文验证令牌码,还包含了交易信息,比如商家的身份和收取的金额。

随后,通过设备验证码和协同密码电文后,交易还需要通过Touch ID 验证,Touch ID 在Apple Pay 交易时扮演了密码和PiN 码的角色。

根据信用卡高管,苹果提供的Apple Pay 提供了更安全标准更高的电子支付体验。

Apple Pay 服务将于10月正式上线,iOS 8.1 将提供相关支持。

目前,iOS 8.1 测试版已经发布。

在宣布将以16nm FinFET制程技术量产ARM 64位处理器后,台积电再进一步与ARM携手宣布,未来将透过10nm FinFET制程技术制作64位架构ARMv8-A 处理器,预计最快在2015年第四季启用此项技术,届时将可支持各客户采用10nm FinFET 制程技术完成64位ARM架构处理器的设计定案。

如何将电源完整性分析与签核的速度提高10倍?

如何将电源完整性分析与签核的速度提高10倍?

在移动计算时代,片上系统(SoC)的设计已经变得更为复杂,因为在设计过程中面临着诸多挑战,如需遵循针对高级流程节点的复杂设计规则,需采用低功率电路设计技术,并放大电路的尺寸。

电源完整性是设计方案能被成功签核的关键因素之一。

本文介绍了一种新的工具,与其他现有技术相比较,它不仅能将电源完整性分析与签核的速度提高10倍,同时还能达到类似于集成电路通用模拟程序(SPICE)的准确度。

该工具将一套完整的设计实现和签核工具整合到一起,以便更好地克服在签核过程中遇到的挑战,从而实现业内最快的设计收敛流程。

简介

为了满足移动计算的各种要求,片上系统的设计变得越来越复杂。

随着消费者开始青睐更小巧、性能更好、电池续航时间更长的设备,设备中所使用的芯片必须能提供更丰富的功能,更低的能耗以及更小的尺寸。

对设计工程师来说,这些变化意味着他们在设计过程中必须运用先进的电源技术(例如电源控制开关)、增加知识产权的内容和功能(例如模拟/混合信号宏指令)以及减少设计裕度(例如电源电压小于1V)。

另一方面,产品上市周期变得越来越短,因此在设计周期的最后阶段,电源签核对成功将设计方案送交制造来说至关重要。

FinFET工艺论文

微电子前沿(4)姓名:学号:签名:微电子前沿------ FinFET技术引言:2015年,这是一个FinFET的时代,FinFET器件纷纷进入移动市场,苹果,三星,华为纷纷推出自己的使用了FinFET工艺的芯片。

在16nm以及14nm制程时代,只有FinFET工艺才能稳定发展,三星、台积电目前的14nm/16nm都极其依赖于FinFET技术。

而在2015年12月24日这一天,美国公布了9名国家科学奖获得者和8名国家技术和创新奖获得者的名单,美籍华人科学家胡正明荣获年度国家技术和创新奖,没错就是鳍式场效晶体管(FinFET)的发明者。

为什么现在FinFET能主宰微电子前沿领域,没有使用这个技术的芯片只能落后于这个时代?因为,早期的IC制程基本都是基于传统的平面型晶体管结构,平面型晶体管指的是MOSFET的源极、漏极、栅极和沟道的横截面处于同一平面上的晶体管。

虽然平面型晶体管技术发展至今已经相当的成熟,成本也日趋低廉,但随着特征尺寸的不断缩小,漏电流和短沟效应对性能的严重影响使得平面晶体管技术已达到瓶颈阶段。

而FinFET器件在抑制亚阈值电流和栅极漏电流方面有着绝对的优势,可以实现平面工艺无法达到的界限。

这样,在这个超级集成度的芯片时代,使用FinFET技术无可避免。

1FinFET概述FinFET称为鳍式场效晶体管(Fin Field-Effect Transistor;FinFET)是一种新的互补式金氧半导体(CMOS)晶体管。

Fin是鱼鳍的意思,FinFET命名根据晶体管的形状与鱼鳍的相似性。

闸长已可小于25纳米,未来预期可以进一步缩小至9纳米,约是人类头发宽度的1万分之1。

由于在这种导体技术上的突破,未来芯片设计人员可望能够将超级计算机设计成只有指甲般大小。

FinFET源自于传统标准的晶体管—场效晶体管(Field-Effect Transistor;FET)的一项创新设计。

在传统晶体管结构中,控制电流通过的闸门,只能在闸门的一侧控制电路的接通与断开,属于平面的架构。

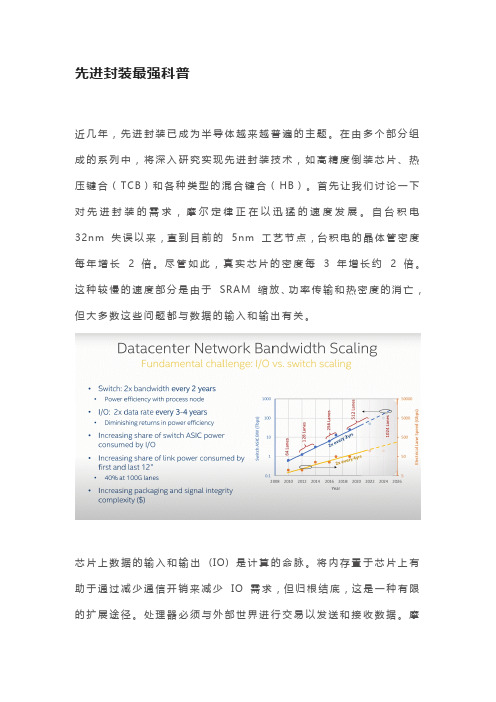

先进封装最强科普

先进封装最强科普近几年,先进封装已成为半导体越来越普遍的主题。

在由多个部分组成的系列中,将深入研究实现先进封装技术,如高精度倒装芯片、热压键合(TCB)和各种类型的混合键合(HB)。

首先让我们讨论一下对先进封装的需求,摩尔定律正在以迅猛的速度发展。

自台积电32nm 失误以来,直到目前的5nm 工艺节点,台积电的晶体管密度每年增长 2 倍。

尽管如此,真实芯片的密度每 3 年增长约 2 倍。

这种较慢的速度部分是由于SRAM 缩放、功率传输和热密度的消亡,但大多数这些问题都与数据的输入和输出有关。

芯片上数据的输入和输出(IO) 是计算的命脉。

将内存置于芯片上有助于通过减少通信开销来减少IO 需求,但归根结底,这是一种有限的扩展途径。

处理器必须与外部世界进行交易以发送和接收数据。

摩尔定律使业界的晶体管密度大约每 2 年增加 2 倍,但IO 数据的速率每 4 年才增加 2 倍。

几十年来,晶体管密度与IO 数据速率的这种差异出现了巨大差异。

共同封装的光学器件只是解决这个问题的一种方法,它并不是单独出现的。

从根本上说,芯片需要容纳更多的通信或IO 点才能跟上。

不幸的是,这方面的最后一个主要步骤功能增加是在90 年代转向倒装芯片封装。

传统的倒装芯片封装的凸点间距在150 微米到200 微米之间。

这意味着每个IO 单元在裸片的底侧相距150 到200 微米。

台积电N7将凸点间距降低到130 微米,英特尔的10nm 将凸点间距降低到100 微米,这些进步被称为细间距倒装芯片。

不要小看这些进步,因为它们极大地促进了更好的处理器,但2000 年的封装技术与2021 年的封装技术基本相同。

2000年的250mm²的芯片与2022年的250mm²芯片在晶体管数量、性能和成本方面有着难以置信的不同。

摩尔定律每 2 年翻一番,表示晶体管数量增加了2000 倍以上。

显然,现实并不那么有利,但晶体管仍然增加了几个数量级。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Cadence 设计工具通过台积电16nm FinFET 制程认

证

益华电脑(Cadence Design Systems)宣布,该公司的系统芯片开发

工具已经通过台积电(TSMC)16 纳米FinFET 制程的设计参考手册(design rule manual,DRM)第0.1 版与SPICE 模型工具认证。

在早期阶段

就达成工具认证里程碑,意味着先进制程客户能够着手开发设计,并驾驭新

一代行动平台所需的低功耗与高效能优势。

工具认证扮演16 纳米FinFET 技术专属设计基础架构的基石角色。

通过认证的Cadence 工具包括:Spectre、Liberate、Virtuoso、Encounter Digital ImplementaTIon (EDI)System、Encounter TIming System、Virtuoso Power System、Encounter Power System、Physical VerificaTIon System 以及QRC ExtracTIon。

还有几项Cadence 设计IP 产品可供客户在这个先进制程测

试芯片。

此外,台积电已经认证立即可以投入生产的Cadence 益华电脑20 纳

米制程专属设计流程。

客户现在可以享用Cadence 益华电脑流程为先进制程

所提供的速度、功耗与面积优势。

整个工具链已经透过ARM Cortex-A9 处理器的设计通过了20 纳米认。