数字频率合成器

射频前端设计中的频率合成器调节方法

射频前端设计中的频率合成器调节方法在射频前端设计中,频率合成器是非常重要的部件,它负责产生稳定的输出信号以满足系统的频率要求。

频率合成器的调节方法对于整个系统的性能和稳定性都至关重要。

下面将介绍几种常见的频率合成器调节方法。

1. 直接数字频率合成器(Direct Digital Synthesizer,DDS):DDS是一种采用数字方式直接合成频率的技术,具有快速调节、低相位噪声和高频率分辨率等优点。

通过控制DDS的相位累加器和频率控制字,可以实现对频率的精确调节。

DDS在射频前端设计中应用广泛,特别是在需要频率快速切换和精确控制的应用中。

2. 锁相环(Phase Locked Loop,PLL):PLL是一种经典的频率合成器调节方法,通过比较参考信号和反馈信号的相位差来调节输出频率,从而实现频率的稳定。

PLL在射频前端设计中常用于产生稳定的局部振荡频率或时钟信号,特别是在无线通信系统中广泛应用。

3. 频率合成器电路的调谐器:频率合成器电路的调谐器可以通过改变电路中的电感或电容来调节输出频率。

调谐器一般采用电容二极管或压控振荡器(Voltage Controlled Oscillator,VCO)来实现频率的调节,通过改变电压或电流来改变频率。

调谐器的优点是调节范围大、响应速度快,适用于一些频率跨度比较大的应用。

4. 数字控制的晶体振荡器(Digitally Controlled Crystal Oscillator,DCXO):DCXO是一种结合了晶体振荡器和数字控制技术的频率合成器调节方法。

通过控制DCXO内部的数字逻辑电路,可以实现对晶体振荡器的频率调节,提高了频率稳定性和精度。

DCXO广泛应用于高性能无线通信系统和频谱分析仪等领域。

总的来说,对于射频前端设计中的频率合成器调节方法,选择合适的调节方式对系统性能至关重要。

不同的应用场景需要选择合适的调节方法,根据频率要求、调节范围、稳定性和成本等因素进行综合考虑。

基于FPGA平台的数字频率合成器的设计和实现

基于FPGA平台的数字频率合成器的设计和实现数字频率合成技术是一种实现高精度频率合成的方法,具有广泛应用价值。

在数字频率合成中,FPGA是一种非常重要的平台,能够实现高速、高精度、可编程的数字频率合成。

本文将介绍基于FPGA平台的数字频率合成器的设计和实现。

一、FPGA简介FPGA是一种可以编程的数字集成电路,具有非常灵活的可编程性。

FPGA中包含了大量的逻辑单元、存储单元和输入输出接口,可以通过编程实现各种数字电路功能。

FPGA具有高速、高度集成、低功耗等优点,在数字电路的设计和实现中得到了广泛应用。

二、数字频率合成的基本原理数字频率合成是通过一组特定的频率合成器和相位加法器来合成所需要的频率。

首先,将参考频率和相位加法器连接起来,形成一个频率合成器。

然后,将输出频率与参考频率的比例进行数字控制,并将输出频率的相位与参考频率相位进行加法计算,最终输出要求的频率。

三、数字频率合成器的设计1. 参考频率生成模块参考频率生成模块是数字频率合成器的核心模块。

参考频率一般使用晶振作为输入信号,并通过频率除和锁相环等技术来产生高精度的参考频率。

在FPGA中,可以使用PLL、DCM等IP核来实现参考频率的生成。

2. 分频器分频器是将参考频率转化为所需的输出频率的模块,一般使用计数器实现。

在FPGA中,可以使用计数器IP核或使用Verilog等HDL语言来实现。

3. 相位加法器相位加法器用于将输出频率的相位和参考频率的相位相加。

在FPGA中,可以使用LUT(查找表)实现相位加法器。

4. 控制单元控制单元用于控制数字频率合成器的各个模块,并实现与外部设备的接口。

在FPGA中,可以使用微处理器或FPGA内部逻辑来实现控制单元。

四、数字频率合成器的实现数字频率合成器的实现需要进行数字电路设计和FPGA编程。

一般来说,可以采用Verilog或VHDL等硬件描述语言进行FPGA编程,实现各个模块的功能。

数字电路设计过程中,需要考虑到功耗、面积和时序等问题,同时需要进行仿真和验证。

直接数字频率合成器原理

直接数字频率合成器原理直接数字频率合成器(Direct Digital Frequency Synthesizer,简称DDFS)是一种用于产生高精度、稳定的频率信号的电子设备。

它通过数字电路实现频率的直接合成,可以产生任意频率的信号,并且具有快速调谐、高精度以及低相位噪声等优点。

本文将介绍DDFS的工作原理及其在实际应用中的重要性。

一、工作原理DDFS的核心组成部分是相位累加器(Phase Accumulator)、频率控制字(Frequency Control Word)和查表器(Look-up Table)。

相位累加器通过不断累加频率控制字的值,从而产生一个随时间线性增加的相位值。

查表器中存储了正弦波的采样值,通过查表器可以根据相位值得到对应的正弦波样本。

最后,通过数模转换器将数字信号转换为模拟信号输出。

具体来说,DDFS的工作原理如下:1. 频率控制字:频率控制字是一个二进制数,用于控制相位累加器的累加速度。

频率控制字的大小决定了相位累加器每个时钟周期累加的值,从而决定了输出信号的频率。

2. 相位累加器:相位累加器是一个寄存器,用于存储当前的相位值。

相位累加器的值会在每个时钟周期根据频率控制字的大小进行累加。

相位累加器的位数决定了相位的分辨率,位数越多,相位分辨率越高,输出信号的频率分辨率也越高。

3. 查表器:查表器中存储了一个周期内的正弦波样本值(或余弦波样本值),通过查表器可以根据相位累加器的值得到对应的正弦波样本值。

4. 数模转换器:数模转换器将数字信号转换为模拟信号输出。

通常使用的是高速数模转换器,能够将数字信号以高速率转换为模拟信号输出。

二、应用领域DDFS在许多领域中都有广泛的应用,其中包括通信、雷达、测量、音频处理等。

1. 通信领域:在通信系统中,DDFS被广泛应用于频率合成器、频率调制器和频率解调器等模块中。

通过DDFS可以快速、精确地合成所需的信号频率,实现高速数据传输和频谱分析等功能。

第4章数字频率合成器的设计讲解

第 4 章数字频率合成器的设计随着通信、雷达、宇航和遥控遥测技术的不断发展,对频率源的频率稳定度、频谱纯度、频率范围和输出频率的个数提出越来越高的要求。

为了提高频率稳定度,经常采用晶体振荡器等方法来解决,但它不能满足频率个数多的要求,因此,目前大量采用频率合成技术。

频率合成是通信、测量系统中常用的一种技术,它是将一个或若干个高稳定度和高准确度的参考频率经过各种处理技术生成具有同样稳定度和准确度的大量离散频率的技术。

频率合成的方法很多,可分为直接式频率合成器、间接式频率合成器、直接式数字频率合成器( DDS) 。

直接合成法是通过倍频器、分频器、混频器对频率进行加、减、乘、除运算,得到各种所需频率。

该方法频率转换时间快(小于100ns),但是体积大、功耗大,目前已基本不被采用。

锁相式频率合成器是利用锁相环( PLL )的窄带跟踪特性来得到不同的频率。

该方法结构简化、便于集成,且频谱纯度高,目前使用比较广泛。

直接数字频率合成器(Direct Digital Frequency Synthesis简称:DDS)是一种全数字化的频率合成器,由相位累加器、波形ROM,D/A 转换器和低通滤波器构成, DDS 技术是一种新的频率合成方法, 它具有频率分辨率高、频率切换速度快、频率切换时相位连续、输出相位噪声低和可以产生任意波形等优点。

但合成信号频率较低、频谱不纯、输出杂散等。

这里将重点研究锁相式频率合成器。

本章采用锁相环, 进行频率合成器的设计与制作4.1设计任务与要求1.设计任务:利用锁相环,进行频率合成器的设计与制作2.设计指标:(1)要求频率合成器输出的频率范围f0为1kHz〜99kHz;(2)频率间隔f为1kHz;(3)基准频率采用晶体振荡频率,要求用数字电路设计,频率稳定度应优于10一4;(4)数字显示频率;(5)频率调节采用计数方式。

3•设计要求:(1)要求设计出数字锁相式频率合成器的完整电路。

(2)数字锁相式频率合成器的各部分参数计算和器件选择。

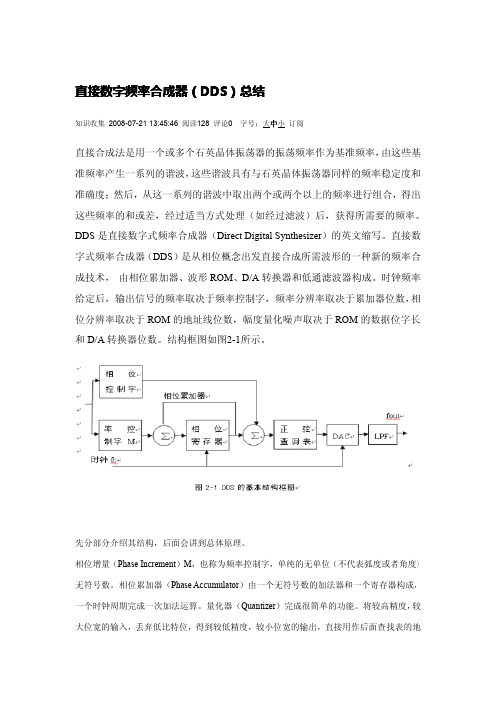

直接数字频率合成器(DDS)总结

直接数字频率合成器(直接数字频率合成器(DDS DDS DDS)总结)总结知识收集2008-07-2113:45:46阅读128评论0字号:大中小订阅直接合成法是用一个或多个石英晶体振荡器的振荡频率作为基准频率,由这些基准频率产生一系列的谐波,这些谐波具有与石英晶体振荡器同样的频率稳定度和准确度;然后,从这一系列的谐波中取出两个或两个以上的频率进行组合,得出这些频率的和或差,经过适当方式处理(如经过滤波)后,获得所需要的频率。

DDS 是直接数字式频率合成器(Direct Digital Synthesizer )的英文缩写。

直接数字式频率合成器(DDS )是从相位概念出发直接合成所需波形的一种新的频率合成技术,由相位累加器、波形ROM 、D/A 转换器和低通滤波器构成。

时钟频率给定后,输出信号的频率取决于频率控制字,频率分辨率取决于累加器位数,相位分辨率取决于ROM 的地址线位数,幅度量化噪声取决于ROM 的数据位字长和D/A 转换器位数。

结构框图如图2-1所示。

先分部分介绍其结构,后面会讲到总体原理。

相位增量(Phase Increment )M ,也称为频率控制字,单纯的无单位(不代表弧度或者角度)无符号数。

相位累加器(Phase Accumulator )由一个无符号数的加法器和一个寄存器构成,一个时钟周期完成一次加法运算。

量化器(Quantizer )完成很简单的功能。

将较高精度,较大位宽的输入,丢弃低比特位,得到较低精度,较小位宽的输出,直接用作后面查找表的地址。

正余弦查找表(Sine/Cosine Lookup Table)存放正余弦数值。

DDS的工作原理:DDS的基本原理是利用采样定理,通过查表法产生波形[2]。

由于,(2-1)其中Δθ为一个采样间隔ΔT之间的相位增量,采样周期,即:(2-2)控制Δθ就可以控制不同的频率输出。

Δθ是由频率控制字M控制的,即:(2-3)所以改变M就可以得到不同的输出频率。

数字频率合成器设计实例

数字频率合成器设计实例数字频率合成器设计实例数字频率合成器(Digital Frequency Synthesizer)是一种能够产生不同频率信号的设备。

它通过使用数字技术和数学算法来合成所需的频率,具有高精度和稳定性。

在本文中,我们将逐步介绍数字频率合成器的设计过程。

1. 设定所需频率范围:首先,确定所需合成的频率范围。

这取决于具体应用,例如音频处理、无线通信等。

假设我们的频率范围为1Hz到10kHz。

2. 确定采样率:采样率是指每秒钟对信号进行采样的次数。

根据香农抽样定理,采样率应大于信号最高频率的两倍。

在我们的例子中,最高频率为10kHz,因此选择采样率为至少20kHz。

3. 选择数字信号处理器(DSP):为了实现数字频率合成器,我们需要选择一种适合的DSP芯片。

DSP芯片能够高效地执行数字信号处理任务,例如信号生成和滤波。

选择一款性能强大且易于编程的DSP 芯片,以满足所需的合成要求。

4. 设计频率控制模块:频率控制模块是数字频率合成器的核心部分,用于生成所需频率的数字信号。

它通常由相位锁定环(PLL)和数字控制振荡器(NCO)组成。

a. 相位锁定环(PLL):PLL是一种控制系统,通过比较输入信号的相位和参考信号的相位差异来产生所需频率的输出信号。

通过调整参考信号的频率和相位,PLL可以实现精确的频率合成。

b. 数字控制振荡器(NCO):NCO是一种可编程振荡器,能够生成具有可变频率的数字信号。

通过调整输入的控制参数,NCO能够实现不同频率的信号合成。

5. 编程实现:根据DSP芯片的编程手册和软件开发工具,编写相应的代码实现频率控制模块。

通过配置PLL和NCO的参数,以及设置合适的参考信号,实现所需频率的合成。

6. 验证和调试:使用示波器或频谱分析仪等测试工具,验证合成的频率是否符合要求。

如果发现频率偏差或其他问题,可以通过调整PLL和NCO的参数来进行调试和校准。

7. 优化和改进:根据实际应用需求和反馈,对数字频率合成器进行优化和改进。

数字频率合成器的技术方案

数字频率合成器的技术方案在这个数字化的时代,频率合成技术已成为电子系统中的关键组成部分。

今天,我就来和大家分享一下关于数字频率合成器的技术方案,希望能为各位提供一个全新的视角。

一、方案背景频率合成器是一种能够产生多种频率信号的设备,广泛应用于通信、雷达、导航、仪器测量等领域。

随着数字信号处理技术的发展,数字频率合成器逐渐成为主流。

相比模拟频率合成器,数字频率合成器具有更高的频率精度、更低的相位噪声和更宽的频率范围。

二、技术方案1.基本原理数字频率合成器基于数字信号处理技术,通过数字信号处理器(DSP)对数字信号进行运算和处理,所需的频率信号。

其主要原理如下:(1)采用相位累加器(PhaseAccumulator)对输入的参考时钟信号进行累加,得到一个线性增长的相位值。

(2)将相位值映射到正弦波查找表(SinLookupTable),得到对应的正弦波采样值。

(3)通过数字到模拟转换器(DAC)将数字信号转换为模拟信号,再经过低通滤波器(LPF)滤波,得到平滑的正弦波信号。

2.关键技术(1)相位累加器相位累加器是数字频率合成器的核心部件,其性能直接影响到合成器的频率精度和相位噪声。

我们采用高性能的FPGA器件实现相位累加器,确保高速运算和低功耗。

(2)正弦波查找表正弦波查找表用于存储正弦波采样值,其大小和精度决定了合成器的频率分辨率和幅度精度。

我们采用16位精度,存储1024个采样点,以满足高精度需求。

(3)数字到模拟转换器(DAC)DAC将数字信号转换为模拟信号,其性能影响到合成器的输出信号质量。

我们选用高性能的DAC芯片,具有14位精度和500MHz的转换速率。

(4)低通滤波器(LPF)低通滤波器用于滤除DAC输出信号中的高频噪声,保证输出信号的平滑。

我们设计了一个4阶椭圆函数低通滤波器,具有-60dBc的带外抑制能力和50MHz的截止频率。

3.系统架构数字频率合成器系统架构如下:(1)输入接口:接收外部参考时钟信号和频率控制信号。

用于数字频率合成器的nco实现与优化

用于数字频率合成器的nco实现与优化数字频率合成器(DFC)是一种可以精确控制信号和信息的设备,是构建数字电路的核心组件,在时钟电路、移相电路、调频电路和信号合成领域有着广泛应用。

要想达到这些目的,必须实现一种能够精确控制正弦波频率和幅度的设备,用于在给定情况下生成特定频率正弦波。

这就是NCO(数字控制频率)发挥作用的原因。

NCO可以被视为一个频率发生器,用来控制正弦波频率,它能够准确地产生频率为n的正弦波,使用累加器实现循环操作,最大的优点是可以用于各种电路,并且可以提供很高的精度。

NCO在数字频率合成器中的实现有多种形式,如基于DSM和DDS,这些实现有不同的优缺点。

DSM(数字混频器),它是一种高速数字混频器,能够精确产生正弦波,精度比DDS(数字直接频率合成器)高,但在实现中会存在噪声。

DDS(数字直接频率合成器),它是一种高精度的数字频率合成器,能够高效的产生不同的频率正弦波,在系统提供的时钟频率范围内可以提供任意的频率。

NCO在实现过程中,有多种优化方法可以用于提高效率,降低噪声,提高精度和稳定性。

首先,使用可变步长算法来改善结构的效率,其次,使用更高精度的累加器,以及更高的时钟频率,以便提高计算精度,还可以使用调制器和高级算法来减少噪声和干扰,保证信号的质量。

此外,使用可编程逻辑模块进行NCO实施将有助于进一步提升系统性能。

NCO在数字频率合成器中的实现具有重要意义,它是用于实施整个系统的核心组件。

针对其实现,可以采取多种优化策略,比如改善结构效率、提高精度和稳定性、减少噪声和干扰等,从而使系统更加高效。

最后,使用可编程的逻辑模块来进行实施,更有利于提升系统的整体性能和可靠性。

总之,NCO是数字频率合成器的核心组件,它能够精确控制正弦波的频率和幅度,因此它在各个领域都有着非常重要的应用。

实现NCO的过程中,可以采取多种优化策略,以便提高系统性能,使系统更加完善和可靠。

FPGA技术-直接数字频率合成器

COMPONENT REG32B PORT ( LOAD : IN STD_LOGIC; DIN : IN STD_LOGIC_VECTOR(31 DOWNTO 0); DOUT : OUT STD_LOGIC_VECTOR(31 DOWNTO 0) );

END COMPONENT; COMPONENT REG10B

接下页

PORT ( LOAD : IN STD_LOGIC;

DIN : IN STD_LOGIC_VECTOR(9 DOWNTO 0);

DOUT : OUT STD_LOGIC_VECTOR(9 DOWNTO 0) );

END COMPONENT;

COMPONENT ADDER32B

PORT ( A : IN STD_LOGIC_VECTOR(31 DOWNTO 0);

B : IN STD_LOGIC_VECTOR(31 DOWNTO 0);

S : OUT STD_LOGIC_VECTOR(31 DOWNTO 0) );

END COMPONENT;

COMPONENT SIN_ROM

PORT ( address : IN STD_LOGIC_VECTOR(9 DOWNTO 0);

inclock

: IN STD_LOGIC ;

接下页

q

: OUT STD_LOGIC_VECTOR(9 DOWNTO 0) );

END COMPONENT;

SIGNAL F32B,D32B,DIN32B : STD_LOGIC_VECTOR(31 DOWNTO 0);

为了对进行数字量化,把切割成2N份,由此每个clk周期的 相 为整数

数字频率合成器原理

数字频率合成器原理

数字频率合成器(DigitalFrequencySynthesizer)是一种电子设备,用于产生高精度和可调节的频率信号。

其原理基于数字信号处理技术和参考时钟信号。

数字频率合成器的工作原理如下:

1.参考时钟:数字频率合成器首先接收一个高精度稳定的参考时钟信号,通常是一个晶体振荡器提供的恒定频率信号。

这个参考时钟作为系统的时基。

2.相位积累器:参考时钟信号经过相位积累器,对其相位进行连续的积累。

相位积累器根据所需输出频率的要求,按照一定的步进值或相位增量来累加相位。

每个时钟周期,相位积累器的相位都会根据步进值逐渐增加,并形成一个随时间线性增长的相位。

3.相位加法器:相位积累器的输出与一个可编程的相位加法器进行相位叠加。

该相位加法器接收用户输入的频率控制字(FrequencyControlWord),用于设定所需频率的分辨率和范围。

在每个时钟周期中,相位加法器将相位积累器的输出相位与频率控制字相加,得到一个新的相位。

4.数字到模拟转换器(DAC):经过相位加法器得到的新相位被输

入到数字到模拟转换器中,将其转换为连续的模拟信号。

这个模拟信号的频率由相位积累器的输出相位和频率控制字来决定。

5.滤波器:通过一个低通滤波器对模拟信号进行滤波,去除高频噪声,得到所需频率信号的纯净输出。

滤波后的信号即为数字频率合成器的输出信号。

由于数字频率合成器采用数字信号处理技术,可以精确控制输出频率,并具有较低的抖动和相位噪声。

它在电子通信、射频信号生成、音频合成等领域有广泛应用。

直接数字频率合成器(DDS)介绍

累加器的工作示意图

设相位累加器的位宽为2 设相位累加器的位宽为 N, Sin表的大小为 表的大小为 2p,累加器的高 位用于寻址 表。 累加器的高P位用于寻址 位用于寻址Sin表 时钟Clock的频率为 c, 若累加器按步进为 地累 的频率为f 时钟 的频率为 , 若累加器按步进为1地累 加直至溢出一遍的频率为

AD9830

芯片特性: 芯片特性:

+5V电压供电 电压供电 50MHz频率 频率 片内正弦查询表 片内10位数模转 片内 位数模转 换器 并行数据接口 掉电功能选择 250mW功耗 功耗 48引脚薄方扁封 引脚薄方扁封 装(TQFP) )

DDS的信号质量分析 的信号质量分析

取样系统信号的频谱

镜像频率分量为-60dB,而其他各种杂散分量 镜像频率分量为- , 分布在很宽的频带上,其幅值远小于镜像频率分量。 分布在很宽的频带上,其幅值远小于镜像频率分量。 D/A之后用的低通滤波器可用来滤去镜像频率分量, 之后用的低通滤波器可用来滤去镜像频率分量, 之后用的低通滤波器可用来滤去镜像频率分量 谐波分量和带外杂散分量。第一个镜像频率分量 谐波分量和带外杂散分量。 最靠近信号频率,且幅度最大,实际应用时, 最靠近信号频率,且幅度最大,实际应用时, 应尽量提高采样时钟频率, 应尽量提高采样时钟频率,使该分量远离低通 滤波器的带宽,以减少低通滤波器的制作难度 以减少低通滤波器的制作难度。 滤波器的带宽 以减少低通滤波器的制作难度。

DDS的信号质量分析 的信号质量分析

DDS信号源的性能指标: 信号源的 1、 频率稳定度,等同于其时钟信号的稳定度。 等同于其时钟信号的稳定度。 2、 频率的值的精度,决定于 决定于DDS的相位分辨率。即由 的相位分辨率。 的相位分辨率 DDS的相位累加器的字宽和 的相位累加器的字宽和ROM函数表决定。如果要 函数表决定。 的相位累加器的字宽和 函数表决定 求频率按10Hz步进,频率值的误差应远小于 步进,频率值的误差应远小于10Hz。 求频率按 步进 。 DDS可达到很高的频率分辨率。 可达到很高的频率分辨率。 可达到很高的频率分辨率 3、 失真与杂波,可用输出频率的正弦波能量与其他各 失真与杂波, 种频率成分的比值来描述。 种频率成分的比值来描述。

实现直接数字频率合成器的种技术方案

实现直接数字频率合成器的种技术方案嘿,小伙伴们,今天我来和大家聊聊如何实现一款牛气冲天的直接数字频率合成器(DDS)。

这可是电子领域里的一大神器,不仅能实现高速频率转换,还能精确控制输出波形,简直是实验室和工业界的宠儿。

下面,我就用我那十年磨一剑的经验,给大家带来一份实操性强的技术方案。

我们要明确DDS的核心原理。

DDS的核心在于一个叫做相位累加器的家伙,它通过不断地累加相位,来控制数字到模拟转换器(DAC)的输出,从而实现频率合成。

那么,我们就来一步步打造这款神奇的DDS。

一、硬件设计1.1选用合适的FPGA芯片FPGA是DDS的核心,负责实现相位累加、正弦查找表、DAC输出等功能。

我们要根据项目需求,选择合适型号的FPGA芯片。

这里我推荐使用Xilinx或Altera的高端FPGA,它们具有丰富的逻辑资源和高速DAC接口,能够满足DDS的高性能要求。

1.2设计数字下变频器数字下变频器是DDS的关键部分,它负责将高频信号转换为低频信号。

我们可以采用数字滤波器来实现这一功能。

在设计过程中,要注意滤波器的类型、阶数和截止频率等参数,以确保信号转换的准确性和稳定性。

1.3设计DAC输出电路DAC输出电路负责将数字信号转换为模拟信号。

这里我们可以选择串行或并行DAC,根据FPGA的接口和性能要求来确定。

同时,要设计合适的驱动电路,确保DAC输出信号的幅度和波形。

二、软件设计2.1相位累加器设计相位累加器是DDS的核心,它决定了输出频率的精度。

在设计相位累加器时,要注意字长和累加速率,以满足频率分辨率和转换速度的要求。

2.2正弦查找表设计正弦查找表是DDS的关键部分,它用于查找正弦波的采样值。

在设计查找表时,要考虑查找表的深度和宽度,以确保输出波形的精度。

2.3数字滤波器设计数字滤波器是数字下变频器的核心,它决定了信号转换的准确性和稳定性。

在设计滤波器时,要选择合适的滤波器类型、阶数和截止频率等参数。

2.4控制界面设计控制界面是用户与DDS交互的桥梁,它负责接收用户输入的频率、幅度等参数,并控制FPGA实现相应的功能。

DDS基本原理及技术指南

DDS基本原理及技术指南DDS是直接数字频率合成器(Direct Digital Synthesizer)的简称,是一种使用数字技术合成连续可变频率输出信号的设备。

DDS技术已经广泛应用在各种通信、测量和控制领域中。

基本原理:DDS的基本原理是通过数字技术直接控制相位和频率,从而合成任意频率和形状的输出信号。

这与传统的模拟频率合成器(AFS)不同,模拟频率合成器需要使用模拟电路来合成频率。

DDS的核心组成部分是相位累加器、DAC和时钟。

相位累加器用于积累相位,DAC用于将相位转换为模拟信号。

时钟提供DDS系统的基本时钟频率。

通过调整相位累加器的步进值和DAC的输出解析度,DDS可以实现非常细腻的频率和相位调整。

此外,DDS还可以通过修改时钟频率来调整输出频率的精度和稳定性。

技术指南:1.时钟频率选择:DDS的输出频率是由时钟频率和相位累加器的步进值共同决定的。

选择适当的时钟频率可以提高DDS系统的输出频率范围和分辨率。

一般来说,时钟频率应远高于所需输出频率的最高频率。

2.相位累加器和相位步进值:相位累加器决定了输出信号的相位,相位步进值决定了输出信号的频率。

通过调节相位累加器的步进值可以实现频率的连续可调。

较小的相位步进值可以提高DDS系统的频率分辨率。

3.数字信号处理:DDS系统中的数字信号处理单元可以对输入信号进行调制和滤波等操作,以实现更复杂的信号处理功能。

通过合理选择数字信号处理算法和参数,可以改善DDS系统的性能和输出质量。

4.输出滤波:DDS系统的输出信号通常需要经过滤波处理,以去除数字部分带来的杂散和非线性失真。

选择合适的滤波器类型和参数可以提高输出信号的质量和纯度。

5.时钟稳定性和干扰抑制:DDS系统对时钟的稳定性和干扰非常敏感。

为了提高系统的性能和稳定性,应选择具有较低抖动和干扰的时钟源,并采取适当的抑制技术。

6.电源和地线设计:DDS系统对电源和地线的设计要求较高。

应该采取合理的电源隔离和滤波措施,以减少电源噪声和干扰。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

本科毕业设计(论文) 题目:数字频率合成器学院:信息工程学院专业:xxx学号:xxx学生姓名:XX指导教师:xxx二○○年月日xxxx2008届毕业设计(论文)数字频率合成器XX摘要直接数字频率合成(简称DDS)是一种以固定的精确时钟为基准,利用数字处理模块产生频率和相位均可调的输出信号的技术。

随着超大规模集成电路和微电子技术的发展,现代高性能、高集成度和小体积的DDS产品正快速取代传统的模拟信号频率合成技术,成为这类问题的新的解决方案。

本文介绍了DDS技术的基本工作原理及特点,并在此基础上详细给出了DDS 频率合成器的设计方案。

在本系统中,用户通过键盘输入所需要频率信号的数据,,利用单片机计算出频率控制字,并对FPGA芯片EP1C6Q240C8进行编程,最后通过D/A转换器和LFP得到所需要的输出波形。

本系统主要由相位累加模块、波形存储模块、D/A转换模块和LFP模块组成,通过EDA开发软件,在线编译DDS信号源设计文件到FPGA开发板上,得出一个相位可调的正弦信号发生器。

只要改变存储波形信息的ROM数据,就可以灵活的实现任意波形发生器。

DDS信号发生器工作稳定,易于实现,输出频率分辨率高,可以满足人们不断提高的要求。

关键字:FPGA ;DDS ;相位累加器;正弦信号;单片机Ixx:<数字频率合成器>Direct Digital SynthesizerLiutaoAbstractDirect digital synthesis (DDS) is a technique for using digital data processing blocks as a means to generate a frequency-and-phase-tunable output signal referenced to a fixed-frequency precision clock source. With the development of VLSI and microelectronic technology, today’s high-performance, functionally-integrated , and small package-sized DDS products are fast becoming an alternative to traditional frequency-agile analog synthesizer solutions.The paper introduces the theory of DDS operation and its features. On the basis of this, the project of DDS signal generator is discussed in detail. In this system user can input the frequency data through a keyboard, and microcontroller C51 will work out the relevant value of the frequency tuning word (FTW),then programs to control an FPGA chip EP1C6Q240C8 ,so that the required output waveform is obtained by D/A converter and LFP.The system mainly consists of ACCP module, ROM of waveform module, D/A converter module and LFP module , through the EDA software development, online design compiler DDS source documents to the FPGA development board, and arrive at a frequency, phase adjustable sinusoidal signal generator system module. As long as the change in the information storage wave ROM data, the flexibility to achieve arbitrary waveform generatorsIt has been proved that DDS signal generator has good reliability, ease of implementation and high output frequency resolutions, it can meet the people’s continual elevated requires.Key words: FPGA ;DDS ;ACCP;Sinusoidal signal;microcontrollerIIxxxx2008届毕业设计(论文)目录前言 (1)第一章概述 (2)§1.1 DDS工作原理 (2)§1.2设计要求 (2)§1.3设计方案 (3)第2章硬件部分 (4)§2.1硬件平台介绍 (4)§2.2 DA转换 (5)§2.3 LFP (6)第3章软件部分 (6)§3.1 分频器 (6)§3.2相位累加器 (7)§3.3波形转换 (8)§3.4波形ROM (9)§3.5 波形翻转 (11)§3.6 键盘扫描 (12)§3.7显示部分 (16)IIIxx:<数字频率合成器>第4章系统测试 (17)§4.1具体调试 (17)§4.2测试结果 (17)§4.3结果分析 (18)结论 (18)IV武汉科技大学中南分校2008届毕业设计(论文)前言直接数字频率合成(DDS)技术是美国学者J.Tierncy,C.M.Rader和B.Gold 在1971年首次提出的。

这是一种全数字技术,该技术从相位概念出发直接合成所需要的波形。

同传统的频率合成技术相比,DDS技术具有很多优点:频率切换时间短、频率分辨率高、相位变化连续、容易实现对输出信号的多种调制等。

但是由于当时的技术以及器件水平的限制,它的性能指标还无法与已有的技术相比,因此该技术当时并没有引起足够的重视。

最近几年来,随着技术和器件水平的提高,国外一些公司先后推出各种各样的DDS专用芯片,如Qualcomm公司的Q2230、Q2334, AD公司的AD9955、AD9850等。

这些产品的问世,为电路设计者提供了良机,满足了工程实际的需要。

然而,商用DDS专用电路芯片也有它的的局限性,并不能满足所有要求。

例如,在实现线性调频(LFM)等复杂的调制功能时,利用现有的商用芯片就会遇到一些困难。

由于近几年来可编程器件CPLD 、现场可编程门阵列FPGA技术的迅速发展和广泛应用,使用可编程器件实现DDS技术也越来越受到人们的关注。

第1页共20页xx:<数字频率合成器>第2页共20页第一章概述§1.1 DDS工作原理DDS建立在采样定理基础上,由相位累加器、波形ROM、数模转换、LFP四部分构成。

首先对需要产生的波形进行采样或者通过matlab产生波形数据,将采样值数字化后存入存储器作为查找表,然后通过查表读取数据,再经D/A转换器转换为模拟量,将保存的波形重新合成出来。

DDS基本原理框图如图1所示。

除了滤波器(LPF)之外,DDS系统都是通过数字集成电路实现的,易于集成和小型化。

系统的参考时钟源通常是一个具有高稳定性的晶体振荡器,为各组成部分提供同步时钟。

频率控制字(FSW)实际上是相位增量值(二进制编码)作为相位累加器的累加值。

相位累加器在每一个参考时钟脉冲输入时,累加一次频率字,其输出相应增加一个步长的相位增量。

由于相位累加器的输出连接在波形存储器(ROM)的地址线上,因此其输出的改变就相当于查表。

这样就可以通过查表把存储在波形存储器内的波形抽样值(二进制编码)查找出来。

ROM的输出送到D/A转换器,经D/A转换器转换成模拟量输出。

§1.2设计要求设计制作一个正弦信号发生器。

(1)正弦波输出频率范围:10Hz~10kHz;(2)具有频率设置功能,频率步进:10Hz;(3)输出信号频率稳定度:优于410 ;武汉科技大学中南分校2008届毕业设计(论文)(4)输出电压幅度:在负载电阻上的电压峰-峰值V opp≥1V;(5)失真度:用示波器观察时无明显失真。

§1.3设计方案整个DDS中由相位累加器、波形ROM(波形存储器)、D/A转换、低通滤波器五部分组成,其工作原理是:将各波形的幅值/相位进行量化,将量化数据存储在ROM中,按照设定的频率,以相应的频率控制字k为步进,对相位进行累加,以累加相位值作为地址码读取存放在存储器的波形数据,这样存放在ROM中的波形幅值就按照相位关系依次输出,然后经D\A转换将数字信号变成阶梯状的模拟信号,最后通过低通滤波器去掉高频部分使波形变的平滑即可得到所需的波形。

在本设计中,键盘作为人机接口将频率控制字分别送到FPGA和单片机中,频率控制字在进入单片机后经过处理换算成频率数送入到LCD中将其显示出来;同时键盘还将频率控制字送入到FPGA中,在FPGA中经过相位累加器、波形图1.1ROM(波形存储器)输出该频率下波形的离散信号。

这样通过键盘就可以将控制波形的频率,并且让其显示在LCD上。

原理框图如图1.1所示:第3页共20页xx:<数字频率合成器>第4页共20页第2章硬件部分§2.1硬件平台介绍本系统的硬件平台为ETC-1型51&FPGA EVM板,实验板的实物图如图 2.1所示:图2.1实验板的基本性指标如下:1.51系列单片机。

ETC-1选择在中国广泛使用的51系统单片机作为系统的MCU。

2.单片机工作晶振为22.1184MHz,选择此晶振的目的是考虑到单片机的速度与单片机串行通信波特率所需的时钟,使其串行通信波特率可以上到很高,如115200bps或者230400bps等。

FPGA为EP1C6Q240C8。

该FPGA有120000的典型门资源和5980个LE2个PLL92160Bit的RAM资源该芯片为C8级别的,工作频率最高可以超过300MHz。