S6C0641中文资料

ECEC1HA682CJ中文资料(panasonic)中文数据手册「EasyDatasheet - 矽搜」

200

25 40 3.1 0.55 ECEC1AA273CJ

200

30 30 3.1 0.55 ECEC1AA273DJ

200

10

35 25 3.1 0.55 ECEC1AA273EJ

200

33000 25 45 3.4 0.55 ECEC1AA333CJ

200

30 35 3.4 0.55 ECEC1AA333DJ

100

1800 22 25 1.5 0.25 ECEC1HA182BJ

200

30 25 2.9 0.45 ECEC1CA123DJ

200

15000 22 40 3.2 0.45 ECEC1CA153BJ

200

25 35 3.2 0.45 ECEC1CA153CJ

200

16

30 30 3.2 0.45 ECEC1CA153DJ

200

18000 22 45 3.5 0.45 ECEC1CA183BJ

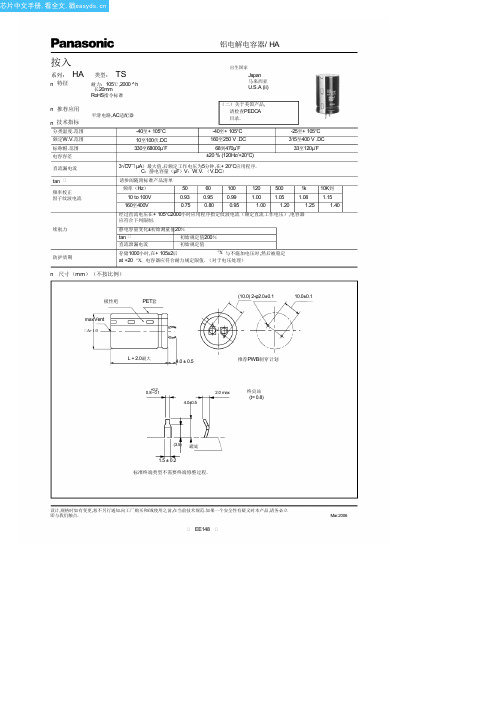

铝电解电容器/ HA

n 标准产品

W.V. (V)

Cap. (±20%)

(µF) 10000

外壳尺寸

产品规格

Dia. (mm)

长短

涟 当前

tan

(120Hz) (120Hz)

(mm)

(+105°C) (A)

(+20°C)

22 25 1.8 0.55

型号

PET套

码头长度

4.0mm

(无P.V.C.plate)

200

33000 30 45 4.7 0.45 ECEC1CA333DJ

100

35 35 4.7 0.45 ECEC1CA333EJ

100

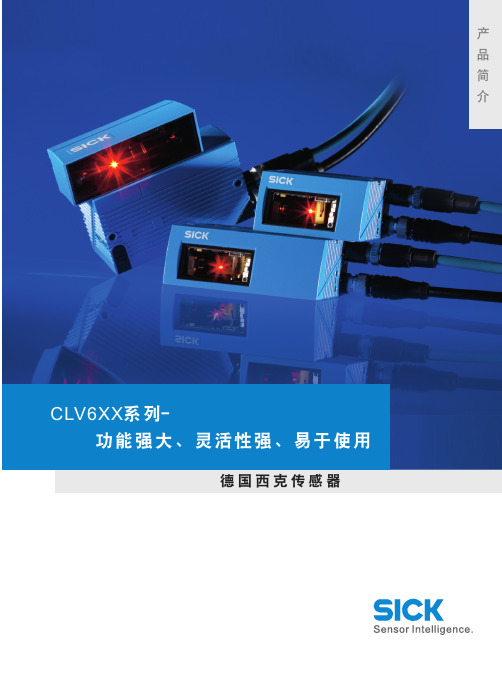

SICK条码扫描器CLV6

过使用外部参数克隆功能实现的无需

使用电脑进行配置,这样可以保证快

速的平均修复时间 (MTTR)*)。

聚焦 固定聚焦型号用于固定焦距的应用, 动态聚焦型号用于有多种读取距离的 应用,还可以根据实时集成距离检测 仪实现自动对焦点转换(无需再配备 光电传感器)。

优化全部生产过程

现今,企业要发展,必须 注重过程而不是功能;必 须排除不灵活的工作过程, 全面优化价值的生产过程。 因此,必须要有一个整体 的,而不是单纯地解决某 一问题的自动化解决方案。

作为全球自动化、安全技 术、环境监测系统和自动 识别系统等传感器领域的 佼佼者,SICK公司致力于 发展工业过程的现代化和 合理化。

阅读距离 • 利用外部参数克隆功能实现快速、简便的更换条

码扫描器

汽车行业

• 阅读距离远 • 具有自动聚焦和动态聚焦型号 • 灵活的现场总线连接 • 快速接头方式 • 无硅 • 利用外部参数克隆功能实现快速、简便的更换条码扫

描器

电子行业

• 紧凑型产品,适用于宽度极小的模块 • 对部分遮盖、污损或对比度低的条码都能提供优异的

• 多样的聚焦模式(固定聚焦、动态聚焦和自动聚焦)几 乎覆盖了所有的读取距离

易于使用

• 简单直观的用户界面 SOPAS-ET Single Device 或 SOPASET(请参见第 32 页)

• 配备连接助手,连接条码扫描器更快捷。无需额外的现 场总线。

• 通过集成按钮、LED 条形图和智能化自动设置功能即可 实现简便设置,无需电脑主机。

外部镜罩 邻输送带之间时,外部镜罩可以缩短阅读距离。

前置读取窗口

侧面读取窗口

侧面读取窗口, 带摆镜

线式扫描器 光栅扫描器 线式扫描器,带摆镜

C1608C0G1H331J资料

REMINDERSPlease read this before using the product.SAFETY REMINDERSREMINDERS1. If you intend to use a product listed in this catalog for a purpose that may cause loss of life or other damage, you must contact our company’s sales window.2. We may modify products or discontinue production of a product listed in this catalog without prior notification.3. We provide “Delivery Specification” that explain precautions for the specifications and safety of each product listed in this cata-log. We strongly recommend that you exchange these delivery specifications with customers that use one of these products.4. If you plan to export a product listed in this catalog, keep in mind that it may be a restricted item according to the “Foreign Exchange and Foreign Trade Control Law”. In such cases, it is necessary to acquire export permission in harmony with this law.5. Any reproduction or transferring of the contents of this catalog is prohibited without prior permission from our company.6. We are not responsible for problems that occur related to the intellectual property rights or other rights of our company or a third party when you use a product listed in this catalog. We do not grant license of these rights.7. This catalog only applies to products purchased through our company or one of our company’s official agencies. This catalog does not apply to products that are purchased through other third parties.8. The descriptions in this catalog apply as of April 2007.General Multilayer Ceramic Chip Capacitors C Series C1608 (EIA CC0603) TypeFEATURES•High capacitance has been achieved through precision technologies that enable the use of multiple thinner ceramic dielectric layers.• A monolithic structure ensures superior mechanical strength and reliability.•High-accuracy automatic mounting is facilitated through the maintenance of very precise dimensional tolerances.•Composed of only ceramics and metals, these capacitors provide extremely dependable performance, exhibiting virtually no degradation even when subjected to temperature extremes.•Low stray capacitance ensures high conformity with nominal values, thereby simplifying the circuit design process.•Low residual inductance assures superior frequency characteristics.•Because electrostatic capacity has been obtained up to the electrolytic capacitor range, these capacitors offer long service life and are optimally suited for power supply designs that require high levels of reliability.•Owing to their low ESR and excellent frequency characteristics, these products are optimally suited for high frequency and high-density type power supplies.SHAPES AND DIMENSIONS PRODUCT IDENTIFICATION(1) Series name(2) Dimensions L×W(3) Capacitance temperature characteristicsClass 1 (T emperature compensation)Class 2 (T emperature stable and general purpose)(4) Rated voltage Edc(5) Nominal capacitanceThe capacitance is expressed in three digit codes and in units of pico farads (pF).The first and second digits identify the first and second significant figures of the capacitance.The third digit identifies the multiplier.R designates a decimal point.(6) Capacitance tolerance(7) Packaging styleConformity to RoHS DirectiveC1608CH1H100D(1)(2)(3)(4)(5)(6)(7)1608 1.6×0.8mmT emperaturecharacteristicsCapacitance change Temperature rangeCH0±60ppm/°C–25 to +85°CSL+350 to –1000ppm/°C+20 to +85°CT emperaturecharacteristicsCapacitance change Temperature rangeJB±10%–25 to +85°CJF+30, –80%–25 to +85°CX7R±15%–55 to +125°CX5R±15%–55 to +85°CY5V+22, –82%–30 to +85°C1A10V1C16V1H50V0101pF10010pF1021,000pF0R50.5pFSymbol T oleranceApplicable capacitancerangeC±0.25pF10pF or lessJ±5%Over 10pFK±10%Z+80, –20%T T aping (reel)B Bulk•Conformity to RoHS Directive: This means that, in conformity with EU Directive 2002/95/EC, lead, cadmium, mercury, hexavalent chromium, and specific bromine-based flame retardants, PBB and PBDE, have not been used, except for exempted applications.CAPACITANCE RANGES: CLASS 1 (TEMPERATURE COMPENSATION)TEMPERATURE CHARACTERISTICS: CH(0±60ppm/°C), C0G(0±30ppm/°C)RATED VOLTAGE Edc: 50V TEMPERATURE CHARACTERISTICS: SL(+350 to –1000ppm/ )RATED VOLTAGE Edc: 10VCAPACITANCE RANGES: CLASS 2TEMPERATURE CHARACTERISTICS: JB(±10%), X5R/X7R(±15%)RATED VOLTAGE Edc: 50VCapacitance(pF)ToleranceThickness T (mm)Part No.T emperature characteristics: CH T emperature characteristics: C0G 0.5 ±0.25pF 0.8±0.10C1608CH1H0R5C C1608C0G1H0R5C 0.75 ±0.25pF 0.8±0.10C1608CH1HR75C C1608C0G1HR75C 1 ±0.25pF 0.8±0.10C1608CH1H010C C1608C0G1H010C 1.5 ±0.25pF 0.8±0.10C1608CH1H1R5C C1608C0G1H1R5C 2 ±0.25pF 0.8±0.10C1608CH1H020C C1608C0G1H020C 3 ±0.25pF 0.8±0.10C1608CH1H030C C1608C0G1H030C 4 ±0.25pF 0.8±0.10C1608CH1H040C C1608C0G1H040C 5 ±0.25pF 0.8±0.10C1608CH1H050C C1608C0G1H050C 6 ±0.5pF 0.8±0.10C1608CH1H060D C1608C0G1H060D 7 ±0.5pF 0.8±0.10C1608CH1H070D C1608C0G1H070D 8 ±0.5pF 0.8±0.10C1608CH1H080D C1608C0G1H080D 9 ±0.5pF 0.8±0.10C1608CH1H090D C1608C0G1H090D 10 ±0.5pF 0.8±0.10C1608CH1H100D C1608C0G1H100D 12 ±5%0.8±0.10C1608CH1H120J C1608C0G1H120J 15 ±5%0.8±0.10C1608CH1H150J C1608C0G1H150J 18 ±5%0.8±0.10C1608CH1H180J C1608C0G1H180J 22 ±5%0.8±0.10C1608CH1H220J C1608C0G1H220J 27 ±5%0.8±0.10C1608CH1H270J C1608C0G1H270J 33 ±5%0.8±0.10C1608CH1H330J C1608C0G1H330J 39 ±5%0.8±0.10C1608CH1H390J C1608C0G1H390J 47 ±5%0.8±0.10C1608CH1H470J C1608C0G1H470J 56 ±5%0.8±0.10C1608CH1H560J C1608C0G1H560J 68 ±5%0.8±0.10C1608CH1H680J C1608C0G1H680J 82 ±5%0.8±0.10C1608CH1H820J C1608C0G1H820J 100 ±5%0.8±0.10C1608CH1H101J C1608C0G1H101J 120±5%0.8±0.10C1608CH1H121J C1608C0G1H121J 150 ±5%0.8±0.10C1608CH1H151J C1608C0G1H151J 180±5%0.8±0.10C1608CH1H181J C1608C0G1H181J 220 ±5%0.8±0.10C1608CH1H221J C1608C0G1H221J 270±5%0.8±0.10C1608CH1H271J C1608C0G1H271J 330 ±5%0.8±0.10C1608CH1H331J C1608C0G1H331J 390±5%0.8±0.10C1608CH1H391J C1608C0G1H391J 470 ±5%0.8±0.10C1608CH1H471J C1608C0G1H471J 560±5%0.8±0.10C1608CH1H561J C1608C0G1H561J 680 ±5%0.8±0.10C1608CH1H681J C1608C0G1H681J 820±5%0.8±0.10C1608CH1H821J C1608C0G1H821J 1,000 ±5%0.8±0.10C1608CH1H102J C1608C0G1H102J 1,500 ±5%0.8±0.10C1608CH1H152J C1608C0G1H152J 2,200 ±5%0.8±0.10C1608CH1H222J C1608C0G1H222J 3,300 ±5%0.8±0.10C1608CH1H332JC1608C0G1H332JCapacitance (pF)Tolerance Thickness T (mm)Part No.T emperature characteristics: SL 15,000±5%0.80±0.10C1608SL1A153J 22,000±5%0.80±0.10C1608SL1A223JCapacitance(pF)ToleranceThickness T (mm)Part No.T emperature characteristics: JB T emperature characteristics: X5R Temperature characteristics: X7R 10,000 ±10%0.8±0.10C1608JB1H103KC1608X5R1H103K C1608X7R1H103K15,000 ±10%0.8±0.10C1608JB1H153KC1608X5R1H153K C1608X7R1H153K 22,000 ±10%0.8±0.10C1608JB1H223K C1608X5R1H223K C1608X7R1H223K 33,000 ±10%0.8±0.10C1608JB1H333KC1608X5R1H333K C1608X7R1H333K 47,000 ±10%0.8±0.10C1608JB1H473KC1608X5R1H473K C1608X7R1H473K 68,000 ±10%0.8±0.10C1608JB1H683KC1608X5R1H683K C1608X7R1H683K 100,000±10%0.8±0.10C1608JB1H104K C1608X5R1H104K C1608X7R1H104K ±20%0.8±0.10C1608JB1H104MC1608X5R1H104MC1608X7R1H104MRATED VOLTAGE Edc: 16VTEMPERATURE CHARACTERISTICS: JB(±10%), X5R(±15%)RATED VOLTAGE Edc: 25VRATED VOLTAGE Edc: 16VRATED VOLTAGE Edc: 10VRATED VOLTAGE Edc: 6.3VTEMPERATURE CHARACTERISTICS: JF(+30, –80%), Y5V(+22, –82%)RATED VOLTAGE Edc: 50VT emperature characteristics: JB T emperature characteristics: X5R Temperature characteristics: X7R 150,000 ±10%0.8±0.10C1608JB1E154K C1608X5R1E154K C1608X7R1E154K ±20%0.8±0.10C1608JB1E154M C1608X5R1E154M C1608X7R1E154M 220,000 ±10%0.8±0.10C1608JB1E224K C1608X5R1E224K C1608X7R1E224K ±20%0.8±0.10C1608JB1E224M C1608X5R1E224M C1608X7R1E224M 330,000±10%0.8±0.10C1608JB1E334K C1608X5R1E334K C1608X7R1E334K ±20%0.8±0.10C1608JB1E334MC1608X5R1E334MC1608X7R1E334MCapacitance (pF)Tolerance Thickness T (mm)Part No.T emperature characteristics: JB T emperature characteristics: X5R Temperature characteristics: X7R 470,000 ±10%0.8+0.15, –0.1C1608JB1C474K C1608X5R1C474K C1608X7R1C474K ±20%0.8+0.15, –0.1C1608JB1C474M C1608X5R1C474M C1608X7R1C474M 680,000 ±10%0.8+0.15, –0.1C1608JB1C684K C1608X5R1C684K C1608X7R1C684K ±20%0.8+0.15, –0.1C1608JB1C684M C1608X5R1C684M C1608X7R1C684M 1,000,000±10%0.8+0.2, –0.1C1608JB1C105K C1608X5R1C105K C1608X7R1C105K ±20%0.8+0.2, –0.1C1608JB1C105MC1608X5R1C105MC1608X7R1C105MCapacitance (pF)Tolerance Thickness T (mm)Part No.T emperature characteristics: JB T emperature characteristics: X5R 470,000±10%0.80±0.10C1608JB1E474K C1608X5R1E474K ±20%0.80±0.10C1608JB1E474M C1608X5R1E474M 680,000±10%0.80±0.10C1608JB1E684K C1608X5R1E684K ±20%0.80±0.10C1608JB1E684M C1608X5R1E684M 1,000,000±10%0.80±0.10C1608JB1E105K C1608X5R1E105K ±20%0.80±0.10C1608JB1E105MC1608X5R1E105MCapacitance (pF)Tolerance Thickness T (mm)Part No.T emperature characteristics: JB T emperature characteristics: X5R 1,500,000 ±10%0.8±0.10C1608JB1C155K C1608X5R1C155K ±20%0.8±0.10C1608JB1C155M C1608X5R1C155M 2,200,000±10%0.8±0.10C1608JB1C225K C1608X5R1C225K ±20%0.8±0.10C1608JB1C225MC1608X5R1C225MCapacitance (pF)Tolerance Thickness T (mm)Part No.T emperature characteristics: JB T emperature characteristics: X5R 3,300,000 ±10%0.8±0.10C1608JB1A335K C1608X5R1A335K ±20%0.8±0.10C1608JB1A335M C1608X5R1A335M 4,700,000±10%0.8±0.10C1608JB1A475K C1608X5R1A475K ±20%0.8±0.10C1608JB1A475MC1608X5R1A475MCapacitance (pF)Tolerance Thickness T (mm)Part No.T emperature characteristics: JB T emperature characteristics: X5R 6,800,000 ±10%0.80+0.15,–0.10C1608JB0J685K C1608X5R0J685K ±20%0.80+0.15,–0.10C1608JB0J685M C1608X5R0J685M 10,000,000±10%0.80+0.15,–0.10C1608JB0J106K C1608X5R0J106K ±20%0.80+0.20,–0.10C1608JB0J106MC1608X5R0J106MCapacitance(pF)ToleranceThickness T (mm)Part No.T emperature characteristics: JF T emperature characteristics: Y5V 100,000 +80,–20%0.8±0.10C1608JF1H104Z C1608Y5V1H104Z 220,000 +80,–20%0.8±0.10C1608JF1H224Z C1608Y5V1H224Z 470,000 +80,–20%0.8±0.10C1608JF1H474ZC1608Y5V1H474ZRATED VOLTAGE Edc: 16V RATED VOLTAGE Edc: 6.3V T emperature characteristics: JF T emperature characteristics: Y5V1,000,000 +80,–20%0.8±0.10C1608JF1E105Z C1608Y5V1E105ZCapacitance (pF)ToleranceThickness T(mm)Part No.T emperature characteristics: JF T emperature characteristics: Y5V2,200,000 +80,–20%0.8±0.10C1608JF1C225Z C1608Y5V1C225ZCapacitance (pF)ToleranceThickness T(mm)Part No.T emperature characteristics: JF T emperature characteristics: Y5V4,700,000 +80,–20%0.8±0.10C1608JF0J475Z C1608Y5V0J475Z 10,000,000 +80,–20%0.8+0.15,–0.10C1608JF0J106Z C1608Y5V0J106Z • For more information about the products of other capacitance or data, please contact us.。

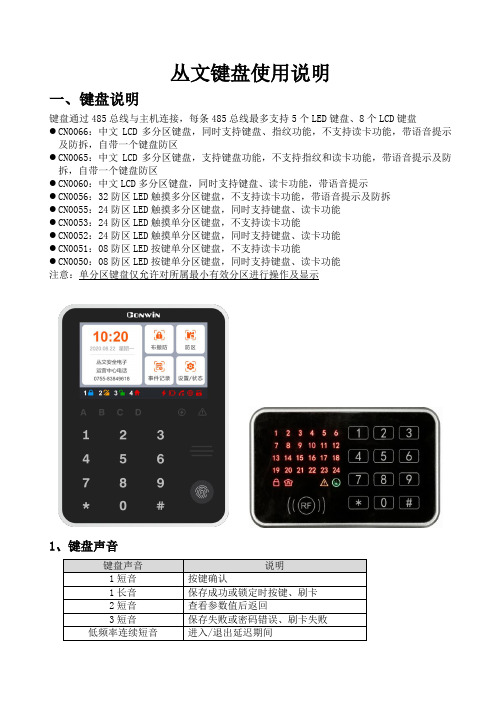

丛文键盘使用说明说明书

丛文键盘使用说明一、键盘说明键盘通过485总线与主机连接,每条485总线最多支持5个LED键盘、8个LCD键盘●CN0066:中文LCD多分区键盘,同时支持键盘、指纹功能,不支持读卡功能,带语音提示及防拆,自带一个键盘防区●CN0065:中文LCD多分区键盘,支持键盘功能,不支持指纹和读卡功能,带语音提示及防拆,自带一个键盘防区●CN0060:中文LCD多分区键盘,同时支持键盘、读卡功能,带语音提示●CN0056:32防区LED触摸多分区键盘,不支持读卡功能,带语音提示及防拆●CN0055:24防区LED触摸多分区键盘,同时支持键盘、读卡功能●CN0053:24防区LED触摸单分区键盘,不支持读卡功能●CN0052:24防区LED触摸单分区键盘,同时支持键盘、读卡功能●CN0051:08防区LED按键单分区键盘,不支持读卡功能●CN0050:08防区LED按键单分区键盘,同时支持键盘、读卡功能注意:单分区键盘仅允许对所属最小有效分区进行操作及显示1、键盘声音2、键盘指示灯●LED按键键盘(CN0050/CN0051)撤防准备:红灯灭,绿灯亮撤防未准备:红灯灭,绿灯慢闪布防:红灯亮,绿灯亮防区报警:红灯快闪,绿灯亮进入旁路模式或连接485总线故障:红灯、绿灯同时快闪进入编程或用户模式:红灯、绿灯同时慢闪●LED触摸键盘(CN0052/CN0053/CN0055/CN0056)指示灯布防留守布防(CN0052/CN0053)A/B/C/D:分区布撤防(CN0055/CN0056)故障电源1主机布防/留守布防所有网络连接及电话通讯故障交流、电池正常防区未准备快闪主机报警(分区报警) 交流故障防区报警●CN0052/CN0053单分区键盘:+两个灯同时慢闪,进入编程或用户模式;两个灯同时快闪,进入旁路模式;仅灯快闪,表示进入故障查询模式●CN0055/CN0056多分区键盘:当灯快闪,且A/B/C/D/五个灯同时慢闪,表示进入编程或用户模式;当灯快闪,且A/B/C/D/五个灯也同时快闪,表示进入旁路模式;仅灯快闪,表示进入故障查询模式●中文LCD键盘(CN0060/CN0066)布防留守布防(CN0060)A/B/C/D:分区布撤防(CN0066)故障电源准备(仅CN0060)主机布防/留守布防所有网络连接及电话通讯故障交流/电池正常防区未准备快闪主机报警(分区报警) * 主机防拆报警交流故障------------- ●CN0066多分区键盘:当灯快闪,且A/B/C/D/五个灯同时慢闪,表示进入编程或用户模式;当灯快闪,且A/B/C/D/五个灯也同时快闪,表示进入旁路模式●CN0060多分区键盘:当灯快闪,且灯同时慢闪,表示进入编程或用户模式;当灯快闪,且灯也同时快闪,进入旁路模式3、中文LCD键盘屏幕蓝色,外出布防灰色,外出布防退出延时期间红色,外出布防报警蓝色,留守布防灰色,留守布防退出延时期间红色,留守布防报警绿色,撤防准备红色,撤防报警黄色,撤防未准备红色,电池故障红色,交流故障红色,电话外线故障向上还有内容时,此图标出现向下还有内容时,此图标出现向上快翻向下快翻返回关闭窗口3.1 主界面(待机状态)●日期时间:显示日期时间,或者显示报警及未准备防区(自动滚屏显示)注意:当显示报警及未准备防区时,直接点击该区域可以进入“防区”菜单●用户信息:用于显示用户信息。

FPGA可编程逻辑器件芯片XC2S30-6CSG144C中文规格书

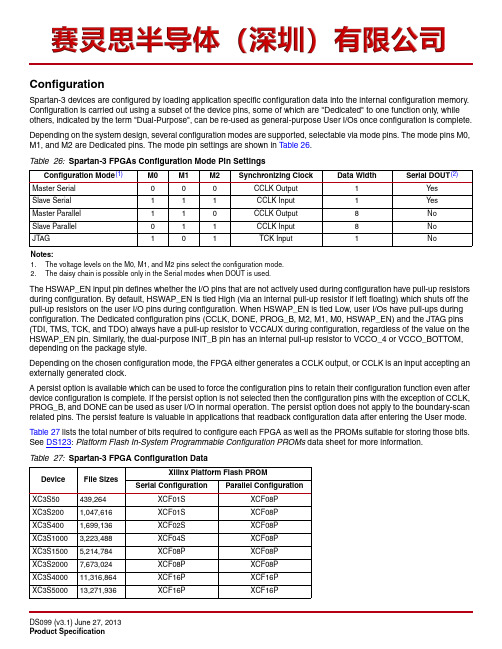

ConfigurationSpartan-3 devices are configured by loading application specific configuration data into the internal configuration memory. Configuration is carried out using a subset of the device pins, some of which are "Dedicated" to one function only, while others, indicated by the term "Dual-Purpose", can be re-used as general-purpose User I/Os once configuration is complete.Depending on the system design, several configuration modes are supported, selectable via mode pins. The mode pins M0, M1, and M2 are Dedicated pins. The mode pin settings are shown in Table 26.The HSWAP_EN input pin defines whether the I/O pins that are not actively used during configuration have pull-up resistorsduring configuration. By default, HSWAP_EN is tied High (via an internal pull-up resistor if left floating) which shuts off the pull-up resistors on the user I/O pins during configuration. When HSWAP_EN is tied Low, user I/Os have pull-ups during configuration. The Dedicated configuration pins (CCLK, DONE, PROG_B, M2, M1, M0, HSWAP_EN) and the JTAG pins (TDI, TMS, TCK, and TDO) always have a pull-up resistor to VCCAUX during configuration, regardless of the value on the HSWAP_EN pin. Similarly, the dual-purpose INIT_B pin has an internal pull-up resistor to VCCO_4 or VCCO_BOTTOM, depending on the package style.Depending on the chosen configuration mode, the FPGA either generates a CCLK output, or CCLK is an input accepting an externally generated clock.A persist option is available which can be used to force the configuration pins to retain their configuration function even after device configuration is complete. If the persist option is not selected then the configuration pins with the exception of CCLK, PROG_B, and DONE can be used as user I/O in normal operation. The persist option does not apply to the boundary-scan related pins. The persist feature is valuable in applications that readback configuration data after entering the User mode.Table 27 lists the total number of bits required to configure each FPGA as well as the PROMs suitable for storing those bits. See DS123: Platform Flash In-System Programmable Configuration PROMs data sheet for more information.Table 26:Spartan-3 FPGAs Configuration Mode Pin SettingsConfiguration Mode (1)M0M1M2Synchronizing ClockData WidthSerial DOUT (2)Master Serial 000CCLK Output 1Yes Slave Serial 111CCLK Input 1Y es Master Parallel 110CCLK Output 8No Slave Parallel 011CCLK Input 8No JTAG 11TC K Input1NoNotes:1.The voltage levels on the M0, M1, and M2 pins select the configuration mode.2.The daisy chain is possible only in the Serial modes when DOUT is used.Table 27:Spartan-3 FPGA Configuration DataDevice File Sizes Xilinx Platform Flash PROMSerial ConfigurationParallel ConfigurationXC3S50439,264XCF01S XCF08P XC3S2001,047,616XCF01S XCF08P XC3S4001,699,136XCF02S XCF08P XC3S10003,223,488XCF04S XCF08P XC3S15005,214,784XCF08P XCF08P XC3S20007,673,024XCF08P XCF08P XC3S400011,316,864XCF16P XCF16P XC3S500013,271,936XCF16PXCF16PSpartan-3 FPGA Family: Functional DescriptionSimultaneously Switching Output GuidelinesThis section provides guidelines for the maximum allowable number of Simultaneous Switching Outputs (SSOs). These guidelines describe the maximum number of user I/O pins, of a given output signal standard, that should simultaneously switch in the same direction, while maintaining a safe level of switching noise. Meeting these guidelines for the stated test conditions ensures that the FPGA operates free from the adverse effects of ground and power bounce.Ground or power bounce occurs when a large number of outputs simultaneously switch in the same direction. The output drive transistors all conduct current to a common voltage rail. Low-to-High transitions conduct to the V CCO rail; High-to-Low transitions conduct to the GND rail. The resulting cumulative current transient induces a voltage difference across the inductance that exists between the die pad and the power supply or ground return. The inductance is associated with bonding wires, the package lead frame, and any other signal routing inside the package. Other variables contribute to SSO noise levels, including stray inductance on the PCB as well as capacitive loading at receivers. Any SSO-induced voltage consequently affects internal switching noise margins and ultimately signal quality.Table49 and Table50 provide the essential SSO guidelines. For each device/package combination, T able49 provides the number of equivalent V CCO/GND pairs. The equivalent number of pairs is based on characterization and will possibly not match the physical number of pairs. For each output signal standard and drive strength, Table50 recommends the maximum number of SSOs, switching in the same direction, allowed per V CCO/GND pair within an I/O bank. The T able50 guidelines are categorized by package style. Multiply the appropriate numbers from T able49 and Table50 to calculate the maximum number of SSOs allowed within an I/O bank. Exceeding these SSO guidelines may result in increased power or ground bounce, degraded signal integrity, or increased system jitter.SSO MAX/IO Bank = Table49 x Table50The recommended maximum SSO values assume that the FPGA is soldered on the printed circuit board and that the board uses sound design practices. The SSO values do not apply for FPGAs mounted in sockets, due to the lead inductance introduced by the socket.The number of SSOs allowed for quad-flat packages (VQ, TQ, PQ) is lower than for ball grid array packages (FG) due to the larger lead inductance of the quad-flat packages. Ball grid array packages are recommended for applications with a large number of simultaneously switching outputs.Table 49:Equivalent V CCO/GND Pairs per BankDevice VQ100CP132(1)(2)TQ144(1)PQ208FT256FG320FG456FG676FG900FG1156(2) XC3S501 1.5 1.52––––––XC3S2001– 1.523–––––XC3S400–– 1.52335–––XC3S1000––––3355––XC3S1500–––––356––XC3S2000––––––569–XC3S4000–––––––61012XC3S5000–––––––61012Digital Clock Manager (DCM) TimingFor specification purposes, the DCM consists of three key components: the Delay-Locked Loop (DLL), the Digital Frequency Synthesizer (DFS), and the Phase Shifter (PS).Aspects of DLL operation play a role in all DCM applications. All such applications inevitably use the CLKIN and the CLKFB inputs connected to either the CLK0 or the CLK2X feedback, respectively. Thus, specifications in the DLL tables (Table58 and Table59) apply to any application that only employs the DLL component. When the DFS and/or the PS components are used together with the DLL, then the specifications listed in the DFS and PS tables (Table60 through Table63) supersede any corresponding ones in the DLL tables. DLL specifications that do not change with the addition of DFS or PS functions are presented in Table58 and Table59.Period jitter and cycle-cycle jitter are two (of many) different ways of characterizing clock jitter. Both specifications describe statistical variation from a mean value.Period jitter is the worst-case deviation from the average clock period of all clock cycles in the collection of clock periods sampled (usually from 100,000 to more than a million samples for specification purposes). In a histogram of period jitter, the mean value is the clock period.Cycle-cycle jitter is the worst-case difference in clock period between adjacent clock cycles in the collection of clock periods sampled. In a histogram of cycle-cycle jitter, the mean value is zero.Delay-Locked Loop (DLL)Table 58:Recommended Operating Conditions for the DLLSymbol Description Frequency Mode/F CLKIN RangeSpeed GradeUnits -5-4Min Max Min MaxInput Frequency RangesF CLKIN CLKIN_FREQ_DLL_LF Frequency for the CLKIN input Low18(2)167(3)18(2)167(3)MHzCLKIN_FREQ_DLL_HF High48280(3)48280(3)(4)MHz Input Pulse RequirementsCLKIN_PULSE CLKIN pulse width as apercentage of the CLKIN period F CLKIN≤ 100 MHz40%60%40%60%-F CLKIN> 100 MHz45%55%45%55%-Input Clock Jitter Tolerance and Delay Path Variation(5)CLKIN_CYC_JITT_DLL_LF Cycle-to-cycle jitter at the CLKINinput Low–±300–±300psCLKIN_CYC_JITT_DLL_HF High–±150–±150ps CLKIN_PER_JITT_DLL_LF Period jitter at the CLKIN input All–±1–±1ns CLKIN_PER_JITT_DLL_HF ––CLKFB_DELAY_VAR_EXT Allowable variation of off-chipfeedback delay from the DCMoutput to the CLKFB inputAll–±1–±1nsNotes:1.DLL specifications apply when any of the DLL outputs (CLK0, CLK90, CLK180, CLK270, CLK2X, CLK2X180, or CLKDV) are in use.2.The DFS, when operating independently of the DLL, supports lower F CLKIN frequencies. See Table60.3.The CLKIN_DIVIDE_BY_2 attribute can be used to increase the effective input frequency range up to F BUFG. When set to TRUE,CLKIN_DIVIDE_BY_2 divides the incoming clock frequency by two as it enters the DCM.4.Industrial temperature range devices have additional requirements for continuous clocking, as specified in T able64.5.CLKIN input jitter beyond these limits may cause the DCM to lose lock. See UG331 for more details.。

5C-06中文资料

15 WATT WIDE INPUTDC-DC CONVERTERSFeature• 15W Isolated Output • Remote ON/OFF Control • 4:1 Input Range • Efficiency to 82%• Six-Sided ShieldNOTE: 1.Nominal Input Voltage 24 or 48 VDCMODEL INPUT OUTPUT OUTPUT INPUT CURRENT % EFF.CASENUMBER VOLTAGE VOLTAGE CURRENT NO LOAD FULL LOAD 5C-015C-025C-035C-045C-055C-065C-075C-085C-095C-115C-125C-135C-145C-155C-165C-175C-185C-199-36 VDC18-72 VDC 5 VDC 12 VDC 15 VDC ±5 VDC ±12 VDC ±15 VDC 5/±12 VDC 5/±15 VDC 3.3 VDC 5 VDC 12 VDC 15 VDC ±5 VDC ±12 VDC ±15 VDC 5/±12 VDC 5/±15 VDC 3.3 VDC3000 mA 1250 mA 1000 mA ±1500 mA ±625 mA ±500 mA 1500/±310 mA 1500/±250 mA3000 mA 3000 mA 1250 mA 1000 mA ±1500 mA ±625 mA ±500 mA 1500/±310 mA 1500/±250 mA3000 mA15 mA 15 mA 15 mA 20 mA 20 mA 20 mA 20 mA 20 mA 15 mA 10 mA 10 mA 10 mA 15 mA 15 mA 15 mA 15 mA 15 mA 10 mA810 mA 780 mA 780 mA 810 mA 780 mA 780 mA 780 mA 780 mA 545 mA 410 mA 390 mA 390 mA 400 mA 380 mA 380 mA 380 mA 380 mA 270 mA778080778080808076778080798282828276CC15CSpecifications5CAll Specifications Typical At Nominal Line,Full Load and 25˚C Unless Otherwise Noted.NOTE:1.Measured From High Line to Low Line2.Measured From Full Load to 1/4 LoadINPUT SPECIFICATIONS:Input Voltage Range..........................................................................................................................................24V ...................................................................9-36V48V .................................................................18-72VInput Filter....................................................................................................................................................................................................................................Pi TypeOUTPUT SPECIFICATIONS:Voltage AccuracySingle Output.......................................................................................................................................................................................................................±1.0% max.Dual +Output.......................................................................................................................................................................................................................±1.0% max.-Output.......................................................................................................................................................................................................................±3.0% max.Triple,5V ...............................................................................................................................................................................................................................±2.0% max.12V/15V .....................................................................................................................................................................................................................±3.0% max.Voltage Balance (Dual).....................................................................................................................................................................................................±1.0% max.Transient Response:Single,25% Step Load Change.........................................................................................................................................................................................<500µsec.Dual,FL-1/2L±1% Error Band...............................................................................................................................................................................................<500µsec.External Trim Adj.Range.............................................................................................................................................................................................................±10%.Ripple & Noise,20MHz BW.......................................................................................................................................................................................10mV RMS,max.75mV p-p max.Temperature Coefficient...................................................................................................................................................................................................±0.02%/°C Short Circuit Protection.....................................................................................................................................................................................................Continuous Line Regulation 1,Single/Dual............................................................................................................................................................................................±0.2% max.Triple......................................................................................................................................................................................................±1.0% max.Load Regulation 2,Single/Dual..........................................................................................................................................................................................±1.0% max.Triple...................................................................................................................................................................................................±5.0% max.GENERAL SPECIFICATIONS:Efficiency ..........................................................................................See Table Isolation Voltage........................................................................500 VDC min Isolation Resistance...........................................................................109ohms Switching Frequency ...................................................................300KHz,min Case Grounding...............................................Capacity Coupled to Input Operating Temperature Range...........................................-25°C to + 71°C Case Temperature.......................................................................100˚C max.Cooling...........................................................................Free-Air Convection Storage Temperature Range..............................................-55°C to + 105°C EMI/RFI................................................................Six-Sided Continuous Shield Dimensions...........................................................................2 x 2 x 0.4 inches(50.8 x 50.8 x 10.2 mm)Case Material...................................................Black Coated Copper withNon-Conductive BaseCASE CPIN CONNECTIONPin Single Daul Triple 1.2.3.4.5.6.7.8.No Pin -Vin +Vin Trim -Vout +Vout No PinNo Pin -Vin +Vin Trim -Vout Common +VoutNo Pin -Vin +Vin-Aux.Out Common +5V out +Aux.OutRemote On/Off ControlLogic Compatibility EC-On EC-OffShutdown Idle Current Input Resistance Control CommonCMOS or Open Collector TTL >+5.5VDC or Open Circuit<1.8 VDC 10 mA100K ohms (Ein 0 VDC to 9 VDC)Referenced to Input MinusExternal Output TrimmingOutput may optionally be externally trimmed (±10%) with a TRIPLE OUTPUT LOADING TABLE (1)AmperesMin.(2) Nom.Output Voltage( Pin No.)78 & 58 & 5+5+12 or -12+15 or -150.250.100.10 1.50.310.25NOTE:1.Maximum total power from all outputs is limited to 15 watts but no output should be allowed to exceed its maximum current.2.Minimum current on each output is required to maintain specified regulation.Remote On/Off Control PIN 7PIN 6PIN 52BEHLMAN4532 Telephone Road Suite 103 Ventura, CA 93003 80 Cabot Court Hauppauge, NY 11788(805 ) 642-0660 (800)456-2006 Fax (805) 642-0790 e-mail: sales@ (631)435-0410 (800)874-6727 Fax(631)951-4341Web-site: 。

赋芯电子 SMC92106 数据手册说明书

FORICS产品手册上海赋芯电子科技有限公司SMC92106数据手册日期:2014年09月09日版本号:V1.4SMC92106非接触感应式读写模块产品概述可读写ISO_IEC14443卡片(支持Mifare One S50、Mifare One S70、Mifare Ultra Light、Mifare Pro等卡片)可读取卡片序列号及任意区块数据,包括密钥块及数据块接供UART接口,串口波特率可设置范围:1200BPS~256000BPS串口通信协议简单,全系列管脚兼容,操作简洁方便模块供电电压,3.3V精选进口器件,确保产品的稳定一致体积小巧,采用耐高温阻燃材料封装,可过波峰焊接,方便批量生产一、产品规格:型号SMC92106尺寸27(长)×17(高)×7(厚)mm工作频率13.56MHz读卡距离5~8cm二、技术参数:工作电压VCC=3.3V消耗电流25mA休眠电流<3mAI/O输出电流10mA工作温度-40℃~85℃储存温度-40℃~125℃储存湿度5~95%RH三、模块外型与实际尺寸:SMC92106China1408图1.模块外型图SMC92106China 14081217A N T 2A N T 1N CB E E P /L E DT X D R X D R E S E T G N D V C C2772,54图2.模块详细尺寸(单位mm )四、脚位说明:SMC92106China 1408图3.SMC92106引脚功能图脚位说明&电气特性:PIN NAME I/O SymbolMinNomMaxDESCRIPTION1ANT2A ---Driver output2/ANT in 2ANT1A ---Driver output13NCNote1-Not Connect 4BEEP/LED O Vo-H Vo-L V DD -0.45----0.45V Software controllable 5TXD O Vo-H Vo-L V DD -0.45---0.45VDigital data output 6RXD IVi-H Vi-L V DD X 0.70V SS +0.2V --V DD +0.3V V DD X 0.3VDigital data input 7/RESET Note2I Low active 8GND P V SS Ground 9VCCPV DD3.0V 3V 3.3VVCC=3.3V注意1:建议该脚悬空。

S6C0666中文资料

4

元器件交易网

6 BIT 384 CHANNEL RSDS TFT–LCD SOURCE DRIVER

PREMILINARY VER 1.0

S6C0666

BLOCK DIAGRAM

Y382

Y383 6

POL

Output Buffer

R-DAC

VGMA1 to VGMA10

Prepared by:

Akira Kang

akira211@samsung.co.kr

1

元器件交易网

S6C0666

PREMILINARY VER 1.0

6 BIT 384 CHANNEL RSDS TFT–LCD SOURCE DRIVER

S6C0666 Specification Revision History Version 0.0 Original Content Date Aug.1999

元器件交易网

6 BIT 384 CHANNEL RSDS TFT–LCD SOURCE DRIVER

PREMILINARY VER 1.0

S6C0666

S6C0666

6 BIT 384 CHANNEL RSDS TFT-LCD SOURCE DRIVER

August. 1999. Ver. 0.0

RPI2 RPO2

Figure 1. S6C0666 Block Diagram

Y384

Y1

Y2

Y3

5

元器件交易网

S6C0666

PREMILINARY VER 1.0

6 BIT 384 CHANNEL RSDS TFT–LCD SOURCE DRIVER

S6C0649资料

S6C0649

256 CHANNEL TFT-LCD GATE DRIVER

November. 1999. Ver. 0.1

Prepared by:

Jae il Byeon

kerigma@samsung.co.kr

Contents in this document are subject to change without notice. No part of this document may be reproduced or transmitted in any form or by any means, electronic or mechanical, for any purpose, without the express written permission of LCD Driver IC Team.

4

元器件交易网

256 CH. TFT-LCD GATE DRIVER

S6C0649

BLOCK DIAGRAM

VDD VLO VSS1 U/D CPV

DI/O

S/R S/R 001 002

256 Shift Register

S/R S/R 255 256

DO/I

OE1 OE2 OE3

Content

Date Aug.1999 Nov.1999

2

元器件交易网

256 CH. TFT-LCD GATE DRIVER

S6C0649

CONTENTS

INTRODUCTION .................................................................................................... 4 FEATURES............................................................................................................. 4 BLOCK DIAGRAM ................................................................................................. 5 PIN ASSIGNMENTS ............................................................................................. 6 PIN DESCRIPTIONS.............................................................................................. 7 ABSOLUTE MAXIMUM RATINGS ........................................................................ 8 RECOMMENDED OPERATION RATINGS ........................................................... 8 DC CHARACTERISTICS ....................................................................................... 9 AC CHARACTERISTICS ..................................................................................... 10 AC TIMING DIAGRAM ......................................................................................... 11 OPERATION DESCRIPTION............................................................................... 12

C6026资料

-60 -70 -80 -90 -100

1

0 -10 -20 -30 -40

dB -50

-60 -70 -80 -90 -100

1

Low Pass Insertion Loss

10

100

Frequency (MHz)

Crossover Isolation

10

100

Frequency (MHz)

dB -50

-60 -70 -80 -90 -100

1

0 -10 -20 -30 -40

dB -50

-60 -70 -80 -90 -100

1

Low Pass Insertion Loss

10

100

Frequency (MHz)

Crossover Isolation

10

100

Frequency (MHz)

4

C236.B (11/06)

元器件交易网

DIPLEXERS FOR CABLE MODEMS, SET TOP BOXES AND GATEWAYS

0 -10 -20 -30 -40

dB -50

-60 -70 -80 -90 -100

1

元器件交易网

DIPLEXERS FOR CABLE MODEMS, SET TOP BOXES AND GATEWAYS

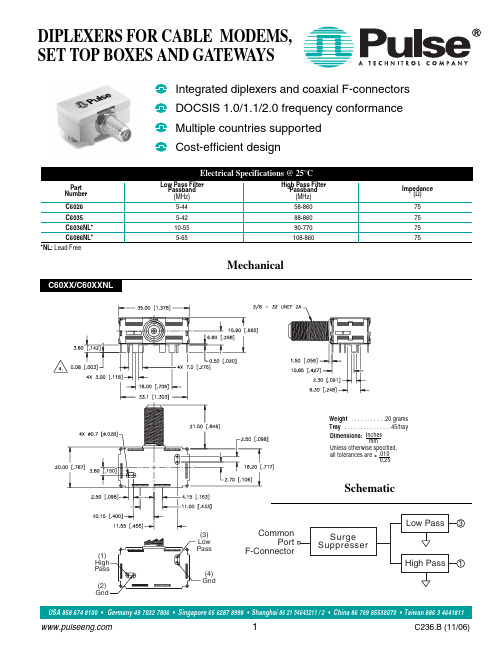

Part Number C6026 C6035 C6036NL* C6086NL* *NL: Lead Free

C60XX/C60XXNL

Integrated diplexers and coaxial F-connectors DOCSIS 1.0/1.1/2.0 frequency conformance Multiple countries supported Cost-efficient design

P0640SP06C中文资料

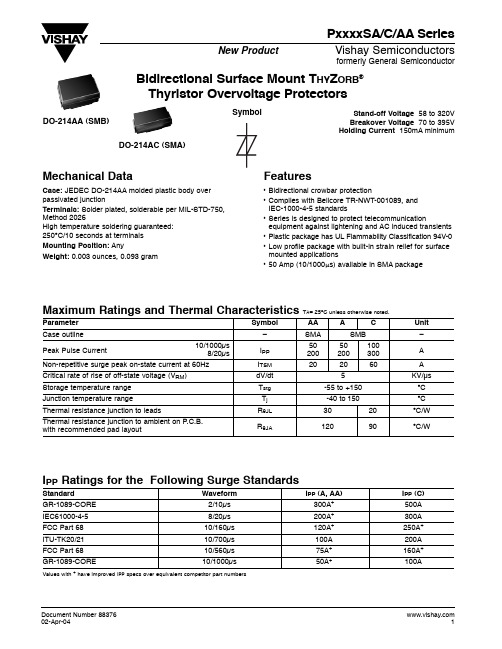

PxxxxSA/C/AA SeriesVishay Semiconductorsformerly General SemiconductorDocument Number New ProductBidirectional Surface Mount T HY Z ORB ®Thyristor Overvoltage ProtectorsStand-off Voltage 58 to 320V Breakover Voltage 70 to 395V Holding Current 150mA minimumFeatures• Bidirectional crowbar protection• Complies with Bellcore TR-NWT-001089, and IEC-1000-4-5 standards• Series is designed to protect telecommunicationequipment against lightening and AC induced transients •Plastic package has UL Flammability Classification 94V-0• Low profile package with built-in strain relief for surface mounted applications• 50 Amp (10/1000µs) available in SMA packageMechanical DataCase:JEDEC DO-214AA molded plastic body over passivated junctionTerminals: Solder plated, solderable per MIL-STD-750,Method 2026High temperature soldering guaranteed:250°C/10 seconds at terminals Mounting Position:AnyWeight:0.003 ounces, 0.093 gramMaximum Ratings and Thermal Characteristics T A= 25OC unless otherwise noted.Parameter Symbol AAA C Unit Case outline –SMA SMB –Peak Pulse Current10/1000µsI PP 5050100A 8/20µs200200300Non-repetitive surge peak on-state current at 60HzI TSM 202060A Critical rate of rise of off-state voltage (V RM )dV/dt 5KV/µs Storage temperature range T stg -55 to +150°C Junction temperature range T j -40 to 150°CThermal resistance junction to leadsR θJL 3020°C/W Thermal resistance junction to ambient on P .C.B. R θJA12090°C/Wwith recommended pad layoutDO-214AA (SMB)DO-214AC (SMA)SymbolI PP Ratings for the Following Surge StandardsStandard Waveform I PP (A, AA)I PP (C)GR-1089-CORE 2/10µs 300A+500A IEC61000-4-58/20µs 200A +300A FCC Part 6810/160µs 120A +250A +ITU-TK20/2110/700µs 100A 200A FCC Part 6810/560µs 75A+160A +GR-1089-CORE10/1000µs50A +100AValues with +have improved I PP specs over equivalent competitor part numbersPxxxxSA/C/AA SeriesVishay Semiconductorsformerly General Semiconductor Document Number 88376Electrical Characteristics(T A = 25°C unless otherwise noted)P0640S_58570*800 3.015075115P0720S_65580*800 3.015070115P0900S_75595*800 3.015066115P1100S_905115*800 3.01506075P1300S_1205145*800 3.01505070P1500S_1405180800 3.01504565P1800S_1605220800 3.01504565P2300S_1905250*800 3.01504565P2600S_2205290*800 3.01504065P3100S_2755350800 3.01504060P3500S_3205395*8003.01503560Notes: (1) dv/dt = 100V/µs(2) V R = 2V, f = 1MHz(3) Values with * have improved VBO specs over equivalent competitor part numbersType Stand-off Voltage V DRM (V)Max. Reverse Leakage at V DRM I DRM (µA)Minimum Holding Current I H (mA)Typical Capacitance C (pF)(2)AA, A C Maximum Breakover Current I BO (mA)(1)Maximum Breakover Voltage V BO (V)(1)(3)Max. On-State Voltage at I T = 1A V T (V)Device MarkingTypeSuffix AAA C P0640S_06A P06A P06C P0720S_07A P07A P07C P0900S_09A P09A P09C P1100S_11A P11A P11C P1300S_13A P13A P13C P1500S_15A P15A P15C P1800S_18A P18A P18C P2300S_23A P23A P23B P2600S_26A P26A P26B P3100S_31A P31A P31C P3500S_35AP35AP35CDO-214AA (SMB)DO-214AC (SMA)SMB Mounting Pad LayoutSMA Mounting Pad LayoutPxxxxSA/C/AA SeriesVishay Semiconductorsformerly General SemiconductorDocument Number Legal Disclaimer NoticeVishay Document Number: NoticeSpecifications of the products displayed herein are subject to change without notice. Vishay Intertechnology, Inc., or anyone on its behalf, assumes no responsibility or liability for any errors or inaccuracies.Information contained herein is intended to provide a product description only. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Vishay's terms and conditions of sale for such products, Vishay assumes no liability whatsoever, and disclaims any express or implied warranty, relating to sale and/or use of Vishay products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright, or other intellectual property right. The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications. Customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Vishay for any damages resulting from such improper use or sale.。

XCS05XL-5BG256C中文资料

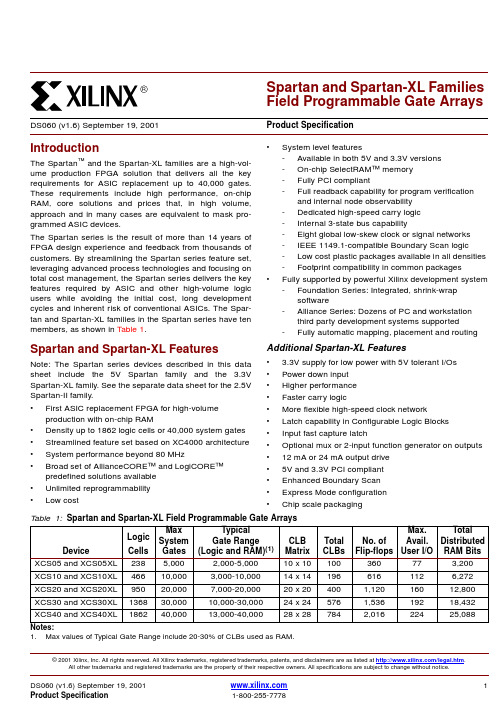

© 2001 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at /legal.htm .All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.IntroductionThe Spartan ™ and the Spartan-XL families are a high-vol-ume production FPGA solution that delivers all the key requirements for ASIC replacement up to 40,000 gates.These requirements include high performance, on-chip RAM, core solutions and prices that, in high volume,approach and in many cases are equivalent to mask pro-grammed ASIC devices.The Spartan series is the result of more than 14 years of FPGA design experience and feedback from thousands of customers. By streamlining the Spartan series feature set,leveraging advanced process technologies and focusing on total cost management, the Spartan series delivers the key features required by ASIC and other high-volume logic users while avoiding the initial cost, long development cycles and inherent risk of conventional ASICs. The Spar-tan and Spartan-XL families in the Spartan series have ten members, as shown in T able 1.Spartan and Spartan-XL FeaturesNote: The Spartan series devices described in this data sheet include the 5V Spartan family and the 3.3V Spartan-XL family. See the separate data sheet for the 2.5V Spartan-II family.•First ASIC replacement FPGA for high-volume production with on-chip RAM•Density up to 1862 logic cells or 40,000 system gates •Streamlined feature set based on XC4000 architecture •System performance beyond 80MHz•Broad set of AllianceCORE ™ and LogiCORE ™ predefined solutions available •Unlimited reprogrammability •Low cost•System level features-Available in both 5V and 3.3V versions -On-chip SelectRAM ™ memory -Fully PCI compliant-Full readback capability for program verificationand internal node observability -Dedicated high-speed carry logic -Internal 3-state bus capability-Eight global low-skew clock or signal networks -IEEE 1149.1-compatible Boundary Scan logic -Low cost plastic packages available in all densities -Footprint compatibility in common packages•Fully supported by powerful Xilinx development system -Foundation Series: Integrated, shrink-wrapsoftware-Alliance Series: Dozens of PC and workstationthird party development systems supported-Fully automatic mapping, placement and routing Additional Spartan-XL Features• 3.3V supply for low power with 5V tolerant I/Os •Power down input •Higher performance •Faster carry logic•More flexible high-speed clock network•Latch capability in Configurable Logic Blocks •Input fast capture latch•Optional mux or 2-input function generator on outputs •12 mA or 24 mA output drive •5V and 3.3V PCI compliant •Enhanced Boundary Scan •Express Mode configuration •Chip scale packagingSpartan and Spartan-XL Families Field Programmable Gate ArraysDS060 (v1.6) September 19, 2001Product Specification T able 1: Spartan and Spartan-XL Field Programmable Gate Arrays1.Max values of Typical Gate Range include 20-30% of CLBs used as RAM.2DS060 (v1.6) September 19, 2001General OverviewSpartan series FPGAs are implemented with a regular, flex-ible, programmable architecture of Configurable Logic Blocks (CLBs), interconnected by a powerful hierarchy of versatile routing resources (routing channels), and sur-rounded by a perimeter of programmable Input/Output Blocks (IOBs), as seen in Figure 1. They have generous routing resources to accommodate the most complex inter-connect patterns.The devices are customized by loading configuration data into internal static memory cells. Re-programming is possi-ble an unlimited number of times. The values stored in thesememory cells determine the logic functions and intercon-nections implemented in the FPGA. The FPGA can either actively read its configuration data from an external serial PROM (Master Serial mode), or the configuration data can be written into the FPGA from an external device (Slave Serial mode).Spartan series FPGAs can be used where hardware must be adapted to different user applications. FPGAs are ideal for shortening design and development cycles, and also offer a cost-effective solution for production rates well beyond 50,000 systems per month.Figure 1: Basic FPGA Block DiagramSpartan series devices achieve high-performance, low-cost operation through the use of an advanced architecture and semiconductor technology. Spartan and Spartan-XL devices provide system clock rates exceeding 80MHz and internal performance in excess of150MHz. In contrast to other FPGA devices, the Spartan series offers the most cost-effective solution while maintaining leading-edge per-formance. In addition to the conventional benefit of high vol-ume programmable logic solutions, Spartan series FPGAs also offer on-chip edge-triggered single-port and dual-port RAM, clock enables on all flip-flops, fast carry logic, and many other features.The Spartan/XL families leverage the highly successful XC4000 architecture with many of that family’s features and benefits. T echnology advancements have been derived from the XC4000XLA process developments.Logic Functional DescriptionThe Spartan series uses a standard FPGA structure as shown in Figure1, page2. The FPGA consists of an array of configurable logic blocks (CLBs) placed in a matrix of routing channels. The input and output of signals is achieved through a set of input/output blocks (IOBs) forming a ring around the CLBs and routing channels.•CLBs provide the functional elements for implementing the user’s logic.•IOBs provide the interface between the package pins and internal signal lines.•Routing channels provide paths to interconnect the inputs and outputs of the CLBs and IOBs.The functionality of each circuit block is customized during configuration by programming internal static memory cells. The values stored in these memory cells determine the logic functions and interconnections implemented in the FPGA.Configurable Logic Blocks (CLBs)The CLBs are used to implement most of the logic in an FPGA. The principal CLB elements are shown in the simpli-fied block diagram in Figure2. There are three look-up tables (LUT) which are used as logic function generators, two flip-flops and two groups of signal steering multiplexers. There are also some more advanced features provided by the CLB which will be covered in the Advanced Features Description, page13.Function GeneratorsTwo 16x1 memory look-up tables (F-LUT and G-LUT) are used to implement 4-input function generators, each offer-ing unrestricted logic implementation of any Boolean func-tion of up to four independent input signals (F1 to F4 or G1 to G4). Using memory look-up tables the propagation delay is independent of the function implemented.A third 3-input function generator (H-LUT) can implement any Boolean function of its three inputs. Two of these inputs are controlled by programmable multiplexers (see box "A" of Figure2). These inputs can come from the F-LUT or G-LUT outputs or from CLB inputs. The third input always comes from a CLB input. The CLB can, therefore, implement cer-tain functions of up to nine inputs, like parity checking. The three LUTs in the CLB can also be combined to do any arbi-trarily defined Boolean function of five inputs.4DS060 (v1.6) September 19, 2001A CLB can implement any of the following functions:•Any function of up to four variables, plus any second function of up to four unrelated variables, plus any third function of up to three unrelated variablesNote: When three separate functions are generated, one of the function outputs must be captured in a flip-flop internal to the CLB. Only two unregistered function generator outputs are available from the CLB.•Any single function of five variables•Any function of four variables together with some functions of six variables•Some functions of up to nine variables.Implementing wide functions in a single block reduces both the number of blocks required and the delay in the signal path, achieving both increased capacity and speed. The versatility of the CLB function generators significantly improves system speed. In addition, the design-software tools can deal with each function generator independently.This flexibility improves cell usage.Flip-FlopsEach CLB contains two flip-flops that can be used to regis-ter (store) the function generator outputs. The flip-flops and function generators can also be used independently (see Figure 2). The CLB input DIN can be used as a direct input to either of the two flip-flops. H1 can also drive either flip-flop via the H-LUT with a slight additional delay.The two flip-flops have common clock (CK), clock enable (EC) and set/reset (SR) inputs. Internally both flip-flops are also controlled by a global initialization signal (GSR) which is described in detail in Global Signals: GSR and GTS ,page 20.Latches (Spartan-XL only)The Spartan-XL CLB storage elements can also be config-ured as latches. The two latches have common clock (K)and clock enable (EC) inputs. Functionality of the storage element is described in Table 2.Figure 2: Spartan/XL Simplified CLB Logic Diagram (some features not shown)Clock InputEach flip-flop can be triggered on either the rising or falling clock edge. The CLB clock line is shared by both flip-flops.However, the clock is individually invertible for each flip-flop (see CK path in Figure 3). Any inverter placed on the clock line in the design is automatically absorbed into the CLB. Clock EnableThe clock enable line (EC) is active High. The EC line is shared by both flip-flops in a CLB. If either one is left discon-nected, the clock enable for that flip-flop defaults to the active state. EC is not invertible within the CLB. The clock enable is synchronous to the clock and must satisfy the setup and hold timing specified for the device.Set/ResetThe set/reset line (SR) is an asynchronous active High con-trol of the flip-flop. SR can be configured as either set or reset at each flip-flop. This configuration option determines the state in which each flip-flop becomes operational after configuration. It also determines the effect of a GSR pulse during normal operation, and the effect of a pulse on the SR line of the CLB. The SR line is shared by both flip-flops. If SR is not specified for a flip-flop the set/reset for that flip-flop defaults to the inactive state. SR is not invertible within the CLB.CLB Signal Flow ControlIn addition to the H-LUT input control multiplexers (shown in box "A" of Figure 2, page 4) there are signal flow control multiplexers (shown in box "B" of Figure 2) which select the signals which drive the flip-flop inputs and the combinatorial CLB outputs (X and Y).Each flip-flop input is driven from a 4:1 multiplexer which selects among the three LUT outputs and DIN as the data source.Each combinatorial output is driven from a 2:1 multiplexer which selects between two of the LUT outputs. The X output can be driven from the F-LUT or H-LUT, the Y output from G-LUT or H-LUT .Control SignalsThere are four signal control multiplexers on the input of the CLB. These multiplexers allow the internal CLB control sig-nals (H1, DIN, SR, and EC in Figure 2 and Figure 4) to be driven from any of the four general control inputs (C1-C4 in Figure 4) into the CLB. Any of these inputs can drive any of the four internal control signals.T able 2: CLB Storage Element FunctionalityLegend:XDon ’t careRising edge (clock not inverted).SR Set or Reset value. Reset is default.0*Input is Low or unconnected (default value)1*Input is High or unconnected (default value)Figure 3: CLB Flip-Flop Functional Block Diagram6DS060 (v1.6) September 19, 2001The four internal control signals are:•EC: Enable Clock•SR: Asynchronous Set/Reset or H function generator Input 0•DIN: Direct In or H function generator Input 2•H1: H function generator Input 1.Input/Output Blocks (IOBs)User-configurable input/output blocks (IOBs) provide the interface between external package pins and the internal logic. Each IOB controls one package pin and can be con-figured for input, output, or bidirectional signals. Figure 6shows a simplified functional block diagram of the Spar-tan/XL IOB.IOB Input Signal PathThe input signal to the IOB can be configured to either go directly to the routing channels (via I1 and I2 in Figure 6) or to the input register. The input register can be programmed as either an edge-triggered flip-flop or a level-sensitive latch. The functionality of this register is shown in Table 3,and a simplified block diagram of the register can be seen in Figure 5.Figure 4: CLB Control Signal InterfaceFigure 5: IOB Flip-Flop/Latch Functional BlockDiagramTable 3: Input Register FunctionalityX Don ’t care.Rising edge (clock not inverted).SR Set or Reset value. Reset is default.0*Input is Low or unconnected (default value)1*Input is High or unconnected (default value)The register choice is made by placing the appropriate library symbol. For example, IFD is the basic input flip-flop (rising edge triggered), and ILD is the basic input latch (transparent-High). Variations with inverted clocks are also available. The clock signal inverter is also shown in Figure5 on the CK line.The Spartan IOB data input path has a one-tap delay ele-ment: either the delay is inserted (default), or it is not. The Spartan-XL IOB data input path has a two-tap delay ele-ment, with choices of a full delay, a partial delay, or no delay. The added delay guarantees a zero hold time with respect to clocks routed through the global clock buffers. (See Glo-bal Nets and Buffers, page12 for a description of the glo-bal clock buffers in the Spartan/XL families.) For a shorter input register setup time, with positive hold-time, attach a NODELAY attribute or property to the flip-flop.The output of the input register goes to the routing channels (via I1 and I2 in Figure6). The I1 and I2 signals that exit the IOB can each carry either the direct or registered input signal.The 5V Spartan input buffers can be globally configured for either TTL (1.2V) or CMOS (VCC/2) thresholds, using an option in the bitstream generation software. The Spartan output levels are also configurable; the two global adjust-ments of input threshold and output level are independent. The inputs of Spartan devices can be driven by the outputs of any 3.3V device, if the Spartan inputs are in TTL mode. Input and output thresholds are TTL on all configuration pins until the configuration has been loaded into the device and specifies how they are to be used. Spartan-XL inputs are TTL compatible and 3.3V CMOS compatible. Supported sources for Spartan/XL device inputs are shown in Table4.Spartan-XL I/Os are fully 5V tolerant even though the V CC is 3.3V. This allows 5V signals to directly connect to the Spar-tan-XL inputs without damage, as shown in Table4. In addi-tion, the 3.3V V CC can be applied before or after 5V signals are applied to the I/Os. This makes the Spartan-XL devices immune to power supply sequencing problems.Figure 6: Simplified Spartan/XL IOB Block Diagram8DS060 (v1.6) September 19, 2001Spartan-XL V CC ClampingSpartan-XL FPGAs have an optional clamping diode con-nected from each I/O to V CC . When enabled they clamp ringing transients back to the 3.3V supply rail. This clamping action is required in 3.3V PCI applications. V CC clamping is a global option affecting all I/O pins.Spartan-XL devices are fully 5V TTL I/O compatible if V CC clamping is not enabled. With V CC clamping enabled, the Spartan-XL devices will begin to clamp input voltages to one diode voltage drop above V CC . If enabled, TTL I/O com-patibility is maintained but full 5V I/O tolerance is sacrificed.The user may select either 5V tolerance (default) or 3.3V PCI compatibility. In both cases negative voltage is clamped to one diode voltage drop below ground.Spartan-XL devices are compatible with TTL, LVTTL, PCI 3V, PCI 5V and LVCMOS signalling. The various standards are illustrated in Table 5.Additional Fast Capture Input Latch (Spartan-XL only)The Spartan-XL IOB has an additional optional latch on the input. This latch is clocked by the clock used for the output flip-flop rather than the input clock. Therefore, two different clocks can be used to clock the two input storage elements.This additional latch allows the fast capture of input data,which is then synchronized to the internal clock by the IOB flip-flop or latch.T o place the Fast Capture latch in a design, use one of the special library symbols, ILFFX or ILFLX. ILFFX is a trans-parent-Low Fast Capture latch followed by an active High input flip-flop. ILFLX is a transparent Low Fast Capture latch followed by a transparent High input latch. Any of the clock inputs can be inverted before driving the library element,and the inverter is absorbed into the IOB.IOB Output Signal PathOutput signals can be optionally inverted within the IOB,and can pass directly to the output buffer or be stored in an edge-triggered flip-flop and then to the output buffer. The functionality of this flip-flop is shown in T able 6.T able 4: Supported Sources for Spartan/XL InputsT able 5: I/O Standards Supported by Spartan-XL FPGAsTable 6: Output Flip-Flop Functionality X Don ’t careRising edge (clock not inverted). SR Set or Reset value. Reset is default.0*Input is Low or unconnected (default value)1*Input is High or unconnected (default value)Z3-stateOutput Multiplexer/2-Input Function Generator (Spartan-XL only)The output path in the Spartan-XL IOB contains an addi-tional multiplexer not available in the Spartan IOB. The mul-tiplexer can also be configured as a 2-input function generator, implementing a pass gate, AND gate, OR gate, or XOR gate, with 0, 1, or 2 inverted inputs.When configured as a multiplexer, this feature allows two output signals to time-share the same output pad, effec-tively doubling the number of device outputs without requir-ing a larger, more expensive package. The select input is the pin used for the output flip-flop clock, OK.When the multiplexer is configured as a 2-input function generator, logic can be implemented within the IOB itself. Combined with a Global buffer, this arrangement allows very high-speed gating of a single signal. For example, a wide decoder can be implemented in CLBs, and its output gated with a Read or Write Strobe driven by a global buffer. The user can specify that the IOB function generator be used by placing special library symbols beginning with the letter "O." For example, a 2-input AND gate in the IOB func-tion generator is called OAND2. Use the symbol input pin labeled "F" for the signal on the critical path. This signal is placed on the OK pin — the IOB input with the shortest delay to the function generator. Two examples are shown in Figure7.Output BufferAn active High 3-state signal can be used to place the out-put buffer in a high-impedance state, implementing 3-state outputs or bidirectional I/O. Under configuration control, the output (O) and output 3-state (T) signals can be inverted. The polarity of these signals is independently configured for each IOB (see Figure6, page7). An output can be config-ured as open-drain (open-collector) by tying the 3-state pin (T) to the output signal, and the input pin (I) to Ground.By default, a 5V Spartan device output buffer pull-up struc-ture is configured as a TTL-like totem-pole. The High driver is an n-channel pull-up transistor, pulling to a voltage one transistor threshold below V CC. Alternatively, the outputs can be globally configured as CMOS drivers, with additional p-channel pull-up transistors pulling to V CC. This option, applied using the bitstream generation software, applies to all outputs on the device. It is not individually programma-ble.All Spartan-XL device outputs are configured as CMOS drivers, therefore driving rail-to-rail. The Spartan-XL outputs are individually programmable for 12mA or 24mA output drive.Any 5V Spartan device with its outputs configured in TTL mode can drive the inputs of any typical 3.3V device. Sup-ported destinations for Spartan/XL device outputs are shown in Table7.Three-State Register (Spartan-XL Only)Spartan-XL devices incorporate an optional register control-ling the three-state enable in the IOBs. The use of the three-state control register can significantly improve output enable and disable time.Output Slew RateThe slew rate of each output buffer is, by default, reduced, to minimize power bus transients when switching non-criti-cal signals. For critical signals, attach a FAST attribute or property to the output buffer or flip-flop.Spartan/XL devices have a feature called "Soft Start-up," designed to reduce ground bounce when all outputs are turned on simultaneously at the end of configuration. When the configuration process is finished and the device starts up, the first activation of the outputs is automatically slew-rate limited. Immediately following the initial activation of the I/O, the slew rate of the individual outputs is deter-mined by the individual configuration option for each IOB. Pull-up and Pull-down NetworkProgrammable pull-up and pull-down resistors are used fortying unused pins to V CC or Ground to minimize power con-sumption and reduce noise sensitivity. The configurablepull-up resistor is a p-channel transistor that pulls to V CC.The configurable pull-down resistor is an n-channel transis-tor that pulls to Ground. The value of these resistors is typi-cally 20KΩ − 100KΩ (See "Spartan DC Characteristics Figure 7: AND and MUX Symbols in Spartan-XL IOB10DS060 (v1.6) September 19, 2001Over Operating Conditions" on page 43.). This high value makes them unsuitable as wired-AND pull-up resistors.After configuration, voltage levels of unused pads, bonded or unbonded, must be valid logic levels, to reduce noise sensitivity and avoid excess current. Therefore, by default,unused pads are configured with the internal pull-up resistor active. Alternatively, they can be individually configured with the pull-down resistor, or as a driven output, or to be driven by an external source. To activate the internal pull-up, attach the PULLUP library component to the net attached to the pad. To activate the internal pull-down, attach the PULL-DOWN library component to the net attached to the pad.Set/ResetAs with the CLB registers, the GSR signal can be used to set or clear the input and output registers, depending on the value of the INIT attribute or property. The two flip-flops can be individually configured to set or clear on reset and after configuration. Other than the global GSR net, no user-con-trolled set/reset signal is available to the I/O flip-flops (Figure 5). The choice of set or reset applies to both the ini-tial state of the flip-flop and the response to the GSR pulse.Independent ClocksSeparate clock signals are provided for the input (IK) and output (OK) flip-flops. The clock can be independently inverted for each flip-flop within the IOB, generating eitherfalling-edge or rising-edge triggered flip-flops. The clock inputs for each IOB are mon Clock EnablesThe input and output flip-flops in each IOB have a common clock enable input (see EC signal in Figure 5), which through configuration, can be activated individually for the input or output flip-flop, or both. This clock enable operates exactly like the EC signal on the Spartan/XL CLB. It cannot be inverted within the IOB.Routing Channel DescriptionAll internal routing channels are composed of metal seg-ments with programmable switching points and switching matrices to implement the desired routing. A structured,hierarchical matrix of routing channels is provided to achieve efficient automated routing.This section describes the routing channels available in Spartan/XL devices. Figure 8 shows a general block dia-gram of the CLB routing channels. The implementation soft-ware automatically assigns the appropriate resources based on the density and timing requirements of the design.The following description of the routing channels is for infor-mation only and is simplified with some minor details omit-ted. For an exact interconnect description the designer should open a design in the FPGA Editor and review the actual connections in this tool.The routing channels will be discussed as follows;•CLB routing channels which run along each row and column of the CLB array.•IOB routing channels which form a ring (called a VersaRing) around the outside of the CLB array. It connects the I/O with the CLB routing channels.•Global routing consists of dedicated networks primarily designed to distribute clocks throughout the device with minimum delay and skew. Global routing can also be used for other high-fanout signals.CLB Routing ChannelsThe routing channels around the CLB are derived from three types of interconnects; single-length, double-length,and longlines. At the intersection of each vertical and hori-zontal routing channel is a signal steering matrix called a Programmable Switch Matrix (PSM). Figure 8 shows the basic routing channel configuration showing single-length lines, double-length lines and longlines as well as the CLBs and PSMs. The CLB to routing channel interface is shown as well as how the PSMs interface at the channel intersec-tions.T able 7: Supported Destinations for Spartan/XL OutputsNotes:1.Only if destination device has 5V tolerant inputs.CLB InterfaceA block diagram of the CLB interface signals is shown in Figure9. The input signals to the CLB are distributed evenly on all four sides providing maximum routing flexibility. In general, the entire architecture is symmetrical and regular. It is well suited to established placement and routing algo-rithms. Inputs, outputs, and function generators can freely swap positions within a CLB to avoid routing congestion during the placement and routing operation. The exceptions are the clock (K) input and CIN/COUT signals. The K input is routed to dedicated global vertical lines as well as four single-length lines and is on the left side of the CLB. The CIN/COUT signals are routed through dedicated intercon-nects which do not interfere with the general routing struc-ture. The output signals from the CLB are available to drive both vertical and horizontal channels.Programmable Switch MatricesThe horizontal and vertical single- and double-length lines intersect at a box called a programmable switch matrix (PSM). Each PSM consists of programmable pass transis-tors used to establish connections between the lines (see Figure10).For example, a single-length signal entering on the right side of the switch matrix can be routed to a single-length line on the top, left, or bottom sides, or any combination thereof, if multiple branches are required. Similarly, a dou-ble-length signal can be routed to a double-length line on any or all of the other three edges of the programmable switch matrix.Single-Length LinesSingle-length lines provide the greatest interconnect flexibil-ity and offer fast routing between adjacent blocks. There are eight vertical and eight horizontal single-length lines associ-ated with each CLB. These lines connect the switching matrices that are located in every row and column of CLBs. Single-length lines are connected by way of the program-mable switch matrices, as shown in Figure10. Routing con-nectivity is shown in Figure8.Single-length lines incur a delay whenever they go through a PSM. Therefore, they are not suitable for routing signals for long distances. They are normally used to conduct sig-nals within a localized area and to provide the branching for nets with fanout greater than one.Figure 8: Spartan/XL CLB Routing Channels and Interface Block DiagramFigure 9: CLB Interconnect Signals。

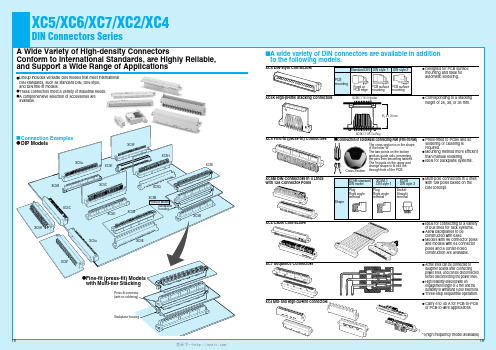

XC6T-644,XC2A-6412,XC6D-6421,XC4G-3212,XC4H-3213,XC4K-1542,XC4L-1546, 规格书,Datasheet 资料

XC5A XC5EXC5DXC5CXC5CXC5HXC5FXC5BXC5AXC5EXC5HXC5GXC5EXC5BXC5BBackplane housingXC5FPress-fit ModelXC5B25, 30, 35 mmXC5B- 31-0 SocketXC5K- 31- A PlugPress-fit connector (with no soldering)Backplane housingXC5 DIN-style ConnectorsXC5K High-profile Stacking ConnectorsPCB mountingStandard DINFixed at PCB edge PCB surface mounting PCB surface mountingDIN style 1DIN style 2ShapeXC5M standard DIN model PlugRight angle terminalPlugRight angle terminalSocket Straight terminalXC5M-1 DIN style 1XC5N DIN style 3XC5 Fine-fit (press-fit) ConnectorsConstruction of Solderless Connecting Part (Fine-fit Part)Cross SectionThe cross section is in the shape of the letter W.The two points on the bottom work as guide rails, preventing the pins from becoming twisted.The fin parts on the upper part change shape to fit into the through hole of the PCB.Designed for PCB surface mounting and ideal for automatic soldering.Corresponding to a stackingheight of 25, 30, or 35 mm.Press-fitted to PCBs and so soldering or cleaning is required.Mounting method more efficient than manual soldering.Ideal for backplane systems.XC5M DIN Connectors in 4 Lines with 128 Connector PolesMulti-pole connectors in 4 lines with 128 poles based on the DIN concept.XC6 Cable ConnectorsIdeal for connecting to a variety of bus lines for rack systems. Allow backplanes to be constructed with ease.Models with 96 connector poles and models with 64 connector poles and a center-holed construction are available.XC7 Sequence ConnectorsActive lines can be connected to daughter boards after connecting power lines, and can be disconnected before disconnecting the power lines. High reliability ensured with anengagement length of 4 mm and the durability to withstand 5,000 insertions. Three-step sequential operation.XC4 Mid- and High-current ConnectorsCarry 6 to 40 A for PCB-to-PCB or PCB-to-wire applications.*1*1(high frequency model available)Lineup includes versatile DIN models that meet internationalDIN standards, such as standard DIN, DIN-style, and DIN fine-fit models.These connectors meet a variety of industrial needs. A comprehensive selection of accessories are available.Connection Examples DIP ModelsA wide variety of DIN connectors are available in additionto the following models.Fine-fit (press-fit) Modelswith Multi-tier StackingA Wide Variety of High-density ConnectorsConform to International Standards, are Highly Reliable, and Support a Wide Range of ApplicationsNumber of contactsShape20,32,44,50,64,10020,32,44,50,64,10020,32,44,50,64,100Number of contacts Shape20,32,44,50,64,10032,48,64,9632,48,64,96Number of contactsShape48,64,9648,64,96Number of contactsShape20,24,26,30,32,44,50,60,64,90,10010*,14*,20,24*,30,32,40*,44,50,60,64,80,90,10020,30,32,40,44,50,60,64,90,10010,14,16,20,24,26,30,32,40,44,50,60,64,80,90,100Number of contacts Shape16,20,3264,9664,9664,96Number of contacts*1: Terminal type/ Straight, 4mm *2: Terminal type/ Straight, 13mm *3: Terminal type/ Straight, 17mm Shape32,64,10048,64,9648,64,9632,64,100Number of contactsShape128128Number of contacts Shape6496XC5 DIN ConnectorsXC5 DIN Connectors (4-Rows and 128 Contacts type)XC6 DIN Connectors (Cable Connecting type)XC5 DIN Connectors (Twin-contact Model)XC5 DIN Connectors (Fine-fit, W-shaped terminal type)XC5A 2-Row Plugs (DIN-B Standard Models)Straight terminal XC5B- 21Right angle terminal XC5A- 22Right angle terminal XC5F- 22Straight wrapping terminal XC5B- 23XC5B 2-Row Sockets (DIN-B Standard Models)XC5F 2-Row Sockets (DIN-Q Reverse Models)Straight terminal XC5G- 21Straight wrapping terminal XC5G- 23XC5G 3-Row Plugs (DIN-R Reverse Models)Right angle terminal XC5A- 82-1XC5A 2-Row Plugs (DIN Style 1)XC5K- 31-4A with 35-mm-pitch Straight terminal XC5K- 31-3A with 30-mm-pitch Straight terminal XC5K- 31-2A with 25-mm-pitch Straight terminalXC5K High-profile Stacking PlugsStraight terminalXC5B- 2P-1140 *1 XC5B- 2P-1131 *2 XC5B- 2P-1132 *3XC5B 2-Row Sockets (DIN-B Fine-fit, W-terminal Models)Straight terminalXC5E- 2P-1140 *1XC5E- 2P-1131 *2 XC5E- 2P-1132 *3XC5E 2-Row Plugs (DIN-Q Fine-fit, W-terminal Models)Straight terminalXC5D- 2P-1140 *1XC5D- 2P-1131 *2XC5D- 2P-1132 *3XC5D 3-Row Sockets(DIN-C Fine-fit, W-terminal Models)Straight terminalXC5G- 2P-1140 *1 XC5G- 2P-1131 *2XC5G- 2P-1132 *3XC5G 3-Row Plugs (DIN-R Fine-fit, W-terminal Models)Right angle terminal XC5C- 82-1XC5C 3-Row Plugs(DIN Style 1)Straight terminal XC5D- 31-0XC5D 3-Row Sockets (DIN Style Compatible)Right angle terminal XC5H- 32-1XC5H 3-Row Sockets(DIN Style 1)Straight terminalXC5B- 31-0(with coding key)XC5B- 31-3XC5B 2-Row Sockets(DIN-style Compatible Models)Straight terminal XC5E- 81-2 XC5E- 81-3 *XC5E 2-Row Plugs (DIN Style 2)Right angle terminal XC5F- 32-2XC5F 2-Row Sockets (DIN Style 2)Right angle terminal XC5H- 22XC5H 3-Row Sockets (DIN-R Reverse Models)Right angle terminal XC5C- 22XC5C 3-Row Plugs (DIN-C Standard Models)Straight terminal XC5D- 21Straight wrapping terminal XC5D- 23XC5D 3-Row Sockets (DIN-C Standard Models)Straight terminal XC5E- 21Straight wrapping terminal XC5E- 23XC5E DIP Plugs (DIN-Q Reverse Models)Standard DINRight angle type terminal XC5M-0222DIN StyleRight angle terminal XC5M-0222-1XC5M 4-Row PlugsSocketXC6D-6421Strain relief XC6T-644XC6D Center-holed 2-Row Flat Cables (DIN-C Models)SocketXC6H-9621Strain relief XC6T-644XC6H 3-Row Flat Cable (DIN-C Models)DIN Style 3Straight terminal XC5N-0221XC5N 4-Row SocketsOrdering InformationShapeXC6V DIN Connectors (IDC Connectors for Discretedwire)Unit housing XC6M-96Housing without contacts XC6T-32Number of contactsShape64,9664,9632,48Number of contactsShape32,483232Number of contactsShape1515ShapeXC2G 3-Row Plugs (DIN-R Reverse model)XC4A/BFXC4K/LHXC4M/NMXC4G/HDXC4E/FEStraight wrapping terminalXC2G- 13Straight terminalXC2G- 11Right angle terminalXC2H- 12XC2H 3-Row Sockets (DIN-R Reverse model)Wrapping terminalXC4F- 13Right angle terminalXC4G-3212XC4F Sockets (DIN-E)XC4G Plugs (DIN-D)Right angle terminalXC4K-1542XC4K Plugs (DIN-H)Plug with Solder Cup TerminalXC4W- 11Plug with L-shaped Solder TerminalXC4W-0412Receptacle withSolder Cup TerminalXC4W- 11with Fasten TerminalXC4L-1546XC4L Sockets(with Fastening Terminals)(DIN-H)Wrapping terminalXC4H-3213XC4H Sockets (DIN-D)XC4E Plugs (DIN-E)Right angle terminalXC4E- 1264Right angle terminalXC2F-6412XC2F 2-Row Sockets (DIN-Q Reverse model)Number of contactsShape64,9664Number of contactsShape64,90,100969664,90,100Number of contactsShape6464,9664XC7 DIN Socket Sequence Connectors XC4 DIN Connectors (Medium and High-current Connectors)XC2 DIN ConnectorsShapeDINModelsXC4 DIN typesXC4W Co-axial Contacts for XC4M/XC4NXC4W High-current Contacts (for XC4M/XC4N)Right angle terminalXC7A- 42-N001 *1XC7A- 42-N003 *2*1:N001 Normal *2:N003 SequenceXC7A 2-Row PlugsRight angle terminalXC2A-6412XC2A 2-Row Plugs (DIN-B standard models)Straight terminalXC2D- 11Straight wrapping terminalXC2D- 13XC2D 3-Row Sockets (DIN-C standard)Straight terminalXC2E-6411Straight wrapping terminalXC2E-6413XC2E 2-Row Plugs (DIN-Q Reverse model)ShapeXC4W-2111( 2.2)XC4W-2211( 3.2)XC4W-2014XC4W-3111( 2.2)XC4W-3211( 3.2)XC4W-3112( 2.2)XC4W-3212( 3.2)Right angle terminalXC2C- 12XC2C 3-Row Plugs (DIN-C standard models)Straight terminalXC2B-6411Straight wrapping terminalXC2B-6413XC2B 2-Row Sockets (DIN-B standard models)Straight terminalXC7B- 41-N001 *1XC7B- 41-N003 *2XC7B 2-Row SocketsRight angle terminalXC7C-9642-N001 *1XC7C-9642-N003 *2XC7C 3-Row PlugsStraight terminalXC7D-9641-N001 *1XC7D-9641-N003 *2XC7D 3-Row SocketsNumber of contactsShape4848Right angle terminalXC4A-4812XC4A Plugs (DIN-F)Straight terminalXC4B-4813XC4B Sockets (DIN-F)Wrapping terminalXC4B-481115Straight terminalXC4L-1541XC4L Sockets (DIN-H)Number of contacts*: contacts/ Number of signal circuit polesShape2/78, 4/60, 6/42 *2/78, 4/60, 6/42 *Number of contacts1,2,4411,12,14Right angle terminalXC4M- 12XC4M Plugs (DIN-M)Straight wrapping terminalXC4N- 13XC4N Sockets (DIN-M)Ordering Information。

红外报警主机说明书.

CVC064-C用户使用手册神州太讯安防总线报警系统说明CVC064-C通讯主机系统是具有很强的使用性被广泛地应用在小区住家及周界报警系统大楼安保系统、以及工厂学校仓储等各类大型安保系统可实现计算机管理并方便地与其它系统集成。

CVC064-C主要功能及性能指标一. 主要功能●最多可接520个防区:自身带有8个有线,通过通讯接口可以外接最多64个报警模块或者可独立布撤防的8防区小主机,每个输入设备最多可接8个防区●整个主机可以分为8个子系统,每个子系统相当于一台主机。

●外接的接警设备(报警模块或小主机)从000设备开始,按照地址码的顺序,最大64个设备,地址码是63,64号设备是主板自身8个防区。

每个键盘可以拥有其中的1个或多个设备,各键盘分别对自己的所管辖的所有设备同时进行布防、撤防等操作;键盘可以对单个设备、防区独立进行布防、撤防操作●可最多接入8个键盘,独立操作,汉字界面。

其中1个主键盘、7个从键盘,通过主键盘或管理密码编程可以让任意键盘跟随所有报警并显示报警信息●挂在通讯总线上的设备都可以带有1-32个输出,其中报警模块最多带有1个输出,32路指示灯最多可带4块指示灯板128路输出。

每个防区可以联动最多3个输出,联动包括:防区报警联动、防区布撤防联动、防区异常联动。

可以达到电子地图、DVR 报警输入、就地报警等功能●有3个密码权限,包括管理、编程、操作●可实现与中心计算机连接●可通过电话线与报警中心通过Contact ID协议连接,并可电话通知用户●通过键盘密码、遥控器、中心计算机、电话进行撤/布防●通过管理密码或者对主键盘(0号键盘)的撤布防,同时对所有键盘进行撤布防●通过键盘对单个分区、防区进行布撤防●通过键盘对联动设备单个或全部进行操作●通过电脑进行编程和配置。

可远程配置好,文件发送,就地写入主机,让编程和服务更为简单、有效。

二.电性能指标●输入电源AC16.5V●主机板耗电静态300mA●报警状态850mA●输出电源DC13.8V●报警输出口DC14V 800mA●外观尺寸350 x 280 x 75mm●键盘端口总线总长度不得大于1200m●通讯端口总线总长度每个接口不得大于1200m,两个接口最多可达2400m第一章. 系统配置及连线说明一. 主板接线端口定义及系统基本配置CVC064-C 通讯主机是一种大型的报警系统,它本身留有8个有线防区输入接口。

XC6106C645资料