Xilinx FPGA入门连载41:FT232串口芯片驱动安装

RS232 或 RS422驱动安装说明

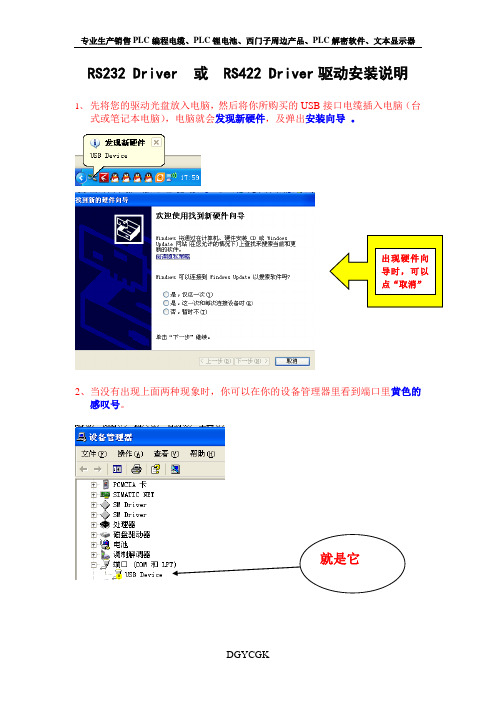

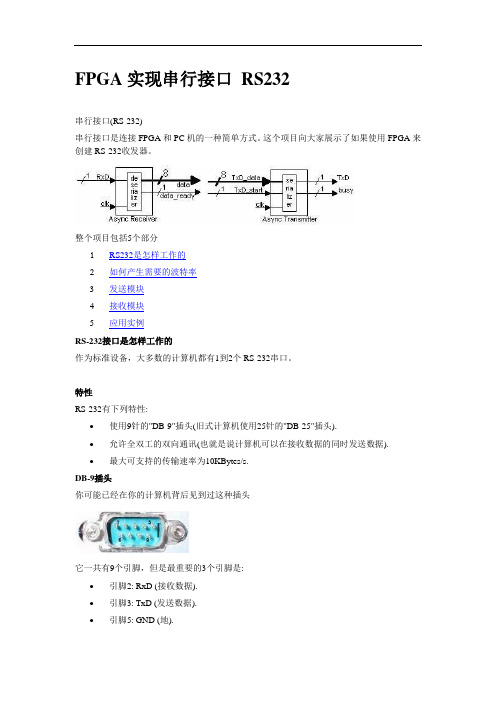

RS232 Driver 或 RS422 Driver驱动安装说明1、先将您的驱动光盘放入电脑,然后将你所购买的USB接口电缆插入电脑(台式或笔记本电脑),电脑就会发现新硬件,及弹出安装向导。

感叹号。

3、以上二种迹象都说明你的电缆已被电脑识别,你需要安装驱动,打开光盘里的RS232或RS422文件,点击SETUP.EXE 安装,即会出来“图片2”所示。

图片1图片24、点击即可,等到出现以下显示时,恭喜你,你的驱动已安装成功!5、这时回到你的“设备管理器”里就可以在“端口”里面看到电缆生成的新串口了。

6、然后你需要在PLC编程软件里把端口改成电缆生成的新串口即可使用。

完7、如何改变COM口号有些早期的应用软件支持的串口数量是有限的,如某PLC编程软件支持的串口号为COM1~COM4,由于安装USB编程电缆之前已安装了其它的USB转换设备,安装USB编程电缆驱动程序后在设备管理器中显示该电缆地址为COM5,这样一来编程软件就无法访问该COM口。

这时候就需改变编程电缆的COM口号,方法如下:1、如何找到端口位置1、在Windows2000/XP系统中可直接更改COM口号,首先安装好以上驱动后,点击桌面“我的电脑”右键属性→“硬件”→“设备管理器”→即可看到“端口”。

2如果修改端口1这里以COM5为例:找到端口后,点“COM5口”→右键属性→“端口设置或Parametres du port”→“高级或Avance”即可看到,选择对应的COM1口即可。

小提示在这里修改端口即可,其它设置不要动它小提示在这里修改端口即可,其它设置不要动它这里需要注意的是:如果你的电脑本身有COM1口,你不可以把端口改成重复的COM口。

最新fpga实现串行接口 rs232资料讲解

FPGA实现串行接口RS232串行接口(RS-232)串行接口是连接FPGA和PC机的一种简单方式。

这个项目向大家展示了如果使用FPGA来创建RS-232收发器。

整个项目包括5个部分1RS232是怎样工作的2如何产生需要的波特率3发送模块4接收模块5应用实例RS-232接口是怎样工作的作为标准设备,大多数的计算机都有1到2个RS-232串口。

特性RS-232有下列特性:•使用9针的"DB-9"插头(旧式计算机使用25针的"DB-25"插头).•允许全双工的双向通讯(也就是说计算机可以在接收数据的同时发送数据).•最大可支持的传输速率为10KBytes/s.DB-9插头你可能已经在你的计算机背后见到过这种插头它一共有9个引脚,但是最重要的3个引脚是:•引脚2: RxD (接收数据).•引脚3: TxD (发送数据).•引脚5: GND (地).仅使用3跟电缆,你就可以发送和接收数据.串行通讯数据以每次一位的方式传输;每条线用来传输一个方向的数据。

由于计算机通常至少需要若干位数据,因此数据在发送之前先“串行化”。

通常是以8位数据为1组的。

先发送最低有效位,最后发送最高有效位。

异步通讯RS-232使用异步通讯协议。

也就是说数据的传输没有时钟信号。

接收端必须有某种方式,使之与接收数据同步。

对于RS-232来说,是这样处理的:6串行线缆的两端事先约定好串行传输的参数(传输速度、传输格式等)7当没有数据传输的时候,发送端向数据线上发送"1"8每传输一个字节之前,发送端先发送一个"0"来表示传输已经开始。

这样接收端便可以知道有数据到来了。

9开始传输后,数据以约定的速度和格式传输,所以接收端可以与之同步10每次传输完成一个字节之后,都在其后发送一个停止位("1")让我们来看看0x55是如何传输的:0x55的二进制表示为:01010101。

FPGA软件的安装说明

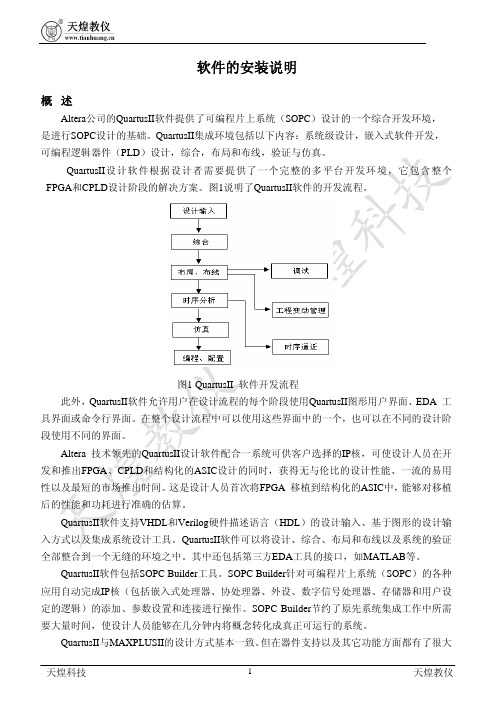

软件的安装说明概 述Altera公司的QuartusII软件提供了可编程片上系统(SOPC)设计的一个综合开发环境, 是进行SOPC设计的基础。

QuartusII集成环境包括以下内容:系统级设计,嵌入式软件开发, 可编程逻辑器件(PLD)设计,综合,布局和布线,验证与仿真。

QuartusII设计软件根据设计者需要提供了一个完整的多平台开发环境,它包含整个 FPGA和CPLD设计阶段的解决方案。

图1说明了QuartusII软件的开发流程。

图1 QuartusII 软件开发流程 此外,QuartusII软件允许用户在设计流程的每个阶段使用QuartusII图形用户界面、EDA 工 具界面或命令行界面。

在整个设计流程中可以使用这些界面中的一个,也可以在不同的设计阶 段使用不同的界面。

Altera 技术领先的QuartusII设计软件配合一系统可供客户选择的IP核,可使设计人员在开 发和推出FPGA、CPLD和结构化的ASIC设计的同时,获得无与伦比的设计性能、一流的易用 性以及最短的市场推出时间。

这是设计人员首次将FPGA 移植到结构化的ASIC中, 能够对移植 后的性能和功耗进行准确的估算。

QuartusII软件支持VHDL和Verilog硬件描述语言(HDL)的设计输入、基于图形的设计输 入方式以及集成系统设计工具。

QuartusII软件可以将设计、综合、布局和布线以及系统的验证 全部整合到一个无缝的环境之中。

其中还包括第三方EDA工具的接口,如MATLAB等。

QuartusII软件包括SOPC Builder工具。

SOPC Builder针对可编程片上系统(SOPC)的各种 应用自动完成IP核(包括嵌入式处理器、协处理器、外设、数字信号处理器、存储器和用户设 定的逻辑)的添加、参数设置和连接进行操作。

SOPC Builder节约了原先系统集成工作中所需 要大量时间,使设计人员能够在几分钟内将概念转化成真正可运行的系统。

大作业RS232串口驱动

大作业:RS232串口驱动Verilog设计实验报告计算机学院1203121857闫林周六晚上机——第五批1.1 实验内容本实验要为最后一次大实验。

为自选实验。

本人选择驱动Terasic DE0开发板上的RS232串口作为最后一次大的作业。

本实验使用友晶科技的De0开发板进行实验。

使用cyclone III EP3C16F484 FPGA芯片。

1.2 试验要求使用Verilog语言驱动开发板上的rs232模块,使之能够与计算机进行通信。

串口的通信速率设为9600HZ,每次传送8bit,没有校验位,空闲位的长度为1。

1.3 设计说明RS232使用如下的电平标准进行通信。

图1 RS232通信协议空闲状态下,电路一直保持低电平,当有数据需要发送时,电平拉高一个周期。

接下来为8个数据位,最后为一个周期的结束低电平。

这一过程可以用状态机进行表示。

由于DE0开发版的空间有限,所以并没有RS232使用的标准DB9口只保留了引脚进行使用。

因此试验中使用到了USB转TTL的转换线进行与计算机的连接。

如下图所示。

在试验过程中,为简便实验的实现过程,只是用了发送(TXD)和接收(TXD)两条线。

也就是下图中的第2、3两根线。

为了验证程序的正确性,程序将接收到的数据传送到发送端。

因此,在FPGA开发板和计算机之间形成了一个回环的网络。

网络拓补如下图所示:1.4 源程序顶层测试模块:module rs232_tb (input CLK_50M,input RX,output TX,output[9:0] LEDG);wire rx_vld;wire[7:0] rx_data;assign LEDG[7:0]= rx_data[7:0];assign LEDG[9]= rx_vld;RS232_RX #(.baud(9600),.mhz(50)) rx_232(.clock(CLK_50M),.reset(0),.RS232_DCE_RXD(RX),.rx_vld(rx_vld),.receive_data(rx_data));wire tx_vld;wire[7:0] tx_data;assign tx_vld = rx_vld;assign tx_data = rx_data;RS232_TX #(.baud(9600),.mhz(50)) tx_232(.clock(CLK_50M),.reset(0),.RS232_DCE_TXD(TX),.tx_vld(tx_vld),.transmit_data(tx_data),.tx_rdy(LEDG[8]));endmodule发送模块:module RS232_TX#(parameter baud = 9600, mhz = 50)(input clock,input reset,output reg RS232_DCE_TXD,input[7:0] transmit_data,input tx_vld,output reg tx_rdy);parameter txd_bit_per =(mhz*1_000_000)/baud;//--State Definitions--parameter st_ready = 2'b00;parameter st_start_bit = 2'b01;parameter st_data_bits = 2'b10;parameter st_stop_bit = 2'b11;reg[1:0] state = st_ready;reg[1:0] n_state = st_ready;reg[31:0] counter;reg[31:0] n_counter;reg[2:0] data_bit_count;reg[2:0] n_data_bit_count;reg[7:0] tx_data;//transmit procalways@(*)beginn_state <= state;n_counter <= counter;n_data_bit_count <= data_bit_count;if(reset == 1'b1)RS232_DCE_TXD <= 1'b0;elsecase(state)st_ready:beginif(tx_vld == 1'b1)begintx_rdy <= 1'b0;tx_data <= transmit_data;n_state <= st_start_bit;endelse beginRS232_DCE_TXD <= 1'b0;tx_rdy <= 1'b1;n_state <= st_ready;n_counter <= 0;n_data_bit_count <= 0;endendst_start_bit:beginif(counter == txd_bit_per)beginn_counter <= 0;n_state <= st_data_bits;n_data_bit_count <= 0;endelse beginRS232_DCE_TXD <= 1'b1;n_state <= st_start_bit;n_counter <= counter + 1;endendst_data_bits:beginif(counter == txd_bit_per)beginn_counter <= 0;n_data_bit_count <= data_bit_count + 1;if(data_bit_count == 7)beginn_state <= st_stop_bit;end elsen_state <= st_data_bits;endelse beginn_counter <= counter + 1;RS232_DCE_TXD <=~tx_data[data_bit_count];n_state <= st_data_bits;endendst_stop_bit:beginif(counter == txd_bit_per)n_state <= st_ready;else beginRS232_DCE_TXD <= 1'b0;n_state <= st_stop_bit;n_counter <= counter + 1;endendendcaseend//clock procalways@(posedge clock or posedge reset)beginif(reset == 1)beginstate <= st_ready;counter <= 0;data_bit_count <= 0;endelse beginstate <= n_state;counter <= n_counter;data_bit_count <= n_data_bit_count;endendendmodule接收模块:module RS232_RX#(parameter baud = 9600, mhz = 50)(input clock,input reset,input RS232_DCE_RXD,output[7:0] receive_data,output reg rx_vld);parameter rcv_bit_per =(mhz*1_000_000)/baud; parameter half_rcv_bit_per = rcv_bit_per/2;//--State Definitions--parameter st_ready = 2'b00;parameter st_start_bit = 2'b01;parameter st_data_bits = 2'b10;parameter st_stop_bit = 2'b11;reg[31:0] counter;reg[31:0] n_counter;reg[2:0] data_bit_count;reg[2:0] n_data_bit_count;reg[7:0] rcv_sr;reg[7:0] n_rcv_sr;reg[1:0] state;reg[1:0] n_state;assign receive_data = rcv_sr;//receive procalways@(*)beginn_rcv_sr <= rcv_sr;n_state <= state;n_counter <= counter;n_data_bit_count <= data_bit_count;rx_vld <= 0;if(reset == 1)n_rcv_sr <= 0;elsecase(state)st_ready:beginn_counter <= 0;n_data_bit_count <= 0;if(RS232_DCE_RXD == 1)n_state <= st_start_bit;endst_start_bit:beginif(counter == half_rcv_bit_per)beginn_counter <= 0;n_state <= st_data_bits;n_data_bit_count <= 0;endelse beginn_counter <= counter + 1;endendst_data_bits:beginif(counter == rcv_bit_per)beginn_counter <= 0;n_rcv_sr <={~RS232_DCE_RXD, rcv_sr[7:1]};n_data_bit_count <= data_bit_count + 1;if(data_bit_count == 7)beginrx_vld <= 1'b1;n_state <= st_stop_bit;endendelsen_counter <= counter + 1;endst_stop_bit:beginif(counter ==rcv_bit_per)//should be 1/2 stop_bit periodn_state <= st_ready;elsen_counter <= counter + 1;endendcaseend//clock procalways@(posedge clock or posedge reset)beginif(reset == 1)beginstate <= st_ready;rcv_sr <= 0;counter <= 0;data_bit_count <= 0;endelse beginstate <= n_state;rcv_sr <= n_rcv_sr;counter <= n_counter;data_bit_count <= n_data_bit_count;endendendmodule1.5 程序结果使用USB转串口TTL线进行连接之后,就可以进行数据传送接收的验证。

串口RS232教程

•

RS232、RS485、RS422的区别

1.传输电缆长度 • RS-232一般用于20m以内的通信。

• RS422和RS485在19kpbs下能传输1200米。

2.工作方式 • RS232是单端输入输出,双工工作时至少需要数字地线 。发送线和接受线三条线(异步 传输),还可以加其它控制线完成同步等功能。 存在共地噪声和不能抑制共模干扰等问题。

• 4. RS-485接口的最大传输距离标准值为4000英尺,

实际上可达 3000米,另外RS-232-C接口在总线上 只允许连接1个收发器, 即单站能力。而RS-485 接口在总线上是允许连接多达128个收发器。即具 有多站能力,这样用户可以利用单一的RS-485接口 方便地建立起设备网络。 5.因RS-485接口具有良好的抗噪声干扰性,长的 传输距离和多站能力等上述优点就使其成为首选 的串行接口。 因为RS485接口组成的半双工网络, 一般只需二根连线,所以RS485接口均采用屏蔽 双绞线传输。 RS485接口连接器采用DB-9的9芯 插头座,与智能终端RS485接口采用DB-9(孔)。

RS232、RS485、RS422

简明教程

串行通讯概述

• 串行通讯协议有很多种,像RS232,RS485,

RS422,甚至现今流行的USB等都是串行通讯协议。 而串行通讯技术的应用无处不在。可能大家见的 最多就是电脑的串口与Modem的通讯。记得在PC 机刚开始在中国流行起来时(大约是在90年代前五 年),那时甚至有人用一条串行线进行两台电脑之 间的数据共享。除了这些,手机,PDA,USB鼠标、 键盘等等都是以串行通讯的方式与电脑连接。而 我们工作性质的关系,所接触到的就更多了,像 多串口卡,各种种类的具有串口通讯接口的检测 与测量仪器,串口通讯的网络设备等。

RS232安装说明

选择:从列表或指定位置安装,单击下一步,

选择:不要搜索,我要自己选择要安装的驱动程序.单击下一步,

选择:从磁盘安装,打开浏览,从驱动盘中找到hidcom.INF文件,打开,单击确定,

选择下一步,此时系统会提示微软的数字签证,选择仍然继续,单击完成。

2、在WinXP系统中:安装HIDCOM driver可能失败

先插上USB线,进入设备管理器,在“人体学输入设备”一栏中可以看到

“HID-compliant Device”和“USB人体学输入设备”

(在此之前请确认已经移去所有其他“USB人体学输入设备”),

在“HID-compliant Device”上点击鼠标右键:

在“USB人体学输入设备”上点击鼠标右键:

选择:更新驱动程序

选择:从列表或指定位置安装,单击下一步,

选择:不要搜索,我要自己选择要安装的驱动程序.单击下一步,

选择:从磁盘安装,打开浏览,从驱动盘中找到hidcom.INF文件,打开,单击确定,

选择下一步,此时系统会提示微软的数字签证,选择仍然继续,单击完成。

3.Select Update Driver

4.Select"Install from list from specific location" and click Next

5.De-select"Search removable media",Then select"Include this location in Search".

8.Select"SemiTech USB-HID->COM device" and click Next.

小梅哥和你一起深入学习FPGA之串口调试(一)

小梅哥和你一起深入学习FPGA之串口调试(一)大家好,这几天在各个论坛上,经常就有人在向我咨询基于FPGA的串口通信代码,大部分都是在网上下载一个现成的代码,但是在使用中就遇到了各种问题,于是就发到了论坛上来求助。

在阅读了他们的代码之后,我发现几乎出自同一个版本(目前确定为特权同学的基于EPM240入门实验的代码)。

他们在调试这个代码的时候,经常存在这样几个问题:1、部分人对该串口通讯模块完全不理解,对每句话,甚至每个模块的功能都不理解;2、部分人采用最原始的画波形的方式来对该模块进行仿真,结果无法得到仿真结果;3、部分人不会使用modelsim对该设计进行仿真;4、绝大部分人不会编写testbench;5、下板测试无法进行正确的字符串收发。

在公司内部,我将这种现象和几位老师交流之后,夏宇闻老师建议我专门针对该代码写一个由原理到代码,由仿真到板级的调试笔记。

争取用最通俗,也是最笨的办法,手把手的教会大家来调试这个代码。

本调试笔记主要由五个部分组成:原始代码分析;原始代码验证;对原始代码进行修改;对修改后的代码进行验证;对修改后的设计进行板级验证。

每个部分,小梅哥都会用图文结合的方式,教大家一步一步的来进行。

一、原始代码分析该代码来自小梅哥最崇拜的大神,特权同学。

当时小梅哥也是看着特权同学的书和视频教程一步一步走过来的。

特权同学的代码实现了单字节的收发测试,没有对连续字节的收发进行测试。

特权同学当时也说过,这个只是一个简单的实验,离实际工业应用还有一定的距离。

考虑到论坛上很多小伙伴都希望能够实现连续字节的收发功能,因此小梅哥就在特权同学的代码上进行了修改。

修改后的代码,输入时钟可以在一定范围内选择任意频率,目前已经支持5种波特率选择(9600、19200、38400、57600、115200),实际小梅哥还做过更高波特率的测试,目前实测在115200波特率的速率下可以实现超过9999999次连续无间断的收发。

单片机rs232串口通信完美解析

单片机rs232串口通信完美解析

在制作电路前我们先来看看要用的MAX232,这里我们不去具体讨论它,只要知道它是TTL 和RS232 电平相互转换的芯片和基本的引脚接线功能就行了。

通常我会用两个小功率晶体管加少量的电路去替换MAX232,可以省一点,效果也不错(如有兴趣可以查看cdle 网站中的相关资料)。

下图就是MAX232 的基本接线图。

图7-1MAX232

在上两课的电路的基础上按图7-3 加上MAX232 就可以了。

P 串口座

用DB9 的母头,这样就可以用买来的PC 串口延长线进行和电脑相连接,也可以直接接到电脑com 口上。

图7-3加上了MAX232 的实验电路做好后我们就先用回第一课的”Hello World!”程序,用它来和你的电脑说声Hello!把程序烧到芯片上,把串口连接好。

嘿嘿,这时要打开你的串口调试软件,没有就赶快到网上DOWN 一个了。

你会用Windows 的超级中端也行,不过我从不用它。

我用emouze 的comdebug,它是个不错的软件,我喜欢它是因为它功能好而且还有”线路状态”功能,这对我制作小玩意时很有用。

串口号,波特率调好,打开串口,单片机上电,就可以在接收区看到不断出现的”Hello World!”。

一定要先打开软件的串口,再把单片机上电,否则可能因字符不对齐而看到乱码哦。

tips:感谢大家的阅读,本文由我司收集整编。

仅供参阅!。

fpga软件的使用流程

FPGA软件的使用流程1. 准备工作在开始使用FPGA软件之前,需要完成以下准备工作:•安装FPGA软件:根据硬件型号和供应商提供的资料,下载并安装相应的FPGA软件。

常见的FPGA软件包括Xilinx ISE、Altera Quartus等。

•学习基础知识:了解FPGA的基本原理,掌握HDL(硬件描述语言)的知识,例如Verilog或VHDL。

同时,理解FPGA的架构和工作流程也是必要的。

2. 创建新工程在使用FPGA软件之前,首先需要创建一个新的工程。

按照以下步骤进行:1.打开FPGA软件:双击桌面上的应用程序图标或通过开始菜单打开相应的应用程序。

2.选择“创建新工程”:在软件界面上找到“新建工程”或类似的选项,点击进入新工程界面。

3.命名工程:为工程命名,选择保存路径,并指定工程的类型(例如Xilinx或Altera)。

4.选择设备型号:根据所使用的FPGA硬件,选择相应的设备型号。

如果不清楚型号,可以参考FPGA供应商的技术手册或官方网站。

3. 设计RTL电路RTL(Register Transfer Level)是描述数字电路的一种方法,FPGA软件可以通过RTL描述用户的电路设计。

在设计RTL电路时,可以按照以下步骤进行:1.打开设计视图:在FPGA软件界面中,找到“设计视图”或类似选项,打开RTL设计界面。

2.添加模块:在设计界面上,选择“添加模块”或类似选项,将所需的模块添加到设计中。

3.连接模块:使用软件提供的连接工具,将各模块按照设计要求连接起来。

4.编写HDL代码:使用HDL语言(如Verilog或VHDL),编写每个模块的逻辑代码。

5.进行仿真:使用软件提供的仿真工具,对设计的RTL电路进行仿真验证。

4. 进行综合在完成RTL电路设计后,需要进行综合(Synthesis)操作,将RTL代码转化为FPGA支持的逻辑元件。

按照以下步骤进行:1.打开综合工具:在FPGA软件界面中,找到“综合”或类似选项,打开综合工具。

vivado入门教程-峰哥版

Xilinx zynq 7010clg400-1 sopc 基于zybo开发板之gpio使用Vivado 2015.4SDK 2015.4如峰2016年6月7日20:10:33目录Vivado 搭建底层硬件系统 (4)二、sdk使用 (26)三、总结 (38)附录程序 (38)Vivado 搭建底层硬件系统首先使用vivado搭建一个底层硬件系统,具体操作过程如下,用图的方式来说明,直观方便打开vivado 2015.4 如下单击create new project,如下图,单击next继续单击next,如下如,解释一下1:工程的名字2:工程在电脑中的位置,不要中文,不要空格3:打上勾表示在2的位置基础上创建一个子目录,不勾就表示不创建,我一般都是按大类来分,比如米尔的文件夹,zingsk的文件夹,zybo的文件夹,所以我都勾上,我的位置如下图设置好了之后继续单击next,这里是说创建一个什么养的工程一般都是rtl的工程,其他的我还没研究过,直接看官方文档学的,做fpga或者soc,sopc,都是rtl工程。

这里也有个可以勾选的地方,勾上的意思是现在不指定源文件,如果不够上,就进入具体设置,有硬件语言的类型,ip的选择,and so on ,可以自己去看看,建议勾选,这些可以在工程中设置的,没有必要提前设置单击next这里面可选的就很多了,从上到下,从左到右简单的说下Part和board分别指的是单个芯片和官方或者安富利的板子下面的这些是指fpga的类和速度和温度,左后的search,是你之前用过的芯片的记录或者直接收你想要的芯片名字,第一次选好,以后直接到search中选就行这个是zybo的板子的芯片型号,或者在board中直接选zybo,继续单击next,一个summary继续单击next,vivado给咱们创建工程创建好了就是这个样子,一个空的工程接下来我们要建立一个空的图片,用来搭建zynq的底层,单击箭头指的地方会出现下图这样这个表示设计的名字和存储的路径,一般都是系统,我习惯于功能加系统的方式命名,比如这次是对gpio进行操作,我会做gpio_sys,然后单击ok接下来我们来添加zynq的ps,单击,或者单击,再或者crtl + I 出现这个图我们在search这输入zynq,选择第一个,单击左键或者回车,都行,下面的那个好像是microblaze,没用过,以后再研究,好像类似于nios(这块我不确定,可以忽略不记)完了是这个样子的双击zynq如图,配置zynq,这里是重点,详细说起来很多,可以参考ug585,我现在也没有全搞明白,也是觉得哪里不对去文档里找,那个文档1800多页,细读完了一定会忘,不如用哪看哪(个人观点)配置完是这样单击run block automtian完了是这样的,把ddr和fix——io引出来了接下来就是本文重点,开始添加gpio的ip双击配置gpio的ip,简单改一下ip的位宽,单击ok然后直接单击如图然后在导航栏,点source右键gpio_sys单击create hdl wapper单击ok上面的那个是手动,后面让eda自动updata,选下面的就好,单击ok在左侧的导航栏中,单击箭头指的位置生成一些ip的约束,单击genrate等一会单击ok,然后编译,等着如果之前忘了保存,这时候会弹出保存的,选save一段漫长的等待之后,分配管教,指定电平水平LMOS33 然后这样,先不要综合,没有分配管教在这点这个然后在这选layout然后选ioplane单击之后如下图分配完了,ctrl + s 点ok设置一个名字可以叫pin_location然后综合然后生成bit文件这个bit文件可以生成,也可以不生成,取决于有没有pl,有的话就要生成bit文件这两个过程很长时间!!!!!!!最后好了单击okVivado的工作要完成了,就剩最后两步File –》export export hardware如下图单击ok最后file –》lanch sdk,vivado的工作就完成了二、sdk使用File—》new—》baord suport package默认选项就行单击finish如下图,再单击finish左边多了一个bsp的文件夹在这里有我们想要用的函数和一些参数信息今天这个是gpio的,主要这个两个函数头文件再建一个应用工程然后起名子,短则刚才建立bsp生成的bsp Next,选helloword工程单击finish多了一个工程接下来就可以写程序了展开这个gpio的工程打开如图接下来我们先写程序,要讲三个函数1.gpio初始化函数2.gpio数据方向设置函数3.gpio写数据函数有关gpio大概有十二三个函数,在bsp→include→xgpio.h下,在crtl+左键,进入xgpio.c 讲的很详细,不过是英语的,如图这是讲初始化函数的我先说这几个参数什么意思,再说怎么用首先int Xgpio_Initialize(Gpio*inr,u16 DeviceID);这个函数是有返回值的,返回一个int型,0和1其中0:XST_SUCCESS,1:XTS_DEVICE_NOT_FOUND写程序的时候可以直接判断一个变量比如if(a == XST_SUCCESS or XTS_DEVICE_NOT_FOUND ){}或者if(a==0 or 1){}前面的指针变量是指向某个gpio的,该gpio在xilinx中被定义为Xgpio类型的变量,后面的device id 表示你要初始化的具体的gpio,这个id在bsp→include→xparameters.h下,比如在这里可以对这些代码进行更改,如果觉得名字太长的话。

GB PPI-FT232 编程电缆说明书

PPI-FT232编程电缆1.产品概述:感谢使用工贝电子GB PPI-FT232编程电缆,为充分发挥本产品的性能和设备安全,请仔细阅读本手册。

GB PPI-FT232是一款满足大多数客户需求的,高可靠性、高性价比的S7-200PLC专用编程电缆,采用行业公认的最可靠的进口芯片FT232RL,完美解决USB口插拔多次后无法识别,下载过程出错,使用寿命短等缺陷,比CH340方案更加稳定可靠。

支持9600,19200波特率,支持PPI、Modbus、自由口等通讯协议。

2.布局说明:USB一端连电脑或触摸屏,内部蓝色电源指示灯亮起;PPI一端连PLC;RX为接收指示灯;TX为发送指示灯。

3.安装驱动:3.1下载解压缩《【工贝电子】GB PPI-FT232编程电缆驱动.rar》到桌面即可。

将编程电缆USB端连接电脑,编程电缆正面蓝色电源灯亮,电脑右下角会提示有些电脑非常智能,能通过互联网搜索到驱动,耐心等待1分钟,如果自动安装失败,我们就手动添加驱动。

3.2打开设备管理器(在我的电脑右键点管理,左侧栏点设备管理器),下图红框中带叹号的就是编程电缆。

3.3右击上图中无法识别的设备,选择“更新驱动程序软件”,选中桌面解压好的文件夹,点下一步,再看设备管理器界面,叹号消失了,在端口一栏增加了设备,表示驱动安装完成。

如下图,表示驱动安装成功。

3.4修改COM口号:细心的同学发现上图中端口号是27,S7软件是不能支持大序号的COM,要改小,打开设备管理器。

5.S7软件设置:4.1打开“设置PG/PC接口”界面,如下图。

4.2搜索设备。

在通信窗口中双击刷新。

4.3电脑显示有个搜索过程,PLC出厂是默认地址为2,波特率9600,如下图所示,即表示连接成功。

如果搜索出来的PLC没有显示型号,显示Unknown,属于正常现象,国产编程线固有的毛病,不影响使用。

5.常见问题:5.1设置不成功,或者总是弹“错误框”,电脑提示RPC错误。

fpga串口通信的verilog驱动

fpga串⼝通信的verilog驱动 串⼝的全程为串⾏接⼝,也称为串⾏通信接⼝,是采⽤串⾏通信⽅式的扩展接⼝。

与串⼝对应的并⾏接⼝,例如⾼速AD和DA,这些都是⽤的并⾏接⼝,⽽且在编程也简单⼀些。

串⼝有⼀下特点: (1)通信线路简单,只要⼀对传输线就可以实现双向通信。

(2)布线简单,成本低。

(3)通信距离长,可以实现数⽶到数千⽶的通信距离。

(4)传输速率慢。

常见的串⼝速率如4800 , 9600 , 115200bps,代表每秒钟发送多少bit数据,例如9600bps就代表1秒内发送9600bit数据。

串⼝协议:协议⽐较简单,⼀般都是10位数据,1个起始位低电平,然后⼋个数据位,低位在前,⼀个奇偶校验位,平时⼀般不⽤,最后是⼀位停⽌位⾼电平,这样⼀帧数据发送结束。

下⾯介绍⼀下我的程序框架: 整体框架分为两个部分:⼀个是串⼝驱动部分另⼀个是串⼝数据控制部分。

串⼝驱动部分负责串⼝驱动和波特率的选择,串⼝数据控制模块 负责控制数据内容的控制和发送速度的控制。

从上⾯时序图可以看出,每10ms发送⼀帧数据,这⾥data_en负责波特率驱动使能,uart_tx_end有两个功能,⼀个是关闭data_en使能,另⼀个是给10ms计数器清零。

/*-----------------------------------------------------------------------Date : 2017-09-03Description : Design for uart_driver.-----------------------------------------------------------------------*/ module uart_tx_driver(//global clockinput clk , //system clock input rst_n , //sync reset//uart interfaceoutput reg uart_tx ,//user interfaceinput [1:0] bps_select , //波特率选择input [7:0] uart_data ,input data_en , //发送数据使能output reg uart_tx_end);//--------------------------------//Funtion : 参数定义parameter BPS_4800 = 14'd10417 ,BPS_9600 = 14'd5208 ,BPS_115200 = 14'd434 ;reg [13:0] cnt_bps_clk ;reg [13:0] bps ;reg bps_clk_en ; //bps使能时钟reg [3:0] bps_cnt ;wire [13:0] BPS_CLK_V = bps >> 1 ;//--------------------------------//Funtion : 波特率选择always @(posedge clk or negedge rst_n)beginif(!rst_n)bps <= 1'd0;else if(bps_select == 2'd0)bps <= BPS_115200;else if(bps_select == 2'd1)bps <= BPS_9600;elsebps <= BPS_4800;end//--------------------------------//Funtion : 波特率计数always @(posedge clk or negedge rst_n)beginif(!rst_n)cnt_bps_clk <= 1'd0;else if(cnt_bps_clk >= bps - 1 && data_en == 1'b0)cnt_bps_clk <= 1'd0;elsecnt_bps_clk <= cnt_bps_clk + 1'd1;end//--------------------------------//Funtion : 波特率使能时钟always @(posedge clk or negedge rst_n)beginif(!rst_n)bps_clk_en <= 1'd0;else if(cnt_bps_clk == BPS_CLK_V - 1)bps_clk_en <= 1'd1;elsebps_clk_en <= 1'd0;end//--------------------------------//Funtion : 波特率帧计数always @(posedge clk or negedge rst_n)beginif(!rst_n)bps_cnt <= 1'd0;else if(bps_cnt == 11)bps_cnt <= 1'd0;else if(bps_clk_en)bps_cnt <= bps_cnt + 1'd1;end//--------------------------------//Funtion : uart_tx_endalways @(posedge clk or negedge rst_n)beginif(!rst_n)uart_tx_end <= 1'd0;else if(bps_cnt == 11)uart_tx_end <= 1'd1;elseuart_tx_end <= 1'd0;end//--------------------------------//Funtion : 发送数据always @(posedge clk or negedge rst_n)beginif(!rst_n)uart_tx <= 1'd1;else case(bps_cnt)4'd0 : uart_tx <= 1'd1;4'd1 : uart_tx <= 1'd0; //begin4'd2 : uart_tx <= uart_data[0];//data4'd3 : uart_tx <= uart_data[1];4'd4 : uart_tx <= uart_data[2];4'd5 : uart_tx <= uart_data[3];4'd6 : uart_tx <= uart_data[4];4'd7 : uart_tx <= uart_data[5];4'd8 : uart_tx <= uart_data[6];4'd9 : uart_tx <= uart_data[7];4'd10 : uart_tx <= 1; //stopdefault : uart_tx <= 1;endcaseendendmodule/*-----------------------------------------------------------------------Date : 2017-XX-XXDescription : Design for .-----------------------------------------------------------------------*/module uart_tx_control(//global clockinput clk , //system clockinput rst_n , //sync reset//user interfaceoutput reg [7:0] uart_data ,output reg data_en ,input uart_tx_end);//--------------------------------//Funtion : 参数定义parameter DELAY_10MS = 500_000 ;reg [31:0] cnt_10ms ;wire delay_10ms_done ;//data definereg [31:0] cnt_1s;//--------------------------------//Funtion : cnt_10msalways @(posedge clk or negedge rst_n)beginif(!rst_n)cnt_10ms <= 1'd0;else if(cnt_10ms == DELAY_10MS - 1 && uart_tx_end == 1'd1)cnt_10ms <= 1'd0;elsecnt_10ms <= cnt_10ms + 1'd1;endassign delay_10ms_done = (cnt_10ms == DELAY_10MS - 1) ? 1'd1 : 1'd0; //--------------------------------//Funtion : data_enalways @(posedge clk or negedge rst_n)beginif(!rst_n)data_en <= 1'd0;else if(delay_10ms_done)data_en <= 1'd1;else if(uart_tx_end)data_en <= 1'd0;end///////////////////////数据测试///////////////////////////////--------------------------------//Funtion : cnt_1salways @(posedge clk or negedge rst_n) beginif(!rst_n)cnt_1s <= 1'd0;else if(cnt_1s == 49_999_999)cnt_1s <= 1'd0;elsecnt_1s <= cnt_1s + 1'd1;end//--------------------------------//Funtion : uart_dataalways @(posedge clk or negedge rst_n) beginif(!rst_n)uart_data <= 1'd0;else if(uart_data >= 10)uart_data <= 1'd0;else if(cnt_1s == 49_999_999)uart_data <= uart_data + 1'd1; endendmodule。

FPGA串口通信

FPGA实现RS-232串口收发的仿真过程(Quartus+Synplify+ModelSim)(2007-09-11 12:17:37)网上关于RS-232的异步收发介绍得很多,最近没事学着摸索用ModelSim来做时序仿真,就结合网上的参考资料和自己的琢磨,做了这个东西。

针对我这个小程序结合FPGA的开发流程,主要走了以下几步:1. 文本程序输入(Verilog HDL)2. 功能仿真(ModelSim,查看逻辑功能是否正确,要写一个Test Bench)3. 综合(Synplify Pro,程序综合成网表)4. 布局布线(Quartus II,根据我选定的FPGA器件型号,将网表布到器件中,并估算出相应的时延)5. 时序仿真(ModelSim,根据时延做进一步仿真)这里贴出我的程序和各个详细步骤,能和各位正在学习的新手们一起分享。

0. 原理略一、文本程序输入(Verilog HDL)发送端:module trans(clk,rst,TxD_start,TxD_data,TxD,);input clk,rst,TxD_start;input[7:0] TxD_data;// 待发送的数据output TxD,// 输出端口发送的串口数据TxD_busy;reg TxD;reg [7:0]TxD_dataReg;// 寄存器发送模式,因为在串口发送过程中输入端不可能一直保持有效电平reg [3:0]state;parameter ClkFrequency = 25000000;// 时钟频率-25 MHzparameter Baud = 115200;// 串口波特率-115200// 波特率产生parameter BaudGeneratorAccWidth = 16;reg[BaudGeneratorAccWidth:0] BaudGeneratorAcc;wire [BaudGeneratorAccWidth:0] BaudGeneratorInc = ((Baud<<(BaudGeneratorAccWidth-4))+(ClkFrequency>>5))/(ClkFrequency>>4); wire BaudTick = BaudGeneratorAcc[BaudGeneratorAccWidth];always @(posedge clk or negedge rst)if(~rst)BaudGeneratorAcc <= 0;else if(TxD_busy)BaudGeneratorAcc <= BaudGeneratorAcc[BaudGeneratorAccWidth-1:0] + BaudGeneratorInc;// 发送端状态wire TxD_ready = (state==0);// 当state = 0时,处于准备空闲状态,TxD_ready = 1 assign TxD_busy = ~TxD_ready;// 空闲状态时TxD_busy = 0// 把待发送数据放入缓存寄存器TxD_dataRegalways @(posedge clk or negedge rst)if(~rst)TxD_dataReg <= 8'b00000000;else if(TxD_ready & TxD_start)TxD_dataReg <= TxD_data;// 发送状态机always @(posedge clk or negedge rst)if(~rst)beginstate <= 4'b0000;// 复位时,状态为0000,发送端一直发1电平TxD <= 1'b1;endelsecase(state)4'b0000: if(TxD_start) beginstate <= 4'b0100; // 接受到发送信号,进入发送状态end4'b0100: if(BaudTick) beginstate <= 4'b1000;// 发送开始位- 0电平TxD <= 1'b0;end4'b1000: if(BaudTick) beginstate <= 4'b1001;// bit 0TxD <= TxD_dataReg[0];end4'b1001: if(BaudTick) beginstate <= 4'b1010;// bit 1TxD <= TxD_dataReg[1];end4'b1010: if(BaudTick) beginstate <= 4'b1011;// bit 2TxD <= TxD_dataReg[2];end4'b1011: if(BaudTick) beginstate <= 4'b1100;// bit 3 TxD <= TxD_dataReg[3];end4'b1100: if(BaudTick) beginstate <= 4'b1101;// bit 4 TxD <= TxD_dataReg[4];end4'b1101: if(BaudTick) beginstate <= 4'b1110;// bit 5 TxD <= TxD_dataReg[5];end4'b1110: if(BaudTick) beginstate <= 4'b1111;// bit 6 TxD <= TxD_dataReg[6];end4'b1111: if(BaudTick) beginstate <= 4'b0010;// bit 7 TxD <= TxD_dataReg[7];end4'b0010: if(BaudTick) beginstate <= 4'b0011;// stop1 TxD <= 1'b1;end4'b0011: if(BaudTick) beginstate <= 4'b0000;// stop2TxD <= 1'b1;enddefault: if(BaudTick) beginstate <= 4'b0000;TxD <= 1'b1;endendcaseendmodule接收端:module rcv(clk,rst,RxD,RxD_data,RxD_data_ready,);input clk,rst,RxD;output[7:0] RxD_data;// 接收数据寄存器output RxD_data_ready;// 接收完8位数据,RxD_data 值有效时,RxD_data_ready 输出读信号parameter ClkFrequency = 25000000; // 时钟频率-25MHzparameter Baud = 115200;// 波特率-115200reg[2:0]bit_spacing;reg RxD_delay;reg RxD_start;reg[3:0]state;reg[7:0]RxD_data;reg RxD_data_ready;// 波特率产生,使用8倍过采样parameter Baud8 = Baud*8;parameter Baud8GeneratorAccWidth = 16;wire [Baud8GeneratorAccWidth:0] Baud8GeneratorInc = ((Baud8<<(Baud8GeneratorAccWidth-7))+(ClkFrequency>>8))/(ClkFrequency>>7); reg[Baud8GeneratorAccWidth:0] Baud8GeneratorAcc;always @(posedge clk or negedge rst)if(~rst)Baud8GeneratorAcc <= 0;elseBaud8GeneratorAcc <= Baud8GeneratorAcc[Baud8GeneratorAccWidth-1:0] + Baud8GeneratorInc;// Baud8Tick 为波特率的8倍-115200*8 = 921600wire Baud8Tick = Baud8GeneratorAcc[Baud8GeneratorAccWidth];// next_bit 为波特率-115200always @(posedge clk or negedge rst)if(~rst||(state==0))bit_spacing <= 0;else if(Baud8Tick)bit_spacing <= bit_spacing + 1;wire next_bit = (bit_spacing==7);// 检测到RxD 有下跳沿时,RxD_start 置1,准备接收数据always@(posedge clk)if(Baud8Tick)beginRxD_delay <= RxD;RxD_start <= (Baud8Tick & RxD_delay & (~RxD));end// 状态机接收数据always@(posedge clk or negedge rst)if(~rst)state <= 4'b0000;else if(Baud8Tick)case(state)4'b0000: if(RxD_start) state <= 4'b1000;// 检测到下跳沿4'b1000: if(next_bit)state <= 4'b1001;// bit 04'b1001: if(next_bit)state <= 4'b1010;// bit 14'b1010: if(next_bit)state <= 4'b1011;// bit 24'b1011: if(next_bit)state <= 4'b1100;// bit 34'b1100: if(next_bit)state <= 4'b1101;// bit 44'b1101: if(next_bit)state <= 4'b1110;// bit 54'b1110: if(next_bit)state <= 4'b1111;// bit 64'b1111: if(next_bit)state <= 4'b0001;// bit 74'b0001: if(next_bit)state <= 4'b0000;// 停止位default: state <= 4'b0000;endcase// 保存接收数据到RxD_data 中always @(posedge clk or negedge rst)if(~rst)RxD_data <= 8'b00000000;else if(Baud8Tick && next_bit && state[3])RxD_data <= {RxD, RxD_data[7:1]};// RxD_data_ready 置位信号always @(posedge clk or negedge rst)if(~rst)RxD_data_ready <= 0;elseRxD_data_ready <= (Baud8Tick && next_bit && state==4'b0001); endmodule为了测试收发是否正常,写的Test Bench`timescale 1ns / 1nsmodule rs232_test;reg clk,rst,TxD_start;reg [7:0]TxD_data;wire[7:0]RxD_data;wire//RxD,TxD,TxD_busy,RxD_data_ready;trans trans(.clk(clk),.rst(rst),.TxD_start(TxD_start),.TxD_busy(TxD_busy),.TxD_data(TxD_data),.TxD(TxD));rcv rcv(.clk(clk),.rst(rst),.RxD(TxD),// 收发相接时RxD = TxD .RxD_data(RxD_data),.RxD_data_ready(RxD_data_ready) );initial beginTxD_start = 0;TxD_data = 0;clk = 0;rst = 1;#54 rst = 0;#70 rst = 1;#40 TxD_start = 1'b1;#10 TxD_data = 8'b11011001;#100 TxD_start = 1'b0;endalways begin#30 clk = ~clk;#10 clk = ~clk;endendmodule二、综合三、FPGA与PC串口自收发通信串口通信其实简单实用,这里我就不多说,只把自己动手写的verilog代码共享下。

ft232用法 -回复

ft232用法-回复FT232是一种常用的USB转串口芯片,广泛应用于各种电子设备中。

它具有高度的灵活性和可靠性,可以实现计算机与外围设备之间的数据传输和通信。

本文将详细介绍FT232的用法,从硬件连接到驱动程序的安装和使用。

一、硬件连接首先,我们需要将FT232芯片与目标设备进行连接。

FT232芯片具有四个串口端口,分别是TXD、RXD、RTS和CTS,我们需要根据需要选择相应的端口。

连接步骤如下:1. 确定好FT232的电源供应,可以通过从USB接口提供电源或者外接电源适配器。

2. 将FT232的TXD引脚连接到目标设备的RXD引脚,以实现数据的串行传输。

3. 将FT232的RXD引脚连接到目标设备的TXD引脚,以实现数据的接收。

4. 如果目标设备支持硬件流控制,可以将FT232的RTS引脚连接到目标设备的CTS引脚,以实现数据的流控制。

如果不需要硬件流控制,这一步可以省略。

5. 将FT232芯片的地线(GND)连接到目标设备的地线,以确保电位一致。

二、驱动程序安装完成硬件连接后,我们需要安装FT232的驱动程序,以使计算机能够识别和与FT232进行通信。

FT232芯片由FTDI公司生产,他们提供了Windows和Mac等操作系统的驱动程序。

1. 在计算机上打开FTDI公司的官方网站,下载并安装适用于您操作系统版本的驱动程序。

2. 运行驱动程序安装程序,按照提示完成安装过程。

3. 完成安装后,系统会自动识别FT232并分配一个COM端口号。

4. 可以在设备管理器中查看FT232的状态,确保驱动程序正确安装且设备正常工作。

三、使用FT232安装完成驱动程序后,我们可以开始使用FT232进行数据传输和通信了。

使用FT232可以通过命令行或者编程语言来完成。

1. 命令行方式:可以使用命令行工具,如TeraTerm、PuTTY等,来直接发送和接收数据。

首先,打开命令行工具,选择正确的COM端口号和波特率,然后输入指令进行数据传输。

fpga串口通信教程

FPGA实现串口通信目录摘要 (1)1 绪论 (2)1.1 选题背景 (2)1.1.1课题相关技术的发展 (2)1.1.2 课题研究的必要性 (3)1.2 课题研究的内容 (3)2 FPGA及其开发环境简介 (4)2.1 FPGA简介 (4)2.1.1 FPGA概述 (4)2.1.2 FPGA基本结构 (4)2.1.3 FPGA系统设计流程 (5)2.1.4 FPGA开发编程原理 (7)2.2 Quartus II9.1集成开发环境简介 (7)2.3VHDL硬件描述语言简介 (8)2.3.1基本介绍 (8)2.3.2 VHDL系统设计的特点 (8)2.3.3VHDL系统优势 (9)3 串口通信总体设计方案 (9)3.1串口通信的原理图 (9)3.2 设计的基本要求 (10)4 串口通信各单元电路设计 (10)4.1 RS-232发送顶层模块发送模块设计 (10)4.2 RS-232接收顶层模块设计 (14)4.3 显示模块 (18)5 实验结论与研究展望 (20)5.1 实验结论 (20)5.2 研究展望 (21)致谢.......................................... 错误!未定义书签。

主要参考文献.. (21)摘要本设计用接口芯片的VHDL的设计方法,通过对MAX232串行通总线接口的设计,掌握发送与接收电路的基本设计思路,并进行串口通信。本设计用文本输入法实现串口通信的发送与接收电路的设计。采用VHDL语言设计分频模块、发生模块、接收模块和显示模块;用键盘输入及串口调试软件调试;拨码开关开关控制发送资料,并在串口调试软件环境下显示,数码管显示出接收到的数据。关键词硬件描述语言;VHDL;FPGA;RS232界面AbstractThis design using the interface chip design method, through the VHDL for MAX232 serial links bus interface design, grasps the sending and receiving circuit design, the basic and serial interface communication.This design using text input method of realization of serial communication sending and receiving circuit design. Using VHDL language design frequency module, producing module, receiving module and display module, Use the keyboard input and serial debugging software debugging, Dial the code switch switch control, and send data in serial adjustment under software environment display, digital pipe showed received data.Keywords hardware description language, VHDL, The FPGA, RS232 interface1 绪论现代社会的标志之一就是信息产品的广泛使用,而且是产品的性能越来越强,复杂程度越来越高,更新步伐越来越快。支撑信息电子产品高速发展的基础就是微电子制造工艺水平的提高和电子产品设计开发技术的发展。前者以微细加工技术为代表,而后者的代表就是EDA(electronic design automatic,电子设计自动化)技术。本设计采用的VHDL是一种全方位的硬件描述语言,具有极强的描述能力,能支持系统行为级、寄存器传输级和逻辑门级三个不同层次的设计;支持结构、数据流、行为三种描述形式的混合描述、覆盖面广、抽象能力强,因此在实际应用中越来越广泛。ASIC(Application Specific Integrated Circuit)是专用的系统集成电路,是一种带有逻辑处理的加速处理器。而FPGA(Field-Programmable Gate Array,现场可编程门阵列)是特殊的ASIC芯片,与其它的ASIC芯片相比,它具有设计开发周期短、设计制造成本低、开发工具先进、标准产品无需测试、质量稳定以及可实时在线检测等优点。串行通信是将数据分解成二进制位用一条信号线,一位一位顺序传送的方式,其优势是用于通信的线路少,因而在远距离通信时可以极大地降低成本,它适合于远距离数据传送,也常用于速度要求不高的近距离数据传送PC系列机上有两个串行异步通信接口、键盘、鼠标与主机间采用串行数据传送。异步通信是一种很常用的通信方式。异步通信在发送字符时,所发送的字符之间的时间间隔可以是任意的。发送端可以在任意时刻开始发送字符,因此必须在每一个字符的开始和结束的地方加上标志,即加上开始位和停止位,以便使接收端能够正确地将每一个字符接收下来。异步通信的好处是通信设备简单、便宜,但传输效率较低(因为开始位和停止位的开销所占比例较大)。1.1 选题背景本节将从FPGA嵌入式应用开发技术与串行通信发展的客观实际出发,通过对该技术发展状况的了解,以及课题本身的需要,指出研究基于FPGA的芯片系统与设计——FPGA串口通信的设计与实现的必要性。1.1.1课题相关技术的发展当今电子产品正向功能多元化,体积最小化,功耗最低化的方向发展。它与传统的电子产品在设计上的显著区别师大量使用大规模可编程逻辑器件,使产品的性能提高,体积缩小,功耗降低.同时广泛运用现代计算机技术,提高产品的自动化程度和竞争力,缩短研发周期。EDA技术正是为了适应现代电子技术的要求,吸收众多学科最新科技成果而形成的一门新技术。美国ALTERA公司的可编程逻辑器件采用全新的结构和先进的技术,加上MaxplusII或QUARTUS开发环境,更具有高性能,开发周期短等特点,十分方便进行电子产品的开发和设计。EDA技术,技术以大规模可编程逻辑器件为设计载体,以硬件描述语言为系统逻辑描述主要表达方式,以计算机、大规模可编程逻辑器件的开发软件及实验开发系统为设计工具,通过有关的开发软件,自动完成用软件的方式设计的电子系统到硬件系统的逻辑编译,逻辑化简,逻辑分割,逻辑映像,编程下载等工作。最终形成集成电子系统或专用集成芯片的一门新技术。本设计利用VHDL硬件描述语言结合可编程逻辑器件进行的,并通过数码管显示通信结果。RS232通信可以由各种技术实现,如单片机等。利用可编程逻辑器件具有其它方式没有的特点,它具有易学,方便,新颖,有趣,直观,设计与实验项目成功率高,理论与实践结合紧密,体积小,容量大,I/O口丰富,易编程和加密等特点,并且它还具有开放的接口,丰富的设计库,模块化的工具以及LPM定制等优良性能,应用非常方便。因此,本设计采用可编程逻辑器件实现。1.1.2 课题研究的必要性现在是一个知识爆炸的新时代。新产品、新技术层出不穷,电子技术的发展更是日新月异。可以毫不夸张的说,电子技术的应用无处不在,电子技术正在不断地改变我们的生活,改变着我们的世界。RS-232异步通讯协议,数据在传输过程中没有时钟信号,在接收端必须以一种特定的方式,与接收数据进行同步。串行通信要求的传输线路少,可靠性高,传输距离远,凭借其多方面的优势,已接口,但是在FPGA中还没有集成这个功能,因此将所需要的串口通信集成被广泛应用到微机与外设的数据交换。目前在很多芯片中集成了串口通信到FPGA芯片内部中,使得整个系统更加稳定,集成度更高。1.2 课题研究的内容本设计主要研究基于FPGA的RS232异步通信,要求根据RS232异步通信的帧格式FPGA 数据接收模块中采用的每一帧格式为:1位开始位+8位数据位+1位结束位,波特率为9600。该模块首先检测串口数据的起始位,在检测到起始位后,每隔一个波特率的时间对串口数据进行一次采样,并存入寄存器的相应位置,当每一帧的8位数据全部写入寄存器后,再统一输出。2 FPGA及其开发环境简介2.1 FPGA简介2.1.1 FPGA概述FPGA是现场可编程门阵列(Field Programmable Gate Array)的简称,与之相应的CPLD是复杂可编程逻辑器件(Complex Programmable Logic Device)的简称,两者的功能基本相同,只是实现原理略有不同,所以有时可以忽略这两者的区别,统称为可编程逻辑器件或CPLD/PGFA。CPLD/PGFA几乎能完成任何数字器件的功能,上至高性能CPU,下至简单的74电路。它如同一张白纸或是一堆积木,工程师可以通过传统的原理图输入或硬件描述语言自由的设计一个数字系统。通过软件仿真可以事先验证设计的正确性,在PCB完成以后,利用CPLD/FPGA的在线修改功能,随时修改设计而不必改动硬件电路。使用CPLA/FPGA开发数字电路,可以大大缩短设计时间,减少PCB面积,提高系统的可靠性。这些优点使得CPLA/FPGA技术在20世纪90年代以后得到飞速的发展,同时也大大推动了EDA软件和硬件描述语言HDL的进步。2.1.2 FPGA基本结构FPGA具有掩膜可编程门阵列的通用结构,它由逻辑功能块排成数组,并由可编程的互连资源连接这些逻辑功能块来实现不同的设计。FPGA一般由3种可编程电路和一个用于存放编程数据的静态内存SRAM组成。这3种可编程电路是:可编程逻辑模块(CLB--Configurable Logic Block)、输入/输出模块(IOB--I/O Block)和互连资源(IR—Interconnect Resource)。可编程逻辑模块CLB是实现逻辑功能的基本单元,它们通常规则的排列成一个数组,散布于整个芯片;可编程输入/输出模块(IOB)主要完成芯片上的逻辑与外部封装脚的接口,它通常排列在芯片的四周;可编程互连资源包括各种长度的连接线段和一些可编程连接开关,它们将各个CLB之间或CLB、IOB之间以及IOB之间连接起来,构成特定功能的电路。1.CLB是FPGA的主要组成部分。图2-1是CLB基本结构框图,它主要由逻辑函数发生器、触发器、数据选择器等电路组成。CLB中3个逻辑函数发生器分别是G、F 和H,相应的输出是G’ 、F’和H’。G有4个输入变量G1、G2、G3和G4;F也有4个输入变量F1、F2、F3和F4。这两个函数发生器是完全独立的,均可以实现4输入变量的任意组合逻辑函数。逻辑函数发生器H有3个输入信号;前两个是函数发生器的输出G’和F’,而另一个输入信号是来自信号变换电路的输出H1。这个函数发生器能实现3输入变量的各种组合函数。这3个函数发生器结合起来,可实现多达9变量的逻辑函数。CLB中有许多不同规格的数据选择器(四选一、二选一等),通过对CLB内部数据选择器的编程,逻辑函数发生器G、F和H的输出可以连接到CLB输出端X或Y,并用来选择触发器的激励输入信号、时钟有效边沿、时钟使能信号以及输出信号。这些数据选择器的地址控制信号均由编程信息提供,从而实现所需的电路结构。CLB中的逻辑函数发生器F和G均为查找表结构,其工作原理类似于ROM。F 和G的输入等效于ROM的地址码,通过查找ROM中的地址表可以得到相应的组合逻辑函数输出。另一方面,逻辑函数发生器F和G还可以作为器件内高速RAM或小的可擦写内存使用,它由信号变换电路控制。2.输入/输出模块IOB。IOB提供了器件引脚和内部逻辑数组之间的连接。它主要由输入触发器、输入缓冲器和输出触发/锁存器、输出缓冲器组成。每个IOB 控制一个引脚,它们可被配置为输入、输出或双向I/O 功能。当IOB 控制的引脚被定义为输入时,通过该引脚的输入信号先送入输入缓冲器。缓冲器的图2-1 CLB 基本结构时几纳秒(或者不延时)送到输入通路D 触发器,再送到数据选择器。通过编程给数据选择器不同的控制信息,确定送至CLB 数组的I1和I2是来自输入缓冲器,还是来自触发器。当IOB 控制的引脚被定义为输出时,CLB 数组的输出信号OUT 也可以有两条传输途径:一条是直接经MUX 送至输出缓冲器,另一条是先存入输出通路D 触发器,再送至输出缓冲器。IOB 输出端配有两只MOS 管,它们的栅极均可编程,使MOS 管导通或截止,分别经上拉电阻接通Vcc 、地线或者不接通,用以改善输出波形和负载能力。3.可编程互连资源IR 。可编程互连资源IR 可以将FPGA 内部的CLB 和CLB 之间、CLB 和IOB 之间连接起来,构成各种具有复杂功能的系统。IR 主要由许多金属线段构成,这些金属线段带有可编程开关,通过自动布线实现各种电路的连接。2.1.3 FPGA 系统设计流程一般说来,一个比较大的完整的项目应该采用层次化的描述方法:分为几个较大的模块,定义好各功能模块之间的接口,然后各个模块再细分去具体实现,这就是TOP DOWN(自顶向下)的设计方法。目前这种高层次的设计方法已被广泛采用。高层次设计只是定义系统的行为特征,可以不涉及实现工艺,因此还可以在厂家综合库的支持下,利用综合优化工具将高层次描述转换成针对某种工艺优化的网络表,使工艺转化变得轻而易举。CPLD/FPGA 系统设计的工作流程如图2-2所示。 可编程开关矩输入输出模块互连资源图2-2 CPLD/FPGA系统设计流程流程说明:1.工程师按照“自顶向下”的设计方法进行系统划分。2.输入VHDL代码,这是设计中最为普遍的输入方式。此外,还可以采用图形输入方式(框图、状态图等),这种输入方式具有直观、容易理解的优点。3.将以上的设计输入编译成标准的VHDL檔。4.进行代码级的功能仿真,主要是检验系统功能设计的正确性。这一步骤适用于大型设计,因为对于大型设计来说,在综合前对源代码仿真,就可以大大减少设计重复的次数和时间。一般情况下,这一仿真步骤可略去。5.利用综合器对VHDL源代码进行综合优化处理,生成门级描述的网络表文件,这是将高层次描述转化为硬件电路的关键步骤。综合优化是针对ASIC芯片供货商的某一产品系列进行的,所以综合的过程要在相应的厂家综合库的支持下才能完成。6.利用产生的网络表文件进行适配前的时序仿真,仿真过程不涉及具体器件的硬件特性,是较为粗略的。一般的设计,也可略去这一步骤。7.利用适配器将综合后的网络表文件针对某一具体的目标器件进行逻辑映像操作,包括底层器件配置、逻辑分割、逻辑优化和布局布线。8.在适配完成后,产生多项设计结果:(a)适配报告,包括芯片内部资源利用情况,设计的布尔方程描述情况等;(b)适配后的仿真模型;(c)器件编程檔。根据适配后的仿真模型,可以进行适配后时序仿真,因为已经得到器件的实际硬件特性(如时延特性),所以仿真结果能比较精确的预期未来芯片的实际性能。如果仿真结果达不到设计要求,就修改VHDL源代码或选择不同速度和质量的器件,直至满足设计要求。最后将适配器产生的器件编程檔通过编程器或下载电缆加载到目标芯片CPLD/FPGA中。2.1.4 FPGA开发编程原理硬件设计需要根据各种性能指针、成本、开发周期等因素,确定最佳的实现方案,画出系统框图,选择芯片,设计PCB并最终形成样机。CPLD/FPGA软件设计可分为两大块:编程语言和编程工具。编程语言主要有VHDL和V erilog两种硬件描述语言;编程工具主要是两大厂家Altera和Xilinx的集成综合EDA软件(如MAX+plusII、QuartusII、Foundation、ISE)以及第三方工具(如FPGA Express、Modelsim、Synposys SVS等)。具体的设计输入方式有以下几种:1.HDL语言方式。HDL既可以描述底层设计,也可以描述顶层的设计,但它不容易做到较高的工作速度和芯片利用率。用这种方式描述的项目最后所能达到的性能与设计人员的水平、经验以及综合软件有很大的关系。2.图形方式。可以分为电路原理图描述,状态机描述和波形描述3种形式。有的软件3种输入方法都支持,如Active-HDL。MAX+plusII 图形输入方式只支持电路原理图描述和波形描述两种。电路原理图方式描述比较直观和高效,对综合软件的要求不高。一般大都使用成熟的IP核和中小规模集成电路所搭成的现成电路,整体放到一片可编程逻辑器件的内部去,所以硬件工作速度和芯片利用率很高,但是但项目很大的时候,该方法就显得有些繁琐;状态机描述主要用来设计基于状态机思想的时序电路。在图形的方式下定义好各个工作状态,然后在各个状态上输入转换条件以及相应的输入输出,最后生成HDL语言描述,送去综合软件综合到可编程逻辑器件的内部。由于状态机到HDL语言有一种标准的对应描述方式,所以这种输入方式最后所能达到的工作速度和芯片利用率主要取决于综合软件;波形描述方式是基于真值表的一种图形输入方式,直接描述输入与输出的波形关系。这种输入方式最后所能达到的工作速度和芯片利用率也是主要取决于综合软件。2.2 Quartus II9.1集成开发环境简介Quartus II软件是Altera的综合开发工具,它集成了Altera的FPGA/CPLD 开发流程中所涉及的所有工具和第三方软件接口。Quartus II9.1版本几乎支持Altera现行的所有FPGA,在该集成开发环境中可以实现电路的设计、综合、适配到最后形成下载文件以及在线配置FPGA,还能对电路进行功能仿真,对适配后形成的最终电路进行时序仿真。也就是说只要有了Quartus II这个集成开发环境,就基本上可以完成Altera公司FPGA开发过程中的所有工作。另外,为了方便设计,Quartus II还提供了免费LPM模块供用户调用,如计数器、内存、加法器、乘法器等。除了这些免费的LPM模块外,Altera公司还开发了有偿IP核提供给有需要的用户使用。这些LPM模块和IP核都大大简化了设计过程,缩短了开发周期。Quartus II 9.1支持多种输入方式,常用的有:(1)原理图输入:这种方法最直观,适合顶层电路的设计;(2)硬件描述语言输入:包括AHDL、VHDL及Verilog HDL输入。采用硬件描述语言的优点易于使用自顶向下的设计方法、易于模块规划和复用、移植性强、通用性好。(3)网表输入:对于在其它软件系统上设计的电路,可以采用这种设计方法,而不必重新输入,Quartus II支持的网表檔包括EDIF、VHDL及Verilog等格式。这种方法的优点是可以充分利用现有的设计资源。在本章的设计中,采用的是VHDL 硬件描述语言与原理图输入相结合的方式。一般来说,完整的FPGA设计流程包括电路设计与输入、功能仿真、综合、综合后仿真、实现、布线后仿真与验证、板级仿真验证与调试等主要步骤。2.3VHDL硬件描述语言简介2.3.1基本介绍VHDL的英文全名是Very-High-Speed Integrated Circuit HardwareD escription Language,诞生于1982年。1987年底,VHDL被IEEE和美国国防部确认为标准硬件描述语言。自IEEE公布了VHDL的标准版本,IEEE-1076 (简称87版)之后,各EDA公司相继推出了自己的VHDL设计环境,或宣布自己的设计工具可以和VHDL接口。此后VHDL在电子设计领域得到了广泛的接受,并逐步取代了原有的非标准的硬件描述语言。1993年,IEEE对VHDL进行了修订,从更高的抽象层次和系统描述能力上扩展VHDL的内容,公布了新版本的VHDL,即IEEE标准的1076-1993版本,(简称93版)。现在,VHDL和Veri log作为IEEE的工业标准硬件描述语言,又得到众多EDA公司的支持,在电子工程领域,已成为事实上的通用硬件描述语言。有专家认为,在新的世纪中, VHDL于Verilog语言将承担起大部分的数字系统设计任务。VHDL语言是一种用于电路设计的高级语言。它在80年代的后期出现。最初是由美国国防部开发出来供美军用来提高设计的可靠性和缩减开发周期的一种使用范围较小的设计语言。VHDL的英文全写是:VHSIC(Very High Speed Integrated Circuit)Ha rdware Description Language.翻译成中文就是超高速集成电路硬件描述语言。因此它的应用主要是应用在数字电路的设计中。目前,它在中国的应用多数是用在FPGA/CPLD/EPLD的设计中。当然在一些实力较为雄厚的单位,它也被用来设计ASIC。VHDL主要用于描述数字系统的结构,行为,功能和接口。除了含有许多具有硬件特征的语句外,VHDL的语言形式和描述风格与句法是十分类似于一般的计算机高级语言。VHDL的程序结构特点是将一项工程设计,或称设计实体(可以是一个组件,一个电路模块或一个系统)分成外部(或称可视部分,及埠)和内部(或称不可视部分),既涉及实体的内部功能和算法完成部分。在对一个设计实体定义了外部接口后,一旦其内部开发完成后,其它的设计就可以直接调用这个实体。这种将设计实体分成内外部分的概念是VHDL系统设计的基本点。2.3.2 VHDL系统设计的特点与其它硬件描述语言相比,VHDL具有以下特点:功能强大、设计灵活。VHDL具有功能强大的语言结构,可以用简洁明确的源代码来描述复杂的逻辑控制。它具有多层次的设计描述功能,层层细化,最后可直接生成电路级描述。VHDL支持同步电路、异步电路和随机电路的设计,这是其它硬件描述语言所不能比拟的。VHDL还支持各种设计方法,既支持自底向上的设计,又支持自顶向下的设计;既支持模块化设计,又支持层次化设计。支持广泛、易于修改。由于VHDL已经成为IEEE标准所规范的硬件描述语言,目前大多数EDA工具几乎都支持VHDL,这为VHDL的进一步推广和广泛应用奠定了基础。在硬件电路设计过程中,主要的设计檔是用VHDL编写的源代码,因为VHDL 易读和结构化,所以易于修改设计。强大的系统硬件描述能力。VHDL具有多层次的设计描述功能,既可以描述系统级电路,又可以描述门级电路。而描述既可以采用行为描述、寄存器传输描述或结构描述,也可以采用三者混合的混合级描述。另外,VHDL支持惯性延迟和传输延迟,还可以准确地建立硬件电路模型。VHDL支持预定义的和自定义的数据类型,给硬件描述带来较大的自由度,使设计人员能够方便地创建高层次的系统模型。独立于器件的设计、与工艺无关。设计人员用VHDL进行设计时,不需要首先考虑选择完成设计的器件,就可以集中精力进行设计的优化。当设计描述完成后,可以用多种不同的器件结构来实现其功能。很强的移植能力。VHDL是一种标准化的硬件描述语言,同一个设计描述可以被不同的工具所支持,使得设计描述的移植成为可能。易于共享和复用。VHDL采用基于库(Library)的设计方法,可以建立各种可再次利用的模块。这些模块可以预先设计或使用以前设计中的存盘模块,将这些模块存放到库中,就可以在以后的设计中进行复用,可以使设计成果在设计人员之间进行交流和共享,减少硬件电路设计。2.3.3VHDL系统优势(1)与其它的硬件描述语言相比,VHDL具有更强的行为描述能力,从而决定了他成为系统设计领域最佳的硬件描述语言。强大的行为描述能力是避开具体的器件结构,从逻辑行为上描述和设计大规模电子系统的重要保证。(2)VHDL丰富的仿真语句和库函数,使得在任何大系统的设计早期就能查验设计系统的功能可行性,随时可对设计进行仿真模拟。(3)VHDL语句的行为描述能力和程序结构决定了他具有支持大规模设计的分解和已有设计的再利用功能。符合市场需求的大规模系统高效,高速的完成必须有多人甚至多个代发组共同并行工作才能实现。(4)对于用VHDL完成的一个确定的设计,可以利用EDA工具进行逻辑综合和优化,并自动的把VHDL描述设计转变成门级网表。(5)VHDL对设计的描述具有相对独立性,设计者可以不懂硬件的结构,也不必管理最终设计实现的目标器件是什么,而进行独立的设计。3 串口通信总体设计方案3.1串口通信的原理图如图3.1所示。其中TXD为发送数据线,RXD为接收数据线。图3.13.2 设计的基本要求根据RS232异步通讯的帧格式FPGA 数据接收模块中采用的每一帧格式为:1位开始位+8位数据位+1位结束位,波特率为9600。该模块首先检测串口数据的起始位,在检测到起始位后,每隔一个波特率的时间对串口数据进行一次采样,并存入寄存器的相应位置,当每一帧的8位数据全部写入寄存器后,再统一输出。4 串口通信各单元电路设计4.1 RS-232发送顶层模块发送模块设计RS-232发送模块下面是我们所想要实现的:。

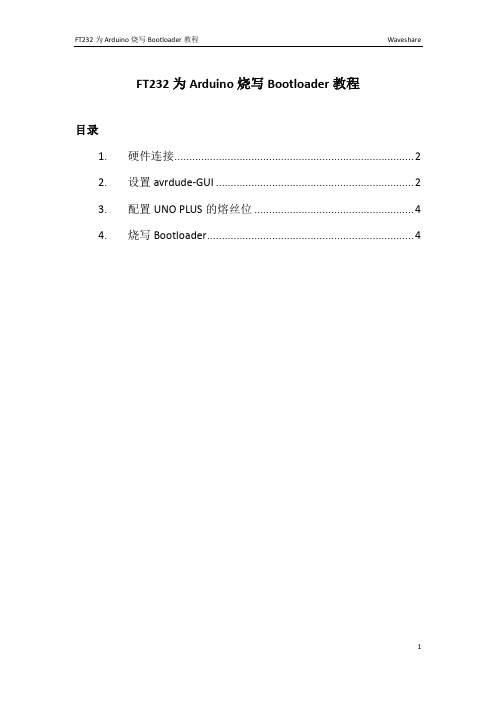

FT232 为Arduino 烧写 Bootloader 教程

FT232为Arduino烧写Bootloader教程目录1.硬件连接 (2)2.设置avrdude-GUI (2)3.配置UNO PLUS的熔丝位 (4)4.烧写Bootloader (4)1.硬件连接按照下图对UNO PLUS进行连接:图 1. UNO PLUS硬件连接2.设置avrdude-GUI1)解压Software目录下的FT232RL AVRDUDE,打开avrdude-GUI(位于avrdude-GUI-1.0.5文件夹),界面如下图所示:图 2. avrdude-GUI界面2)Avrdude.exe File处填入avrdude.exe所在路径,用户也可以点击地址栏3)Programmer下拉列表选择FT232R Synchronous BitBang (diecimila)。

4)Device下拉列表选择相应的CPU型号。

UNO PLUS板载ATmega328P-AU芯片,因此这里选择为ATmega328P(m328p)。

5)Command line Option处填入接口信息:-P ft0图 3. 设置avrdude-GUI3.配置UNO PLUS的熔丝位1)点击Fuse和Lock Bit图 4. 读取熔丝位2)上一步骤中,读取出的熔丝位并不一定是用户所需要的。

Arduino官方推荐配置如下:●high_fuses=0xde●low_fuses=0xff●extended_fuses=0x05●lock_bits=0x0F●unlock_bits=0x3F注意:Arduino各个版本的熔丝位配置可在Arduino安装文件夹hardware\arduino下的boards.txt文件中找到,用户根据需要进行配置。

如果读出的值与Arduino板子官方推荐的不一样的话,则需要通过把官方推荐的熔丝位配置写入CPU。

填写推荐的熔丝位之后,点击入。

4.烧写Bootloader1)Flash处填入optiboot_atmega328-Mini.hex所在路径,用户也可以点击地Arduino官方提供了各个版本相应的Bootloader,它们存放在安装文件下的hardware\arduino\bootloaders文件夹中。

用于keil的stm32驱动安装说明

1、驱动安装

1、先找到“开发板驱动程序”,安装过程很简单,依次点击下一步即可完成安装。

2、用usb线连接开发板和电脑。

会出现如下问题。

双击可以发现,FT232被识别成了未知设备,连设备类型标签都丢失了

别担心,一会就能解决:首先,点击更新驱动程序,选择手动查找并安装驱动程序

从列表中选取

选择通用串行总线控制器

选择厂商“FTDI”,型号“USB,Serial Converter”,

下一步,选择继续安装驱动

然后,你可以看到。

还要更新一次驱动,虽然是只有一个设备,却要更新两次才能正常,再双击这个设备这次选择的不是通用串行总线控制器,二是是端口(COM和LPT)

厂商和版本,和之前的一样

至此驱动安装完毕

2、STMISP安装

1、找到“STM32 ISP程序下载器”,选择安装路径,依次点击下一步完成安装。

2、此软件由于年代久远,缺乏更新,在新的一代系统中缺少相应的组件mesa.dll,打开软件时会出现缺少组件等问题。

解决办法:找到把已经下载好的“mesa.dll”文件拷到如下系统路径。

C:\Windows\SysWOW64或者C:\Windows\System32

3、程序烧写步骤

1、用跳线帽短路boot0,选择单片机启动方式为下载模式。

拔掉跳线帽则为正常运行模式

2、打开STM32ISP程序下载器,根据下图次序选择操作

1)其中端口的选择要在在设备管理器中进行查看

2)连接设备成功之后,会显示操作信息。

3)装载。

找到MDK工程生成的hex文件。

4)选择自动烧写。

5)拔掉跳线帽,复位单片机,程序可正常运行。

串口安装

如何安装USB转232串口

本学习板必须有RS232串口支持,才可以进行ISP(在线编程)。

如果你的电脑没有RS232接口,则必须配接一个USB转232串口的电缆设备,此设备可以把USB接口转为232串口。

USB转232串口的设备一般可以在电脑市场购买,本文以常用的型号为HL-340的USB转232串口为例,讲述如何安装驱动程序。

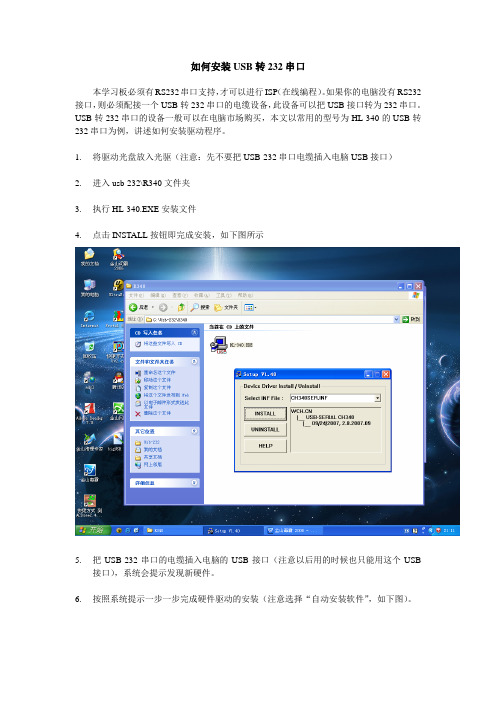

1.将驱动光盘放入光驱(注意:先不要把USB-232串口电缆插入电脑USB接口)

2.进入usb-232\R340文件夹

3.执行HL-340.EXE安装文件

4.点击INSTALL按钮即完成安装,如下图所示

5.把USB-232串口的电缆插入电脑的USB接口(注意以后用的时候也只能用这个USB

接口),系统会提示发现新硬件。

6.按照系统提示一步一步完成硬件驱动的安装(注意选择“自动安装软件”,如下图)。

7.驱动程序安装完成后,右击桌面上我的电脑,查看设备管理器,端口(COM和LPT)

中增加了USB-SERIAL CH340的串口,后面对应的COM?就是我们要用到的串口,一定要记住COM?的顺序号,在线编程时会用到。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Xilinx FPGA入门连载41:FT232串口芯片驱动安装

特权同学,版权所有

配套例程和更多资料下载链接:

/s/1jGjAhEm

1 FT232串口芯片驱动安装

如果是第一次连接PC和UART-USB接口,需要安装驱动。

驱动可以直接到FTDI公司的官方网站(/Drivers/VCP.htm)下载。

在我们配套资料的FT232_Driver 文件夹里面也有已经下载好的驱动,大家可以直接使用。

第一次将FT232的USB port和PC连接时,会弹出如图所示的驱动安装提示(下面使用的英文XP操作系统的界面,中文的类似)。

选择Install from a list or specific location选项。

然后点击Next。

接着使用Browse定位到驱动所在目录(…\FT232_Driver\CDM 2.08.28 WHQL Certified,即驱动),点击Next。

如图所示,驱动正在安装。

驱动安装完毕,如图所示。

此时,我们可以打开设备管理器,如图所示,Ports下面多了一个USB Serial Port(COM10),实际上它相当于一个模拟的UART,记住它是COM10,后面我们使用串口调试助手的时候需

要选择这个端口进行通信。