YCL-DSP2812-Pro硬件电路详解

DSP2812教程 (2)

HELLODSP 版权所有 请勿用于商业用途 违者必究

Measuring our success is your success !

外部引脚 (GPIO/XINT2_ADCSOC) EVB 的多种事件 外部引脚

对于第 11 点,ADC 控制寄存器 1 的位 ACQ_PS3—ACQ_PS0 决定了采集窗口的大小,这一位控制了 SOC 脉冲的宽度,也就是一开始开关 S(t)的导通时间。SOC 脉冲的宽度是(ACQ_PS+1)*ADCLK。

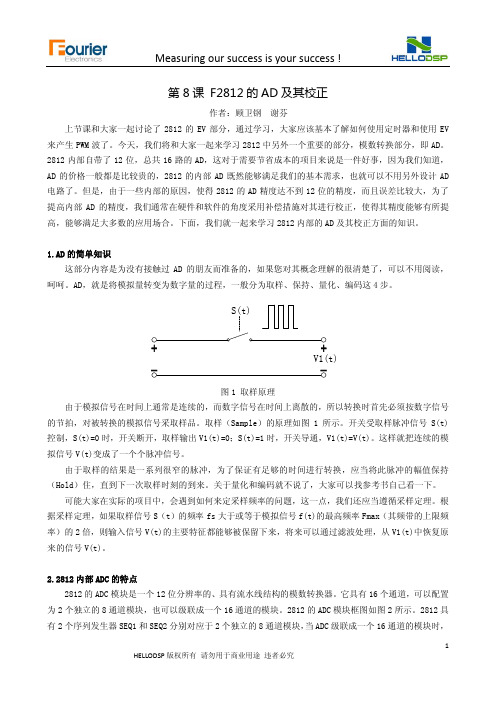

1.AD 的简单知识 这部分内容是为没有接触过 AD 的朋友而准备的,如果您对其概念理解的很清楚了,可以不用阅读, 呵呵。AD,就是将模拟量转变为数字量的过程,一般分为取样、保持、量化、编码这 4 步。ຫໍສະໝຸດ S(t)+ _

图 1 取样原理

V1(t)

+ _

由于模拟信号在时间上通常是连续的,而数字信号在时间上离散的,所以转换时首先必须按数字信号 的节拍,对被转换的模拟信号采取样品。取样(Sample)的原理如图 1 所示。开关受取样脉冲信号 S(t) 控制,S(t)=0 时,开关断开,取样输出 V1(t)=0;S(t)=1 时,开关导通,V1(t)=V(t)。这样就把连续的模 拟信号 V(t)变成了一个个脉冲信号。 由于取样的结果是一系列很窄的脉冲,为了保证有足够的时间进行转换,应当将此脉冲的幅值保持 (Hold)住,直到下一次取样时刻的到来。关于量化和编码就不说了,大家可以找参考书自己看一下。 可能大家在实际的项目中,会遇到如何来定采样频率的问题,这一点,我们还应当遵循采样定理。根 据采样定理,如果取样信号 S(t)的频率 fs 大于或等于模拟信号 f(t)的最高频率 Fmax(其频带的上限频 率)的 2 倍,则输入信号 V(t)的主要特征都能够被保留下来,将来可以通过滤波处理,从 V1(t)中恢复原 来的信号 V(t)。

DSP2812管脚详解

DSP2812管脚详解XINTF信号XA[0]~XA[18] --- 19位地址总线XD[0]~XD[15] --- 16位数据总线XMP/MC` --- 1 --微处理器模式--- XINCNF7有效0 --微计算机模式--- XINCNF7无效XHOLD` ---外部DMA保持请求信号。

XHOLD为低电平时请求XINTF释放外部总线,并把所有的总线与选通端置为高阻态。

当对总线的操作完成且没有即将对XINTF进行访问时,XINTF释放总线。

此信号是异步输入并与XTIMCLK同步XHOLDA` ---外部DMA保持确认信号。

当XINTF响应XHOLD 的请求时XHOLDA呈低电平,所有的XINTF 总线和选通端呈高阻态。

XHOLD和XHOLDA信号同时发出。

当XHOLDA有效(低)时外部器件只能使用外部总线XZCS0AND1` --- XINTF区域O和区域1的片选,当访XINTF区域0或1时有效(低)XZCS2` --- XINTF区域2的片选,当访XINTF区域2时有效(低) XZCS6AND7` --- XINTF区域6和区域7的片选,当访XINTF区域6或7时有效(低)XWE` ---写有效。

有效时为低电平。

写选通信号是每个区域操作的基础,由XTIMINGX寄存器的前一周期、当前周期和后一周期的值确定XRD` ---读有效。

低电平读选通。

读选通信号是每个区域操作的基础,由xTIMINGX寄存器的前一周期、当前周期和后一周期的值确定。

注意:XRD`和XWE`是互斥信号XR/W` ---通常为高电平,当为低电平时表示处于写周期,当为高电平时表示处于读周期XREADY ---数据准备输入,被置1表示外设已为访问做好准备。

XREADY可被设置为同步或异步输入。

在同步模式中,XINTF接口块在当前周期结束之前的一个XTIMCLK时钟周期内要求XREADY有效。

在异步模式中,在当前的周期结束前XINTF接口块以XTIMCLK的周期作为周期对XREADY采样3次。

DSP2812-V1.3原理图

R29 XF-XPLLDIS 10k R3 10k R33 MDXA 10k R6 10k R30 SPISTEA 10k R4 10k R31 SPICLKA 10k R5 R38 10k XMP/MC 10k R7 VSS 10k

1 2 3 1 CON3 2 3 J8 1 2 3

CON3 1 2 3 J13

复位电路

SW4 VDD3.3 10k R20 R19 1k SW DPST VSS C3 1uf XRS

SPICLKA

XMP/MC

1 2 3

CON3

CON3

89 91 93 95 97 101 103 106 108 110 115 117 122 124 130

89 91 93 95 97 101 103 106 108 110 115 117 119 122 124 130

VDD VoutB VinbVinb+

8 7 6 5 2 J5

VCC3.3 ADCINA0

AVSSREFBG AVDDREFBG ADCLO

OPA2344 1

VDD3.3 10k

19 32 38 52 58 70 78 86 99 105 113 120 129 142 153 176

VSS-1 VSS-2 VSS-3 VSS-4 VSS-5 VSS-6 VSS-7 VSS-8 VSS-9 VSS-10 VSS-11 VSS-12 VSS-13 VSS-14 VSS15 VSSAIO

1

REF2 2 JUMPER

2

Rev <RevCode> 1 of 5

5

4

3

2

5

4

3

2

1

GPIO/此处IO都可设置为普通IO口,方便扩展

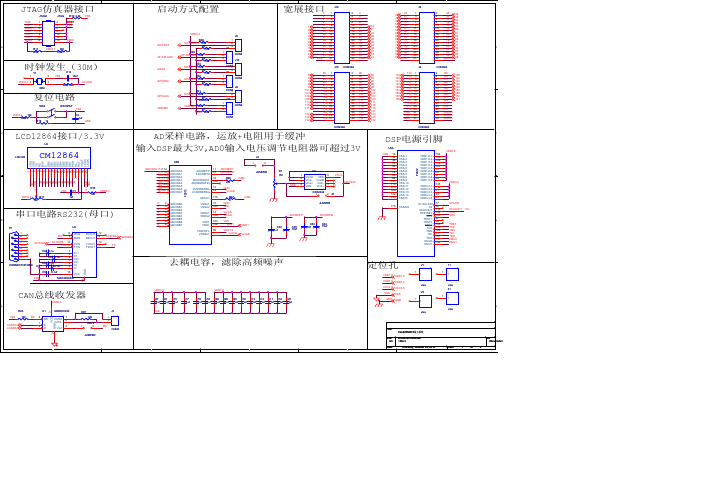

开发板DSP2812原理框图及各部分分析

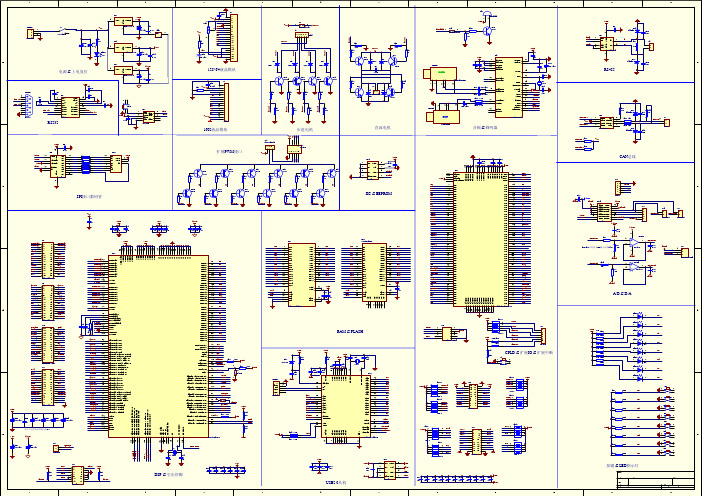

开发板DSP2812原理框图及各部分分析开发板DSP2812原理框图及各部分分析T-DSP2812开发板主要集成了RS232接口、CAN 接口、网络接口、PS2接口、12864液晶接口、ADC 接口、EEPROM 、蜂鸣器、1×4键盘、流水灯等电路,囊括了几乎所有的常用接口和应用电路。

基本单元测试程序包括以下几个部分:1.蜂鸣器程序。

2 流水灯程序;3 1×4独立式按键输入显示程序;4 DSP 通过PS2端口接收显示键盘输入数据程序;5 SO12864液晶显示画面程序;6 DSP 通过RS232接口与PC 机通信程序;7 DSP 通过USB 接口与PC 机通信程序;8 PC 机通过网络接口(RJ45)和DSP 通信程序;9 256K × 16 SRAM 读写程序;10 读写EEPROM 程序开发板DSP2812原理框图如图1所示:LED 显示液晶显示10K*8 UART图1 DSP2812原理框图一.电源电路TMS320F2812采用高性能静态CMOS技术,I/O供电电压及FLASH编程电压为3.3V,内核供电电压降为1.8V(135MHz)或1.9V(150MHz),故本开发板选用TI公司的双路输出低压降(LDO)稳压器TPS767D318,将输入的5V 直流电压稳压输出一路为3.3V,一路为1.8V,每路最大输出电流为1A。

为了抑制电源线上的高频噪声和尖峰干扰,降低数字噪声对模拟电路的干扰,模拟电源和数字电源、模拟地和数字地都采用磁珠隔离。

同时板上5V、3.3V、1.8V电压都采用发光二极管指示电源状态,方便用户使用。

二.按键电路TMS320F2812采用高性能静态CMOS技术,I/O供电电压及FLASH编程电压为3.3V,内核供电电压降为1.8V(135MHz)或1.9V(150MHz),故本开发板选用TI公司的双路输出低压降(LDO)稳压器TPS767D318,将输入的5V 直流电压稳压输出一路为3.3V,一路为1.8V,每路最大输出电流为1A。

基于DSP2812无刷直流电机控制

• 系统控制方框图

功率变换模块的控制

• 以三相两极无刷直流电机为例,如下为三相半桥电路

三相半桥驱动电路绕组利用率低,转矩波动大

三相全桥二二导通方式

调速技术

• 本系统通过PWM调速方式,通过控制开关管的PWM触发信号

来改变占空比,从而改变端电压U来实现对无刷直流电机 的调速。

• PWM技术主要有两种:单极性PWM控制和双极性PWM控制。

串口接收中断开始

接收转速正负位

依次接收转速千位,百 位,十位,个位

设定转速给定值setn

清除中断标志位

开中断

中断返回

主要内容

1 2 3 4 5 选题背景 设计简介 无刷直流电机控制系统硬件设计 无刷直流电机控制系统软件设计 无刷直流电机的 MATLAB 仿真 实验结果与分析 结论与展望

6

7

无刷直流电机的简介

下一位置导通相

ANC BNC BNA CNA

当前位置(H1, 下一位置导通相 H2,H31) 001 BNA

011 010 110 100 101 CNA CNB ANB ANC BNC

100

101

CNB

ANB

位置检测子程序开始

读端口电平放入 H1,H2,H3

判断转向,正转?

Y

N

正转 ,转向设定setd=1

定时器2中断开始

转速计算 n=(cap/3)*50*60

调运PID()

Timer=20

Y

N

串口发送转速n

清除中断标志位

开中断

中断返回

五、捕获中断程序

捕获中断程序主要执行PWM的换向操作,换向时 要根据电机设定的转动的正反方向和转子此时对 应的位置来改变PWM的输出,转子位置有6种状态, 这6种状态不断循环,根据设定的正反转方向,查 表获得下一时刻的输出,使电机持续旋转。 同时,每一次捕获中断的发生都要将capn加1, capn就是转速计算的标志位,当capn为3时,则表 明转子转过一圈,再根据定时器2的定时就能定时 算出转子转速。

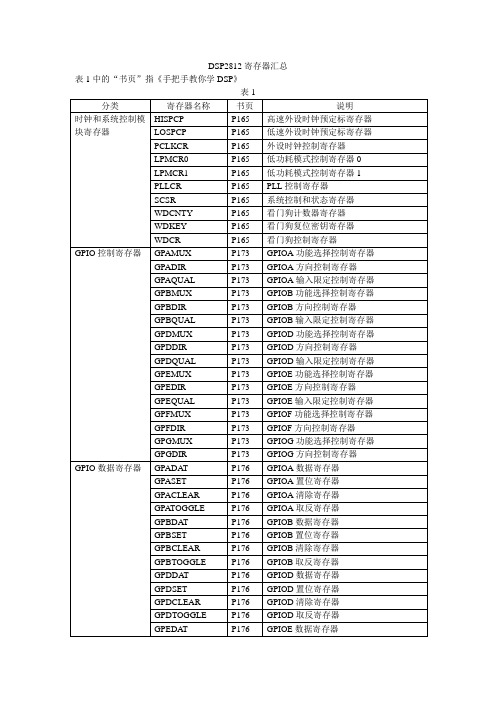

DSP2812寄存器汇总

PIE, INT9组使能寄存器

PIEIFR9

P201

PIE, INT9组标志寄存器

PIEIER10

P201

PIE, INT10组使能寄存器

PIEIFR10

P201

PIE, INT10组标志寄存器

PIEIER11

P201

PIE, INT11组使能寄存器

PIEIFR11

P201

PIE, INT11组标志寄存器

P187

CPU定时器2控制寄存器

TIMER2TPR

P187

CPU定时器2预定标寄存器低位

TIMER2TPRH

P187

CPU定时器2预定标寄存器高位

CPU中断寄存器

IER

P196

CPU中断使能寄存器

IFR

P196

CPU中断标志寄存器

INTM

P196

CPU全局中断标志位

PIE(外设中断控制器)中断寄存器

EVAIFRA

P257

EVA中断标志寄存器A

EVAIMRA

P257

EVA中断屏蔽寄存器A

EVAIFRB

P257

EVA中断标志寄存器B

EVAIMRB

P257

EVA中断屏蔽寄存器B

EVAIFRC

P257

EVA中断标志寄存器C

EVAIMRC

P257

EVA中断屏蔽寄存器C

EVBIFRA

P257

EVB中断标志寄存器A

P293

ADC自动序列状态寄存器

ADCRESULT0

P293

ADC转换结果缓冲寄存器0

ADCRESULT1

P293

ADC转换结果缓冲寄存器1

DSP2812实验指导书第二部分_图文(精)

第2章F2812-A评估板硬件使用指导2.1 F2812-A评估板技术指标主处理芯片:TMS320F2812,运行速度为150M;工作速度可达150MIPS;片上RAM 18k*16bit;片上扩展RAM存贮空间64K×16Bit;自带16路12bit A/D,最大采样速率12.5msps;4路的DAC7617转换,100K/S,12Bit;两路UART串行接口,符合RS232标准;16路PWM输出;1路CAN接口通讯;片上128*16bit FLASH,自带128位加密位;设计有用户可以自定义的开关和测试指示灯;4组标准扩展连接器,为用户进行二次开发提供条件;具有IEEE1149.1相兼容的逻辑扫描电路,该电路仅用于测试和仿真; +5V电源输入,内部+3.3V、+1.6V电源管理;4层板设计工艺,工作稳定可靠;具有自启动功能设计,可以实现脱机工作;可以选配多种应用接口板,包括语音板,网络板等。

2.2 F2812 –A 评估板原理图和实物图一. F2812-A 评估板实物图图2.2.2 F2812-A 器件分布图图2.2.1 F2812-A 评估板实物图二. F2812-A 器件分布图图1.2 ICETEK-F2812-A 器件分布图三.F2812-A评估板原理框图图2.2.3 F2812-A评估板原理框图2.3 F2812-A评估板接口说明以下将详细说明这些外围接口的功能和特征定义。

首先,表2-3-1 归纳总结了这些跳线和功能分类,接口位置请参考图2.2.1表2-3-1:接口和功能分类下面将分别介绍这些接口:1. +5v 电源插座: 这个接口用于接入为整个板子供电的电源,电源电压为+5V ,标准配置的电源电流为1A ,如果不使用随板提供的电源,请注意电源的正负极性和电流的大小。

下面是这个接口的插孔示意图:+5V地(GND图2.3.1 电源插孔示意图2. 标准RS-232: 9针D 型连接器,异步串口连接器,符合RS-232规范,输出电平为正负12V .下面是9针连接器的管脚定义:图2.3.2 异步串口连接器示意图3.P1扩展插座:34芯扩展总线接口。

2812DSP-12EV之全比较单元和PWM电路演示教学

PWM Signal Representation

t

Original Signal

same areas (energy)

2

t T

PWM representation

t T

PAM representation

脉宽调制(PWM)信号是脉冲宽度可以变化的脉冲序列,这些脉冲展开到几 个固定长度的周期内,以确保每个周期内都有一个脉冲。这个固定的周期 即为PWM载波周期,其倒数就被称为PWM载波频率

Three phase outputs which go to the motor terminals

DSP技术及应用

死区

281x 全比较单元及PWM电路

◆在运动控制中,通常会将两个功率器件(上级

和下级)串联起来构成一个功率转换桥臂;

◆为了避免受击穿导致失效,两个功率器件的导

通周期不能有重叠。因此就需要一对无重叠的PWM 2 输出信号来正确地开启和关闭这两个桥臂;

一个16位的比较控制寄存器(EVA为COMCONA;EVB为 COMCONB),该寄存器也是可读/写的

2一个16位的动作控制寄存器(EVA为ACTRA;EVB为ACTRB) ,均带有相应的映像寄存器,可读/写

六个PWM(三态)输出(比较输出)引脚(即PWMy引脚,对 于EVA来说y=1,2,3,4,5,6;对于EVB来说y=7,8,9,10,11,12)

存器(带映像的)

CMPRx

2

全比较寄存器 (带映像的)

PWM电路

输出逻辑

通用定时器1的计数器值不断地与三个比较寄存器的值相比 较,当一个比较匹配产生时,比较单元对应的两个输出引脚 就会根据动作控制寄存器(ACTRA)的设置发生跳变

DSP2812程序运行过程学习总结

DSP2812程序运⾏过程学习总结DSP2812程序运⾏过程学习总结⼀、2812的上电运⾏过程以下是2812上电(复位)后运⾏过程的描述:1:上电运⾏时根据MP/MC引脚的状态决定是从⽚外的3fffc0处读取复位向量或者时从⽚内的rom的3fffc0处读取复位向量。

MC ⽅式下从⽚内读取,MP⽅式下从⽚外读取。

2:⼀般我们⽤的是MC⽅式,即从⽚内读取复位向量,在⽚内的rom 3fffc0处有⼀个地址为3ffc00。

3:复位后处理器从3fffc0处读取3ffc00这个地址,所以程序从3ffc00处开始执⾏4:3ffc00处开始的就是initboot过程,根据IO管教的状态判断该进⼊那⼀种引导⽅式5:在SCITXA引脚为⾼电平时就是flash boot⽅式,此时置PC=3F7FF6SCITXA引脚有内部上拉,所以只要没有强制下拉的话,DSP检测的都是⾼电平。

对于通讯不影响。

SCITXA不⽤在外部上拉。

不能直接接到⾼电平上。

6:在⽚内flash的3F7FF6和3F7FF7处有⼀个跳转指令,该跳转指令就是LB _c_int007:执⾏这个跳转指令后程序就开始运⾏c_int00这个函数了8:这个函数就是建⽴⼀个c程序的运⾏环境,等建⽴完c运⾏环境后c_int00调⽤main函数9:main函数开始就是我们⾃⼰编写的应⽤程序了。

⼆、CMD⽂件介绍DSP开发过程中,编译器⽣成的代码和数据要由链接器分配到合适的存储空间,通常链接器的命令⽂件.cmd⽂件是由⽤户⾃⼰编写的,编写不当,就会使仿真开发不能进⾏。

1存储空间的配置TMS320F2812的DSP存储器分为三个独⽴选择的空间-程序空间、数据空间和I/O空间,其中程序存储器存放待执⾏的指令和执⾏中所⽤的系数(常数),可使⽤⽚内或⽚外的RAM、ROM或EPROM等来构成;数据存储器存放指令执⾏中产⽣的数据,可使⽤⽚内或⽚外的RAM和ROM来构成;I/O存储器存放与映象外围接⼝相关的数据,也可以作为附加的数据存储空间使⽤。

DSP2812深入讲解

DSP 的发展历史大致可以分成四个阶段:萌芽阶段、成长阶段、成熟阶段、突破阶段。 萌芽阶段:1982 年以前 在这段时期里为解决 Von Neumann 结构在进行数字信号处理时总线和存储器之间的瓶颈效应,许多公司投入 大量人力和物力开展了很多探索性的工作,研制出了一些 DSP 的雏形,如 AMI 的 S2811、INTEL 的 2920、 AT&T 的 DSP-1 和 NEC 的 uPD7720。但这些产品的运算速度都太慢,而且开发工具严重不足,无法进行大 规模的开发工作,还不能称作真正意义上的 DSP。第一片 DSP 是 1982 年 TI 公司出品的 TMS320C10,它是 —个 16 位的定点 DSP,采用了哈佛(Harvard)结构,有一个乘加器和一个累加器。TMS320C10 完成—次乘加 操作需要 390ns,即在一秒钟的时间内可以完成 250 万次左右的乘加运算。或许正是因为生产出了第一个 DSP, TI 公司在此后的三十几年中一直是 DSP 界的领军人物。 成长阶段:1982-1987 年 这段时间内各公司相继研制出了自己的 DDSP 并不断地改进。如 1985 年,TI 推出了 TMS320C20,它具备单 指令循环的硬件支持,寻址空间达到 64K 字,有专门的地址寄存器,一次乘加运算只需耗时 200ns。1987 年, MOTOROLA 公司推山了 DSP56001,采用 24 位的数据和指令,有专门的地址寄存器,可以循环寻址,累加 器有保护位,一坎乘加运算只需耗时 75ns。此外,在这段时期中还有一些代表产品,如 AT&T 的 DSPl6A、 AD 的 ADSP-2100,TI 的 TMS320C50。 成熟阶段:1987-1997 年 在这个阶段里各公司不断借鉴相互的优点,并完善自身的设计,推出了特点分明的产品,如 TI 的 TMS320C54 系列、AD 的 ADSP2100 系列、Lucent(前身为 AT&T)的 DSPl600 系列和 MOTOROLA 的 DSP56000 系列。 它们在供电上都支持 3.3v,片上的存储器也较大,都有 JTAG 模块支持用户在线调试。另外,TI 等公司还专门 提供 DSP 的内核,为一些专用集成电路(ASIC)的开发提供了空间。此外,在成熟阶段还首次出现了多处理核 的 DSP,如 TI 的 TMS320C80 和 MOTOROLA 的 MC68356 等,虽然它们的推出在商业上并不算成功,但却 指明了一个有潜力的发展方向。 突破阶段:1997 年直至现在 这段时间里 DSP 的发展非常迅速,各公司相继建立了自己从定点到浮点,从低端到高端,从通用到专用完整 的产品系列,并且在 DSP 设计上有了大的飞跃,推出了一些性能突出的产品。很多公司相继采用先进技术研 制了计算性能很高的 DSP,如 AD 的 SHARC 系列、TI 的 TMS320C6000 系列、MOTOROLA 和 Agere(前身 为 Lucent 微电子)的 StarPro 等,每秒钟可以完成 1G 条以上的指令,计算速度惊人。TI 公司还研制出功耗最 小的 DSP TMS320C55 系列,为便携式设备提供了一个明智的选择。 回顾 DSP 发展的二十几年,也正是电子、信息和微电于技术快速发展的二十年,正是后者为 DSP 提供了必要 的技术支持和应用的广阔空间,使得 DSP 及其相关的技术日益受到人们的重视。

DSP2812开发板说明书

2812开发板系统主要分为两部分,分别为硬件系统和相应的测试软件。

在开发板系统中主要集成了DSP、SRAM、FLASH、A/D、PWM、QEF、UART、SPI、CAN、USB、 以太网、LCD接口等,这样能够使其应用在电机、电力、车载等工业控制领域。

相应的测试软件包括以下几部分:

DSP对片外SRAM和FLASH的操作示例 DSP对片内外设A/D的操作示例 DSP对片内外设定时器0和定时器2的操作示例 DSP对片内外设GPIO的操作示例 DSP对片内外设SPI的操作示例 DSP对片内外设MCBSP的操作示例 DSP对片内外设SCI的操作示例 DSP对片内外设CAN的操作示例 DSP对片内外设PWM的操作示例 外部中断扩展示例 LED跑马灯示例 GUI图形接口示例 TCP/IP协议栈示例 HOST USB操作示例(选配) FAT文件系统示例(选配)

TMS320F2812的外部存储器接口包括:19位地址线,16位数据线,3个片选控制线及读 写控制线。这3个片选线映射到5个存储区域,Zone0,Zone1,Zone2,Zone6和Zone7。其中, Zone0和Zone1共用1个片选线XCS0AND1,Zone6和Zone7共用1个片选线XCS6AND7。这5个存 储区域可分别设置不同的等待周期。

第三章 TMS320F2812的基本系统

1. 时钟电路

开发板用30MHz外部晶体给DSP提供时钟,并使能F2812 片上PLL电路。PLL倍频系数由PLL 控制寄存器PLLCR的低4位控制,可由软件动态的修改。外部复位信号(RS)可将此4位清零(CCS 中的复位命令将不能对这4位清零)。TMS320F2812的CPU最高可工作在150M的主频下,也即是 对30M输入频率进行5倍频。

DSP2812硬件电路设计

3结语

随着 信息 技术 的 不断 发展, 数字 信号 处

A/ D 片进 行采样。更具采样定理得 出进 行采 理 技术也得到了广泛的应用 ,它 在计算 机、通

样 的 频 率 要 大 于 对 应 的 采 样 信 息 号 宽 带 的 两 倍,一 般 的通 讯信 号 宽带 是 2 5 K Hz , 而 语 音 信 号一般 在几 k H z -几 - / k H z , 其 中 图 像 的 信

号要 达 8 MHz .

信 、 电 子 等 方 面 的 应 用 的 较 多 ,成 为 _ , 很受 欢

迎 的技 术。随 着 D S P功能 的 日益更新 ,技 术

在 不断 的改 进 , 对 于 DS P 技 术的 应 用 也 在 增 多 。 在对 D S P硬 件 的 整 体 设 计 中 原 理 图 的 设 计 是 最基础 的内容。

源 的电压转换 为 3 , 3 V~ 5 V,这 时输 出的电流就

魁3 A: 主 要 提 供 的 设 备有 :ADC模 拟 电 源 、

I / O模拟 电源 、F l a s A HC 2 4 5 。

在 AD 两 片 中 的 1 2通 道 进 行 同时 的采 样 ,将每 个通道 转 换 为 2 5 0 K S P S ,模 拟 的输

X Z CS OA ND1( XI NT F区域 的 l 或 是 0片 选 )、

进而完成逻辑控制该芯片 。 设 计 内 容 包 含 : 复 位 电 路 、 数 模 转 换 电 路 、 外 部存 储 器 、 电 源 芯 片 、 晶 振 、接 口芯 片 等 ( 如图 1 ): 对 于 T MS 3 2 0 F 2 8 1 2芯 片 需 要 的 电 压 有很 多科 ,包括 :1 . 9 V、3 . 3 V; 其 中外 围 电路需 要的 电压 有 1 0 V、 I 5 V、 数 字 5 V、 模拟 5 V 将 供 电 芯 片 为 3 . 3 v的 T P S 7 5 7 3 3电 根 据 DS P 系统 相 关 的 模 拟 信 号 处 理 , 对 2 . 2 A / D 数 模转 换 电路

DSP2812教程(8)

DSP2812教程(8)第4课F2812⽚内资源、存储器映射以及CMD⽂件的编写作者:顾卫钢谢芬(HELLODSP资深会员)从今天开始,我们的课程终于进⼊F2812的核⼼了,呵呵。

在今天的课程中,我们将带领⼤家⼀起学习2812的⽚内资源,初步了解它究竟有哪些本事,能拿来⼲些什么,然后⼀起了解2812存储器的结构,统⼀编址的⽅式、存储器映射关系,并重点分析CMD⽂件,以期望消除⼤家对CMD⽂件的迷惑,在⾃⼰编写程序的时候会修改CMD⽂件中的部分内容,从⽽满⾜⾃⼰设计时的需求。

1.F2812的⽚内资源我们知道,TMS320F2812是32位的定点DSP,它既具有数字信号的处理能⼒,⼜具有强⼤的事件管理能⼒和嵌⼊式控制功能,特别适合⽤于需要⼤批量数据处理的测控领域,例如⾃动化控制、电⼒电⼦技术、智能化仪表、电机伺服控制。

下⾯是F2812的内部资源框图。

图1 TMS320F2812内部资源框图2812采⽤了⾼性能的静态CMOS技术,时钟频率可达150MHZ(6.67ns),其核⼼电压为1.8V,I/O⼝电压3.3V,Flash编程电压也为3.3V,所以我们在设计2812电源部分的时候,需要将常⽤的5V电压转换成1.8V和3.3V的电压之后,才能供给2812。

具体的设计我们将会在以后的硬件设计内容⾥进⾏探讨。

让我们⼀起来看看图1,最左边的A(18-0)和D(15-0)是表⽰2812外扩存储器的能⼒,2812外扩的存储空间最⼤是219*16 bit,就是说最多只能扩512K个存储单元,每⼀个存储单元的位数为16位。

从图中我们也可以看到,F2812⽀持JTAG边界扫描(Boundary Scan),这也是为什么我们的仿真器都是采⽤JTAG⼝的原因了,在这⾥,提醒⼤家⼀点的就是,仿真的时候,JTAG⼝的⽅向不能插反,如果插反的话会将仿真器烧坏。

我们所使⽤的14针JTAG⼝的第6针是空脚,所以⼀般情况下仿真器JTAG线的第6针是填针的,同时在板⼦上的第6脚是拔空的,这样可以防⽌您插反JTAG⼝,以避免不必要的损失。

dsp2812最新原理图

Q3 4007 C

Q4 4007

Q5 4007

电源 & 上电复位

VCC C3 0.1u JACK1 1 6 RX_232 2 7 TX_232 3 8 4 9 5 RS232 C1 0.1u TX_232 TXA C2 0.1u 1 3 4 5 13 11 8 10 U4 C1+ C1C2+ C2R1IN T1IN R2IN T2IN SP3232 VCC GND V+ VR1OUT T1OUT R2OUT T2OUT C4 16 0.1u 15 2 6 12 14 9 RXA 7 RX_232

Green

2

1 2 3 POWER

1 2 3

1

JACK2

S1 SW SPDT

SPX1117-3.3 +5V

+5V

1 J3

J4

VCC C8 0.1u 1 4 2 3 8 Q26 P6KE8.2

Motor Power

3

1 2 3 4 5

Motor Power

C57u/16V 0.1u 1

20 19

XIN LLINEIN RLINEIN XTO CLKOUT

E

C

9 10

LHPOUT RHPOUT

DC-MOTER 4007

4007

8050

11 3

10

C5 0.1u

2 4

C41 10u/16V 1 2

R52 4.7k R53 4.7k

MODE /CE SDIN SCLK BCLK DIN DOUT LRCIN LRCOUT

C40 T3CTRIP T4CTRIP D0' D1' D2' D3' D4' D5' D6' D7'

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1

TTL 3.3V

CMOS5V

1.1.关于电平转换及兼容性问题

1.1.1.各种电平特性

1.1.

2.电平的兼容性问题

●相同供电电压的TTL器件驱动CMOS器件

×

●相同供电电压的CMOS器件驱动TTL器件

●不同供电电压的TTL器件驱动CMOS器件

●不同供电电压的CMOS器件驱动TTL器件,

不同供电电压的TTL器件在输入端具有5V容限的情况下可以直接接口;不同供电电压的CMOS器件由于电平不匹配不能直接接口。

1.1.3.电平转换常用方法

逻辑电平转换芯片74LVX4245

,

.

3.35, 3.3,

,5

3.3V5V

1.2.LDO电源电路

V333

●电源可由外部电源插孔提供,其中电源插孔5V Power标识为内正外负。

电压为直流5V,提供电流1A以上。

●AMS1117-3.3或AMS1084-3.3电源转换芯片(UP1)作为5V转3.3V的高性能稳压芯片,为这个开发板提供稳定可靠的主电源3.3V,由指示灯DP1指示。

●AMS1117-1.8电源转换芯片(UP3)提供的1..8V给DSP内核使用,由指示灯DP3指示。

该指示灯相对DP1和DP2要暗一点。

●AMS1117-3.3电源转换芯片(UP2)提供A3.3V是提供给F2812的AD 等模拟部分和AIC23的模拟部分使用的。

由指示灯DP2指示。

●其中的B100是500mA的自恢复保险,在过大电流的时候断开,可以自恢复。

●由于本开发板电流消耗比较大,建议用外部电源供电

1.3.MAX811复位电路

R10710K

VCC3V3

●芯片上电后自动输出最少140mS 低电平复位脉冲●复位按钮S100保证手工复位●当电压低于3.08V 时自动复位

●复位信号提供给F2812、CPLD EPM3128等1.4.时钟电路及PLL 模块

●锁相环(PLL )模块主要用来控制DSP 内核的工作频率,外部提供一个参考时钟输入,经过PLL 倍频或分频后提供给DSP 内核。

●2812 DSP 有4位倍频位,能够实现0.5~10倍的倍频。

●本开发板上采用的电路,采用的内部振荡器方式。

选用的外部晶振为20M 。

●内核工作频率由PLLCR 寄存器的bits [3:0]位确定。

对应的PLL 倍频或分频系数见下表

1.5.AD输入电路

AD

●DSP内置16通道12位ADC,可配置为2个独立的8通道模块,分别服务于事件管理器A和B

●DSP能接受的AD信号在0~3V,注意:外部输入电压值不能超出这个范围,否则很容易烧毁F2812

●ADC时钟可配置为25MHz,最高采样带宽为12.5MHz

●实验中,ADCLO电压可以接地或其他参考电压,ADINA0的输

入电压可以使SPI DA TLV5616输出或是可变电位器输入,或者是外部输入

P780

1-2ADINA0DA OUT

2-3ADINA0R780

1.6.SPI串行12位D/A转换电路

D/A TI SPI TLV561612D/A

DSP SPI MASTER DACS DAFS SPI_CS CPLD:

1.7.SPI 数码管电路

SPI

-SN74HC595

DSP SPI

MASTER

LED_CS#

SPI_CS

CPLD

VCC3V3

C751

104

VCC3V3

1.8.SPI 方式的SD 卡接口电路

●SD 卡工作模式为兼容的SPI 模式,工作在SLA VE 模式●DSP 的SPI 控制器对其进行控制,工作在MASTER 模式

VCC3V3

1.9.SCI 串行通讯电路

RS-232MAX3232 3.3V

-2-23-35-5

VCC3V3

1.10.485通讯电路

3.3V

MAX3485

485

/485CS

CPLD

IO

1.11.蜂鸣器电路

P730

VCC3V3

1.1

2.CAN 通讯电路

DSP

CAN2.0

3.3V

CAN

SN65HVD230

CANTX,CANRX

CANH,CANL

CAN 1MBPS

RS SN65HVD230RS=0

;RS=1; RS

R

R70510 k to achieve a

15 V/

s slew

rate,100 k to achieve a

2.0 V/s slew rate

1.13.DSP 和PLD 的JTAG 接口电路

V C C 3V 3

202

0K V C C 3V 3

V3

1.14.外扩512K字节SRAM电路

SRAM IS61LV25616-1010nS256K 16bit512K16bit IS61LV51216F2812XINTF

/XZCS20x08 0000

3

1.15.外扩1M 字节NOR FLASH 电路

NOR FLASH

SST39VF800A 70nS

512K 16bit 256K 16bit SST39VF400A

F2812

XINTF

/XZCS6

0x10 0000

VCC3V3

1.16.走马灯与按键电路

8

LED 4

8

LED

CPLD

IO

4

V

V

1.17.PWM直流电机和步进电机驱动电路

●PWM直流电机控制实验针对5V微型直流电机。

DSP的PWM1和PWM2信号驱动4个NPN的三极管。

●当PWM1为高电平,PWM2为低电平,Q800导通,同时Q803导通,电流从MOTA向MOTB流动,假设这时电机正转。

●当PWM2为高电平,PWM1为低电平,Q802导通,同时Q801导通,电流从MOTB向MOTA流动,这时电机反转。

MOT5V

●步进电机由DSP的PWM3—PWM6信号驱动ULN2003驱动,ULN2003再驱动步进电机。

ULN2003和电机接口PMOT2之间的电阻是防止过流。

1.18.字符型和图形LCD接口电路

LCD

CPLD

●支持字符型LCD 接口,推荐型号为1602A ,12864

●支持图形汉字LCD 接口

1.19.TLV320AIC23音频电路及McBSP 多路复用电路

●本音频电路采用TI 公司的TLV320AIC23B 。

具有放音和录音功能。

●TLV320AIC23B 的控制接口采用SPI 方式

A3V3

1.20.CPLD 电路

CPLD

Altera

MAX3000A

CPLD EPM3128ATC144-10

B

2.0高速USB SLA VE (CY7C68013A )接口

Cypress

CY7C68013A-56

USB 2.0

Slave FIFO

1.2

B2.0全速USB HOST (SL811HST )接口

Cypress

SL811HST

USB 2.0USB HOST USB HOST

U

U 256M 512M 1G 2G 4G 8G

120G

30G

VCC3V3

1.23.以太网(RTL8019)接口

16

8019RST。