反激式电源设计及应用五[电磁干扰之共模部分]

反激式开关电源的设计—毕业设计说明

毕业设计说明书反激式开关电源的设计专业 电气工程及其自动化学生姓名 伊利优酸乳班级 XXXXXX学号 XXXXXX 指导教师 XXXXXX完成日期 2XXXXXXXXX反激式开关电源的设计摘要:各种电子设备中,有一个不可或缺的组成部分,那就是电源。

反激式开关电源的设计阐述了反激式开关电源的工作原理;通过方案的对比,选择出了用电流控制型PWM技术;最后详细介绍了利用TOPSwitch 器件设计开关电源的设计过程。

TOPSwitch器件是近代出现的芯片,它有很多功能,如对过流,过热进行保护,能自动重启等。

对TOPSwitch-GX 的工作原理进行了理解,对内部结构进行了分析,对以TOP244Y为控制核心的反激式开关电源进行了设计。

设计出的采用此芯片的反激式开关电源的外围电路很简单,所用元器件少,性能指标高,价格低,有较高的集成度,很有实用价值。

该芯片的开关频率为132kHZ。

设计电路的开关电源输出功率为25W时,可以实现12V/1.2A,5V/2A和30V/20mA三路直流电压输出。

另外,还设计了外围电路,并对此进行了分析。

高频变压器的设计是重点,对磁心,线圈匝数进行了选择。

用此开关电源不但可以使外围电路器件大大减少,成本降低,还能使可靠性大大提高,正常工作时,可以提供多路输出,能在家电、IT等领域被广泛应用。

关键词:开关电源;反激式变换器;TOPSwitch-GX;高频变压器The Design of Single-end Flyback Switching Power SupplyAbstract: There is an integral part of a variety of electronic devices, and that is power. Flyback switching power supply design elaborated flyback switching power supply works; contrast through the program, select a current-controlled PWM technology used; finally describes the use of TOPSwitch device design of switching power supply design process. TOPSwitch device is the modern appearance of the chip, it has many features, such as over current, over temperature protection, can automatically restart and so on. The working principle of TOPSwitch-GX are understood, the internal structure is analyzed, based on TOP244Y has been designed for the flyback switching power supply control center. The use of this chip design flyback switching power supply external circuit is very simple, the use of fewer components, high performance, low price, have a higher degree of integration, very practical value. Theswitching frequency of the chip 132kHZ. Design of circuit switching power supply output power of 25W, you can achieve 12V/1.2A, 5V/2A and 30V/20mA three-way DC voltage output. In addition, the design of the peripheral circuits, and this analyzed. High-frequency transformer design is the key, right core, coil turns is a selection. With this switching power supply can not only greatly reduce the peripheral circuit components, cost reduction, but also to greatly improve the reliability, normal working hours, you can provide multiple outputs in home appliances, IT and other fields are widely used.Key words: Switching power supply;Fly-back converter;TOPSwitch-GX;High frequency transformer目录1 概述 (1)1.1 课题来源及基本技术要求 (1)1.2 设计内容及设计思路 (1)1.3 预期成果及其意义 (2)2 反激式开关电源方案比较与选择 (2)2.1反激式开关电源介绍 (3)2.2 反激式开关电源的方案比较与选择 (3)3 基于TOP244Y芯片的单端反激式开关电源的设计 (7)3.1 TOPSwitch-GX芯片简介 (7)3.2 基本参数确定 (8)3.3 高频变压器设计 (9)3.4 输入整流滤波电路的设计 (13)3.5 钳位保护电路的设计 (14)3.6 输出整流滤波电路的设计 (15)3.7 反馈整流滤波电路设计 (17)3.8 反馈电路设计 (17)3.9 TOPSwitch-GX芯片的外围设计 (21)4 结束语 (20)参考文献 (21)致谢 (24)附录 (23)附录1 反激式开关电源原理图 (26)附录2反激式开关电源PCB图 (28)附录3 反激式开关电源主要元件清单 (29)反激式开关电源的设计1 概述1.1 课题来源及基本技术要求1.1.1课题来源如今,开关电源在生活中的应用极其广泛。

反激式电源设计及应用

反激式电源设计及应用变压器有两种绕法:顺序绕法和夹层绕法.这两种绕法对EMI 和漏感有不同的影响. 顺序绕法一般漏感为电感量的5%左右,但由于初,次级只有一个接触面,耦合电容较小,所以EMI比较好.夹层绕法一般漏感为电感量的1-3%左右,但由于初,次级只有两个接触面,耦合电容较大,所以EMI比较难过.一般30-40W 以下,功率不大,漏感能量还可以接受,所以用顺序绕法比较多,40W 以上,漏感的能量较大,一般只能用夹层绕法.变压器的漏感主要与哪些因素有关绕组顺序:夹层绕法一般是先初级,后次级的1/2-1/3. 变压器形状:长宽比越大的变压器漏感越小.先初級1/2-次級-初級1/2,大家叫這為三明治繞法夹层?好象是先原边的二分之一,再逼边,再原边的二分之一吧!(1) 变压器由于绕制造成的耦合电容偏差对变压器有那些指标有影响?(2) 如你所说,顺序绕法露感较大,耦合电容较小,EMI 较好,怎样从理论上解释耦合电容小EMI 小这一问题?当然我想你这是从变压器本身来说的,从整个电源来说,漏感较大的话,整个产品的EMI是不好的.所以我到认为,漏感的因素比耦合电容更能引起EMI 难过,我这样说有道理吗?(3) 在提到屏蔽层时,我有点不明白屏蔽绕组在变压器中是怎样设计的?耦合电容是最大的共模干扰传导途径.<br> 漏感产生的干扰频率比较低,也容易处理这个电容到底起到什么作用?<br> 通常的隔离变换器中,在原边和副边需接一个或两个耐高压隔离电容,通常也很小,这个电容到底是起到什么作用呢?事实也是,如果这个电容取得不当,会影响到输出噪声指标?不知cmg 老哥对这个电容怎么看?还有就是这个电容连接到原副边,是接两个地呢,还是接输入地端和输出正端...?并不是说不能用三名治饶,功率稍微大一点也只能用这个方法.否则漏感太大.<br> 只是干扰大小的问题,当然在小功率的时候有更多的考虑,比如取消共摸电感,来降低成本我发现个有趣的问题,以前我也一直是认为更小的耦合电容对EMI 有更多的好处.但我在最近的实验中发现当我把漏感控制在0.5%-0.8% 时,整机电源的效率显著上升,再测传导和辐射发现原本辐射超过标准2个DB变成留有6.4DB余量.(说明:电源输岀电压19V,功率75w.采用四段式绕法)漏感小后,MOS 关断时D-S 端的震荡波形的幅度会减小,而这是最重要的干扰源,小了干扰能量会降低.在反激式开关电源中,变压器相当于电感的作用.在开关管导通时,变压器储能,开关管关断时,变压器向次级释放能量.那么功率由开关管导通电流确定还是电感量确定? 在反激开关电源变压器设计时,如何计算变压器的气隙? 能否详细介绍开关电源的斜率补偿的作用,原理?功率既不是由电感量确定, 也不是由开关管确定, 是由你的需要确定.一般程序是这样,由功率和经验效率确定变压器的型号,也可以由“ AP等书上介绍的方法确定变压器,我一般是根据经验确定,要求比较严格时用允许温升确定变压器型号.确定变压器后其他参数可算出.包括开关管的电流,这样就可以选管子.变压器的气隙有相关的公式计算,但注意气息一般不要大于 1 毫米,否则可能引起边缘磁通效应使初级有过热点.反激电压方式不需要斜率补偿.电流方式大于50%脉宽,或为了防止噪音影响需要加,计算方法可参考3842 应用指南.变压器的两种屏蔽层.<br>在小功率电源变压器中,一般有两种两种屏蔽层,铜薄和绕组.铜薄的原理是切断了初次级间杂散电容的路径,让其都对地形成电容,其屏蔽效果非常好,但工艺,成本都上升.绕组屏蔽有两种原理都在起作用:切断电容路径和电场平衡.所以绕组的匝数,绕向和位置对EMI 的结果都有很大影响.可惜我不会在这里画图来讲解,总之有一点:屏蔽绕组感应的电压要和被屏蔽绕组工作时的电压方向相反.屏蔽绕组的位置对电源的待机功耗有较大的影响.下节讲变压器浸漆和屏蔽绕组位置对待机功耗的影响.你说的屏蔽层是不是这个意思<br>只是起隔离作用的一个隔离层?(对不起,我接触的都是些通讯电源和仪表电源都是体积小的二次片式电源,所用的变压器也都是采用体积小的表贴变压器,没有用什么屏蔽层,也没有见过其它同类电源用屏蔽层),你所说的用了屏蔽层的电源主要用在哪方面这样一来是不是体积就大了呢?还有你的“屏蔽绕组感应的电压要和被屏蔽绕组工作时的电压方向相反” 是什么意思?还有,你的屏蔽绕组输出接哪儿?最好能图文结合,这样大家的兴趣不是就来了吗?屏蔽的接地” <br屏蔽在初次级间时,其接地可以不接,接原边地,接次边地,接大地几种形式,一般接原边的地的情况较多.不知道cmg 兄是如何处理的.变压器的外部加屏蔽,特别在flyback 中,由于要加气隙,在批量小或简单起见,不是只在中间加,而是磁心截面全有气隙,为减小外部气隙的磁场干扰,而加屏蔽的,此屏蔽一般接大地.是EMI屏蔽,非安全屏蔽.<br>可以接原边的地线,也可以接原边的高压端,EMI几乎没有分别,因为有高压电容存在,上下对共模信号(一般大于1M 后以共模干扰为主)来说是等电位的. 变压器的外部屏蔽可以不接,也可以接初级地线,其对EMI 的影响看绕组内部的情况,但注意安规的问题,接初级地线,磁芯就是初级.屏蔽绕组对变压器的工作有影响<br>屏蔽绕组为了起到很好的作用,一般紧靠初级,这样它跟初级绕组之间形成一个电容,屏蔽绕组一般接初级地线或高压端,这个电容就相当于接在MOS 的D-S 端,很明显造成很大的开通损耗.影响了待机功耗,对3842 控制来说还可能引起空载不稳定. 当然,加屏蔽也会使漏感增大,但此影响在空载时是次要的.理论上关断损耗会小.<br>但由于关断电路作用都很强,MOS速度又快,所以对关断的损耗影响很小.另外屏蔽引起的损耗严格来说不全算开通损耗,有一部分是导通损耗,在开通瞬间和导通后,电容放电.用电流探头可以很明显看到导通瞬间有一个很大的尖峰.我看到很大的电流尖峰,你说的尖峰是不是在FLYBACK 的MOSFET 开通时有一个很大的尖峰, 我以前一直没法理解这是怎么来的,但我的变压器好象没有什么屏蔽呀,只是中间加了绝缘胶带如果你能反饶也可以,但在生产工艺上是不可能的.<br> 可以改变绕组从左到右,或从右到左的方向.可能你没有接触过工厂的生产过程.<br> 骨架换方向当然可以,但生产效率差不多降低40%.变压器的价格就上来了.1. 实际的电容总有感抗成分在内,在共模频率内,接高压端和地线真对EMI 没有分别吗?2. \"变压器的外部屏蔽可以不接,也可以接初级地线,其对EMI 的影响看绕组内部的情况\", 能详细说明一下吗?比如顺绕和夹绕时外部屏蔽该怎样处理呢?3. \" 磁芯就是初级\" 是什么意思?第一个确实几乎没有影响,我测过很多.第二个有很多情况,我不一一细说,只告诉你一个原则, 绕组最外层如果工作时电压变动大,则接地有巨大的影响,如果变动小,也有影响,但不是很大,当然电源功率本身很大时最好接地.第三个是安规的问题,已经有人说了.3 倍之说需要查安规.<br> 但其原理是明显的, 如果安全屏蔽的保险丝电流额定值比电源保险丝小或一样大,则发生短路时可能安全屏蔽的保险丝先断,起不到安全屏蔽的作用.至于外部屏蔽,首先要满足安规的要求,在此前提下,当然宽一些会好一点,但增加了成本,只要把两半磁心的结合面包住就好了,还有一个更好的方法,让铜带直接接触磁心.反激式电源的开关过程分析.<br> 我看到有个帖子在讨论此问题,所以需详细写一下.我看到有个帖子在讨论此问题,所以需详细写一下.很多人对反激电源开关转换期间的过程不清楚,以至于产生电流突变等想法.我来详细解释一下:MOS 关断后,初级电流给MOS 输出电容和变压器杂散电容充电(实际杂散电容放电,为简单,我们统一说充电),然后DS端电压谐振上升,由于电流很大,谐振电路Q值很小,所以基本上是线形上升当DS 端电压上升到在次级的电压达到输出电压加整流管的电压后,本应该次级就导通,但由于次极漏感的影响,电压还会上升一些来克服次级漏感的影响,这样反映到初级的电压也略高于正常反射电压,在这样条件下,次级电流开始上升,初级电流开始下降,但不要忘记初级的漏感,它由于不能偶合,所以它的能量要释放,这时是漏感和MOS 输出电容,变压器杂散电容谐振,电压冲高,形成几个震荡,能量在嵌位电路消耗掉,这里要注意一点,漏感的电流始终是和初级电流串联的,所以漏感电流的下降过程就是次级电流的上升过程,而漏感电流的下降过程是由嵌位电路电容上的电压和反射电压的差来决定的,此差越大,下降越快,转换过程越快,明显效率会提高,转换的过程是电压电流叠加的过程.用RC做吸收时,由于稳态时C上的电压和反射电压差别不是太大,所以转换过程慢,效率低,用TVS做吸收时,其允许电压和反射电压差很多,所以转换快,效率高,当然RC 耗电是另一个方面.我曾经在21ic 上请教过您一些问题,对于mos 的关断,通过您上序的分析,已经很透彻了,其他拓扑应是同样的原理,比如正激,在mos 关断后,副边折射电流与激磁电流对coss 充电,电压上升到vin 后,按理折射电流应变为零,但正由于漏感的影响,使电流并不太图变只剩下激磁电流,正是这个原因,导致电流与电压重叠时间过长,mos 端并电容也没有明显效果,所以只能减少漏感来减小关端重叠时间,实现零电压关端,我要问的是激磁电感与漏感在一个什么样的比列下才算正常呢,我目前变压器激磁电感20uh,漏感为2uh,我总怀疑漏感太大,您说有无道理呢?基本同意说明有些不认同,说出来共同分析一下.<br> 你的 1 得出的结论是不对的,和我的原意不符可能我的语文表达差一些 .我的意思是初级电压上升 ,次级也跟着生 ,当次级的电压达到次级输出 电压加整流管的压降后 ,次极整流管应该导通 .1、不清楚“杂散电容放电”2、“漏感电流的下降过程是由嵌位电路电容上的电压和反射电压的差来决定的 ”嵌,位电路电容上的电压不是由反射电压决定的吗 ?(当然和 R 的放电也有关 ).3、假如正激式电源输出不要储能电感 ,会怎样 ?(如有必要 ,我可以按我的疑惑画个原理图 ,贴在这儿)4、能不能详细说说 RCD 吸收回路吸收初级电感储能的情况,能不能避免 ?5、请回复一下 SOMETIMES 的“ faraday screen and safety screen 中的疑问好吗” ? 1、与其说“杂散电容放电”不, 如杂散电容反向充电来得准确.2、 “漏感电流的下降过程是由嵌位电路电容上的电压和反射电压的差来决定的 ”无,论怎样 , 漏感电流的下降过程是非常剧烈的 ,故而激起的自感电压是远高于副边反射电压(MOSFET 关断的尖峰应是因此而起 ),关断时刻 RCD 上的电压应由自感电压决定 ,而和反射电压无关 .3、这个问题单列出去算了 .4、RCD 吸收回路吸收初级电感储能是因为与反射电压串联 ,反激过程始终存在.用TVS,选择合适的工作电压可避免之 .是由电磁定律决定的:u=l di/dt;其中丨是原边漏感,其电流的变化必然感应岀一相应电压 ,此电压值 由外部电路决定 ,由公式可知 ,感应电压越高 ,电流变化越快 ,开关管上的电压电 流交叉时间越短 , 关断损耗越小 .(因漏感与原边励磁电感串联 ,故原边漏感厨师电流等于开关管关断时的电流值.)1. 怎么说都没有关系 ,关键是理解这个过程 ,MOS 导通时杂散电容电压是上正下负 ,转换过程结 束后是下正上负 .2 用 RCD 吸收 ,漏感电流下降激起的电压一般不会高于副边反射电压 .C 上的电压是反射电压和漏感电压的和,当MOS 关断时,C 上的电压和反射电压 的差决定了漏感的电流下降速度,差U=Llou*dl/dT.当然C 上的电压也包括漏感引起的一个尖峰 ,C 越大时此尖峰也越小.用TVS 时因为没有C,此尖峰就是TVS 的稳压值. 4.这个问题实际上已说过 ,RCD 的能量有两部分 ,漏感能量和一点励磁能量,原因很简单 :我们设想变压器没有漏感 ,MOS 关断时反射电压还是加在 R 上,当然要耗能 .1、你用安培环路定律做个积分看看 .2、反激变压器的电流是从异名端流岀去的 ,你用右手螺旋定责看看是不是和先前的磁场方向 一致. 对你的第一个问题结论并不正确,根据变压器线圈的比例关系般正向道通时次级反压由初级电压和线圈比例关系相乘决定 次级供电 ,这时的电压由次级决定 ,在而实际能量变换是变压 压器输岀一定的功率 ,由负载电阻决定输岀电压,而这个电压再根据变压器线圈比例反馈到初级所以初级和次级的电压关系主 要由线圈的匝数比例决定的 ,在相同的电路下如刚上电时 ,次级电压很底 ,这时初级开关的损耗是会减小,但要知道减少的只是初级MOS 管的开关损耗 (包括漏 感).另外输岀电压很底 ,整流管的损耗比例相对会成主要的损耗 ,所以实际电路联系很多 ,很多电路都是矛盾的 ,好的设计就是要找到最佳点,可以确定变压器初次级的电 压,一,而关断时边压器储能相当于电源向 压起要求输岀一定的功率 ,相当于变一个经验值.<br> 顺序绕法(先初级,后次级)一般漏感为电感量的5%左右.三明治绕法,一般在3%以下,用屏蔽好的磁心和绕线顺序可达1%以下.RCD 吸收回路,如果電容很大,但RC 時間常數還是開關周期的1/10 到1/5. 那損耗就會很大.會不會RC 回路不隻吸收漏感能量,還消耗了一部份初級電感蓄積的能量.也就是說,當MOSFET 關斷後,變壓器初級電感蓄能大部分通過次級釋放,還有一部分被RC 回路吸收.加上電容上的直流電壓(n*(V o+Vd)) 在電阻上的損耗會很大.首先加在電容上的直流電壓不是(n*(V o+Vd)), 如果是这个电压,则电源的转换时间将非常长.一定会比这个电压高.其次,RCD 吸收回路吸收的能量恰恰向你说的,是由两部分组成,一部分是漏感的能量,还有一部分是初级电感储能.这后一部分是很多人不会想到的.RC 吸收电路的设计.<br> 开关管和输出整流管的震铃是每个电源设计工程师最讨厌的事情.过度的震铃引起的过压可能使器件损坏,引起高频EMI 问题,或者环路不稳,解决的办法通常是加一个RC 吸收电路. 但很多人不知该如何选取RC 的值.首先在不加吸收电路轻载下用示波器测量震铃的频率,但注意用低电容的探头,因为探头的电容会引起震铃频率的改变,使设计结果不准.其次,在测量震铃频率时尽可能在工作的最高电压下,因为震零的频率会随电压升高而变化,这主要是MOS 或二极管的输出电容会随电压而变化.震零产生的原因是等效RLC 电路的震荡,对于一个低损的电路,这种震荡可能持续几个周期.要阻尼此震荡,我们要先知道此震荡的一个参数,对MOS, 漏感是引起震荡的主要电感,此值可以测出,对二极管,电容是主要因素,可以有手册查岀.计算其阻抗:知道L,则Z=2*3.14*f*L;知道C,Z=1/(2*3.14*f*C).先试选R=Z,通常足可以控制震铃.但损耗可能很高,这时需要串联一个电容来减小阻尼电路的功率损耗.可如此计算 C 值:C=1/(3.14*f*R).增加C 值损耗就增加,但阻尼作用加强,减小C值当然是相反的作用.电阻的损耗P=C*(V*V)Fs. 当然在某些电路形式里面损耗可能是0.5P. 实际中,可依计算的值为基础,根据实验做一些调整.不知哪位高手可以帮帮忙,替我写几部分,谢谢!当然,如果大家感觉没什么意思,就结束这个专题.1) RCD 吸收电路的设计方法.2) 反激电源多路输岀交叉调整率的产生原因和改进方法.3) 开关电源电磁干扰产生的原因及对策.4) 反激电源的控制环路零,极点分析及环路定性分析(定量分析要占用大量的时间和篇幅)5) 大功率反激电源:双管反激.6) 反激电源的软开关和无损吸收.变压器因为已经有很多帖子了,在此专题里面不在赘述.千万不要忽视理论!<br> 理论是指导实践的,这是真理,如果没有理论,当你有问题时就无处下手,有的人就到处改,到处试,改好了也不知道其所以然.要知道,电源设计应该是一个严格的数学过程,如果不能做到这一点,说明还有很多东西需要学习.如果我真写书的话,每一点都会有理论解释,只是在BBS 上,画图,写公式都很麻烦(实际上我根本就不知道怎么弄) ,所以只能写几句.刘胜利很熟悉,还送了我一本书,他的书基本上是实验数据堆起来的,很佩服老刘的精神,很大年纪了还在做实验研究.不过老人家很好玩:你跟他讲话一定要先让他讲完,否则插不进嘴.反激电源多路输出交叉调整率的产生原因和改进方法.<br> 理论上反激电源比正激电源更使用于多路输出,但实际上反击电源的多路输出交叉调整率比正激电源更难做,这主要是正激后面加了个偶合电感,而反激的漏感不是零.很多人做反激电源时都遇到这个问题,一路输出稳定性非常好,但多路输出时没有直接取反馈的路的电压会随其他路的负载变化而剧烈变化,这是什么原因呢?原来,在MOS 关断,次级输出时能量的分配是有规律的,它是按漏感的大小来分配,具体是按匝比的平方来分配(这个可以证明,把其他路等效到一路就可得岀结果)如:5V 3匝,漏感1uH,12V 7匝,如果漏感为(7/3)(平方)*1=5.4uH, 则两路输出的电流变化率是一样的,没有交叉调整率的问题,但如果漏感不匹配时,就会有很多方面影响到输岀调整率:1.次级漏感,这是明显的; 2 ,输入电压,如果设计不是很连续,则在高压时进入DCM 状态,DCM 时由于电流没有后面的平台,漏感影响更显著. 改进方法: 1 ,变压器工艺,让功率比较大,电压比较低的绕组最靠近初级,其漏感最小,电压比较高,功率比较小的远离初级,这样就增加了其漏感.2,电路方法,电压输岀较高的绕组在整流管前面加一个小的磁珠或一个小的电感,人为增加其漏感,这样电流的变化率就接近于主输岀,电压就稳定.3,电压相近的输岀,如:3.3V 5V,按我们的解释其漏感应该差别很小,这时就要把这两个绕组绕在同一层里面,甚至有时候5V 要借用3.3 的绕组,也就是所谓的堆叠绕法,来保证其漏感比.另外有时候电压不平衡是由于算岀的匝数不为整数造成的,如半匝,当然半匝是有办法绕的,但半匝的绕法也是很危险的(可参考其他资料),这是我们可以通过二极管的压降来调整,如12V 用7 匝,5V用3匝,如果发现12V偏高,则12V借用5V的3匝,但剩下的4匝的起点从5V输岀的整流管后面连接,则12V的整流管的压降为两组输岀整流管的压降和,如:0.5(5V)+0.7(12V)=1.2V,另外12V 输岀负载变化时,其电流必然引起5V 整流管的压降变化,也就是5V 输岀变化,而5V 的变化会通过反馈调整,这样也间接控制了12V.1、关于匝比平方的问题是这样的:电感值L=匝数的平方*AL(磁芯的电感因子).本质上还是电感量的问题.能量:P=1/2LI A2.2、漏感随便怎么调,如果不采取稳压措施一个绕组的负载状态(I)都会影响另一绕组.(个人观点)1. 你说的问题是电感的电感量,而漏感是不遵守这个规律的,你可以把其他组的电压,电流,漏感等效到一组,然后就看到我的结论,只有每个绕组的电流上升率一样时,理论上电压就不会再随负载而变化. 2.因为漏感受很多因素的影响,不可能完全调整到理想状态,所以实际上一个绕组还会影响另一个绕组,但可以把这个影响减到实际产品可应用的水平,而不需要加二次稳压.这个指的是每路输岀的实际功率是看其负载的大小,而我说的是交叉稳定性,是两个事情,交叉稳定性不好时,其电压值在负载大小变化时变化很大.从一个朋友的角度我建议你还是先去多学点东西,再来发帖.<br> 其实这是一个改进交叉调整率的方法之一,并不矛盾.其实还有很多方法来改进交叉调整率,如减小RCD 电路的电阻,但会造成很大的耗能,所以没列在里面,还有能量再生绕组,它是把能量反送会电网,属于反激软开关的类型之一.你写了这么多,其实我看的岀来,你压根就没理解我的说法.我已经告诉你怎么去把结果推岀来为何不去实验以下,你说我的方法无法实现,为何不照我由此推岀的改进方法去试一下,实际上我已经帮很多人用此方法改进了交叉调整率,特别是在DVD,DVR,DVB 里面. 我将不再回复此帖, 信不信由你.。

反激式电源设计[电磁干扰之共模部分]

![反激式电源设计[电磁干扰之共模部分]](https://img.taocdn.com/s3/m/5253570302020740be1e9b76.png)

作者cmg大师干扰的测量虽然传导干扰并不要求屏蔽室,但实际上各个实验室都用的是全屏蔽房间.这样使电源与地线有更大的电容,实际增加了传导高频部分(共模)通过的难度.3线时,由于电源与地线距离很近,电容很大,原理上EMI更难通过一些.但同样因为很近,可以采取一些两线没法采取的方法,如前面加两粒小的Y电容,可以把高频部分(共模)很好的短路掉,又容易通过,任何事情都是有利又有弊.我们以第一种情况来分析.复习一下干扰源,这个干扰源是最根本的干扰源,差模,共模,辐射都是由它产生动力.看这个帖子之前,最好看一下差模部分的帖子.共模EMI交流等效电路.C1的大小与漏极连接的面积跟正比,布板时减小漏极的面积是个好方法.漏极加个散热片接源极可减少EMI高频和辐射.C2是变压器初次级的杂散电容,夹层绕法C2会很大,可能需要加屏蔽,C3是次级与地的等效电容,C2,C3一般远远大于C1,所以C3是主要的共模电流流通路径.这个电容是时实在在存在的,不是等效的,但面积S除PCB线外,还包括漏极引脚对地的投影面积,变压器对地面积等效一部分(等效的大小与变压器的屏蔽处理有关).C3可以理解成PCB铜薄部分对地的面积形成的电容,其计算也是一样的.变压器对地的问题:不要忘了EMI是高频信号,静地是个相对的概念.“静地”是我自己的定义,非标准叫法.次级地之所以安静是因为Y电容的存在,如果Y电容不存在,或性能不好,次级就不是静地了.从上面图上可看到,Y电容不是理想的,它有ESL,所以高频时性能就下降了,而共模干扰恰恰是高频信号.所以次级在高频时就不是静地了,大面积铺地就加大了电容.还有一个原因:如果次级是信号线,实际上加大次级地(大面积铺地)是很好的:减小辐射,提高EMS的能力.但开关电源里面是大的脉冲电流,大面积铺地(不知你的加大地是不是这个意思)容易造成地线电流从多个回路流.产生辐射,另外辐射的磁通通过大的共模电流回路(电源,屏蔽地,LISN,电源),有感应出共模电流.如果是单纯的脑干结构的地线,加大一些或加焊锡增厚,当然可以减小ESR,ESL(高频起主要作用的是ESL),是对EMI有帮助的.但我说的不是这种情况:你没见我说的是“不问青红皂白吗”?不要断章取义,否则解释起来很费劲.Y电容的作用:从次级到初级地线提供一个低阻抗回路,使流向地再通过LISN回来的电流直接短路掉,但由于Y电容非完全理想,次级各部分间也存在阻抗,所以不可能全部回来.还是有一部分流到地.共模电感的作用:增加共模电流部分的阻抗,减小共模电流.变压器屏蔽的作用:把流向次级再到地的电流短路掉,让它直接回到初级地线.一般电源功率较大时,这几项措施要共同使用.测量两线干扰不平衡的原因:1)两线的阻抗不平衡 2)空间干扰.解决方法是在前面加X电容,并且X电容的位置要靠近初级电源进线.当然如果干扰是直接耦合到进线上,这是X电容也没有作用,要改PCB布板.Y电容的接法:。

最新反激式开关电源共模传导发射模型的分析与应用

反激式开关电源共模传导发射模型的分析与应用反激式开关电源共模传导发射模型的分析与应用作者:林思聪陈为福州大学电气工程及自动化学院摘要以反激式开关电源为研究对象,分析了其共模传导噪声的干扰源、传输通道以及变压器分布电容参数对共模嗓声的作用,建立相应的共模传导发射分析模型和变压器分布电容模型;重点分析了二次侧干扰源的影响及其作用机理,提出了一种简单但有效降低共模传导噪声的方法,并进行了实验验证。

关键词开关电源共模传导噪声变压器分布电容1 引言开关功率变换器中非线性工作的开关半导体器件形成的非线性的电压和电流干扰噪声源通过变压器和功率器件的分布参数及引线、PCB走线等的杂散参数的耦合传播,形成EMI噪声,对公用电网造成严重的电磁干扰。

抑制EMI主要是从减小干扰噪声源和阻断耦合传播通道上着手的。

对EMI的分析,比较有效的方法是通过建立EMI噪声发射模型,分析模型中的各个影响因素,再进一步提出降低噪声的方法。

许多文献都对开关电源建立了噪声模型,甚至包括开关元器件、PCB板走线、连线等高频模型,但存在的不足是没能比较完整地考虑变压器分布参数的影响。

有的只用一个耦合电容Cps来表达变压器一次绕组与二次绕组间的噪声耦合关系,没有考虑二次侧干扰源的作用,所建立的共模传导发射模型不够完整。

也有不少文献对功率变压器高频模型进行研究,但主要是针对电气参数模型,如损耗、漏感、多绕组等的等效电路,而不是针对EMI模型分析的。

本文以反激式开关电源为研究对象,分析其EMI干扰源及其共模传导发射传播机理,进一步建立了比较完整的共模传导发射模型,并进行了实验验证。

该模型考虑了一次侧开关管和二次侧整流二极管的干扰源效应及其关系,细化了变压器一次绕组与二次绕组的耦合电容。

在此基础上,进一步分析变压器绕组屏蔽对分布电容参数及模型的影响,并提出了一种降低共模传导噪声的简单方法,进行了实验验证。

2 考虑二次侧干扰源作用的共模传导发射模型反激式开关电源及共模传导发射测量原理图如图1a所示。

反激式电源设计及应用

为提高大家的兴趣,我先讲一点变压器.大家都知道变压器有两种绕法:顺序绕法和夹层绕法.这两种绕法对EMI和漏感有不同的影响. 顺序绕法一般漏感为电感量的5%左右,但由于初,次级只有一个接触面,耦合电容较小,所以EMI比较好. 夹层绕法一般漏感为电感量的1-3%左右,但由于初,次级有两个接触面,耦合电容较大,所以EMI比较难过.一般30-40W以下,功率不大,漏感能量还可以接受,所以用顺序绕法比较多,40W以上,漏感的能量较大,一般只能用夹层绕法。

绕组顺序:夹层绕法一般是先初级的1/2-1/3,后次级. 变压器形状:长宽比越大的变压器漏感越小. 耦合电容是最大的共模干扰传导途径.漏感产生的干扰频率比较低,也容易处理. 也许你是不加共模电感吧!很多的公司都是用的三明治绕制的!并不是说不能用三明治绕,功率稍微大一点也只能用这个方法.否则漏感太大.只是干扰大小的问题,当然在小功率的时候有更多的考虑,比如取消共摸电感,来降低成本. 我也一直是认为更小的耦合电容对EMI有更多的好处.但我在最近的实验中发现当我把漏感控制在0.5%-0.8%时,整机电源的效率显著上升,再测传导和辐射发现原本辐射超过标准2个DB变成留有6.4DB余量.(说明:电源输出电压19V,功率75w.采用四段式绕法)。

漏感小后,MOS关断时D-S端的震荡波形的幅度会减小,而这是最重要的干扰源,小了干扰能量会降低.如何确定功率?非连续状态下: 初级电感中的单位时间储存的能量:W=1/2*Lp*Ip^2*f ,Lp:初级电感量,Ip:初级电流峰值,f:频率。

开关管关闭时,上述能量向次级传送,一部分被损耗,剩下的为输出功率.功率既不是由电感量确定,也不是由开关管确定,是由你的需要确定. 一般程序是这样,由功率和经验效率确定变压器的型号,也可以由“AP”等书上介绍的方法确定变压器,我一般是根据经验确定,要求比较严格时用允许温升确定变压器型号.确定变压器后其他参数可算出.包括开关管的电流,这样就可以选管子. 变压器的气隙有相关的公式计算,但注意气息一般不要大于1毫米,否则可能引起边缘磁通效应使初级有过热点. 反激电压方式不需要斜率补偿.电流方式大于50%脉宽,或为了防止噪音影响需要加,计算方法可参考3842应用指南.变压器的两种屏蔽层.在小功率电源变压器中,一般有两种屏蔽层,铜泊和绕组.铜泊的原理是切断了初次级间杂散电容的路径,让其都对地形成电容,其屏蔽效果非常好,但工艺,成本都上升.绕组屏蔽两种原理都在起作用:切断电容路径和电场平衡.所以绕组的匝数,绕向和位置对EMI的结果都有很大影响.可惜我不会在这里画图来讲解,总之有一点:屏蔽绕组感应的电压要和被屏蔽绕组工作时的电压方向相反.屏蔽绕组的位置对电源的待机功耗有较大的影响.下节讲变压器浸漆和屏蔽绕组位置对待机功耗的影响. 你的屏蔽绕组输出接哪儿?不用接哪儿,只接一个脚!屏蔽在初次级间时,其接地可以不接,接原边地,接次边地,接大地几种形式,一般接原边的地的情况较多.不知道cmg兄是如何处理的. 变压器的外部加屏蔽,特别在flyback中,由于要加气隙,在批量小或简单起见,不是只在中间加,而是磁心截面全有气隙,为减小外部气隙的磁场干扰,而加屏蔽的,此屏蔽一般接大地.是EMI屏蔽,非安全屏蔽.可以接原边的地线,也可以接原边的高压端,EMI几乎没有分别,因为有高压电容存在,上下对共模信号(一般大于1M后以共模干扰为主)来说是等电位的. 变压器的外部屏蔽可以不接,也可以接初级地线,其对EMI的影响看绕组内部的情况,但注意安规的问题,接初级地线,磁芯就是初级. 屏蔽绕组对变压器的工作有影响:屏蔽绕组为了起到很好的作用,一般紧靠初级,这样它跟初级绕组之间形成一个电容,屏蔽绕组一般接初级地线或高压端,这个电容就相当于接在MOS的D-S端,很明显造成很大的开通损耗.影响了待机功耗,对3842控制来说还可能引起空载不稳定.当然,加屏蔽也会使漏感增大,但此影响在空载时是次要的. 那是不是减小了关断损耗呢?如果关断损耗比开通损耗大呢?理论上关断损耗会小.但由于关断电路作用都很强,MOS速度又快,所以对关断的损耗影响很小. 另外屏蔽引起的损耗严格来说不全算开通损耗,有一部分是导通损耗,在开通瞬间和导通后,电容放电.用电流探头可以很明显看到导通瞬间有一个很大的尖峰. 我觉得在mos管导通时,屏蔽层等效电容被放电,所以会造成开通损耗,效果就象mos管并电容造成损耗,我想cmg大师是这个意思吧.CMG你好,请教屏蔽绕组的饶法!! 比如我的屏蔽绕组在初次级之间,那么从磁芯骨架一针起饶,请问方向是不是和初级线圈的方向相反?饶制屏蔽绕组是不是刚好布满一层为选择?那么屏蔽绕组的起始端和终端是不是接同样点(就是短接后再接出!!) 这样是不是和铜泊屏蔽一样??屏蔽层要充满一层,不能短接,饶向有影响. 屏蔽绕组感应的电压要和被屏蔽绕组工作时的电压方向相反. 你的意思是要反绕是吗?如果你能反饶也可以,但在生产工艺上是不可能的.可以改变绕组从左到右,或从右到左的方向. 不过为什么不可以呢?把骨架换个向不就搞定了!可能你没有接触过工厂的生产过程.骨架换方向当然可以,但生产效率差不多降低40%.变压器的价格就上来了.1. 实际的电容总有感抗成分在内,在共模频率内,接高压端和地线真对EMI没有分别吗?2. \"变压器的外部屏蔽可以不接,也可以接初级地线,其对EMI的影响看绕组内部的情况\",能详细说明一下吗?比如顺绕和夹绕时外部屏蔽该怎样处理呢?3.\"磁芯就是初级\"是什么意思? 3.\"磁芯就是初级\"是什么意思? 即磁芯是在一次侧,应注意与二次侧之间的安规距离.第一个确实几乎没有影响,我测过很多. 第二个有很多情况,我不一一细说,只告诉你一个原则,绕组最外层如果工作时电压变动大,则接地有巨大的影响,如果变动小,也有影响,但不是很大,当然电源功率本身很大时最好接地. 第三个是安规的问题,已经有人说了.屏蔽形成回路问题的解释:屏蔽是为了抗EMI,产生的原因是漏感造成的,不屏蔽会向变压器周围的空间发射,屏蔽以后会把这部分的能量吸收了,严格来说屏蔽是会多吸收变压器的一点能量,这个问题可以形象地来理解为一个内阻很大的电源向外工作带一个负载电阻,很大的内阻是说他只是漏感造成的,对外的感应能力等效于外带负载,屏蔽相当于把外面的负载短路了,这样的结果就是外面的负载上得不到能量,也就消除了EMI干扰,而被多吸收了的能量其实很小,就是因为它只是漏感,相当于电源内阻非常大,所以多吸收的能量其实非常小,一般设计时都不会考虑,但其确实存在.faraday screen and safety screen:书上说faraday screen 一般采用薄铜片,而且不可形成回路,原边屏蔽要同原边连接或者加一个隔直电容接到原边地,副边屏蔽要同副边连接,而且连接的方式,最好从铜片中点引出,以消除电感耦合.对于safety screen 要接地,但是书上说saftey screen 的额定电流值要至少为电源保险丝的3倍,这是为什么?还有对于磁心加气隙,而采用外部屏蔽,屏蔽的宽度是否很有讲究. 3倍之说需要查安规.但其原理是明显的,如果安全屏蔽的保险丝电流额定值比电源保险丝小或一样大,则发生短路时可能安全屏蔽的保险丝先断,起不到安全屏蔽的作用.至于外部屏蔽,首先要满足安规的要求,在此前提下,当然宽一些会好一点,但增加了成本,只要把两半磁心的结合面(菜鸟评:一语中的,就是消除漏感)包住就好了,还有一个更好的方法,让铜带直接接触磁心(菜鸟评:好家伙,可以增强磁导率,减小漏感!).我也来说一点吧:3.“磁芯就是初级”是什么意思? 磁芯本身是既可当成一次侧,也可当成二次侧,如果你初级用双层绝缘线,使磁芯与初级绕组有加强绝缘,则磁芯算二次侧,要与一次侧保持安规距离,如次级绕组用双层绝缘线,则磁芯算一次侧,要与二次侧保持安规距离,cmg大哥则是把磁芯当成一次侧了,所以此时要注意二次侧出线脚与磁芯的距离,如距离不够则磁芯要绝缘胶布反包.很多人对反激电源开关转换期间的过程不清楚,以至于产生电流突变等想法.我来详细解释一下: MOS关断后,初级电流给MOS输出电容和变压器杂散电容充电(实际杂散电容放电,为简单,我们统一说充电),然后DS端电压谐振上升,由于电流很大,谐振电路Q值很小【由于电流很大,谐振电路Q值很小?不太明白,Q=1/R*根号(L/C),是不是很大啊? You are right.】,所以基本上是线性上升,当DS端电压上升到在次级的电压达到输出电压加整流管的电压后,本应该次级就导通,但由于次极漏感的影响,电压还会上升一些来克服次级漏感的影响,这样反映到初级的电压也略高于正常反射电压,在这样条件下,次级电流开始上升,初级电流开始下降,但不要忘记初级的漏感,它由于不能偶合,所以它的能量要释放,这时是漏感和MOS输出电容,变压器杂散电容谐振,电压冲高,形成几个震荡,能量在嵌位电路消耗掉,这里要注意一点,漏感的电流始终是和初级电流串联的,所以漏感电流的下降过程就是次级电流的上升过程,而漏感电流的下降过程是由嵌位电路电容上的电压和反射电压的差来决定的,此差越大,下降越快,转换过程越快,明显效率会提高,转换的过程是电压电流叠加的过程. 用RC做吸收时,由于稳态时C上的电压和反射电压差别不是太大,所以转换过程慢,效率低,用TVS做吸收时,其允许电压和反射电压差很多,所以转换快,效率高,当然RC耗电是另一个方面.我曾经在21ic上请教过您一些问题,对于mos的关断,通过您上面的分析,已经很透彻了,其他拓扑应是同样的原理,比如正激,在mos关断后,副边折射电流与激磁电流对coss充电,电压上升到vin后,按理折射电流应变为零,但正由于漏感的影响,使电流并不太突变只剩下激磁电流,正是这个原因,导致电流与电压重叠时间过长,mos端并电容也没有明显效果,所以只能减少漏感来减小关端重叠时间,实现零电压关端,我要问的是激磁电感与漏感在一个什么样的比列下才算正常呢,我目前变压器激磁电感20uh,漏感为2uh,我总怀疑漏感太大,您说有无道理呢?我详细的看了你的帖子,基本同意你的分析.1、“当DS端电压上升到在次级的电压达到输出电压加整流管的电压后,本应该次级就导通”,这种等效方式,能不能具体介绍(包括介绍些文献,这个对理解变压器的能量传输意义重大).根据这段文章是不是可以得出这样的结论:反激式变换器初次级电压差越大,转换就越快,效率就越高? 2、“漏感电流的下降过程就是次级电流的上升过程”,完全正确,而且漏感电流和次极电流都是在维持磁场的能量(楞次定律).由此可知:漏感电流存在的时间越短、量值越小(漏感越小),则次极电流建立的时间也越短、量值越大,越有利于能量的传输,也有助于效率的提升.所以,减小漏感的目的在此!基本同意说明有些不认同,说出来共同分析一下.你的1得出的结论是不对的,和我的原意不符.可能我的语文表达差一些.我的意思是初级电压上升,次级也跟着升,当次级的电压达到次级输出电压加整流管的压降后,次极整流管应该导通. 我再解释一下,你看是不是这样:1、与其说“杂散电容放电” ,不如杂散电容反向充电来得准确. 2、“漏感电流的下降过程是由嵌位电路电容上的电压和反射电压的差来决定的”,无论怎样,漏感电流的下降过程是非常剧烈的,故而激起的自感电压是远高于副边反射电压(MOSFET关断的尖峰应是因此而起),关断时刻RCD上的电压应由自感电压决定,而和反射电压无关. 3、RCD吸收回路吸收初级电感储能是因为与反射电压串联,反激过程始终存在.用TVS,选择合适的工作电压可避免之.。

反激式开关电源的电磁干扰建模及抑制方法分析

Articles论文反激式幵关电源的电磁干扰建模及抑制方法分析EMI modeling and suppression method analysis of flyback switching powersupply王京1=黄猛u冯上贤2陈宁宁wW ANG Jing12HUANG Meng1.2FENG Shangxian2CHEN Ningning1'21.空调设备及系统运行节能国家重点实验室广东珠海5190702.珠海格力电器股份有限公司广东珠海5190701. State Key Laboratory of Air-Conditioning Equipment and System Energy Conservation Zhuhai 5190702. Gree Electric Appliances, Inc. of Zhuhai Zhuhai 519070摘要:幵关电源在众多领域己被广泛应用,开关电源的高频特性导致了严重的干扰问题。

若在设计时能够明确单一元件和EMI的关系,在此基础上 经参数控制达到开关电源的EMI控制,将对开关电源的开发设计起到巨大的作用。

本文将以反激式开关电源的EMI建模及抑制方法分析作为切入点,对变压器的等效模型进行分析,得出变压器寄生电容对骚扰电压的影响机理,提出一种通过外加电容来补偿变压器寄生电容的EM I抑制方法,并对该 方法的有效性进行实验验证。

关键词:反激式开关电源;EMI建模;抑制方法Abstract: Switching power supply has been widely used in many fields, and the high frequency characteristics of switching power supply lead to serious interference problems. If the relationship between single component and EMI can be made clear in design, and then EMI control of switching power supply can be achieved by parameter control, it will play a great role in the development and design of switching power supply. In this paper, the author takes EMI modeling and suppression method analysis of flyback switching power supply as the breakthrough point, analyzes the equivalent model of transformer, obtains the influence mechanism of transformer parasitic capacitance on disturbance voltage, proposes an EMI suppression method to compensate transformer parasitic capacitance by adding capacitance, and verifies the effectiveness of this method by experiments.Keywords: Flyback switching power supply; Electromagnetic interference modeling; Inhibition method中图分类号:TB6 DOI: 10.19784/ki.issn1672-0172.2021.02.0011i引言开关电源是典型的非线性控制系统,通过控制半导体开关器件 的开通/关断使电源设备进行能量传输11]。

反激电源设计与仿真

反激电源设计与仿真反激电源是一种常见的开关模式电源,它在电源设计中具有广泛的应用。

本文将介绍反激电源的基本原理、设计流程和仿真方法。

一、反激电源的基本原理反激电源属于开关电源的一种,其基本原理是利用开关管对输入直流电压进行开关操作,通过变压器和滤波电感来实现工作频率的降低和输出电压的稳定性。

具体而言,反激电源包括以下几个主要组成部分:1.开关管:常用的开关管有MOSFET、IGBT等,其主要作用是在开关状态下将输入直流电压转换为脉冲信号。

2.变压器:反激电源中的变压器主要负责将输入电压变换为适合于输出负载的电压,并通过电感耦合的方式实现能量传递。

3.滤波电容:通过并联在输出端的滤波电容来平滑输出波形,减小输出纹波。

4.控制电路:包括反馈控制电路、PWM控制电路等,用于实现输出电压的稳定性和输出功率的控制。

二、反激电源设计流程反激电源的设计流程一般分为以下几个步骤:1.确定需求:确定输出电压、输出电流和输出功率等基本要求,并预估负载特性。

2.电源拓扑选择:根据需求选择适合的反激电源拓扑结构,常见的有单端反激、两端反激等。

3.参数计算:根据拓扑结构和需求,计算各个元件的参数,如变压器的参数、电感、容值等。

4.元件选型:根据参数计算结果,在市场上选择合适的元件,如开关管、变压器、电容等。

5.电路原理图设计:根据选定的元器件,设计反激电源的电路原理图。

6.布板设计:根据电路原理图,进行线路布局和元件布置,同时要注意功率引线和地线的布局。

7.仿真测试:利用电路仿真软件对电路进行仿真,验证设计的可行性和性能。

8.样板制作:根据仿真结果和布板设计,制作反激电源的样板。

9.实际测试:测试样板的性能,如输出电压、纹波、效率等,对比需求进行调整。

10.优化改进:根据测试结果,对电路进行优化和改进,提高性能和稳定性。

三、反激电源的仿真方法在反激电源设计中,仿真是一个非常重要的环节。

通过仿真可以有效地验证设计的可行性和预测电路的性能。

反激式电源设计及应用

反激式电源设计及应用变压器有两种绕法:顺序绕法和夹层绕法.这两种绕法对EMI和漏感有不同的影响.顺序绕法一般漏感为电感量的5%左右,但由于初,次级只有一个接触面,耦合电容较小,所以EMI 比较好.夹层绕法一般漏感为电感量的1-3%左右,但由于初,次级只有两个接触面,耦合电容较大,所以EMI 比较难过.一般30-40W以下,功率不大,漏感能量还可以接受,所以用顺序绕法比较多,40W以上,漏感的能量较大,一般只能用夹层绕法.变压器的漏感主要与哪些因素有关绕组顺序:夹层绕法一般是先初级,后次级的1/2-1/3.变压器形状:长宽比越大的变压器漏感越小.先初級1/2-次級-初級1/2,大家叫這為三明治繞法夹层?好象是先原边的二分之一,再逼边,再原边的二分之一吧!(1)变压器由于绕制造成的耦合电容偏差对变压器有那些指标有影响?(2)如你所说,顺序绕法露感较大,耦合电容较小,EMI较好,怎样从理论上解释耦合电容小EMI小这一问题?当然我想你这是从变压器本身来说的,从整个电源来说,漏感较大的话,整个产品的EMI 是不好的.所以我到认为,漏感的因素比耦合电容更能引起EMI难过,我这样说有道理吗?(3)在提到屏蔽层时,我有点不明白屏蔽绕组在变压器中是怎样设计的?耦合电容是最大的共模干扰传导途径.<br>漏感产生的干扰频率比较低,也容易处理这个电容到底起到什么作用?<br>通常的隔离变换器中,在原边和副边需接一个或两个耐高压隔离电容,通常也很小,这个电容到底是起到什么作用呢?事实也是,如果这个电容取得不当,会影响到输出噪声指标?不知cmg老哥对这个电容怎么看?还有就是这个电容连接到原副边,是接两个地呢,还是接输入地端和输出正端...?并不是说不能用三名治饶,功率稍微大一点也只能用这个方法.否则漏感太大.<br>只是干扰大小的问题,当然在小功率的时候有更多的考虑,比如取消共摸电感,来降低成本.我发现个有趣的问题,以前我也一直是认为更小的耦合电容对EMI有更多的好处.但我在最近的实验中发现当我把漏感控制在0.5%-0.8%时,整机电源的效率显著上升,再测传导和辐射发现原本辐射超过标准2个DB变成留有6.4DB余量. (说明:电源输出电压19V,功率75w.采用四段式绕法)漏感小后,MOS关断时D-S端的震荡波形的幅度会减小,而这是最重要的干扰源,小了干扰能量会降低.在反激式开关电源中,变压器相当于电感的作用.在开关管导通时,变压器储能,开关管关断时,变压器向次级释放能量.那么功率由开关管导通电流确定还是电感量确定?在反激开关电源变压器设计时,如何计算变压器的气隙?能否详细介绍开关电源的斜率补偿的作用,原理?功率既不是由电感量确定,也不是由开关管确定,是由你的需要确定.一般程序是这样,由功率和经验效率确定变压器的型号,也可以由“AP”等书上介绍的方法确定变压器,我一般是根据经验确定,要求比较严格时用允许温升确定变压器型号.确定变压器后其他参数可算出.包括开关管的电流,这样就可以选管子.变压器的气隙有相关的公式计算,但注意气息一般不要大于1毫米,否则可能引起边缘磁通效应使初级有过热点.反激电压方式不需要斜率补偿.电流方式大于50%脉宽,或为了防止噪音影响需要加,计算方法可参考3842应用指南.变压器的两种屏蔽层.<br>在小功率电源变压器中,一般有两种两种屏蔽层,铜薄和绕组.铜薄的原理是切断了初次级间杂散电容的路径,让其都对地形成电容,其屏蔽效果非常好,但工艺,成本都上升.绕组屏蔽有两种原理都在起作用:切断电容路径和电场平衡.所以绕组的匝数,绕向和位置对EMI的结果都有很大影响.可惜我不会在这里画图来讲解,总之有一点:屏蔽绕组感应的电压要和被屏蔽绕组工作时的电压方向相反.屏蔽绕组的位置对电源的待机功耗有较大的影响.下节讲变压器浸漆和屏蔽绕组位置对待机功耗的影响.你说的屏蔽层是不是这个意思<br>只是起隔离作用的一个隔离层?(对不起,我接触的都是些通讯电源和仪表电源都是体积小的二次片式电源,所用的变压器也都是采用体积小的表贴变压器,没有用什么屏蔽层,也没有见过其它同类电源用屏蔽层),你所说的用了屏蔽层的电源主要用在哪方面?这样一来是不是体积就大了呢?还有你的“屏蔽绕组感应的电压要和被屏蔽绕组工作时的电压方向相反” 是什么意思?还有,你的屏蔽绕组输出接哪儿?最好能图文结合,这样大家的兴趣不是就来了吗?屏蔽的“接地”<br>屏蔽在初次级间时,其接地可以不接,接原边地,接次边地,接大地几种形式,一般接原边的地的情况较多.不知道cmg兄是如何处理的.变压器的外部加屏蔽,特别在flyback中,由于要加气隙,在批量小或简单起见,不是只在中间加,而是磁心截面全有气隙,为减小外部气隙的磁场干扰,而加屏蔽的,此屏蔽一般接大地.是EMI屏蔽,非安全屏蔽.<br>可以接原边的地线,也可以接原边的高压端,EMI几乎没有分别,因为有高压电容存在,上下对共模信号(一般大于1M后以共模干扰为主)来说是等电位的.变压器的外部屏蔽可以不接,也可以接初级地线,其对EMI的影响看绕组内部的情况,但注意安规的问题,接初级地线,磁芯就是初级.屏蔽绕组对变压器的工作有影响<br>屏蔽绕组为了起到很好的作用,一般紧靠初级,这样它跟初级绕组之间形成一个电容,屏蔽绕组一般接初级地线或高压端,这个电容就相当于接在MOS的D-S端,很明显造成很大的开通损耗.影响了待机功耗,对3842控制来说还可能引起空载不稳定.当然,加屏蔽也会使漏感增大,但此影响在空载时是次要的.理论上关断损耗会小.<br>但由于关断电路作用都很强,MOS速度又快,所以对关断的损耗影响很小.另外屏蔽引起的损耗严格来说不全算开通损耗,有一部分是导通损耗,在开通瞬间和导通后,电容放电.用电流探头可以很明显看到导通瞬间有一个很大的尖峰.我看到很大的电流尖峰,你说的尖峰是不是在FLYBACK的MOSFET开通时有一个很大的尖峰,我以前一直没法理解这是怎么来的,但我的变压器好象没有什么屏蔽呀,只是中间加了绝缘胶带如果你能反饶也可以,但在生产工艺上是不可能的.<br>可以改变绕组从左到右,或从右到左的方向.可能你没有接触过工厂的生产过程.<br>骨架换方向当然可以,但生产效率差不多降低40%.变压器的价格就上来了.1.实际的电容总有感抗成分在内,在共模频率内,接高压端和地线真对EMI没有分别吗?2. \"变压器的外部屏蔽可以不接,也可以接初级地线,其对EMI的影响看绕组内部的情况\",能详细说明一下吗?比如顺绕和夹绕时外部屏蔽该怎样处理呢?3.\"磁芯就是初级\"是什么意思?第一个确实几乎没有影响,我测过很多.第二个有很多情况,我不一一细说,只告诉你一个原则,绕组最外层如果工作时电压变动大,则接地有巨大的影响,如果变动小,也有影响,但不是很大,当然电源功率本身很大时最好接地.第三个是安规的问题,已经有人说了.3倍之说需要查安规.<br>但其原理是明显的,如果安全屏蔽的保险丝电流额定值比电源保险丝小或一样大,则发生短路时可能安全屏蔽的保险丝先断,起不到安全屏蔽的作用.至于外部屏蔽,首先要满足安规的要求,在此前提下,当然宽一些会好一点,但增加了成本,只要把两半磁心的结合面包住就好了,还有一个更好的方法,让铜带直接接触磁心.反激式电源的开关过程分析.<br>我看到有个帖子在讨论此问题,所以需详细写一下.我看到有个帖子在讨论此问题,所以需详细写一下.很多人对反激电源开关转换期间的过程不清楚,以至于产生电流突变等想法.我来详细解释一下:MOS关断后,初级电流给MOS输出电容和变压器杂散电容充电(实际杂散电容放电,为简单,我们统一说充电),然后DS端电压谐振上升,由于电流很大,谐振电路Q值很小,所以基本上是线形上升,当DS端电压上升到在次级的电压达到输出电压加整流管的电压后,本应该次级就导通,但由于次极漏感的影响,电压还会上升一些来克服次级漏感的影响,这样反映到初级的电压也略高于正常反射电压,在这样条件下,次级电流开始上升,初级电流开始下降,但不要忘记初级的漏感,它由于不能偶合,所以它的能量要释放,这时是漏感和MOS输出电容,变压器杂散电容谐振,电压冲高,形成几个震荡,能量在嵌位电路消耗掉,这里要注意一点,漏感的电流始终是和初级电流串联的,所以漏感电流的下降过程就是次级电流的上升过程,而漏感电流的下降过程是由嵌位电路电容上的电压和反射电压的差来决定的,此差越大,下降越快,转换过程越快,明显效率会提高,转换的过程是电压电流叠加的过程.用RC做吸收时,由于稳态时C上的电压和反射电压差别不是太大,所以转换过程慢,效率低,用TVS 做吸收时,其允许电压和反射电压差很多,所以转换快,效率高,当然RC耗电是另一个方面.我曾经在21ic上请教过您一些问题,对于mos的关断,通过您上序的分析,已经很透彻了,其他拓扑应是同样的原理,比如正激,在mos关断后,副边折射电流与激磁电流对coss充电,电压上升到vin 后,按理折射电流应变为零,但正由于漏感的影响,使电流并不太图变只剩下激磁电流,正是这个原因,导致电流与电压重叠时间过长,mos端并电容也没有明显效果,所以只能减少漏感来减小关端重叠时间,实现零电压关端,我要问的是激磁电感与漏感在一个什么样的比列下才算正常呢,我目前变压器激磁电感20uh,漏感为2uh,我总怀疑漏感太大,您说有无道理呢?基本同意说明有些不认同,说出来共同分析一下.<br>你的1得出的结论是不对的,和我的原意不符.可能我的语文表达差一些.我的意思是初级电压上升,次级也跟着生,当次级的电压达到次级输出电压加整流管的压降后,次极整流管应该导通.1、不清楚“杂散电容放电”2、“漏感电流的下降过程是由嵌位电路电容上的电压和反射电压的差来决定的”,嵌位电路电容上的电压不是由反射电压决定的吗?(当然和R的放电也有关).3、假如正激式电源输出不要储能电感,会怎样?(如有必要,我可以按我的疑惑画个原理图,贴在这儿)4、能不能详细说说RCD吸收回路吸收初级电感储能的情况,能不能避免?5、请回复一下SOMETIMES的“faraday screen and safety screen ”中的疑问好吗?1、与其说“杂散电容放电” ,不如杂散电容反向充电来得准确.2、“漏感电流的下降过程是由嵌位电路电容上的电压和反射电压的差来决定的”,无论怎样,漏感电流的下降过程是非常剧烈的,故而激起的自感电压是远高于副边反射电压(MOSFET关断的尖峰应是因此而起),关断时刻RCD上的电压应由自感电压决定,而和反射电压无关.3、这个问题单列出去算了.4、RCD吸收回路吸收初级电感储能是因为与反射电压串联,反激过程始终存在.用TVS,选择合适的工作电压可避免之.是由电磁定律决定的:u=l di/dt;其中l是原边漏感,其电流的变化必然感应出一相应电压,此电压值由外部电路决定,由公式可知,感应电压越高,电流变化越快,开关管上的电压电流交叉时间越短,关断损耗越小.(因漏感与原边励磁电感串联,故原边漏感厨师电流等于开关管关断时的电流值.)1.怎么说都没有关系,关键是理解这个过程,MOS导通时杂散电容电压是上正下负,转换过程结束后是下正上负.2用RCD吸收,漏感电流下降激起的电压一般不会高于副边反射电压.C上的电压是反射电压和漏感电压的和,当MOS关断时,C上的电压和反射电压的差决定了漏感的电流下降速度,差U=Llou*dI/dT.当然C上的电压也包括漏感引起的一个尖峰,C越大时此尖峰也越小.用TVS时因为没有C,此尖峰就是TVS的稳压值.4.这个问题实际上已说过,RCD的能量有两部分,漏感能量和一点励磁能量,原因很简单:我们设想变压器没有漏感,MOS关断时反射电压还是加在R上,当然要耗能.1、你用安培环路定律做个积分看看.2、反激变压器的电流是从异名端流出去的,你用右手螺旋定责看看是不是和先前的磁场方向一致.对你的第一个问题结论并不正确,根据变压器线圈的比例关系,可以确定变压器初次级的电压,一般正向道通时次级反压由初级电压和线圈比例关系相乘决定,而关断时边压器储能相当于电源向次级供电,这时的电压由次级决定,在而实际能量变换是变压压起要求输出一定的功率,相当于变压器输出一定的功率,由负载电阻决定输出电压,而这个电压再根据变压器线圈比例反馈到初级.所以初级和次级的电压关系主要由线圈的匝数比例决定的,在相同的电路下如刚上电时,次级电压很底,这时初级开关的损耗是会减小,但要知道减少的只是初级MOS管的开关损耗(包括漏感).另外输出电压很底,整流管的损耗比例相对会成主要的损耗,所以实际电路联系很多,很多电路都是矛盾的,好的设计就是要找到最佳点一个经验值.<br>顺序绕法(先初级,后次级)一般漏感为电感量的5%左右.三明治绕法,一般在3%以下,用屏蔽好的磁心和绕线顺序可达1%以下.RCD吸收回路,如果電容很大,但RC時間常數還是開關周期的1/10到1/5.那損耗就會很大.會不會RC回路不隻吸收漏感能量,還消耗了一部份初級電感蓄積的能量.也就是說,當MOSFET關斷後,變壓器初級電感蓄能大部分通過次級釋放,還有一部分被RC回路吸收.加上電容上的直流電壓(n*(V o+Vd))在電阻上的損耗會很大.首先加在電容上的直流電壓不是(n*(V o+Vd)),如果是这个电压,则电源的转换时间将非常长.一定会比这个电压高.其次,RCD吸收回路吸收的能量恰恰向你说的,是由两部分组成,一部分是漏感的能量,还有一部分是初级电感储能.这后一部分是很多人不会想到的.RC吸收电路的设计.<br>开关管和输出整流管的震铃是每个电源设计工程师最讨厌的事情.过度的震铃引起的过压可能使器件损坏,引起高频EMI问题,或者环路不稳,解决的办法通常是加一个RC吸收电路.但很多人不知该如何选取RC的值.首先在不加吸收电路轻载下用示波器测量震铃的频率,但注意用低电容的探头,因为探头的电容会引起震铃频率的改变,使设计结果不准.其次,在测量震铃频率时尽可能在工作的最高电压下,因为震零的频率会随电压升高而变化,这主要是MOS或二极管的输出电容会随电压而变化.震零产生的原因是等效RLC电路的震荡,对于一个低损的电路,这种震荡可能持续几个周期.要阻尼此震荡,我们要先知道此震荡的一个参数,对MOS,漏感是引起震荡的主要电感,此值可以测出,对二极管,电容是主要因素,可以有手册查出.计算其阻抗:知道L,则Z=2*3.14*f*L;知道C,Z=1/(2*3.14*f*C).先试选R=Z,通常足可以控制震铃.但损耗可能很高,这时需要串联一个电容来减小阻尼电路的功率损耗.可如此计算C 值:C=1/(3.14*f*R).增加C值损耗就增加,但阻尼作用加强,减小C值当然是相反的作用.电阻的损耗P=C*(V*V)Fs.当然在某些电路形式里面损耗可能是0.5P. 实际中,可依计算的值为基础,根据实验做一些调整.不知哪位高手可以帮帮忙,替我写几部分,谢谢!当然,如果大家感觉没什么意思,就结束这个专题.1)RCD吸收电路的设计方法.2)反激电源多路输出交叉调整率的产生原因和改进方法.3) 开关电源电磁干扰产生的原因及对策.4)反激电源的控制环路零,极点分析及环路定性分析(定量分析要占用大量的时间和篇幅)5)大功率反激电源:双管反激.6)反激电源的软开关和无损吸收.变压器因为已经有很多帖子了,在此专题里面不在赘述.千万不要忽视理论!<br>理论是指导实践的,这是真理,如果没有理论,当你有问题时就无处下手,有的人就到处改,到处试,改好了也不知道其所以然.要知道,电源设计应该是一个严格的数学过程,如果不能做到这一点,说明还有很多东西需要学习.如果我真写书的话,每一点都会有理论解释,只是在BBS上,画图,写公式都很麻烦(实际上我根本就不知道怎么弄),所以只能写几句.刘胜利很熟悉,还送了我一本书,他的书基本上是实验数据堆起来的,很佩服老刘的精神,很大年纪了还在做实验研究.不过老人家很好玩:你跟他讲话一定要先让他讲完,否则插不进嘴.反激电源多路输出交叉调整率的产生原因和改进方法.<br>理论上反激电源比正激电源更使用于多路输出,但实际上反击电源的多路输出交叉调整率比正激电源更难做,这主要是正激后面加了个偶合电感,而反激的漏感不是零.很多人做反激电源时都遇到这个问题,一路输出稳定性非常好,但多路输出时没有直接取反馈的路的电压会随其他路的负载变化而剧烈变化,这是什么原因呢?原来,在MOS关断,次级输出时能量的分配是有规律的,它是按漏感的大小来分配,具体是按匝比的平方来分配(这个可以证明,把其他路等效到一路就可得出结果)如:5V 3匝,漏感1uH,12V 7匝,如果漏感为(7/3)(平方)*1=5.4uH,则两路输出的电流变化率是一样的,没有交叉调整率的问题,但如果漏感不匹配时,就会有很多方面影响到输出调整率:1.次级漏感,这是明显的; 2,输入电压,如果设计不是很连续,则在高压时进入DCM状态,DCM时由于电流没有后面的平台,漏感影响更显著. 改进方法:1,变压器工艺,让功率比较大,电压比较低的绕组最靠近初级,其漏感最小,电压比较高,功率比较小的远离初级,这样就增加了其漏感.2,电路方法,电压输出较高的绕组在整流管前面加一个小的磁珠或一个小的电感,人为增加其漏感,这样电流的变化率就接近于主输出,电压就稳定.3,电压相近的输出,如:3.3V 5V,按我们的解释其漏感应该差别很小,这时就要把这两个绕组绕在同一层里面,甚至有时候5V要借用3.3的绕组,也就是所谓的堆叠绕法,来保证其漏感比.另外有时候电压不平衡是由于算出的匝数不为整数造成的,如半匝,当然半匝是有办法绕的,但半匝的绕法也是很危险的(可参考其他资料),这是我们可以通过二极管的压降来调整,如12V用7匝,5V用3匝,如果发现12V偏高,则12V借用5V的3匝,但剩下的4匝的起点从5V输出的整流管后面连接,则12V的整流管的压降为两组输出整流管的压降和,如:0.5(5V)+0.7(12V)=1.2V,另外12V输出负载变化时,其电流必然引起5V 整流管的压降变化,也就是5V输出变化,而5V的变化会通过反馈调整,这样也间接控制了12V.1、关于匝比平方的问题是这样的:电感值L=匝数的平方*AL(磁芯的电感因子).本质上还是电感量的问题.能量:P=1/2LI^2.2、漏感随便怎么调,如果不采取稳压措施一个绕组的负载状态(I)都会影响另一绕组.(个人观点)1.你说的问题是电感的电感量,而漏感是不遵守这个规律的,你可以把其他组的电压,电流,漏感等效到一组,然后就看到我的结论,只有每个绕组的电流上升率一样时,理论上电压就不会再随负载而变化.2.因为漏感受很多因素的影响,不可能完全调整到理想状态,所以实际上一个绕组还会影响另一个绕组,但可以把这个影响减到实际产品可应用的水平,而不需要加二次稳压.这个指的是每路输出的实际功率是看其负载的大小,而我说的是交叉稳定性,是两个事情,交叉稳定性不好时,其电压值在负载大小变化时变化很大.从一个朋友的角度我建议你还是先去多学点东西,再来发帖.<br>其实这是一个改进交叉调整率的方法之一,并不矛盾.其实还有很多方法来改进交叉调整率,如减小RCD电路的电阻,但会造成很大的耗能,所以没列在里面,还有能量再生绕组,它是把能量反送会电网,属于反激软开关的类型之一.你写了这么多,其实我看的出来,你压根就没理解我的说法.我已经告诉你怎么去把结果推出来,为何不去实验以下,你说我的方法无法实现,为何不照我由此推出的改进方法去试一下,实际上我已经帮很多人用此方法改进了交叉调整率,特别是在DVD,DVR,DVB里面.我将不再回复此帖,信不信由你.。

反激式电源中电磁干扰及其抑制

反激式电源中电磁干扰及其抑制李志江,吴国忠,钱照明(浙江大学电气工程学院,浙江杭州 310027)摘要:在介绍Flyback反激式DC/DC电源及其性能的基础上,主要讨论了该电源中的网侧谐波及其抑制,开关缓冲电路,光耦隔离等问题。

关键词:噪声;干扰;高次谐波;电磁干扰1 电路介绍反激式电源原理图如图1所示。

图1 反激式电源原理图输入为交流85~200V,经功率二极管整流桥变为直流,作为DC/DC反激变换器的输入,输出为三组直流:5V、15V、20V,另外还有一辅助电源5V,用来给光耦NEC2501供电。

控制电路为反馈控制,开关选用TOPSwitch电源芯片(TOP223)。

TOPSwitch为三端离线式PWM电源集成控制器,它将PWM控制器与功率开关MOSFET合为一体,采用TO-220或8脚DIP封装,除D、C 2脚外,其余6脚连在一起作为S端。

本电路中TOP223采用U DS>700V的MOSFET,f s=100kHz。

在这个Flyback反激式电源中,变压器原边绕组33匝,副边有四组:6匝(对应于输出U o2=5V)、11匝(对应于输出U o3=15V)、12匝(对应于输出U o1=20V)、6匝(对应于辅助电源U=5V)。

在副边,WY1和WY2为稳压器件,WY1输入在≥8V时,输出可稳在5V;WY2输入≥18V时,输出可稳在15V。

2 EMI分析开关电源工作时,其内部的电压和电流波形都是在非常短的时间内上升和下降的,所以开关电源本身就是一个噪声发生源。

开关电源的干扰按噪声干扰源种类可分为尖峰干扰和谐波干扰两种。

使电源产生的干扰不至于对电子系统和电网造成危害的根本办法就是采用耗能电路来削弱噪声发生源,或者切断电源噪声和电子系统、电网之间的耦合途径。

2.1 网侧高次谐波电流2.1.1 高次谐波电流的危害参照图1,交流输入电压V i经功率二极管整流桥变为正弦脉动电压,被电容C1平滑后成为直流,但电容电流的波形不是正弦波而是脉冲波。

超详细的反激式开关电源电路图讲解

反激式开关电源电路图讲解一,先分类开关电源的拓扑结构按照功率大小的分类如下:10W以内常用RCC(自激振荡)拓扑方式10W-100W以内常用反激式拓扑(75W以上电源有PF值要求)100W-300W 正激、双管反激、准谐振300W-500W 准谐振、双管正激、半桥等500W-2000W 双管正激、半桥、全桥2000W以上全桥二,重点在开关电源市场中,400W以下的电源大约占了市场的70-80%,而其中反激式电源又占大部分,几乎常见的消费类产品全是反激式电源。

优点:成本低,外围元件少,低耗能,适用于宽电压范围输入,可多组输出.缺点:输出纹波比较大。

(输出加低内阻滤波电容或加LC噪声滤波器可以改善)今天以最常用的反激开关电源的设计流程及元器件的选择方法为例。

给大家讲解如何读懂反激开关电源电路图!三,画框图一般来说,总的来分按变压器初测部分和次侧部分来说明。

开关电源的电路包括以下几个主要组成部分,如图1图1,反激开关电源框图四,原理图图2是反激式开关电源的原理图,就是在图1框图的基础上,对各个部分进行详细的设计,当然,这些设计都是按照一定步骤进行的。

下面会根据这个原理图进行各个部分的设计说明。

图2 典型反激开关电源原理图五,保险管图3 保险管先认识一下电源的安规元件—保险管如图3。

作用:安全防护。

在电源出现异常时,为了保护核心器件不受到损坏。

技术参数:额定电压 ,额定电流 ,熔断时间。

分类:快断、慢断、常规计算公式:其中:Po:输出功率η效率:(设计的评估值)Vinmin :最小的输入电压2:为经验值,在实际应用中,保险管的取值范围是理论值的1.5~3倍。

0.98: PF值六,NTC和MOVNTC 热敏电阻的位置如图4。

图4 NTC热敏电阻图4中的RT为NTC,电阻值随温度升高而降低,抑制开机时产生的浪涌电压形成的浪涌电流。

图4中RV为MOV压敏电阻,压敏电阻是一种限压型保护器件,过电压保护、防雷、抑制浪涌电流、吸收尖峰脉冲、限幅、高压灭弧、消噪、保护半导体元器件等七,XY电容图5 X和Y电容如图X电容,Y电容。

反激式开关电源辅助电路设计

反激式开关电源辅助电路设计反激式开关电源是一种常见的电源设计,常用于电子设备中。

为了提高开关电源的性能和稳定性,通常需要设计一些辅助电路来实现。

本文将介绍反激式开关电源辅助电路的设计原理和实施方法。

我们来了解一下反激式开关电源的工作原理。

反激式开关电源由输入电源、变压器、整流电路、滤波电路、开关管和控制电路等组成。

其中,开关管通过开关动作来控制输入电源与变压器的耦合,从而实现输入电源能量的传递。

为了提高开关电源的效率和稳定性,需要设计一些辅助电路来辅助实现开关管的控制和滤波。

一、过压保护电路过压保护电路是反激式开关电源中重要的辅助电路之一。

其作用是在输出电压超过设定值时,通过控制开关管的导通和断开来保护负载和开关管。

过压保护电路通常由比较器、参考电压源和控制电路等组成。

当输出电压超过设定值时,比较器会检测到这一变化,并通过控制电路来控制开关管的动作,从而实现过压保护的功能。

二、过流保护电路过流保护电路也是反激式开关电源中常用的辅助电路之一。

其作用是在输出电流超过设定值时,通过控制开关管的导通和断开来保护负载和开关管。

过流保护电路通常由电流传感器、比较器和控制电路等组成。

当输出电流超过设定值时,电流传感器会检测到这一变化,并通过控制电路来控制开关管的动作,从而实现过流保护的功能。

三、温度保护电路温度保护电路是为了防止开关电源因过热而损坏而设计的辅助电路。

温度保护电路通常由温度传感器、比较器和控制电路等组成。

当温度传感器检测到开关电源的温度超过设定值时,比较器会发出信号,并通过控制电路来控制开关管的动作,从而实现温度保护的功能。

四、软起动电路软起动电路是为了减小开关电源启动时的冲击电流而设计的辅助电路。

软起动电路通常由电容器、电阻器和继电器等组成。

在开关电源启动时,软起动电路会通过控制继电器的动作来实现对电源的逐渐接入,从而减小冲击电流的影响。

以上是反激式开关电源辅助电路的一些常见设计。

在实际应用中,根据具体的需求和要求,可能还需要设计其他辅助电路来满足特定的功能和性能要求。

反激式开关电源的设计

反激式开关电源的设计1.反激式开关电源的基本原理与拓扑结构2.反激式开关电源的设计步骤(1)选择合适的开关器件:根据设计需求确定开关器件的额定电流和电压。

应选择满足设计需求的高效开关器件,以确保电源的稳定性和可靠性。

(2)设计变压器:变压器是反激式开关电源中非常重要的组成部分,其设计影响着整个电源的性能。

变压器的设计应根据输入电压、输出电压及负载电流等确定变比。

(3)设计输入滤波器:输入滤波器主要用于去除输入电源的高频噪声和电磁干扰。

应根据设计要求选择合适的滤波器元件。

(4)选择输出滤波器:输出滤波器用于去除输出电压中的高频噪声和波动。

应选择满足设计要求的输出滤波器元件。

(5)选择控制器和反馈电路:反激式开关电源需要一个控制器来控制开关器件的开关频率和占空比。

应根据具体设计需求选择合适的控制器和反馈电路。

(6)设计保护电路:反激式开关电源应设计有相应的保护电路,以防止过流、过压和过温等情况的发生,保证电源的安全可靠运行。

(7)进行电路仿真和调试:应使用电子设计自动化工具进行电路仿真和调试,以验证电源设计的正确性和稳定性。

3.注意事项和常见问题(1)电源设计应考虑效率和性能的平衡,既要保持高效率,又要满足设计要求。

(2)电源设计时要合理布局电路板,降低电磁干扰和噪声。

(3)电源设计应注意选择合适的元件,在成本和性能之间进行权衡。

(4)在进行电路仿真和调试时,应注意保护器件和测试仪器的安全,避免电源短路和电流过大导致元器件损坏。

(5)设计完成后,应进行严格的测试和质量控制,确保电源的稳定性和可靠性。

总结:反激式开关电源是一种常见的开关电源拓扑结构,在设计中需要考虑元件选择、变压器设计、滤波器设计、控制器和反馈电路选择等多个因素。

合理的设计和调试能够确保电源的稳定性和可靠性,满足设备的电源需求。

反激式开关电源变压器共模传导干扰问题简析

反激式开关电源变压器共模传导干扰问题简析

反激式的开关电源变压器目前多被用于供电变电领域中,作为电源变压器的家族成员之一,反激式开关电源变压器在平时的工作应用过程中,也同样面临着传导噪声干扰的问题。

在今天的文章中,我们将会就这种电源变压器的传导噪声干扰产生原因,展开简要的分析和总结,希望能够对各位工程师有所帮助。

反激式的开关电源变压器在平时应用的过程中,所遭受的传导干扰主要有共模干扰和差模干扰两种情况。

共模干扰电流在零线与相线上的相位相等,而差模干扰电流在零线与相线上的相位相反。

差模干扰对总体传导干扰的影响较小,且主要集中在噪声频谱低频端,较容易抑制。

相比较而言,共模干扰对传导干扰的影响就非常大了,且主要处在噪声频谱的中频和高频频段。

对共模传导干扰的抑制是电子设备传导EMC设计中的难点,也是最主要的任务。

寄生电容在反激式电源变压器中的分布

与其他的变压器产品一样,在反激式开关电源的电路中,也同样会存在一些电压剧变的节点。

这些剧变的节点和电路中其他电势相对稳定的节点不同,它们的电压包含高强度的高频成分,因此我们通常将这些电压变化十分活跃的节点称为噪声活跃节点。

这些噪声活跃节点,其实就是开关电源电路中的共模传导干扰源,它作用于电路中的对地杂散电容就产生共模噪声电流ICM。

而反激式电椅变压器的主电路系统中,对EMI影响较大的对地杂散电容主要有以下几种,分别是功率开关管的漏极对地的寄生电容Cde、变压器。

反激式电源设计及应用五

反激式电源设计及应用五[电磁干扰] 反激式电源设计及应用五[电磁干扰原来的系列专题还有几个,春节前推出此电磁干扰,我尽量以图示来说明。

希望对大家有所帮助。

实际中如何确定差模和共模的比例。

这样可以看到实际的干扰中差模是多少,共模是多少。

以决定采取的措施。

贴一个例子。

前面一个图是有加4.7uF的X电容,剩下的基本是共模;后面是正常的波形。

峰值,准峰值,平均值的定义及测量。

哇!!频率抖动的作用原来如此。

由于RC的积分作用,所以会降低。

不是在欺骗仪器吗?!对此电源界存在争论,反过来想一下,难道标准就合理吗?管它呢,不管哪国的标准,过了就行了。

一个小问题,反馈控制特性和EMI 有关系吗?我想决大部分人的答案是没有关系,有的说有关系,因为他在实际中发现过(我记的21IC上有人问过)!什么原因?可能没人说的清。

同样输入,输出2的控制带宽和环路增益比输出1高,所以纹波小。

在相同的情况下,输出2要迫使脉冲的宽度更快速的变化(电压高时减小脉宽,反之相同),这恰恰就是频率抖动,所以可以改善EMI。

电流型控制IC比电压型相比具有自动前馈功能,更迅速的改变脉宽压制100Hz纹波,所以同等情况,EMI要好一些。

当然电压型的如果加了电压前馈能起到同样的功能。

低压出来去调制3842的第4脚,就可实现频率抖动功能。

几个因素对干扰的影响(摘自香港大学电力电子实验室资料)我们可以看出,波形和占空比只影响低频段的干扰。

上升和下降沿影响高频段。

为什么会有EMI还是来个图吧。

f1的值大概在6-10MHz之间,f2的值大概在20-30MHz之间,其频率会根据变压器漏感的大小,杂散电容的大小,器件输出电容的大小而变化,但频率大概在上述范围,但你没加RC吸收电路和共模滤波不是超强时,EMI曲线上明显的可以看到此两点。

把这两点抑制掉,再采取点其他措施,你都可能把Y电容拿掉。

传导干扰的差模的产生和抑制加差模电感是常用的方法,但在整流管后面时要注意。

反激式开关电源设计方法

反激式开关电源设计方法1.输入变压器设计:反激式开关电源的输入变压器主要用于实现能量的储存和传递。

其设计方法一般包括确定变压器的变比、计算绕线参数和计算磁芯截面积。

变比的选择要根据输入和输出电压的关系来确定,一般采用副边大于主边的变比。

绕线参数的计算要根据输入电压、输出功率和开关频率来确定。

磁芯截面积的计算要根据输入电压、输出功率和变频器频率来确定。

2.控制电路设计:反激式开关电源的控制电路主要用于实现开关管的开关和关断控制。

其设计方法一般包括选择适合的开关管和控制芯片、设计反馈电路和设计保护电路。

选择合适的开关管和控制芯片要考虑输入和输出电压、输出功率和开关频率等因素。

设计反馈电路主要是为了实现恒定的输出电压,一般采用反馈误差放大器和锁相环等。

设计保护电路主要是为了提高电源的可靠性和稳定性,一般包括过流保护、过压保护和过温保护等。

3.输出滤波电路设计:反激式开关电源的输出滤波电路主要用于滤除开关管开关过程中产生的高频脉冲噪声,保证输出电压的稳定性和纹波度。

其设计方法一般采用LC滤波器或电容滤波器。

LC滤波器具有较好的滤波效果,但体积较大,适用于功率较大的电源。

电容滤波器体积小,但滤波效果相对较差,适用于功率较小的电源。

4.保护电路设计:反激式开关电源的保护电路主要用于保护电源,防止出现过流、过压、过温等故障。

其设计方法一般包括选择合适的保护元件和设计合理的保护电路。

选择合适的保护元件要考虑其额定参数和动态特性,以满足电源的保护要求。

设计合理的保护电路要考虑多种故障情况,实现对电源的全方位保护。

以上是反激式开关电源设计的基本方法和步骤,设计师在实际设计过程中还需考虑电源的稳定性、可靠性、效率等因素,并根据具体的应用需求进行优化设计。

同时,还要注意电源设计中的安全性和可调度性,确保电源工作的稳定性和可靠性。

反激式(RCD)开关电源原理及设计

反激式(RCD)开关电源原理及设计因该电源是公司产品的一个配套使用,且各项指标都不是要求太高,故选用最常用的反激拓扑,这样既可以减小体积(给的体积不算大),还能降低成本,一举双的!反激拓扑的前身是Buck-Boost变换器,只不过就是在Buck-Boost变换器的开关管和续流二极管之间放入一个变压器,从而实现输入与输出电气隔离的一种方式,因此,反激变换器也就是带隔离的Buck-Boost变换器。

先学习下Buck-Boost变换器工作原理简单介绍下1.在管子打开的时候,二极管D1反向偏置关断,电流Is流过电感L,电感电流IL线性上升,储存能量!2.当管子关断时,电感电流不能突变,电感两端电压反向为上负下正,二极管D1正向偏置开通!给电容C充电及负载提供能量!3.接着开始下个周期!从上面工作可以看出,Buck-Boost变换器是先储能再释放能量,VS不直接向输出提供能量,而是管子打开时,把能量储存在电感,管子关断时,电感向输出提供能量!根据电流的流向,可以看出上边输出电压为负输出!根据伏秒法则Vin*Ton=Vout*ToffTon=T*DToff=T*(1-D)代入上式得Vin*D=Vout*(1-D)得到输出电压和占空比的关系Vout=Vin*D/(1-D)看下主要工作波形从波形图上可以看出,晶体管和二极管D1承受的电压应力都为Vs+Vo(也就是Vin+Vout);再看最后一个图,电感电流始终没有降到0,所以这种工作模式为电流连续模式(Ccm模式)。

如果再此状态下把电感的电感量减小,减到一定条件下,会出现这个波形!从上图可以看出,电感电流始终降到0后再到最大,所以这种模式叫不连续模式(DCM模式)。

把上边的Buck-Boost变换器的开关管和续流管之间加上一个变压器就会变成反激变换器!还是和上边一样,先把原理大概讲下:1.开关开通,变压器初级电感电流在输入电压的作用下线性上升,储存能量。

变压器初级感应电压到次级,次级二极管D反向偏置关断。

反激电路设计DCDC-65V3A(共15页)

反激电路设计DCDC-65V3A(共15页)文档标题:反激电路设计DCDC-65V3A

1. 引言

本文档是关于反激电路设计的详细说明,重点介绍了DCDC-

65V3A反激电路的设计原理、电路图、元器件选择和性能测试结果等内容。

2. 设计原理

反激电路是一种常用的电源转换器,能够将高电压转换成低电压,并且提供稳定的电流输出。

DCDC-65V3A反激电路采用了特

定的电路拓扑,通过变压器和开关管实现高效的电能转换。

3. 电路图

在本节中,我们展示了DCDC-65V3A反激电路的详细电路图,包括输入滤波电路、功率开关电路、控制电路和输出滤波电路等部分。

4. 元器件选择

为了保证反激电路的性能和可靠性,本节介绍了各个元器件的

选择原则和具体型号,包括变压器、电容、电感、开关管和控制芯

片等。

5. 性能测试结果

为了验证DCDC-65V3A反激电路的性能指标,我们对该电路

进行了一系列的性能测试,如输出电压稳定性、效率、负载能力等。

本节列出了测试结果并进行了分析和讨论。

6. 结论

根据本文档的介绍和测试结果,DCDC-65V3A反激电路在设

计原理、电路图、元器件选择和性能等方面表现出良好的性能。

该

设计可用于特定的应用场景,提供稳定、高效的电源转换功能。

附录

本文档的附录中包含了详细的参考资料和文献引用,以便读者

进一步深入了解反激电路设计和相关领域的知识。

以上是对反激电路设计DCDC-65V3A的文档简要概述,具体

内容请参阅完整文档。

反激式开关电源实用电磁干扰设计方法

反激式开关电源实用电磁干扰设计方法作者:刘勇刚来源:《科学与财富》2019年第11期摘要:本文叙述了反激式开关电源中电磁干扰(EMI)产生的一些原因,根据EMI产生的不同原因的理论分析,结合工程实践当中的经验,给出了合适的、实用的解决方法和一些关键参数的计算方法,对反激式开关电源的EMI工程设计有一定的实际指导意义。

关键词:反激;EMI设计;开关电源0.引言反激式变换器由于具有一些显著的优点,如:电路元件少、原副边电气隔离、对输入电压变化的适应性强等等,它被广泛运用于中、小功率的AC/DC开关电源中。

但同时,它也会或多或少的带来了一些电磁干扰(EMI),因此在某些应用场合,特别是在一些对EMI比较敏感的应用场合或区域,就需要对EMI进行处理,也就是进行EMI设计。

1. 反激式变换器EMI设计反激式开关电源在AC/DC电源中的电路原理图如图1所示,具体的工作原理就不再赘述。

由于开关管或二极管不断的导通、关断,导致了电路中电压和电流的急剧变化,也就是du/dt和di/dt,这也就是产生EMI的源头。

在一次侧,当MOSFET关断时,由于变压器漏感Llk和MOSFET寄生电容Coss的谐振,会在MOSFET上形成很高的电压尖峰,如图2所示。

这个电压尖峰含有丰富的谐波,会造成严重的EMI,所以需要一个电路来抑制和吸收该电压尖峰。

通常我们用RCD电路作为吸收电路。

吸收电路中的电容电压随着输入电压增加而减小,所以我们以最低输入电压及满载条件来确定。

因此,消耗在吸收电路上的能量:而这些能量是消耗在电阻上的,所以吸收电路上的电阻:吸收电路里面电容上的纹波电压:一般来说,5~10%的纹波电压是比较合适的。

因此,吸收电路中的电容值可由上式计算得到。

在二次侧,由于次级漏感Lls和输出二极管的节电容Cd谐振,同样会在输出二极管上产生较大的高频电压尖峰,恶化电磁环境。

输出二极管D1先不接RC吸收电路时,在最大输入电压、最大负载的条件下,用示波器(不打带宽)测出二极管电压尖峰波形的振荡频率f1;然后在二极管上并联一个合适的电容,使并联电容后的二极管电压尖峰的振荡频率减小为之前的一半。

反激式电源设计及应用五[电磁干扰之共模部分]

![反激式电源设计及应用五[电磁干扰之共模部分]](https://img.taocdn.com/s3/m/0ca25851f01dc281e53af079.png)

costdown: /100 [第19帖]

07-27 11:34:

这算不算作弊?从理论上说我们只是骗了测试设备? 回复第19帖 给第19帖作者加分

cmg: /100 [第21帖]

07-27 11:59:

这与作弊有什么关系,我们也没有骗设备,因为确实流到外面的电流小了。 回复第21帖 给第21帖作者加分

2004-8-10

反激式电源设计及应用五[电磁干扰之共模部分]

页码,5/15

过EMC和安规就可以了,没规定不可以。 回复第41帖 给第41帖作者加分

dragon:

/100 [第47帖]

07-28 15:13:

在 我 们 的 充 电 器 产 品 中 ,测 试 传 导 时 要 求 输 出 接 地 ,即 C3 无 穷 大 ,呜 呜...而 且 没 有 Y 电 容 和 共 模 电 感 C1/C2很小?

sometimes:

/100 [第30帖]

07-27 12:52:

如果增加法拉第屏蔽的话,应该可以消除一些影响吧。 俺的确没有去过EMI实验室,而且没见过任何测试EMI的设备,呜呜~

回复第30帖 给第30帖作者加分

cmg: /100 [第34帖]

07-27 13:06:

确实这样,漏极和散热片之间应该加一个屏蔽层,接到MOS源极,有的IC, 片是源极,就很容易处理。

重新刷新 | 收藏本主题 07-26 16:25:

虽然传导干扰并不要求屏蔽室,但实际上各个实验室都用的是全屏蔽房间。 这样使电源与地线有更大的电容,实际增加了传导高频部分(共模)通过的难度。 3线时,由于电源与地线距离很近,电容很大,原理上EMI更难通过一些。但同样因为很近,可以采取一些两线没法采取的方法 加两粒小的Y电容,可以把高频部分(共模)很好的短路掉,又容易通过,任何事情都是有利又有弊。我们以第一种情

反激式电源设计

如何设计返驰式隔离电源导言本文以FPS为例来介绍如何设计返驰式隔离电源。

设计电源供应器基本上是很花功夫的工作,需要对许多变量反复作演算与取舍。

我们列出并说明一步一步的设计程序期望使设计电源供应器能容易一些。

文章最后之辅助设计软件FPS Design Assistant包含本文介绍之相关计算式,可让设计过程更有效率。

如何设计FLYBACK隔离电源供应器图1是使用FPS(Fairchild Power Switcher)返驰式隔离电源转换器的基本线路图,本文并会以此为参考线路来说明如何设计FLYBACK隔离电源供应器。

因为运用整合MOSFET、PWM及其它周边线路于单一封装的FPS,比利用独立之MOSFET及PWM控制器来设计电源供应器要简单许多。

在设计电源供应器会考虑变压器之设计、输出滤波电感、输出与输入电容的选择及封闭回路补偿的计算。

因此我们按照图1之参考线路,依特定的步骤来设计我们所需之线路。

最后附录范例,则是利用此步骤而设计的辅助软件来帮助我们完成整个线路计算。

图1:基本的flyback隔离电源转换器设计步骤本文将以目前的参考线路来说明设计的步骤。

而几乎所有FPS其第一脚至第四脚的功能定义是不变的。

因此此参考线路适合大部份的FPS。

步骤1 决定系统规格:●输入电压范围(V line min及V line max)●输入交流电频率●最大输出功率(P out)预估的效率(ηeff):首先我们需要预估系统效率以计算最大输入功率。

当没有资料供参考时,一般我们会在低电压输出应用时,效率设在ηeff = 0.7~0.75。

在高电压输出应用时则设ηeff = 0.8~0.85。

●以预设的效率可算出输入功率为:若在多组输出的状况下,每组输出所占之比例系数为:其中P o(n)为第N组之最大输出,若电源供应器只有单组输出则K L(n) =1,考虑最大输入功率以选用适当的组件(如最适当的FPS)。

步骤2决定输入滤波电容容值(C DC)及其电压V DC之范围:最大V DC之涟波电压如下式:其中D ch是C DC电容充电工作周期如图2所示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

cmg: /100 [第81帖]

08-02 12:53:

“静地”是我自己的定义,非标准叫法。次级地之所以安静是因为Y电容的存在,如果 能 不 好,次 级 就 不 是 静 地 了。从 上 面 图 上 可 看 到, Y电 容 不 是 理 想 的,它 有 ESL,所 以 高 了,而共模干扰恰恰是高频信号。所以次级在高频时就不是静地了,大面积铺地就加大了 原因:如果次级是信号线,实际上加大次级地(大面积铺地)是很好的:减小辐射,提高 关电源里面是大的脉冲电流,大面积铺地(不知你的加大地是不是这个意思)容易造成地 路流。产生辐射,另外辐射的磁通通过大的共模电流回路(电源,屏蔽地,LISN,电源 电流。

2004-8-10

反激式电源设计及应用五[电磁干扰之共模部分]

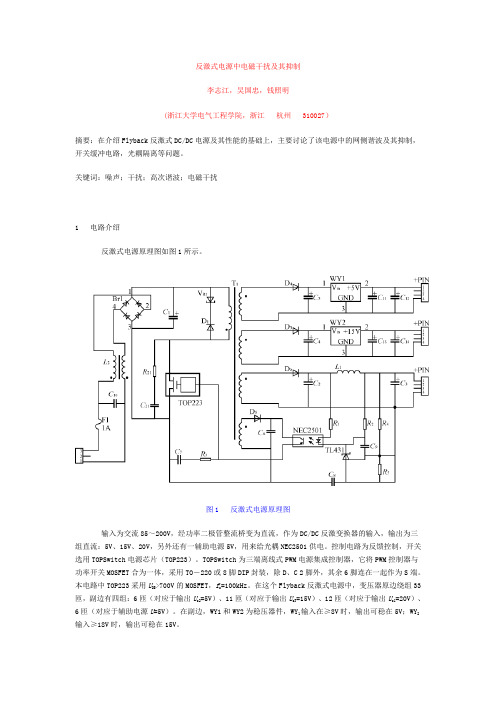

共模EMI交流等效电路。

页码,2/15

C1的大小与漏极连接的面积跟正比,布板时减小漏极的面积是个好方法。漏极加个散热片接源极可减少EMI高频和 初次级的杂散电容,夹层绕法C2会很大,可能需要加屏蔽,C3是次级与地的等效电容,C2,C3一般远远大于C1,所以 电流流通路径。

07-27 13:03:

是指测试地的电流,因为测试地是和大地连在一起的。 初级地和测试地当然有电容了,但是它们的电压没有相对变化,所以不形成电 位是相等的,当然不用去考虑。

回复第33帖 给第33帖作者加分

smps: /100 [第25帖]

07-27 12:36:

c3与什么相关呢? 回复第25帖 给第25帖作者加分

costdown: /100 [第19帖]

07-27 11:34:

这算不算作弊?从理论上说我们只是骗了测试设备? 回复第19帖 给第19帖作者加分

cmg: /100 [第21帖]

07-27 11:59:

这与作弊有什么关系,我们也没有骗设备,因为确实流到外面的电流小了。 回复第21帖 给第21帖作者加分

sometimes:

/100 [第30帖]

07-27 12:52:

如果增加法拉第屏蔽的话,应该可以消除一些影响吧。 俺的确没有去过EMI实验室,而且没见过任何测试EMI的设备,呜呜~

回复第30帖 给第30帖作者加分

cmg: /100 [第34帖]

07-27 13:06:

确实这样,漏极和散热片之间应该加一个屏蔽层,接到MOS源极,有的IC, 片是源极,就很容易处理。

回复第40帖 给第40帖作者加分

jqun: /100 [第38帖]

07-27 14:15:

有些电源是初、次级分别对安全地接电容,而初次极之间没有,这样会怎样?谢谢。 回复第38帖 给第38帖作者加分

cmg: /100 [第41帖]

07-27 16:22:

/bbs/d/19/7715.html PDF 文件使用 "FinePrint pdfFactory" 试用版本创建

07-27 12:29: 07-27 12:31: [前天 11:57]

07-26 16:45:

/bbs/d/19/7715.html PDF 文件使用 "FinePrint pdfFactory" 试用版本创建

回复第3帖 给第3帖作者加分

wb: /100 [第4帖]

07-26 17:07:

CMG大师,好常时间不见了,好久没有得到您的教诲了。 回复第4帖 给第4帖作者加分

boland: /100 [第68帖]

07-30 16:52:

图3 如何看待输入的大电解电容,等效图中用黄线是代表交流短路吗? 还有为什么把它与右边的回路短开, 难到杂讯不会从电容的回路消耗一部分吗

反激式电源设计及应用五[电磁干扰之共模部分]

页码,1/15

登陆&注

论坛首页 -> 电子电源综合区

cmg: /100 [第1帖]

主题:反激式电源设计及应用五[电磁干扰之共模部分] 前面已经介绍了差模部分,为避免一个帖子太长,打开费劲,所以重起了一帖。 主要目的是给电源的初学者介绍一些基本知识。 干扰的测量

回复第68帖 给第68帖作者加分

sometimes:

/100 [第9帖]

07-26 18:58:

我想问下,C1和C3在实际电路中是如何产生的?? 回复第9帖 给第9帖作者加分

ridgewang:

/100 [第12帖]

07-27 09:21:

任何干扰,它一定要回到产生它的源,不采取措施的话,只有通过空间分布,以场的形式返回,这个看不 就可等效为一个分布电容。其二,我想地和屏蔽室是接在一起的,测量时,无形之中就增大了分布电容 二。从EMC的测试,是不是可以得出这样一个结论?这里,我们把干扰叫做没用的信号,无论该信号多强 限于开关电源内部,不辐射、传导到外面都是允许的!

如果是单纯的脑干结构的地线,加大一些或加焊锡增厚,当然可以减小ESR,ESL(高 ESL),是 对 EMI有 帮 助 的。但 我 说 的 不 是 这 种 情 况 : 你 没 见 我 说 的 是 “ 不 问 青 红 皂 白 义,否则解释起来很费劲。

/bbs/d/19/7715.html PDF 文件使用 "FinePrint pdfFactory" 试用版本创建

2004-8-10

反激式电源设计及应用五[电磁干扰之共模部分]

页码,5/15

过EMC和安规就可以了,没规定不可以。 回复第41帖 给第41帖作者加分

dragon:

/100 [第47帖]

07-28 15:13:

在 我 们 的 充 电 器 产 品 中 ,测 试 传 导 时 要 求 输 出 接 地 ,即 C3 无 穷 大 ,呜 呜...而 且 没 有 Y 电 容 和 共 模 电 感 C1/C2很小?

cmg: /100 [第24帖] 哈哈,调出来就用,还真没注意。 回复第24帖 给第24帖作者加分

smps: /100 [第101帖] 我们在整流桥上并电容是否分为两种情况考虑: 1。当考虑共模成分时,应该邻角并电容? 2。当考虑差模成分时,应该对角并电容? 回复第101帖 给第101帖作者加分

cmg: /100 [第3帖]

回复第22帖 给第22帖作者加分 20

sometimes:

/100 [第26帖]

07-27 12:37:

我指的是,有些电源会把散热器接大地,也就是和机壳接在一起,这样会有什么影响? 回复第26帖 给第26帖作者加分

cmg: /100 [第27帖]

07-27 12:42:

如果不采取其他措施,EMI会变差了。 回复第27帖 给第27帖作者加分 30

重新刷新 | 收藏本主题 07-26 16:25:

Байду номын сангаас

虽然传导干扰并不要求屏蔽室,但实际上各个实验室都用的是全屏蔽房间。 这样使电源与地线有更大的电容,实际增加了传导高频部分(共模)通过的难度。 3线时,由于电源与地线距离很近,电容很大,原理上EMI更难通过一些。但同样因为很近,可以采取一些两线没法采取的方法 加两粒小的Y电容,可以把高频部分(共模)很好的短路掉,又容易通过,任何事情都是有利又有弊。我们以第一种情

cmg: /100 [第74帖]

08-01 08:58:

不要忘了EMI是高频信号,静地是个相对的概念。

回复第74帖 给第74帖作者加分

jameszeng: /100 [第78帖]

08-02 09:51:

次级地加大,相应对大地的电容也就增大了,对吧,我们都认可它们是静地,这您也说过, 地加大对EMI的影响应该是微小吧,并且从你上面的等效图上可以看出,次级地加大,可减 样看来,应该是对EMI有帮助才对啊,请建议。

/bbs/d/19/7715.html PDF 文件使用 "FinePrint pdfFactory" 试用版本创建

2004-8-10

反激式电源设计及应用五[电磁干扰之共模部分]

页码,4/15

回复第18帖 给第18帖作者加分

cmg: /100 [第15帖]

07-27 10:40:

变压器对地的问题:

回复第15帖 给第15帖作者加分 30

/bbs/d/19/7715.html PDF 文件使用 "FinePrint pdfFactory" 试用版本创建

07-27 11:52:

2004-8-10

反激式电源设计及应用五[电磁干扰之共模部分]

页码,3/15

sometimes:

/100 [第20帖]

很多情况下,会把散热器接地,那么不是增加C1和C3的值了么? 回复第20帖 给第20帖作者加分

cmg: /100 [第22帖]

07-27 12:05:

散热器是接初级的源极,既干扰电压的地线,C1,C3的地是测试地,它是铁板连接到大地的 个你可能没到过EMI测试实验室看过,看过就不会有疑问了。

ridgewang:

/100 [第17帖]

07-27 11:13:

我是指对抑制共模干扰是不是更好、更有利于EMC通过 回复第17帖 给第17帖作者加分

cmg: /100 [第18帖]

07-27 11:29:

是这样,第三跟线与测量时的大地是连在一起的,加第三跟线以后,电源与地的距离是零了,即 大了,所以共模电流会加大,既EMI升高,共模电流的回流主要靠C4 Y电容。解决方法是从第三跟 到L,N线,使小Y电容与LISN的50欧姆检测电阻并联。这样初次级Y电容没处理完的共模电流回从 免其全部流过50欧姆电阻。图我就不画了。

回复第1帖 给第1帖作者加分 300

cmg: /100 [第2帖]

07-26 16:35:

复习一下干扰源,这个干扰源是最根本的干扰源,差模,共模,辐射都是由它产生动力。看这个帖子之前,最好看一下差模部分 子。