Hardware support for flexible distributed shared memory

MT3339

Pin Assignment and Descriptions .............................................................................................. 9 2.1 2.2 Pin assignment (top view) .................................................................................................... 9 Pin descriptions .................................................................................................................... 9

ห้องสมุดไป่ตู้

Description Update TFBGA ball map and pin description Update pin-mux and strap information Update RF part description Update System overview Update RF part electrical characteristics Update analog part electrical characteristics Update RF LDO electrical characteristics Update power scheme Add RTC domain power scheme Modify according to YC Chien’s suggestion Update by JN Yang about UART baud rate and SPI/I2C clock rate Update RF related description Update system overview by Andy Lee Update host interface related description Update power scheme Update block diagram Update crystal frequency range Update external LNA related information Update power scheme diagram and EEPROM I2C interface timing diagram Update power related description Update footprint size Change minimum input power to 2.7V Sync PIN naming of DC characteristic table and change minimum input power to 2.8V Update power scheme and RF information Update description of 32K_OUT pin Add ECLK and SYNC description Add 1.2V IO characteristic for TIMER and 32K_OUT and update serial flash size to 128Mb Remove description about factory testing and internal SRAM size Remove description about strap function tcxo on/off 1. Update RTC leakage information to typ 2. Update package dimensions information Update RF related descriptions 1. Remove Vcc description in 6.3.1 2. Add strap pin tldo_sw_sel description Change MAX of VIH for TIMER and 32K_OUT to 3.6V Change description in 5.20 about CLDO off Add RF LNA MIN of VGA gain and MAX of noise figure © 2011 MediaTek Inc. Page 2 of 37

Seagate GoFlex Desk 外接硬盘说明书

Perfect for when you need to:• S tore or back up photos, movies, music and documents • A ccess your files with both PC and Mac® computers Capacities500GB, 1TB, 2TB, 3TBProtect, store and access files through the interface of your choice with the world’s most versatile drive. The GoFlex™ Desk external drive delivers high-capacity storage and automatic, continuous backup with encryption for all your files with its pre-loaded software. The included plug-and-play USB 2.0 or USB 3.0 adapter makes it easy to connect to your PC or Mac® computer and it displays the drive’s available storage capacity. As the world’s most upgradable external desktop drive, you now have the ability to upgrade your connection interface to suit your needs. Plus, the option to place the drive vertically or horizontally complements any desktop.Access files with the interface of your choice.Available with the standard USB 2.0 interface or the USB 3.0 interface, or upgrade to the FireWire® 800 adapter. Free your files.With the included NTFS driver for Mac®, you can now interchangeably store and access files from PC and Mac computers without reformatting. The NTFS driver is simply installed once on your Mac computer, allowing it to access and store files in a PC compatible format*.SuperSpeed USB 3.0 for Faster PerformanceThe GoFlex Desk drive is available with a USB 3.0 interface that provides up to 10x faster data transfer rates compared to USB 2.0 interfaces. USB 3.0 is backward compatible with USB 2.0 interfaces so you have the flexibility to access files from any PC.* Reformatting to HFS+ required to use backup software for Mac or Time Machine® softwareHighlights• USB 2.0 or USB 3.0 Plug-and-play• Easy-to-use pre-loaded backup software with encryption• World’s most versatile external drive - upgrade to a faster interface with a GoFlex™ Desk desktop adapter• Includes GoFlex Desk USB 2.0 or USB 3.0 adapter with capacity gauge display• Offers both vertical and horizontal drive orientation• 2-year limited warranty© 2010 Seagate Technology LLC. All rights reserved. Seagate, Seagate Technology, the Wave logo, FreeAgent and GoFlex are trademarks or registered trademarks of Seagate Technology LLC or one of its affiliated companies in the United States and/or other countries. All other trademarks or registered trademarks are the property of their respective owners. When referring to drive capacity, one gigabyte, or GB, equals one billion bytes and one terabyte, or TB, equals one thousand billion bytes. Your computer’s operating system may use a different standard of measurement and report a lower capacity. In addition, some of the listed capacity is used for formatting and other functions and will not be available for data storage. The export or re-export of hardware or software containing encryption may be regulated by the U.S. Department of Commerce, Bureau of Industry and Security (for more information, visit ). Actual data rates may vary depending on operating environment and other factors. Seagate reserves the right to change, without notice, product offerings or specifications. DS1709.3 1009-AMERProduct Dimensions 6.22in L x 4.88in W x 1.73in D (158mm x 124mm x 44mm)Weight: 2.38lb (1.08kg)Retail Packaging SpecsBox dimensions: 7.87in L x 9.06in W x 3.54in D (200mm x 230mm x 90mm) Box weight: 2.93lb (1.33kg)Master carton dimensions: 14.96in L x 9.52in W x 8.58in D (372mm x 242mm x 218mm) Master carton weight: 12.44lb (5.66kg)Master carton quantity: 4Master cartons per pallet: 60Pallet dimensions: 43.93in L x 38.11in W x 47.76in D (1,116mm x 968mm x 1,213mm)Pallet weight: 785lb (356.80kg)Pallet layers: 5System Requirements• Windows ® 7, Windows Vista ®, Windows ® XP (32-bit & 64-bit) operating system or • O perating system Max OS X 10.4.6 Tiger or higher, 10.5 Leopard or 10.6 Snow Leopard (the 32-bit kernel). Reformatting for Mac may be required.• USB 2.0 portCompatibility may vary depending on user’s hardware configuration and operating systemInside the Box• GoFlex ™ Desk external drive• Backup and encryption software pre-loaded on drive • NTFS driver for Mac ® pre-loaded on drive*• GoFlex ™ Desk USB 2.0 or USB 3.0 adapter base with capacity gauge • Power supply•5-foot (150cm) USB 2.0 cable or 4-foot (120cm) USB 3.0 cable • Quick start guide• 2-year limited warranty。

电机控制开发套件motorBench 2.25说明书

Dashboard/…/motorBench 2.25 ReleasemotorBench 2.25.0 Release NotesCreated by Fernando Garibaldi, last modified by Jason Sachs 2 minutes agoOverview of motorBench® Development SuiteWhat’s NewSystem RequirementsSupported HardwareHigh-voltage hardwareOther hardware required with both low-voltage and high-voltage setupsInstalling motorBench® Development Suite 2.25.0RepairsMotor Control Fixed IssuesChanges since revision 2.15Known IssuesMotor Control IssuesLimitationsSupported DevicesSoftware LimitationsMotor Control LimitationsSupported Motor ParametersCustomer SupportThe Microchip Web SiteAdditional SupportOverview of motorBench® Development SuiteMicrochip motorBench Development Suite is a graphical, interactive development environment designed to help motor control engineers to design and implement motor control systems, from very basic to very sophisticated ones.motorBench® Development Suite allows the user to:configure a motor systemmeasure motor parameterstune the controller gainsgenerate code to spin the motorWhat’s New1. Motor Control Application Framework (MCAF) R5 – see MCAF User's Guide for more information.a. Added support for dsPIC33CK256MP508b. Added Angle-tracking PLL (ATPLL) supportc. Improved Customize page support in motorBench2. Customizea. Allow advanced customization of MCAF code generation3. Measurea. Updated fault handing logic to detect if an invalid load is connected to the inverter before starting motor parameter measurement or Board calibrationb. Improvements to support motors with large values of stator inductancec. Improvements to support motors with large inertia and high cogging torque4. MCC Integrationa. Improved support for MCC-generated peripheral and system initialization code5. Device Supporta. Added support for dsPIC33CK256MP508i. This device is not yet supported by the motor parameter measurement featureSystem RequirementsMPLAB X 5.30 or later.XC16 compiler version:Firmware generated by motorBench® Development Suite has been tested with XC16 1.41.33EP devices: XC16 1.36 or later are expected to work with motorBench®Development Suite but have not been extensively tested.33CK devices: Either of the following is required:XC16 1.50 or laterXC16 1.41 with DFP 1.2.66 or laterMPLAB Code Configurator®(MCC) Plugin Version 3.95.0 or laterPIC24/dsPIC33/PIC32MM library 1.166.0 or laterSupported HardwareThis release of motorBench®Development Suite supports both low-voltage and high-voltage setups.Low-voltage hardware1. dsPICDEM MCLV-2 Development Board [Part Number: DM330021-2]2. dsPIC33EP256MC506 External Op Amp Motor Control PIM [Part Number: MA330031-2] with silicon revision A8 or dsPIC33CK256MP508 External Op Amp Motor Control Pim[Part Number: MA330041-1].3. A three phase PMSM or BLDC motor that is compatible with 24V, such as the Hurst 24V BLDC motor DMA0204024B101 [Part Number: AC300022].4. 24V power supply [Part Number: AC002013] - ensure this connects to AC mains using a 2-prong cable. If you have an AC002013 with a 3-prong cable, please contact Microchip.High-voltage hardware1. dsPICDEM MCHV-2 Development Board [Part Number: DM330023-2] or dsPICDEM MCHV-3 Development Board [Part Number: DM330023-3]AC mains voltages 120VAC 60Hz and 220VAC 50Hz have been tested.2. dsPIC33EP256MC506 External Op Amp Motor Control PIM [Part Number: MA330031-2] with silicon revision A8 or dsPIC33CK256MP508 External Op Amp Motor Control Pim[Part Number: MA330041-1].3. A three phase PMSM or BLDC motor that is compatible with rectified AC mains voltage, such as the Leadshine 400W BLDC motor EL5-M0400-1-24 [Part Number: AC300025].Other hardware required with both low-voltage and high-voltage setups1. A USB-to-logic-level-UART converter from the following list:a. Saelig USB-COM-U or USB-COM-U13b. TRENDnet TU-S9 v2.02. Programming tool - one of the following tools: Real ICE, ICD33. Board calibration load resistors - this is optional, please see motorBench® Development Suite User's Guide document for more detailsInstalling motorBench ® Development Suite 2.25.0To install the MPLAB ® Code Configurator v3.95 Plugin1. In the MPLAB® X IDE, select Plugins from the Tools menu2. Select the Available Plugins tab3. Check the box for the MPLAB® Code Configurator v3, and click on InstallTo install different peripheral library version or motorBench ® Development Suite version when connected to internet1. Create a project with dsPIC33EP256MC506 or dsPIC33CK256MP508, or use the sample project.2. Open MPLAB® Code Configurator3. In the Versions tab under PIC24/dsPIC33/PIC32MM MCUs, find the multiple library versions (loaded version is indicated by the green check mark)4. Right-click on the required version of the library and select Mark for Load5. In the Versions tab under motorBench ® Development Suite find the multiple library versions (loaded version is indicated by the green check mark)6. Right-click on the 2.25.0 version of the library and select Mark for Load7. Click on Load Selected Libraries button to load the marked libraries.To install different peripheral library version or motorBench® Development Suite version when not connected to internet1. In the MPLAB® X IDE, select Options from the Tools menu2. Select Plugins tab3. Click on Install Library4. Add pic24-dspic33-pic32mm_v1.166.mc3lib5. Add motorBench_2.25.0.mc3lib6. Restart MPLAB® X IDERepairsMotor Control Fixed IssuesChanges since revision 2.15The following aspects of motorBench® Development Suite and the Motor Control Application Framework (MCAF) have been updated:MCAF has been updated to R5, includingChanges in R2:Support for DC link compensationSupport for overmodulationSupport for wider range of low-voltage motorsUpdated HAL for future MCHV2 supportUpdated Motor Control LibraryNumerous minor fixesChanges in R3:MCC system module compatibilityMCHV-2 and MCHV-3 supportInverter maximum current now has a 1:1 ratio with the maximum commanded dq-frame current of the drive, operating in FOC (in R2 this incorporated a deratingfactor)Other minor fixesChanges in R4:MCC peripheral supportParameter customizationQuadrature encoder supportAdded new startup method (Weathervane startup)Other minor fixesChanges in R5:Added device support for dsPIC33CK256MP508Added Angle-tracking PLL (ATPLL) sensorless estimatorImproved motorBench Customize page supportOther minor fixesSections in this release notes affected:Other RequirementsLimitationsSupported Motor ParametersKnown IssuesPlease note:We do not recommend using the MCP2200 USB to RS232 Demo Board [Part number: MCP2200EV-VCP ] with this release of motorBench® Development Suite.While testing, we have observed more frequent occurrence of a serial communication timeout issue while running motor parameter measurement using this cable.See Known Issues section of this document for more information (MCGUI-1141)Motor parameter measurement is only supported on dsPIC33EP256MC506 device.Issue Key Summary WorkaroundMBPLAN-673Serial port does not get closed programmatically when MCC exits during motor parametermeasurementIf you exit SC during execution, restart MPLAB X.MBPLAN-932Exception during attempted creation of a runtime properties class No workaround needed, this issue doesn't have an impact on thefunctionality.MBPLAN-984Improve error reporting for SC build errors in the event of a code generation failureMBPLAN-1095Switching projects after loading motorBench erroneously allows motorBench code to generate for new projectMBPLAN-1160"Import Motor" and "Export Motor" buttons can be clicked multiple times, opening multiple dialog boxesMotor Control IssuesIssue Key SummaryDB_MC-411Current calibration happens only once (at part reset) rather than upon entry to MCSM_RESET stateDB_MC-560Speed controller exhibits chattering behavior at voltage saturation hysteresis boundary (MCAF)DB_MC-978"Soft start" gate drive in board_service.c has duty cycle that is too smallDB_MC-1092PLL estimator may not converge into rotor reference frame while using the Classic startup method in MCAFDB_MC-1396PLL calculations in code generation do not allow motor.velocity.nominal to be more than 1250Hz electrical (=20kHz/8/2)DB_MC-1415With some motors and 12V operation, increased velocity margin improves startup but creates unstable estimatorDB_MC-1430Quanum MT4012 unstable in closed-loop operation at 4200 RPM speed and aboveDB_MC-1491With Quanum MT4012, MCAF may not detect stallDB_MC-1492Quanum MT4012 Stalls on pressing 'S3'(reverse) at low speeds and on changes to speed command potentiometerDB_MC-1495Anaheim BLY342D-24V-3000, BLY342D-48V-3200 motors creates hardware over-current during stall-detect testingDB_MC-1521Closed loop speed step response overshoot - MCHV2, Leadshine 400DB_MC-1892Some motors with extreme parameters may produce out-of-range error for stall_detect.group.timerCountsVarianceDetect (detected in Monte Carlo analysis)DB_MC-1920Board service isrCount-based timing is not guaranteedDB_MC-1922LED patterns not displayed when in the TEST_DISABLE or TEST_ENABLE statesDB_MC-2122BLWS232D motor startup in QEI mode causes a false detect for stall-detectionDB_MC-2213Deadtime needs to be changed in both MCC and motorBench to affect codeDB_MC-2275Large current rampup times may not start (STARTUP_TORQUE_RAMPUP_RATE = 0)DB_MC-2309QEI tracking loop Kp and Ki produce out-of-range errors for low-speed motorsDB_MC-2323Weathervane transition state should not have active damping enabledDB_MC-2387DC link voltage measurement may have too much phase delay for MCAF DC link compensation to work effectivelyDB_MC-2606MCC-generated code has incorrect IESO/FNOSC config bits for 33CKDB_MC-2671MCAF_CaptureTimestamp calls incorrect timer function for 33CK devicesDB_MC-2785Current sense signal integrity issue with 33CK during overmodulationLimitationsSupported DevicesmotorBench® Development Suite supports these devices:1. dsPIC33EP256MC5062. dsPIC33CK256MP508Software LimitationsmotorBench® Development Suite is tested for serial communication using Windows 7 and Windows 10 platforms. Other platforms may work with standard baud rates, but this operation has not yet been verified.Motor Control LimitationsFollowing are the known limitations for this release of motorBench® Development Suite:1. One mechanical load - constant load. This represents a mechanical load with constant inertia, viscous damping, and friction. The velocity control loop can generally rejectexternal disturbance torques, within the rated current of the motor and board, and within the bandwidth of the velocity control loop. Mechanical loads with time-varying or angle-varying inertia, viscous damping, and friction, such as a blower, compressor, or pump, are currently not supported.2. One motor type - PMSMMCLV-2:The reference motor is the Nidec Hurst motor DMA0204024B101 (MicrochipDirect part number AC300022). Microchip has also validated motorBench® DevelopmentSuite (including motor parameter measurement) with motors with parameters plotted below. Please also read the following section on Supported Motor Parameters. IfmotorBench® Development Suite is unable to spin a motor successfully, please contact Microchip staff for additional assistance.(Note: Mechanical time constant (2/3)×JR/Ke² represents the time constant of velocity acceleration under an open-loop synchronous-frame voltage step, neglecting the effects of inductance, with J, R, and Ke expressed in canonical metric units. R is expressed as line-neutral resistance = half of line-line resistance, and Ke is expressed as V/(rad/s) line-neutral zero-peak = Vrms/KRPM (line-line) × 0.007796968)MCHV-2/MCHV-3:The reference motor is the Leadshine 400W motor EL5-M0400-1-24 (MicrochipDirect part number: AC300025). Microchip has validated motorBench® DevelopmentSuite (including motor parameter measurement) with motors with parameters plotted below. Please also read the following section on Supported MotorParameters. If motorBench® Development Suite is unable to spin a motor successfully, please contact Microchip staff for additional assistance.3. Boarda. dsPICDEM™ MCLV-2 development board. This release of motorBench® Development Suite is compatible with modifications to the board to alter its rated current orvoltage. Contact your local Microchip office to obtain the document "Using MCLV-2 with motorBench® Development Suite to support alternative current and/or voltageratings", which provides guidance for such modifications. Other modifications may not be compatible.b. dsPICDEM™ MCHV-2 and MCHV-3 development boards. This release of motorBench® Development Suite is compatible with unmodified MCHV-2 and MCHV-3development boards.4. Motors should be well-matched to the board and operating voltage. The nominal DC link voltage of the MCLV-2 board is 24V. This voltage can be changed by cutting jumperJ6 and using an appropriate power supply connected to the appropriate terminals of J7. Use of a mismatched motor (for example, a 12V motor used with a 24V DC link voltage) may cause a hardware over-current fault; in this case motor parameter measurement may fail with the message "Fault Code #10: Undefined Fault". Retry with an appropriate DC link voltage.5. Two PIMs and Two devices - dsPIC33EP256MC506 External OpAmp PIM with silicon revision A8 or dsPIC33CK256MP508 External OpAmp PIM. (Please see the HardwareSetup section of the motorBench User's Guide for important modifications to dsPIC33EP256MC506 External OpAmp PIM for use in MCHV-2 and MCHV-3.)6. One algorithm - FOC7. Estimators - PLL, QEI, ATPLL8. Motor parameter measurement:a. Performance criteria adjustment is not presently supported. This includes adjustment of phase margin and PI phase lag at crossover in the current loop; Microchip hasnot completed validation and documentation of these adjustments.9. Autotuning:a. Performance criteria adjustment of the current loop is not presently supported. This includes adjustment of phase margin and PI phase lag at crossover; Microchiphas not completed validation and documentation of these adjustments.b. Use of performance criteria adjustment of the velocity loop is not fully documented or tested. We recommend not adjusting phase margin or PI phase lag unlessnecessary; cases where this is likely to occur are large inertias where αJ = JR/LK m2 > 10, for which an increase of phase margin is appropriate. Phase margin valuesbetween 70 and 85 degrees are recommended in this case, with larger values providing additional stability at the cost of lower velocity bandwidth.10. Axis management not currently implemented - supports only one axis.11. Code generation:a. PWM switching frequency is fixed at 20kHz and does not reflect the value entered under Board parametersb. Integration with external user-supplied code may involve substantial changes. Some guidelines for this are given in the documentation for the Motor ControlApplication Framework. While it is possible to integrate the code generated from motorBench® Development Suite with external code, it is the responsibility of the end user to validate this combination.12. Required compiler settings:a. Optimization-O1 or greater; -O0 and -Os will both compile without errors but do not execute fast enough to complete within the 50 microsecond ADC ISR. Note: at higheroptimization levels, in-circuit debugging using MPLAB X will behave unreliably with respect to breakpoints and single-stepping through C code.The "Omit frame pointer" and "Unroll loops" settings must be enabled.b. Memory model:Large data model (handles using pointers, not direct addressing, to allow for more than 8K of program variables)Small scalar modelc. Additional options:-Wno-volatile-register-var -finlined. Test harness: In order for the test harness to be enabled, the symbols MCAF_TEST_PROFILING and MCAF_TEST_HARNESS should be defined.13. Recommended compiler settings:a. Additional options:-WundefSupported Motor ParametersSince version 2.15, motorBench®Development Suite supports a wide range of motors, subject to the following notes:Ranges of motor parameters (including rated values and computed metrics) must be within the limits noted in either range-limits-mclv2.html or range-limits-mchv2.html.These ranges were tested to ensure that code generation produced firmware constants that were within bounds.Motor parameter measurement does not need to complete successfully but valid motor parameters are required. Some motors may have too low of an inductance or resistance, and may fail motor parameter measurement.Other particular issues that may cause incompatibility with motorBench®Development Suite includeLarge inertia values – in this case, increasing voltage loop phase margin may prevent stability problems. (See "Autotuning" in the Limitations section of this document.) Rotor magnetic saliency – if there are significant differences between Ld and Lq (>10% difference) then some of the MCAF algorithms may not work optimally. Highermismatch between Ld and Lq is typically found in interior-permanent magnet (IPM) motors, and is an intentional feature of the design. See the MCAF User's Guide for more information.Large back-EMF harmonics – a quasi-sinusoidal back-emf is assumedIssues involving individual motor control algorithms, such as PLL estimator, motor startup, or stall detectionHigh cogging torqueMismatch between motor and drive (namely using a motor with current and/or voltage requirements significantly different from that of the hardware) Microchip cannot guarantee that motorBench®Development Suite will work correctly with all motors. If a particular motor does not work properly, please contact the MCU16 Motor Control Team for further guidance.Customer SupportThe Microchip Web SiteMicrochip provides online support via our web site at . This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:Product Support – Data sheets and errata, application notes and sample programs, design resources, user’s guides and hardware support documents, latest software releases and archived softwareGeneral Technical Support – Frequently Asked Questions (FAQs), technical support requests, online discussion groups/forums (), Microchip consultant program member listingBusiness of Microchip – Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representativesAdditional SupportUsers of Microchip products can receive assistance through several channels:Distributor or RepresentativeLocal Sales OfficeField Application Engineering (FAE)Technical SupportCustomers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is available on our web site.Technical support is available through the web site at: 。

华为OSN3500设备CES业务高级属性相关参数

本文档介绍华为OSN3500可以配置以及查询CES业务高级属性的相关参数。

表1 配置PW 高级属性的参数说明域值域说明RTP头禁止、使能缺省值:禁止表示配CES业务时,RTP头封装功能是否使能。

RTP头用来装载时钟信号。

对华为OSN3500系统的影响:RTP头使能,系统才支持自适应时钟恢复ACR的功能。

与其它参数的关联关系:修改PW相关参数之前,需要确认PW没有和业务进行绑定;完成修改后,需要将PW和业务进行绑定,然后才能查询该参数是否修改成功。

抖动缓冲时间(us)125~64000缺省值:8000 表示配置业务的抖动缓冲区大小。

配置抖动缓冲时间的主要目的是为了吸收网络侧的抖动。

对华为OSN3500系统的影响:抖动缓冲时间影响业务的时延。

配置抖动缓冲时间之后,需要等待接收了二分之一抖动缓冲时间的数据时,系统才启动下面的操作。

取值建议:设置抖动缓冲时间的步长为125,即取值只能是:125、250、375、500……64000。

与其它参数的关联关系:域值域说明与报文装载时间关系紧密,要求抖动缓冲时间必须大于两倍报文装载时间。

修改PW相关参数之前,需要确认PW没有和业务进行绑定;完成修改后,需要将PW和业务进行绑定,然后才能查询该参数是否修改成功。

报文装载时间(us) 125~5000缺省值:1000 表示每个报文装载的持续时间。

通过设置报文装载时间可以提高封装效率。

对华为OSN3500系统的影响:影响每个报文中封装的E1信号帧数。

取值建议:设置报文装载时间的步长为125,即取值只能是:125、250、375、500……5000。

承载CES业务的每条PW带宽默认为3M,当“报文装载时间”为“125”或“250”,且“RTP头”设置为“使能华为模式RTP”或“使能标准RTP”时,每条PW的带宽为4M。

与其它参数的关联关系:与抖动缓冲时间关系紧密,要求抖动缓冲时间必须大于两倍报文装载时间。

修改PW相关参数之前,需要确认PW没有和业务进行绑定;完域值域说明成修改后,需要将PW和业务进行绑定,然后才能查询该参数是否修改成功。

DIR-890L R AC3200 Ultra Wi-Fi Router 用户手册说明书

AC3200 Ultra Wi-Fi RouterDIR-890L/ROverviewThe AC3200 Ultra Wi-Fi Router delivers premium performance for today’s most demanding tasks: HD streaming, gaming, and multiple device usage. It comes packed with speeds of up to 3.2Gbps 1, a dual-core processor, three bands (one 2.4GHz and two 5GHz), AC SmartBeam technology, Intelligent Quality of Service (QoS) with traffic prioritization, six high-performance external antennas for maximum range, a new user interface, Smart Connect and with a really easy setup. The perfect combination of performance and ease of use.Smarter Wireless AC FeaturesThe AC3200 Ultra Wi-Fi Router creates an incredibly fast and far-reaching home network for all of your connected devices. The DIR-890L with Smart Connect provides Band Steering Technology to prevent your network from being bottlenecked by devices. In other words, Smart Connect Technology will efficiently select the fastest Wi-Fi for every device. SmartConnect will also simplify your Single Home Network, with one SSID (wireless network identifier) and a security key for all of your devices. All that great technology to let you enjoy more of the stuff you love doing the most.Controlling Your Network Just Got EasierControl your network like never before. Using the new user interface, you can monitor internet activity, block unwanted devices, and prioritize (drag and drop) your devices with our intelligent QoS engine, all from our redesigned UI. It’s really easy to use; you can even check on your connected devices’ statistics. Bottom line, fewer clicks to get where you need to go.FeaturesConnectivity• Advanced Wireless AC beamforming dramatically enhances wireless signal strength and throughput • 802.11 a/g/n/ac wireless LAN for a complete range of wireless compatibility • Gigabit WAN and LAN ports for high-speed wired connections• Two USB ports (one 3.0 and one 2.0) to connect storage drives and printers for sharing mydlink R Cloud• Remotely view and manage your network over the Internet• mydlink Lite mobile app helps you access, manage and view your network remotelySmartConnect• Band steering dynamically balances wireless clients among the three wireless bands QoS• Tracks the type of network traffic (HD media streaming, web surfing, online gaming) and decide which applications deserves higher priority Security• WPA & WPA2 wireless encryption protects the network from intruders• Wi-Fi Protected Setup (WPS) securely addsdevices to your network at the push of a buttonAC SmartBeam Gigabit Smarter BandwidthDual-Core ProcessorSpecifications are subject to change without notice. D-Link is a registered trademark of D-Link Corporation and its overseas subsidiaries. All other trademarks belong to their respective owners. ©2014 D-Link Corporation. All rights reserved.U.S.A. | 17595 Mt. Herrmann Street | Fountain Valley, CA 92708 | 800.326.1688 | For more informationUpdated November 6,, 20144 Gigabit LAN Ports Connects up to 4 wiredInternet Port Plug your Internet cable in here USB 2.0 PortShare aprinterWPSButton One buttonsetupUSB 3.0 Port 5Share media from a USB storageSpecifications are subject to change without notice. D-Link is a registered trademark of D-Link Corporation and its overseas subsidiaries. All other trademarks belong to their respective owners. ©2014 D-Link Corporation. All rights reserved.U.S.A. | 17595 Mt. Herrmann Street | Fountain Valley, CA 92708 | 800.326.1688 | For more informationUpdated November 6,, 20141Maximum wireless signal rate derived from IEEE standard 802.11ac specifications which are subject to change. Actual data throughput will vary. Network conditions and environmental factors, including volume of network traffic, building materials and construction, and network overhead, lower actual data throughput rate. Environmental factors will adversely affect wireless signal range.2Compatibility with more devices will be available in the future.3Latest software and documentation are available at .4Software included is not Mac-compatible.5Maximum transfer rate based on USB 3.0 specifications. Actual data throughput will vary. To meet USB3.0 transfer speeds, USB 3.0 hubs, cables and devices are required.61-Year Limited Warranty available only in the USA.。

用于低功耗、非刚性平面应用的柔性AMOLED器件

ห้องสมุดไป่ตู้

文章编号 :0 6 6 6 (o o 1— 0 0 0 10 — 2 g 2 l )1 0 1 —7

用于低 功耗 刚性平 面应 用 的 非 柔 性 AM 件 OL D器 E

r n e o e o u i n r p o t nt sa e b i g c e t d a g f v lt a y o p ru i e r e n r a e . r o i Ke wo d : y r s AM OL D; O —p w e ; l x be d s ly E lW o r f il ip a e

作 者 针 对 P OL D显 示器 展 望 了一 个 五 阶 段 H E 路 线 图 : 1 低 功耗 —— 显示 器 件 仍然 制 备 在 刚性 的 () 玻璃基板上 , 但具 有低 功耗 和 较 薄 的 外形 ;2) ( 非刚 性— — 去 掉 了玻 璃 基板 , 示器 件 更 薄且 不易 破碎 , 显 具 有 有 限 的柔性 ; 3) 弯 曲—— 显 示器 可 弯 曲且 各 ( 可 层 结 构 之间具 有 一 致性 ;4) 卷 曲— — 这 个 阶段 的 ( 可 显 示器 在 某 个 纬 度 非 常 柔 软 , 因此 可 以卷 成 一 卷 ; ( 任 意 形状— — 这 是 柔性 显 示 的终 极 阶段 , 示器 5) 显

文献 标识码 : B

Fe il lxbe AMOL EDsf rL w-P we ,Ru g d Ap l a in o o o r g e pi t s c o

Ruqn iig Ma, k c , n ui . o Mie Ha k a d J l J Br wn e

LT3960 I2C至CAN物理收发器评估电路EVAL-LT3960-AZ 说明书

1Rev. 0DESCRIPTIONLT3960I 2C to CAN-PhysicalTransceiverEvaluation circuit EVAL-LT3960-AZ features the L T ®3960, an I 2C to CAN-Physical transceiver in a 10-lead plastic MSOP package. EVAL-LT3960-AZ consists of two ICs configured in the master and slave mode using selectable jumpers, JP1 and JP3. The board is designed to be easily snapped apart at the center , separating two circuitries.The LT3960 I 2C to CAN-Physical transceiver is used to send and receive I 2C data through harsh or noisy envi-ronments at up to 400kb/s using the CAN-Physical layer for differential signaling over twisted pair connections. The SDA and SCL data lines are converted to differential signals and are shared between devices connected to the bus. This allows for the physical separation of the I 2C source and I 2C receiver .All registered trademarks and trademarks are the property of their respective owners.PERFORMANCE SUMMARYThe first LT3960 is connected to the I 2C master (I 2C-compatible microcontroller). The second LT3960 should be connected to the first LT3960 by two twisted pairs. It regenerates the I 2C bus locally for one or more I 2C slave devices. The LT3960 devices transmit the clock signal in only one direction, from master to slave. Bidirectional communication of the data signal is always permitted.The LT3960 data sheet gives a complete description of the parts, their operation, and application information. The data sheet must be read in conjunction with this user guide for the evaluation circuit EVAL-LT3960-AZ. The LT3960EMSE is assembled in a 10-lead MSOP package.Design files for this circuit board are available .Specifications are at T A = 25°CSYMBOL PARAMETER CONDITIONMIN TYP MAX UNIT V IN Input VoltageV IN Tied to V CC , 3.3V Range (Jumper JP2, JP4: V IN = V CC ) V IN Tied to V CC , 5V Range (Jumper JP2, JP4: V IN = V CC ) V CC Regulated Internally from V IN (Jumper JP2, JP4: V IN ≠ V CC )3 4.5 4 3.3 53.6 5.5 60V V V V MSTR , V SLV , V SHDN EN/MODE VoltageMaster Mode (Jumper JP1, JP3: MASTER) Slave Mode(Jumper JP1, JP3: SLAVE) Low Power Shutdown Mode(Jumper JP1, JP3: OFF)2 0.7 05 2 0.7V V V f CLK Clock Frequency400kHz V CMBus Common Mode Voltage V CC = 3.3VV CC = 5V±25 ±36V VQUICK START PROCEDUREEVAL-LT3960-AZ can be powered by a voltage source between 4V and 60V due to the integrated LDO in the LT3960. The LDO regulates the input from the V IN pin between 4V and 60V to 3.3V on the V CC pin from which the transceivers and bus lines are powered. Alternatively, the EVAL-LT3960-AZ can be powered from a supply volt-age of 3.3V or 5V on VIN, bypassing the LDO by shorting VCC to VIN using jumpers JP2 and JP4.One procedure for using the EVAL-LT3960-AZ is described as follows:1. Launch Arduino IDE.2. Connect two Linduinos to the computer via USB.3. Download the Linduino code from the EVAL-LT3960-AZ webpage.4. Upload the code to the master and slave Linduinosaccordingly.5. Break the EVAL-LT3960-AZ into two separate boardsby applying force to the horizontal scoring line. 6. Use 2 twisted pairs of small wires to connect CANSCLx1and CANSCLx2; CANSDAx1 and CANS-DAx2.7. Connect GND1 and GND2 pins on two boards using asmall wire (optional).8. Connect SLC, SDA, GND pins from the master (slave)Linduino to SLC1, SDA1, GND1 (SLC2, SDA2, GND2) of the EVAL-LT3960-AZ, respectively.9. With input power off, connect the first (second) inputpower supply to VIN1 and GND1 (VIN2 and GND2) of the EVAL-LT3960-AZ.10. Turn on input power supplies.11. Open the serial monitor associated with the slaveLinduino and check the received message.2Rev. 0QUICK START PROCEDUREFigure 1. Quick Start Procedure Setup Drawing for EVAL-LT3960-AZ3Rev. 04Rev. 0PARTS LISTTEST RESULTSFigure 2. Linduino COM Terminal Window of the Slave DeviceITEM QTY REFERENCE PART DESCRIPTIONMANUFACTURER/PART NUMBER Required Circuit Components12C1, C5CAP ., 1µF, X7R, 50V, 10%, 0603YAGEO, CC0603KRX7R9BB10524C2, C4, C7, C8CAP ., 4700pF, X7R, 50V, 10%, 0402MURATA, GRM155R71H472KA01D 32C3, C6CAP ., 2.2µF, X7S, 10V, 10%, 0603, AEC-Q200TDK, CGA3E3X7S1A225K080AB 42R1, R8RES., 10k, 1%, 1/10W, 0603, AEC-Q200VISHAY, CRCW060310K0FKEA 58R2, R4, R6, R7, R9, R12, R13, R14RES., 60.4Ω, 1%, 1/8W, 0805, AEC-Q200PANASONIC, ERJ6ENF60R4V 64R3, R5, R10, R11RES., 4.99k, 1%, 1/10W, 0603, AEC-Q200PANASONIC, ERJ3EKF4991V 72U1, U2IC, 12C TO DUAL CAN TRANSCEIVER, MSOP-10ANALOG DEVICES, LT3960EMSE#PBF Hardware: For Demo Board Only18E1-E8TEST POINT , TURRET , 0.064" MTG. HOLE, PCB 0.062" THK MILL-MAX, 2308-2-00-80-00-00-07-022J1, J3CONN., TERM BLOCK, 5 POS, 2.54mm, ST , THT , SIDE ENTRY, GREEN ON-SHORE TECHNOLOGY, OSTVN05A15032J2, J4CONN., HDR, MALE, 1x2, 2.54mm, VERT , ST , THT WURTH ELEKTRONIK, 6130021112142JP1, JP3CONN., HDR, MALE, 2x3, 2mm, VERT , ST , THT WURTH ELEKTRONIK, 6200062112152JP2, JP4CONN., HDR, MALE, 1x3, 2mm, VERT , ST , THTWURTH ELEKTRONIK, 62000311121618TP1-TP18TEST POINT , 1POS, 0.040" MTG. HOLE, 2.54mm DIA x 4.57mm L, THT , BLACKKEYSTONE, 500174XJP1, XJP2, XJP3, XJP4CONN., SHUNT , FEMALE, 2 POS, 2mmWURTH ELEKTRONIK, 608002134215Rev. 0Information furnished by Analog Devices is believed to be accurate and reliable. However , no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.SCHEMATIC DIAGRAMc o m6Rev. 0ANALOG DEVICES, INC. 202103/21ESD CautionESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.Legal Terms and ConditionsBy using the evaluation board discussed herein (together with any tools, components documentation or support materials, the “Evaluation Board”), you are agreeing to be bound by the terms and conditions set forth below (“Agreement”) unless you have purchased the Evaluation Board, in which case the Analog Devices Standard Terms and Conditions of Sale shall govern. Do not use the Evaluation Board until you have read and agreed to the Agreement. Your use of the Evaluation Board shall signify your acceptance of the Agreement. This Agreement is made by and between you (“Customer”) and Analog Devices, Inc. (“ADI”), with its principal place of business at One Technology Way, Norwood, MA 02062, USA. Subject to the terms and conditions of the Agreement, ADI hereby grants to Customer a free, limited, personal, temporary, non-exclusive, non-sublicensable, non-transferable license to use the Evaluation Board FOR EVALUATION PURPOSES ONL Y. Customer understands and agrees that the Evaluation Board is provided for the sole and exclusive purpose referenced above, and agrees not to use the Evaluation Board for any other purpose. Furthermore, the license granted is expressly made subject to the following additional limitations: Customer shall not (i) rent, lease, display, sell, transfer , assign, sublicense, or distribute the Evaluation Board; and (ii) permit any Third Party to access the Evaluation Board. As used herein, the term “Third Party” includes any entity other than ADI, Customer , their employees, affiliates and in-house consultants. The Evaluation Board is NOT sold to Customer; all rights not expressly granted herein, including ownership of the Evaluation Board, are reserved by ADI. CONFIDENTIALITY. This Agreement and the Evaluation Board shall all be considered the confidential and proprietary information of ADI. Customer may not disclose or transfer any portion of the Evaluation Board to any other party for any reason. Upon discontinuation of use of the Evaluation Board or termination of this Agreement, Customer agrees to promptly return the Evaluation Board to ADI. ADDITIONAL RESTRICTIONS. Customer may not disassemble, decompile or reverse engineer chips on the Evaluation Board. Customer shall inform ADI of any occurred damages or any modifications or alterations it makes to the Evaluation Board, including but not limited to soldering or any other activity that affects the material content of the Evaluation Board. Modifications to the Evaluation Board must comply with applicable law, including but not limited to the RoHS Directive. TERMINATION. ADI may terminate this Agreement at any time upon giving written notice to Customer . Customer agrees to return to ADI the Evaluation Board at that time. LIMITATION OF LIABILITY. THE EVALUATION BOARD PROVIDED HEREUNDER IS PROVIDED “AS IS” AND ADI MAKES NO WARRANTIES OR REPRESENTATIONS OF ANY KIND WITH RESPECT TO IT . ADI SPECIFICALL Y DISCLAIMS ANY REPRESENTATIONS, ENDORSEMENTS, GUARANTEES, OR WARRANTIES, EXPRESS OR IMPLIED, RELATED TO THE EVALUATION BOARD INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, TITLE, FITNESS FOR A PARTICULAR PURPOSE OR NONINFRINGEMENT OF INTELLECTUAL PROPERTY RIGHTS. IN NO EVENT WILL ADI AND ITS LICENSORS BE LIABLE FOR ANY INCIDENTAL, SPECIAL, INDIRECT , OR CONSEQUENTIAL DAMAGES RESUL TING FROM CUSTOMER’S POSSESSION OR USE OF THE EVALUATION BOARD, INCLUDING BUT NOT LIMITED TO LOST PROFITS, DELAY COSTS, LABOR COSTS OR LOSS OF GOODWILL. ADI’S TOTAL LIABILITY FROM ANY AND ALL CAUSES SHALL BE LIMITED TO THE AMOUNT OF ONE HUNDRED US DOLLARS ($100.00). EXPORT . Customer agrees that it will not directly or indirectly export the Evaluation Board to another country, and that it will comply with all applicable United States federal laws and regulations relating to exports. GOVERNING LAW . This Agreement shall be governed by and construed in accordance with the substantive laws of the Commonwealth of Massachusetts (excluding conflict of law rules). Any legal action regarding this Agreement will be heard in the state or federal courts having jurisdiction in Suffolk County, Massachusetts, and Customer hereby submits to the personal jurisdiction and venue of such courts. The United Nations Convention on Contracts for the International Sale of Goods shall not apply to this Agreement and is expressly disclaimed.。

NVIDIA BOOTH Sl3905 商品展示说明书

AccElERATE YOuR cREATiviTYWiTH NviDiA.BOOTH Sl3905nVidiA At nAb 2013get faster Animation, simulation, and Rendering.featuring: NVIDIA® Maximus™ technology, including the latest generation of NVIDIA Quadro® GPUs with the powerful newNVIDIA Kepler™ architecture, running:> MAXON CINEMA 4D, Jawset TurbulenceFD, and Dell T7600showcasing particle simulation for 3D animation> OTOY Octane Render and HP Z820 showcasing interactive,globally illuminated renderingfor: Animators and 3D and visual-effect artists to create,simulate, and render simultaneously without interrupting their creative workflowAccelerate Color grading.featuring: DaVinci Resolve running on Mac Pro, powered byNVIDIA Quadro K5000 for Macfor: Colorists, video producers, and digital filmmakers whowant to do state-of-the-art color grading on a MacCreate Video productions with Even greater speed.featuring: Adobe® Premiere® Pro Next with an improved GPU-accelerated Mercury Playback Engine, powered by an NVIDIA Kepler-class of Quadro for mobile workstations.for: Video editors, digital filmmakers and broadcasters whoneed real-time performance to enable creative workflows and fast production turnaroundget Quadro performance on windows, mac, orlinux desktops.featuring: the NVIDIA GRID™ Visual Computing Appliance(VCA). Brand new for NAB 2013, the NVIDIA GRID VCA enablesworkgroups to get the full benefits of top-of-the-line NVIDIAGPU acceleration on their Windows, Mac, or Linux systems. The GRID VCA combines the benefits of remoting, virtualization, and Quadro reliability and performance in a turnkey package. At the booth, NVIDIA will feature a technology demonstration of theGRID VCA running:> Adobe® After Effects®Next and Adobe® Photoshop® CS6 on aLinux system, enabling unprecedented creative power andinteractivity when combined with the power of NVIDIA GPUs.> Autodesk 3ds Max 2014 with full GPU acceleration on aMacBook Pro for 3D modeling, animation, visual effects, andrendering to meet the technology demands of today’smodern pipelines> Autodesk Maya 2014, 3D animation software that offers next-generation display technology, accelerated modelingworkflows, robust systems for handling complex data, andinspiring creative toolsetsfor: Broadcasters, post houses, ad agencies, filmmakers,visual-effects artists, motion-graphic artists, and any media-content creator who wants to deliver GPU-accelerated creative and design applications on demandprovide next-generation Content Experiences.featuring: NVIDIA SHIELD,™ a gaming portable designed forgamers who yearn to play when, where, and how they want. With the advanced processing power of NVIDIA Tegra® 4, a full-sizegame controller, breakthrough Wi-Fi technology, and stunning HD video and audio, SHIELD redefines what gaming can be.for: Content creators and content distributors who areinterested in next-generation platforms for gaming and movieson-AiR gRApHiCsPARTNER BOOTH # AccuWeather SL6816 Broadcast Pix SL6324 ChyronHego SL1010 Compix Media SL5705 Harris Broadcast N2503 Miranda Technologies N2531 NewTek SL4610 Orad Hi-Tec Systems SL5709 Pixel Power N2034 Ross Video N3808 Vizrt SL3305 WASP3D SL6328 WSI/Weather Central SL1710 Editing, Compositing, AnimAtion, REndERing, EffECts, And ColoR mAnAgEmEntPARTNER BOOTH # Adobe Systems SL3910 ASSIMILATE SL12705 Autodesk SL3316 Avid SU902 Binocle C12049 Blackmagic Design SL218 Boris FX SL4327 Brainstorm Multimedia SL10621 Cinnafilm SL9605 (HP) Digital Vision SL14518 EditShare SL9010Editing, Compositing, AnimAtion, REndERing,EffECts, And ColoR mAnAgEmEnt (ContinuEd)PARTNER BOOTH #FilmLight SL3928 GenArts SL4224Grass Valley SL206Lightcraft Technology SL12516Marquise Technologies SL12508Maxon Computer Inc. SL5316MTI Film SL15510NewTek SL4610Quantel SL2109Red Giant SL3728SGO SL10321Sony (Vegas™ Pro) C11001The Foundry SL3324EnCoding, tRAnsCoding, And VidEopRoCEssingPARTNER BOOTH #AmberFin SU8505 Cinegy SL11112Digimetrics N3833Elemental Technologies SU2724Interra Systems SL8006Root6 Technology SL7428Sorenson Media SU6806Telestream SL2605For more information on NVIDIA and its partners, visit /quadro.© 2013 NVIDIA Corporation. All rights reserved. All company and product names are trademarks or registered trademarks of the respective owners with which theyare associated. VidEo i/oPARTNER BOOTH #AJA Video SL3816BlackMagic Design SL218Bluefish444 SL9721Deltacast SL11516DVS, a Rohde & Schwarz company SL6316Matrox Electronic Systems SL4616systEm pRoVidER And HARdwARE pARtnERs PARTNERBOOTH #ARRIC4337Canon USAC4325Hewlett-PackardSL9605RED Digital CinemaSL1516Sony ElectronicsC11001Supermicro SL14510。

Microchip电子产品说明书

TREE 3: POWER MANAGEMENT 2Supervisors & Voltage Detectors Unique Strengths (So What)Broad Portfolio(It's likely we have your part)Small Packages: SOT-23 and SC-70 (Saves space)Industrial Standard Crosses (Replace high priced and poor delivery suppliers)Battery Management Unique Strengths (So What)Wide variety of charging solutions for Li-Ion batteries(We have the solution for you)Small SOT-23, MSOP, DFN and QFN packages (Saves space)DC-DC Converter (So What)Low-voltage operation (Saves Power)PFM/PWM Auto switch mode (PFM at low loads reduces current, saves power)Small SOT-23 packaging (Saves space)Step-down, Step-up (Efficiently increase or decrease voltage) Charge Pumps (So What)Low-voltage operation (Battery operation)Small SOT-23 packaging (Saves space)Step-down, Step-up (Efficiently increase or decrease voltage)Doubling & Inverting (Meets V OUT needs) Low-Frequency capable (Reduces EMI)Low-Current Operation (Saves power)LDO Unique Strengths (So What)Hundreds of voltages, currents, packages (We have a match for the need)0.5% V OUT accuracy (Fills precision need)Up to 1.5A output current(Able to power high load applications)Op Amp Unique Strengths (So What)Low current versus GBWP (Saves power)TC and MCP6XXX devices RR-I/O (Expands usable voltage range)MCP604X 1.4V operation(Two alkaline cells 90% used =1.8V)MCP644X, 450 nA operation (Use the batteries even longer)Comparators Unique Strengths (So What)Low current versus propagation delay (Saves power)Integrated Features (Saves space)1.8V and 1.4V operation (That stuff about the batteries)Programmable Gain Amplifier Unique Strengths (So What)MUX inputWide bandwidth (2 to 12 MHz) (Reduces demand on MCU I/O)System control of gain(Changes easier through software configurable hardware)TREE 5: LINEARTemperature Sensor Unique Strengths (So What)Wide variety of solutions: logic, voltage and digital output products(Multiple sensor needs met)Small packages (Saves space)Low operating current(Saves power, smaller supply)Field or factory programmable (Low cost vs. flexibility)Programmable hysteresis (Stop system cycling)Multi-drop capability (Great for large systems)Beta compensation (Compatible with processor substrate diodes)Resistance error correction (Compensates for measurement error from long PCB traces)Fan Controllers Unique Strengths (So What)Closed loop fan control (Adjust to meet target speed even on aging fans)Integrated temperature sensing (Consolidate thermal management)Multiple temperature measurements drive one fan (Consolidate thermal management)Built-in ramp rate control and spin up alogorithm (Quick time to market, lower acoustic noise)Ability to detect/predict failure of less expensive 2-wire fans (Saves system cost)Unique solutions for extending fan life and reducing acoustic noise(Less power, nuisance and long fan life)TREE 6: MIXED-SIGNALADC Unique Strengths (So What)Low current at max sampling rate (Saves power, system cost)Small SOT-23 and MSOP packages (Saves space)Up to 24-bit resolution(Ideal for precision sensitive designs)Differential & single ended inputs (Able to cover various design needs)Up to 6 ADC per device(Save board space, system cost)DAC Unique Strengths (So What)Low Supply Current (Saves power)Low DNL & INL (Better accuracy)Extended Temperature Range(Suitable for wide temperature applications)Digital Potentiometers Unique Strengths (So What)64/256 tap (6-bit to 8-bit resolution)(Sufficient resolution for most applications)Non-volatile Memory(Remembers last wiper setting on power up)WiperLock™ Technology(Locks NV memory setting-better than OTP)Small SOT-23 and 2 × 3 DFN packages (Saves space)Low CostMOSFET Drivers (So What)4.5V up to 30V Supply voltages (Fills many application needs)Up to 12A Peak output current(Able to meet demanding design needs)Outstanding robustness and latch-upi mmunity (Ours work when the others burn up)Low-FOM MOSFETs(Support high-efficency applications)TREE 4: POWER MANAGEMENT 3LIN Unique Strengths(So What)Compliant with LIN Bus Specs 1.3, 2.0, 2.1 andSAE J2602 (Allows for reliable interoperability)High EMI Low EME (Meets OEM requirements)On-board V REG available(Saves space, allows for MCU V CC flexibility)CAN Unique Strengths(So What)Simple SPI CAN controller is an easy way toadd CAN Ports (Short design cycles)High speed transceiver meets ISO-11898 (Drop inreplacement for industry standard transceivers)Low-cost, easy-to-use development tools(Tools easy to buy/use, quick design)I/O Expanders Unique Strengths(So What)Configurable inputs (interrupt configuration flexibility)Interrupt on pin change, or change fromregister default (interrupt source flexibility)Can disable automatic address incrementingwhen accessing the device(allows continual access to the port)The 16-bit devices can operate in 8-bit or 16-bitmode (easy to interface to 8-bit or 16-bit MCUs)IrDA Unique Strengths (So What)IrDA protocol handler embedded on chip(Complex design issue solved)Low cost developer's kit available to assistInfrared design-in (Quick design cycle)Small, cost-effective way of replacing serial links(No more wires)Enables system to wirelessly communicatewith PDA (Wireless connectivity solution) TREE 8: INTERFACEAnalog & InterfaceQuestion TreesAnalog & Interface Development ToolsDemonstration Boards, Evaluation Kits and AccessoriesAnalog & Interface LiteratureADM00313EV: MCP73830L 2 × 2 TDFN Evaluation BoardADM00352: MCP16301 High Voltage Buck Converter 600 mA Demonstration BoardADM00360: MCP16301 High Voltage Buck Coverter 300 mA D2PAK Demonstration BoardADM00427: MCP16323 Evaluation Board (Supports MCP16321 and MCP16322)ARD00386: MCP1640 12V/50 mA Two Cells Input Boost Converter Reference DesignMCP1252DM-BKLT: MCP1252 Charge Pump Backlight Demonstration BoardMCP1256/7/8/9EV: MCP1256/7/8/9 Charge Pump Evaluation BoardMCP1630RD-LIC1: MCP1630 Li-Ion Multi-Bay Battery Charger Reference DesignMCP1630DM-NMC1: MCP1630 NiMH Battery Charger Demonstration BoardMCP1640EV-SBC: MCP1640 Sync Boost Converter Evaluation BoardMCP1640RD-4ABC: MCP1640 Single Quad-A Battery Boost Converter Reference DesignMCP1650DM-LED1: MCP165X 3W White LED Demonstration BoardMCP1726EV: MCP1726 LDO Evaluation BoardMCP73831EV: MCP73831 Evaluation KitMCP7383XEV: MCP73837/8 AC/USB Dual Input Battery Charger Evaluation BoardMCP7383XRD-PPM: MCP7383X Li-Ion System Power Path Management Reference DesignMCP7384XEV: MCP7384X Li-Ion Battery Chager Evaluation BoardMCP73871EV: MCP73871 Load Sharing Li-Ion Battery Charger Evaluation BoardTC1016/17EV: TC1016/17 LDO Evaluation BoardVSUPEV: SOT-23-3 Voltage Supervisor Evaluation BoardPowerManagementThermalManagementMCP9700DM-PCTL: MCP9700 Thermal Sensor PICtail Demonstration BoardMCP9800DM-PCTL: MCP9800 Thermal Sensor PICtail Demonstration BoardTC72DM-PICTL: TC72 Digital Temperature Sensor PICtail Demonstration BoardTC74DEMO: TC74 Serial Daughter Thermal Sensor Demonstration BoardTC1047ADM-PCTL: TC1047A Temperature-to-Voltage Converter PICtail™ Demonstration BoardSerial GPIODM-KPLCD: GPIO Expander Keypad and LCD Demonstration BoardMCP23X17: MCP23X17 16-bit GPIO Expander Evaluation BoardInterface MCP2515DM-BM: MCP2515 CAN Bus Monitor Demonstration BoardMCP2515DM-PTPLS: MCP2515 PICtail™ Plus Daughter BoardMCP2515DM-PCTL: MCP2515 CAN Controller PICtail Demonstration BoardMCP215XDM: MCP215X/40 Data Logger Demonstration BoardMCP2140DM-TMPSNS: MCP2140 IrDA® Wireless Temp Demonstration BoardLinear ADM00375: MCP6H04 Evaluation BoardARD00354: MCP6N11 Wheatstone Bridge Reference DesignMCP651EV-VOS: MCP651 Input Offset Evaluation BoardMCP661DM-LD: MCP661 Line Driver Demo BoardMCP6S22DM-PCTL: MCP6S22 PGA PICtail Demonstration BoardMCP6S2XEV: MCP6S2X PGA Evaluation BoardMCP6SX2DM-PCTLPD: MCP6SX2 PGA Photodiode PICtail Demonstration BoardMCP6SX2DM-PCTLTH: MCP6SX2-PGA Thermistor PICtail Demonstration BoardMCP6V01RD-TCPL: MCP6V01 Thermocouple Auto-Zero Ref DesignMCP6XXXDM-FLTR: Active Filter Demo BoardPIC16F690DM-PCTLHS: Humidity Sensor PICtail Demonstration BoardMixed-Signal MCP3221 DM-PCTL: MCP3221 12-bit A/D PICtail Demonstration BoardMCP3421DM-BFG: MCP3421 Battery Fuel Gauge Demonstration BoardMCP3551DM-PCTL: MCP3551 PICtail Demonstration BoardMCP355XDM-TAS: MCP355X Tiny Application Sensor Demonstration BoardMCP355XDV-MS1: MCP3551 Sensor Demonstration BoardMCP402XEV: MCP402X Digital Potentiometer Evaluation BoardMCP4725EV: MCP4725, 12-bit Non-Volatile DAC Evaluation Board (Preferred One)MCP4725DM-PTPLS: MCP4725, 12-bit Non-Volatile DAC PICtail Demonstration BoardADM00398: MCP3911 ADC Evaluation Board for 16-bit MicrocontrollersCorporate Microchip Product Line Card - DS00890Brochures Analog and Interface Product Selector Guide - DS21060Low Cost Development Tools Solutions Guide - DS51560Analog and Interface Guide (Volume 1) - DS00924Analog and Interface Guide (Volume 2) - DS21975Cards Analog Highlights Card - DS21972Microchip Op Amp Discovery Card - DS21947Analog & Interface Question Trees - DS21728Mirochip SAR and Delta-Sigma ACD Discovery Card - DS22101Software Tools MAPS - Microchip Advanced Product SelectorAnalog & Interface Treelink Products PresentationDesign Guides Analog-to-Digital Converter Design Guide - DS21841Digital Potentiometers Design Guide - DS22017Programmable Gain Amplifiers (PGAs), Operational Amplifiersand Comparators Design Guide - DS21861Interface Products Design Guide - DS21883Signal Chain Design Guide - DS21825Power Solutions Design Guide - DS21913Temperature Sensor Design Guide - DS21895Voltage Supervisors Design Guide - DS51548DS21728JPowerManagementLDO & SwitchingRegulatorsCharge PumpDC/DC ConvertersPower MOSFETDriversPWM ControllersSystem SupervisorsVoltage DetectorsVoltage ReferencesLi-Ion/Li-PolymerBattery ChargersUSB Port PowerControllersMixed-SignalA/D ConverterFamiliesDigitalPotentiometersD/A ConvertersV/F and F/VConvertersEnergyMeasurement ICsCurrent/DC PowerMeasurement ICsInterfaceCAN PeripheralsInfraredPeripheralsLIN TransceiversSerial PeripheralsEthernet ControllersUSB PeripheralLinearOp AmpsInstrumentationAmpsProgrammableGain AmplifiersComparatorsSafety & SecurityPhotoelectricSmoke DetectorsIonization SmokeDetectorsIonization SmokeDetector Front EndsPiezoelectricHorn DriversThermalManagementTemperatureSensorsFan Control& HarwareManagementMotor DriveStepper and DC3Ф BrushlessDC Motor DriverTREE 7: MOTOR DRIVE Stepper Unique Strenghts(So What)Industrial standard footprint(Footprint compatible to industrial leaders)Perfect PIC® MCU companion chip(Solid field support)Micro-stepping ready(Enhanced performance)Integration protections(Simplify software development)3-Phase BLDC Unique Strengths(So What)Full-wave sinusoidal(Quiet operation, low mechanical vibration)Sensorless operation (Minimum externalcomponents, no software required)Thin form factor(Fits space concerned applications)Information subject to change. The Microchip name and logo, the Microchip logo, dsPIC, PIC are registered trademarks and MiWi, PICtail and ZENA are trademarks ofMicrochip Technology Incorporated in the U.S.A. and other countries. All other trademarks mentioned herein are property of their respective companies.© 2012, Microchip Technology Incorporated. All Rights Reserved.。

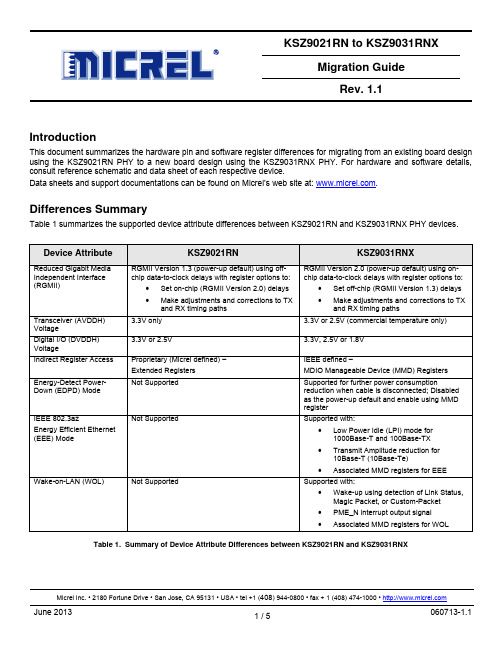

KSZ9021RN to KSZ9031RNX Migration Guide

KSZ9021RN to KSZ9031RNXMigration GuideRev. 1.1IntroductionThis document summarizes the hardware pin and software register differences for migrating from an existing board design using the KSZ9021RN PHY to a new board design using the KSZ9031RNX PHY. For hardware and software details, consult reference schematic and data sheet of each respective device.Data sheets and support documentations can be found on Micrel’s web site at: .Differences SummaryTable 1 summarizes the supported device attribute differences between KSZ9021RN and KSZ9031RNX PHY devices.Device Attribute KSZ9021RN KSZ9031RNXReduced Gigabit Media Independent Interface (RGMII) RGMII Version 1.3 (power-up default) using off-chip data-to-clock delays with register options to:•Set on-chip (RGMII Version 2.0) delays•Make adjustments and corrections to TXand RX timing pathsRGMII Version 2.0 (power-up default) using on-chip data-to-clock delays with register options to:•Set off-chip (RGMII Version 1.3) delays•Make adjustments and corrections to TXand RX timing pathsTransceiver (AVDDH)Voltage3.3V only 3.3V or 2.5V (commercial temperature only)Digital I/O (DVDDH)Voltage3.3V or 2.5V 3.3V, 2.5V or 1.8VIndirect Register Access Proprietary (Micrel defined) –Extended Registers IEEE defined –MDIO Manageable Device (MMD) RegistersEnergy-Detect Power-Down (EDPD) Mode Not Supported Supported for further power consumptionreduction when cable is disconnected; Disabledas the power-up default and enable using MMDregisterIEEE 802.3azEnergy Efficient Ethernet (EEE) Mode Not Supported Supported with:•Low Power Idle (LPI) mode for1000Base-T and 100Base-TX•Transmit Amplitude reduction for10Base-T (10Base-Te)•Associated MMD registers for EEEWake-on-LAN (WOL) Not Supported Supported with:•Wake-up using detection of Link Status,Magic Packet, or Custom-Packet•PME_N interrupt output signal•Associated MMD registers for WOL Table 1. Summary of Device Attribute Differences between KSZ9021RN and KSZ9031RNXPin DifferencesTable 2 summarizes the pin differences between KSZ9021RN and KSZ9031RNX PHY devices. Pin #KSZ9021RNKSZ9031RNXPin NameType Pin FunctionPin NameTypePin Function1 AVDDH P 3.3V analog V DD AVDDH P 3.3V/2.5V (commercial temp only) analog V DD 12 AVDDH P 3.3V analog V DD AVDDH P 3.3V/2.5V (commercial temp only) analog V DD 13VSS_PSGndDigital groundNC–No connectThis pin is not bonded and can be connected to digital ground for footprint compatibility with the Micrel KSZ9021RN Gigabit PHY.16 DVDDH P3.3V / 2.5V digital V DD DVDDH P 3.3V, 2.5V, or 1.8V digital V DD_I/O 17 LED1 /PHYAD0I/OLED Output:Programmable LED1 OutputConfig Mode:The pull-up/pull-down value is latched as PHYAD[0] during power-up / reset.LED1 /PHYAD0 /PME_N1I/O LED1 output:Programmable LED1 outputConfig mode:The voltage on this pin issampled and latched during the power-up/reset process to determine the value of PHYAD[0].PME_N output:Programmable PME_N output (pin option 1). This pin function requires an external pull-up resistor to DVDDH (digital V DD_I/O ) in a range from 1.0k Ω to 4.7k Ω. When asserted low, this pin signals that a WOL event has occurred.When WOL is not enabled, this pin function behaves as per the KSZ9021RN pin definition.This pin is not an open-drain for all operating modes.34 DVDDH P3.3V / 2.5V digital V DD DVDDH P 3.3V, 2.5V, or 1.8V digital V DD_I/O38 INT_N O Interrupt OutputThis pin provides aprogrammable interrupt output and requires an external pull-up resistor to DVDDH in the range of 1K to 4.7K ohms for active low assertion.INT_N/O Interrupt OutputThis pin provides aprogrammable interrupt output and requires an external pull-up resistor to DVDDH in the range of 1K to 4.7K ohms for active low assertion.This pin is an open-drain.PME_N2 PME_N output: Programmable PME_N output (pin option 2). When asserted low, this pin signals that a WOL event has occurred.When WOL is not enabled, this pin function behaves as per the KSZ9021RN pin definition. This pin is not an open-drain for all operating modes.40 DVDDH P 3.3V / 2.5V digital V DD DVDDHP3.3V, 2.5V, or 1.8V digitalV DD_I/O47 AVDDH P 3.3V analog V DD NC–NoconnectThis pin is not bonded and canbe connected to AVDDH powerfor footprint compatibility withthe Micrel KSZ9021RN GigabitPHY.48 ISET I/O Set transmit output levelConnect a 4.99KΩ 1%resistor to ground on thispin. ISET I/O Set the transmit output levelConnect a 12.1kΩ 1% resistorto ground on this pin.Table 2. Pin Differences between KSZ9021RN and KSZ9031RNXStrapping Option DifferencesThere is no strapping pin difference between KSZ9021RN and KSZ9031RNX.Register Map DifferencesThe register space within the KSZ9021RN and KSZ9031RNX consists of direct-access registers and indirect-access registers.Direct-access RegistersThe direct-access registers comprise of IEEE-Defined Registers (0h – Fh) and Vendor-Specific Registers (10h – 1Fh). Between the KSZ9021RN and KSZ9031RNX, the direct-access registers and their bits have the same definitions, except for the following registers in Table 3.Direct-access RegisterKSZ9021RN KSZ9031RNXName Description Name Description3h PHYIdentifier2 Bits [15:10] (part of OUI) – same asKSZ9031RNXBits [9:4] (model number) – unique forKSZ9021RNBits [3:0] (revision number) – uniquedepending on chip revision PHY Identifier 2 Bits [15:10] (part of OUI) – same asKSZ9021RNBits [9:4] (model number) – unique forKSZ9031RNXBits [3:0] (revision number) – uniquedepending on chip revisionBh ExtendedRegister –Control Indirect Register AccessSelect read/write control andpage/address of Extended RegisterReserved ReservedDo not change the default value ofthis registerCh ExtendedRegister –Data Write Indirect Register AccessValue to write to Extended RegisterAddressReserved ReservedDo not change the default value ofthis registerDh ExtendedRegister –Data Read Indirect Register AccessValue read from Extended RegisterAddressMMD Access –ControlIndirect Register AccessSelect read/write control and MMDdevice addressEh Reserved ReservedDo not change the default value ofthis register MMD Access –Register/DataIndirect Register AccessValue of register address/data for theselected MMD device address1Fh, bit [1] Software Reset 1 = Reset chip, except all registers0 = Disable resetReserved ReservedTable 3. Direct-access Register Differences between KSZ9021RN and KSZ9031RNXIndirect-access RegistersThe indirect register mapping and read/write access are completely different for the KSZ9021RN (uses Extended Registers) and KSZ9031RNX (uses MMD Registers). Refer to respective devices’ data sheets for details.Indirect registers provide access to the following commonly used functions:•1000Base-T link-up time control (KSZ9031RNX only)• Pin strapping status• Pin strapping override•Skew adjustments for RGMII clocks, control signals, and datao Resolution of skew steps are different between KSZ9021RN and KSZ9031RNX•Energy-Detect Power-Down Mode enable/disable (KSZ9031RNX only)•Energy Efficient Ethernet function (KSZ9031RNX only)•Wake-on-LAN function (KSZ9031RNX only)Revision HistoryRevision Date Summary of ChangesMigration Guide created1.0 12/7/121.1 6/7/13 Indicate PME_N1 (pin 17) for KSZ9031RNX is not an open-drain.Indicate INT_N (pin 38) is an open-drain for KSZ9021RN, but is not an open-drain for KSZ9031RNX.Indicate direct-access register 1Fh, bit [1] difference.。

XRA1403 1405评估板用户手册说明书