数字电子技术基础第三章逻辑门电路

数字电子技术基础课后答案全解

数字电子技术基础课后答案全解第3章逻辑代数及逻辑门【3-1】填空1、与模拟信号相比,数字信号的特点是它的离散性。

一个数字信号只有两种取值分别表示为0和12、布尔代数中有三种最基本运算:与、或和非,在此基础上又派生出五种基本运算,分别为与非、或非、异或、同或和与或非。

3、与运算的法则可概述为:有“0”出0,全“1”出1;类似地或运算的法则为有”1”出”1”,全”0”出”0”4、摩根定理表示为:AB=AB;AB=AB。

5、函数表达式Y=ABCD,则其对偶式为Y=(AB)CD。

6、根据反演规则,若Y=ABCDC,则Y(ABCD)C7、指出下列各式中哪些是四变量ABCD的最小项和最大项。

在最小项后的()里填入mi,在最大项后的()里填入Mi,其它填某(i为最小项或最大项的序号)。

(1)A+B+D(某);(2)ABCD(m7);(3)ABC(某)(4)AB(C+D)(某);(5)ABCD(M9);(6)A+B+CD(某);8、函数式F=AB+BC+CD写成最小项之和的形式结果应为成最大项之积的形式结果应为m(3,6,7,11,12,13,14,15),写M(0,1,2,4,5,8,9,10)9、对逻辑运算判断下述说法是否正确,正确者在其后()内打对号,反之打某。

(1)若某+Y=某+Z,则Y=Z;(某)(2)若某Y=某Z,则Y=Z;(某)(3)若某Y=某Z,则Y=Z;(√)【3-2】用代数法化简下列各式(1)F1=ABCAB1(2)F2=ABCDABDACDAD(3)F3ACABCACDCD(4)F4ABC(ABC)(ABC)ACD【3-3】用卡诺图化简下列各式ABC(1)F1BCABABC(2)F2ABBCBCABCAB(3)F3ACACBCBC(4)F4ABCABDACDCDABCACDABACBCAD第1页/共46页或ABACBC(5)F5ABCACABD(6)F6ABCDABCADABCABACBDABCCD(7)F7ACABBCDBDABDABCD(8)F8ACACBDBDABDBDABCDABCDABCDABCD(9)F9A(CD)BCDACDABCDCDCD(10)F10=F10ACABBCDBECDECABACBDEC【3-4】用卡诺图化简下列各式(1)P1(A,B,C)=m(0,1,2,5,6,7)ABACBCm(0,1,2,3,4,6,7,8,9,10,11,14)ACADBCDABBC ADBD(2)P2(A,B,C,D)=(3)P3(A,B,C,D)=m(0,1,,4,6,8,9,10,12,13,14,15)(4)P4(A,B,C,D)=M1M7ABCBCD【3-5】用卡诺图化简下列带有约束条件的逻辑函数(1)P1A,B,C,Dm(3,6,8,9,11,12)d(0,1,2,13,14,15)ACBDBCD(或ACD)(2)P2(A,B,C,D)=m(0,2,3,4,5,6,11,12)(8,9,10,13,14,15)dBCBCD(3)P3=ACDABCDABCDADACDBCD(或ABD)AB+AC=0(4)P4=ABCDABCDAB(ABCD为互相排斥的一组变量,即在任何情况下它们之中不可能两个同时为1)【3-6】已知:Y1=ABACBDY2=ABCDACDBCDBC用卡诺图分别求出Y1Y2,Y1Y2,Y1Y2。

数字电子技术基础 第三章(1)11-优质课件

图3.1.2 正逻辑与负逻辑

一些概念

1、片上系统(SoC) 2、双极型TTL电路 3、CMOS

1961年美国TI公司,第一片数字集成电路 (Integrated Circuits, IC)。

VLSI(Very Large Scale Integration)

3.2 半导体二极管门电路

3.2.1 半导体二极管 的开关特性

图3.2.1 二极管开关电路

可近似用PN结方程和下图所 示的伏安特性曲线来描述。

i Is ev/VT 1

其中:i为流过二极管的电流。 v为加到二极管两端的电压。

nkT VT q

图3.2.2 二极管的伏安特性

图3.2.3 二极管伏安特性的几种近似方法

三、电源的动态尖峰电流

图3.5.23 TTL反相器电源电流的计算 (a)vO=VOL 的情况 (b) vO=VOH的情况

图3.5.24 TTL反相器的电源动态尖峰电流

图3.5.25 TTL反相器电源尖峰电流的计算

图3.5.26 电源尖峰电流的近似波形

例3.5.4 计算f=5MHz下电源电流的平均值

图3.3.xx CMOS三态门电路结构之二 (a)用或非门控制 (b)用与非门控制

图3.3.xx CMOS三态门电路结构之三 可连接成总线结构。还能实现数据的双向传输。

3.3.6 CMOS电路的正确使用

一、输入电路的静电防护

1、在存储和运输CMOS器件时最好采用金属屏蔽层 作包装材料,避免产生静电。

tPHL:输出由高电平跳变为低电 平的传输延迟时间。

tPLH:输出由低电平跳变为高电 平的传输延迟时间。

tPD: 经常用平均传输延迟时间tPD

来表示tPHL和tPLH(通常相等)

数字电子技术 第三章 组合逻辑电路

2021/6/10

23

3.2.2 二进制编码器

由于每次操作只有一个输入信号,即输入IR、IY、IG 具有互斥性,根据表3.5,将输出变量取值为1对应的输入 变量相加,可得输出Y1、Y0与输入IR、IY、IG之间的逻辑 关系表达式如下。

Y0 = IR + IG Y1 = IY + IG

对Y1、Y0两次取非,得

5. 断开开关S1、S2,观察发光二极管的发光情况,记 录观察到的结果。

2021/6/10

39

3.3.1 任务描述

图3.18所示是开关S1闭合、S2断开时,观察到的现象。

2021/6/10

图3.18 闭合S1、断开S2时观察到的现象

40

3.3.2 二进制译码器

1. 译码器的基本功能 二进制译码真值表如表3.11所示。

2021/6/10

27

3.2.2 二进制编码器

表中的“×”号表示:有优先级高的输入信号输入时, 优先级低的输入信号有输入还是无输入,不影响编码器的 输出。

2021/6/10

28

3.2.2 二进制编码器

3. 集成8线-3线优先编码器 集成8线-3线优先编码器74LS148、74LS348的引脚排 列完全相同,如图3.12(a)所示。

第四步,判断逻辑电路的逻辑功能。其方法是:根据

真值表进行推理判断。在实际应用中,当逻辑电路很复杂

时,一般难以用简明扼要的文字来归纳其逻辑功能,这时

就用真值表来描述其逻辑功能。

2021/6/10

7

3.1.2 组合逻辑电路的分析

2. 分析举例 【例3.1】 试分析图3.1所示电路的逻辑功能。

解:画出图3.1所示电路的逻辑图如图3.4所示。

数字电子技术基础第三章逻辑门电路

数字电子技术基础第三章逻辑门电路

第一节 常见元器件的开关特性

3.MOS管的开关特性

A、MOS管静态开关特性

在数字电路中,MOS管也是作为 开关元件使用,一般采用增强型的 MOS管组成开关电路,并由栅源电压 uGS控制MOS管的导通和截止。

时间。

toff = ts +tf 关断时间toff:从输入信号负跃变的瞬间,到iC 下降到 0.1ICmax所经历的时间。

数字电子技术基础第三章逻辑门电路

第一节 常见元器件的开关特性

2.三极管的开关特性

B、晶体三极管动态开关特性

ton和toff一般约在几十纳秒(ns=10-9 s)范围。通常都

有toff > ton,而且ts > tf 。

0 .3V 3 .6V 3 .6V

1V 5V

3 .6V

数字电子技术基础第三章逻辑门电路

第三节 TTL和CMOS集成逻辑门电路

1.TTL集成逻辑门电路

3 .6V 3 .6V 3 .6V

2.1V

0 .3V

数字电子技术基础第三章逻辑门电路

第三节 TTL和CMOS集成逻辑门电路

1.TTL集成逻辑门电路

数字电子技术基础第三章逻辑门电路

❖ 2.教学重点:不同元器件的静态开关特性,分立元件门电路 和组合门电路,TTL和CMOS集成逻辑门电路基本功能和电气特 性。

❖ 3.教学难点:组合逻辑门电路、TTL和CMOS集成逻辑门4.课时 安排: 第一节 常见元器件的开关特性 第二节 基本逻辑门电路 第三节 TTL和CMOS集成逻辑门电路

数字电子技术基础第三版第三章答案

题3.10数据选择器和数据分配器各具有什么功能?若想将一组并行输入的数据转换成串行输出,应采用哪种电路?

答:数据选择器根据控制信号的不同,在多个输入信号中选择其中一个信号输出。数据分配器则通过控制信号将一个输入信号分配给多个输出信号中的一个。若要将并行信号变成串行信号应采用数据选择器。

试设计符合上述要求的逻辑电路(器件不限)。

解:题目中要求控制信号对不同功能进行选择,故选用数据选择器实现,分析设计要求,得到逻辑表达式:

。

4选1数据选择器的逻辑表达式:

。

对照上述两个表达式,得出数据选择器的连接方式为:

A0=C1,A1=C2, , , , 。

根据数据选择器的连接方程,得到电路如习题3.3图所示。

1

0

0 0

1 0 0 0

1

0

1 0

1 0 0 1

1

1

1 1

1 0 1 0

1

1

0 1

1 0 1 1

1

0

0 0

1 1 0 0

0

0

1 1

1 1 0 1

0

1

1 0

1 1 1 0

0

1

1 0

1 1 1 1

0

0

0 1

(3)由真值表,作函数卡诺图如习题3.1图(b)所示。

卡诺图化简函数,得到最简与或式:

变换F2的表达式

(2)定义逻辑变量0、1信号的含义。无论输入变量、输出变量均有两个状态0、1,这两个状态代表的含义由设计者自己定义。

(3)再根据设计问题的因果关系以及变量定义,列出真值表。

数字电子技术基础-第3章课后习题答案

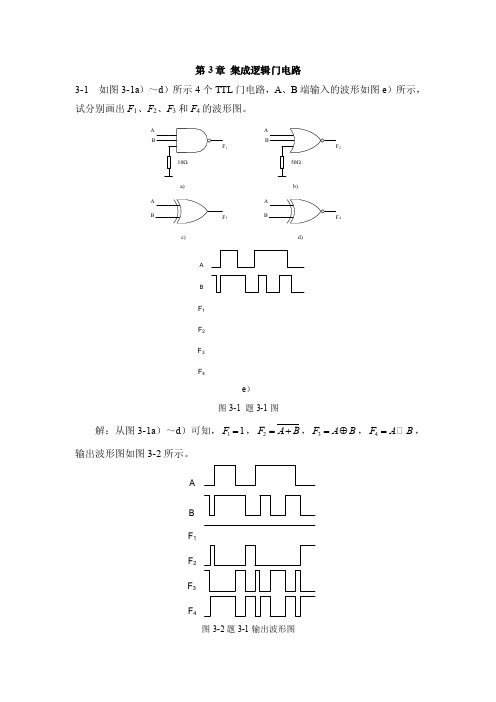

第3章集成逻辑门电路3-1 如图3-1a)~d)所示4个TTL门电路,A、B端输入的波形如图e)所示,试分别画出F1、F2、F3和F4的波形图。

A1A234a)b)c)d)F1F2F3F4BAe)图3-1 题3-1图解:从图3-1a)~d)可知,11F=,2F A B=+,3F A B=⊕,4F A B= ,输出波形图如图3-2所示。

F1F2F3F4AB图3-2题3-1输出波形图3-2 电路如图3-3a )所示,输入A 、B 的电压波形如图3-3b )所示,试画出各个门电路输出端的电压波形。

1A 23b)a)AB图3-3 题3-2图解:从图3-3a )可知,1F AB =,2F A B =+,3F A B =⊕,输出波形如图3-4所示。

F 1F 2F 3AB图3-4 题3-2输出波形3-3在图3-5a )所示的正逻辑与门和图b )所示的正逻辑或门电路中,若改用负逻辑,试列出它们的逻辑真值表,并说明F 和A 、B 之间是什么逻辑关系。

b)a)图3-5 题3-3图解:(1)图3-5a )负逻辑真值表如表3-1所示。

表3-1 与门负逻辑真值表F 与A 、B 之间相当于正逻辑的“或”操作。

(2)图3-5b )负逻辑真值表如表3-2所示。

表3-2 或门负逻辑真值表F 与A 、B 之间相当于正逻辑的“与”操作。

3-4试说明能否将与非门、或非门和异或门当做反相器使用?如果可以,各输入端应如何连接?解:与非门、或非门和异或门经过处理以后均可以实现反相器功能。

1)与非门:将多余输入端接至高电平或与另一端并联; 2)或非门:将多余输入端接至低电平或与另一端并联;3) 异或门:将另一个输入端接高电平。

3-5为了实现图3-6所示的各TTL 门电路输出端所示的逻辑关系,请合理地将多余的输入端进行处理。

b)a)AB=A B=+A BC DABC D图3-6 题3-5图解:a )多余输入端可以悬空,但建议接高电平或与另两个输入端的一端相连;b )多余输入端接低电平或与另两个输入端的一端相连;c) 未用与门的两个输入端至少一端接低电平,另一端可以悬空、接高电平或接低电平;d )未用或门的两个输入端悬空或都接高电平。

数字电子技术第三章习题课

辽宁工业大学

电子与信息工程学院 电子信息工程教研室

第3章、门电路

一、本章内容: 逻辑门电路是各种数字电路及数字系统的基本逻辑单元。本章首先介

绍了半导体二极管和三极管的开关特性,同时介绍了TTL和CMOS两类集成 门电路的特性,即它们的逻辑功能和外部电气特性(包括电压传输特性、 输入特性、输出特性和动态特性等)。为便于合理选择和正确使用数字 集成器件,必须熟悉它们的主要参数,逻辑门使用中的接口问题以及其 他一些实际问题。

写出真值表。

DM

1

表题2.18

△ △ △

S1 S0

≥1

DN

EN 1

EN

输入

输

S1

S0

Y

0

0

0

1

1

DP

1

1

0

EN

&

图3.6

1

1

, 解: 在输入S1、S0各种取值下的输出Y见下表。

输入

S1

S0

输出 Y

0

0

Y DN

0

1

Y DP

信息工程学院 电子教研室

1

9

Y DM

第3章、门电路

解:Y1为低电平;Y2为高电平;Y3为高电平;Y4为低电平;Y5为低电平;Y6 为高阻态;Y7为高电平;Y8为低电平。

电子与信息工程学院

19

电子教研室

第3章、门电路

题3.15 说明图3.15中各门电路的输出时高电平还是低电平。已知他们 都是74HC系列的CMOS电路。

解:Y1为高电平;Y2为高电平;Y3为低电平;Y4为低电平。

解 (a) Y1 ABCDE (c) Y3 ABC DEF

《数字电子技术基础》第六版--门电路-1117省名师优质课赛课获奖课件市赛课一等奖课件

S

D

B

不论D、S间有无电压, 均无法导通,不能导电

第 章 门电路

3.3.1 MOS管旳开关特征 以N沟道增强型为例研究通电情况:

数字电子技术基础 第六版

2、添加垂直电压VGS

形成电场G—B,把衬底中旳电子吸引 到上表面,除复合外,剩余旳电子在 上表面形成了N型层(反型层)为D、 S间旳导通提供了通道。

VGS(th)称为阈值电压(开启电压)

第 章 门电路

数字电子技术基础 第六版

3.3.1 MOS管旳开关特征

MOS管输入特征和输出特征

① 输入特征:直流电流为0,看进去有一种输入电 容CI,对动态有影响。

② 输出特征: iD = f (VDS) 相应不同旳VGS下得一族曲线 。

第 章 门电路

3.3.1 MOS管旳开关特征 输出特征曲线(分三个区域)

第 章 门电路

3.2.2 二极管或门 二极管构成旳门电路旳缺陷

• 电平有偏移 • 带负载能力差

数字电子技术基础 第六版

• 只用于IC内部电路

第 章 门电路

集成门电路

数字电子技术基础 第六版

集成门电路

双极型 TTL (Transistor-Transistor Logic Integrated Circuit)

第 章 门电路

数字电子技术基础 第六版

3.3.2 CMOS反相器旳电路构造和工作原理 三、输入噪声容限

噪声容限--衡量门电路旳抗干扰能力。 噪声容限越大,表白电路抗干扰能力越强。

测试表白:CMOS电路噪声容限VNH=VNL=30%VDD,且 随VDD旳增长而加大。所以能够经过提升VDD来提升噪声容限

第 章 门电路

半导体基础知识(2)

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第一节 常见元器件的开关特性

❖以TTL门电路为例:高电平范围2.4V~3.6V,标准高电平为 3V;低电平范围0V~0.8V,标准低电平为0.3V。

数字电路中,不需要 关注具体电压值,只 需关注电平状态

标准低电平 0.3V

0.8V 0V

0

3.6V

1

2.4V

标准高电 平 3V

TTL门电路中的高、低电 平构成的正逻辑示意图

第一节 常见元器件的开关特性

1.二极管的开关特性

A、晶体二极管静态开关特性

VON :门槛电压或称阈值电压、开启电压 VD :导通电压降

二极管正向导通时 的等效电路

VD =0.7V 视为硅二极管导通的条件(锗二极管0.3V)

第一节 常见元器件的开关特性

1.二极管的开关特性

A、晶体二极管静态开关特性

第一节 常见元器件的开关特性

2.三极管的开关特性

B、晶体三极管动态开关特性

ton和toff一般约在几十纳秒(ns=10-9 s)范围。通常都

有toff > ton,而且ts > tf 。

ts 的大小是影响三极管速度的最主要因素,要提高三极 管的开关速度就要设法缩短ton与toff ,特别是要缩短ts 。

第一节 常见元器件的开关特性

❖数字集成电路绝大多数都是由双极型二极管、三极管或单极 型场效应管组成。这些晶体管大部分工作在导通和截止状态

,相当于开关的“接通”和“断开”,故门电路又称为电子

开关。

静态开关特性 : 什么条件下导通,什么条件下截止

开关特性

动态开关特性 : 导通与截止两种状态之间转换过程的特性

数字电子技术基础第三 章逻辑门电路

2020/8/1

教学参考书

• 《数字电子线路(第2版)》姜有根、郭晋阳 电子工业 出版社 中等职业教育国家规划教材(适用中专、中职)

• 《数字电子技术基础(第2版)》杨志忠、卫桦林等 高等 教育出版社 “十五”国家级规划教材(适用大专)

• 《数字电子技术基础(第5版)》阎石 高等教育出版社 面向21世纪课程教材(适用本科)

第一节 常见元器件的开关特性

2.三极管的开关特性

B、晶体三极管动态开关特性

t下s-降-存到储0.时9I间Cmax(所St需or的a时ge间t。ime):从输入信号的负跃变瞬间到iC tf--下降时间(Fall time):从0.9ICmax下降到0.1ICmax所需的

时间。

toff = ts +tf 关断时间toff:从输入信号负跃变的瞬间,到iC 下降到 0.1ICmax所经历的时间。

第一节 常见元器件的开关特性

3.MOS管的开关特性

B、MOS管动态开关特性

设输入ui的低电平为0V,高电平为VDD ➢当输入ui由低电平0V正跃到高电平 VDD时,NMOS管需经过ton才能由截止 转为导通; ➢当输入ui由高电平VDD负跃到低电平 0V时,NMOS管需经过toff才能由导通 转为截止;

第一节 常见元器件的开关特性

2.三极管的开关特性

A、晶体三极管静态开关特性

三极管具有饱和、放大和 截止三种工作状态,在数 字电路中,主要工作于饱 和和截止状态 。

NPN型硅三极管开 关电路及其特性

第一节 常见元器件的开关特性

2.三极管的开关特性

A、晶体三极管静态开关特性

第一节 常见元器件的开关特性

A. 截止条件:vD <VON B. 实际:vD≤0,保证二极管可靠截止 C. VZ:二极管的反向击穿电压

二极管截止时 的等效电路

第一节 常见元器件的开关特性

1.二极管的开关特性

B、二极管动态开关特性

t re反向恢复时间:二极管从导

通到截止所需时间。 动态过程(过渡过程):二极管导 通和截止之间转换过程。

❖ 3.教学难点:组合逻辑门电路、TTL和CMOS集成逻辑门4.课时 安排:

第一节 常见元器件的开关特性

第二节 基本逻辑门电路

第三节 TTL和CMOS集成逻辑门电路

第一节 常见元器件的开关特性

❖逻辑门电路:用以实现基本逻辑运算和复合逻辑运算的电子 电路。常用的逻辑门电路有:与门、或门、非门、与非门、或 非 门、同或门、异或门等,称为基本逻辑门电路。

2.三极管的开关特性

B、晶体三极管动态开关特性

td----延迟时间(Delay time),为从输入信号正跃变瞬间到iC 上升到0.1ICmax所需的时间。 tr----上升时间(Rise time),是集电极电流iC 从0.1ICmax上 升到0.9ICmax所需的时间。

ton = td +tr 开通时间 ton :为从输入信号正跃变瞬间到iC 上升到最大值 ICmax的90%所经历的时间。

第三章 逻辑门电路

❖ 1.教学目标:掌握二极管、三极管、MOS管静态开关特性,了 解他们的动态开关特性;掌握常见的分立元件门电路和组合 逻辑门电路,掌握TTL逻辑门的逻辑功能,了解其电气特性; 掌握CMOS逻辑门的逻辑功能,了解其电气特性;了解TTL门和 CMOS门使用的注意事项;

❖ 2.教学重点:不同元器件的静态开关特性,分立元件门电路 和组合门电路,TTL和CMOS集成逻辑门电路基本功能和电气特 性。

第一节 常见元器件的开关特性

❖各种门电路的输入和输出只有高电平和低电平两个不同的状 态。高、低电平不是一个固定的数值,而是有一定的变化范围 。 ❖正逻辑:1表示高电平,0表示低电平 ❖负逻辑:0表示高电平,1表示低电平

如右ห้องสมุดไป่ตู้正逻辑表示:

K开---VO输出高电平,对应“1” K合---VO输出低电平,对应“0”

第一节 常见元器件的开关特性

3.MOS管的开关特性

A、MOS管静态开关特性

在数字电路中,MOS管也是作为 开关元件使用,一般采用增强型的 MOS管组成开关电路,并由栅源电压 uGS控制MOS管的导通和截止。

(右图为增强型N沟型MOS管)

➢当UGS<UGS(th)门限电压时,NMOS管截止,漏极电流iD=0,输出 uo=VDD,这时,NMOS相当于开关断开; ➢当UGS>UGS(th)门限电压时,NMOS管导通,其导通电阻为RD, 如果RD>>RON,则uo≈0V,这是NMOS管相当于开关接通。

集成TTL门电路:由双极性晶体管组成,工作速度快,功耗大, 集成度低

集成CMOS门电路:由单极型MOS管组成,功耗低,集成度高,工 作速度较慢

第一节 常见元器件的开关特性

门电路 (电子开关)

开门状态: 满足一定条件时,电路允 许信号通过 开关接通 。

关门状态: 条件不满足时,电路信号 通不过 开关断开 。