06章 S12输入输出口

S12硬件及基本功能

S12硬件配臵原则及功能简介1,基础知识2,S12窄带交换模块3,S12辅助控制单元ACE4,S12窄带交换机机架5,S12远端模块(RTSU,RASM,JRSU,ARCU)6,S12(MCC,AMA,TAX)计费7,S12智能网业务及硬件(SSP)8,S12宽带(P3S)硬件1,基础知识我们把用户在1小时内连续不断的通话话务量定义为1E。

我们把每秒呼叫处理能力称为CAPS(Call Attempt Per Second)我们把每个用户每次通话的占用时长作一个平均数称为平均通话占用时长,市话局的平均通话占用时长一般取60S,长途局的平均通话占用时长一般取90S或70S。

CAPS_OR=用户发话话务量/平均通话占用时长CAPS_TER=用户受话话务量/平均通话占用时长CAPS_OUT=中继出局话务量/平均通话占用时长CAPS_INC=中继入局话务量/平均通话占用时长CAPS_OR_OUT=用户的出局发话话务量/平均通话占用时长CAPS_IN_TER=用户的入局受话话务量/平均通话占用时长CAPS_OR_LOC=用户本局发话话务量/平均通话占用时长CAPS_TRAN=中继转移话务量/平均通话占用时长CAPS_OR CAPS_OR_OUT CAPS_OUT1 2 3CAPS_OR_LOC CAPS_TRAN用户7 8 中继CAPS_TER CAPS_TER_INC CAPS_INC4 5 6呼叫过程:用户打电话时,由1转入(我们称1为用户的发话话务量),判断此次通话是本局呼叫还是出局呼叫:如果是对本局用户的呼叫,转入7(我们称7为用户的本局通话话务量),最终回到4(我们称4为用户的受话话务量),完成一次通话。

如果不是对本局用户的呼叫,而是需要出局的,那么即转入2(我们称2为用户的出局发话话务量),转到3(我们称3为中继出局话务量),最后由中继模块连到其它局寻找呼叫对象。

当出现其它局的呼叫由6(我们称6为中继入局话务量)转入当前交换机时,首先判断此次呼叫的对象是不是本局的:如果呼叫的对象是本局的,那么转入5(我们称5为用户的入局受话话务量),最后转入4完成一次通话。

西门子 S120 开机调试手册

SINAMICS S120崬峾㍴⊵ SINAMICS调试手册_______________________________________________________________________________________________SINAMICSS120 调试手册开机调试手册适用于:固件版本 4.5前言 调试准备 1 调试 2 诊断 3 附录 ASiemens AGIndustry SectorPostfach 48 4890026 NÜRNBERG文件订购号: 6SL3097-4AF00-0RP2 Ⓟ 08/2012 本公司保留技术更改的权利 Copyright © Siemens AG 2012. 保留所有权利法律资讯警告提示系统为了您的人身安全以及避免财产损失,必须注意本手册中的提示。

人身安全的提示用一个警告三角表示,仅与财产损失有关的提示不带警告三角。

警告提示根据危险等级由高到低如下表示。

危险表示如果不采取相应的小心措施,将会导致死亡或者严重的人身伤害。

警告表示如果不采取相应的小心措施,可能导致死亡或者严重的人身伤害。

小心表示如果不采取相应的小心措施,可能导致轻微的人身伤害。

注意表示如果不采取相应的小心措施,可能导致财产损失。

当出现多个危险等级的情况下,每次总是使用最高等级的警告提示。

如果在某个警告提示中带有警告可能导致人身伤害的警告三角,则可能在该警告提示中另外还附带有可能导致财产损失的警告。

合格的专业人员本文件所属的产品/系统只允许由符合各项工作要求的合格人员进行操作。

其操作必须遵照各自附带的文件说明,特别是其中的安全及警告提示。

由于具备相关培训及经验,合格人员可以察觉本产品/系统的风险,并避免可能的危险。

Siemens 产品请注意下列说明: 警告Siemens 产品只允许用于目录和相关技术文件中规定的使用情况。

如果要使用其他公司的产品和组件,必须得到 Siemens 推荐和允许。

飞思卡尔S12系列寄存器和中断讲解

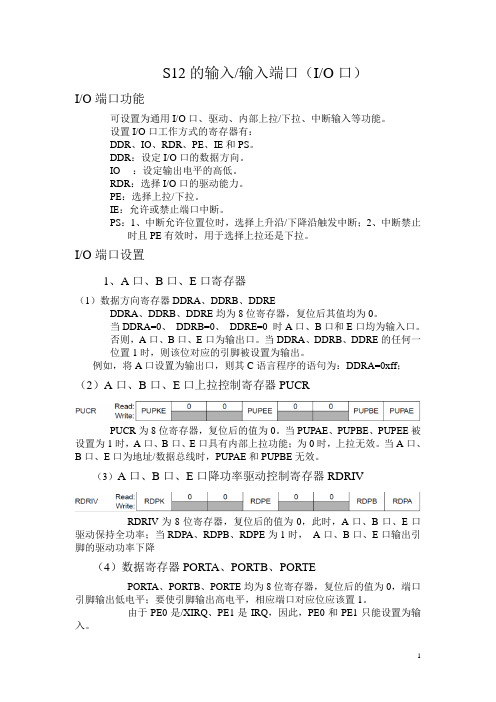

S12的输入/输入端口(I/O口)I/O端口功能可设置为通用I/O口、驱动、内部上拉/下拉、中断输入等功能。

设置I/O口工作方式的寄存器有:DDR、IO、RDR、PE、IE和PS。

DDR:设定I/O口的数据方向。

IO :设定输出电平的高低。

RDR:选择I/O口的驱动能力。

PE:选择上拉/下拉。

IE:允许或禁止端口中断。

PS:1、中断允许位置位时,选择上升沿/下降沿触发中断;2、中断禁止时且PE有效时,用于选择上拉还是下拉。

I/O端口设置1、A口、B口、E口寄存器(1)数据方向寄存器DDRA、DDRB、DDREDDRA、DDRB、DDRE均为8位寄存器,复位后其值均为0。

当DDRA=0、DDRB=0、DDRE=0 时A口、B口和E口均为输入口。

否则,A口、B口、E口为输出口。

当DDRA、DDRB、DDRE的任何一位置1时,则该位对应的引脚被设置为输出。

例如,将A口设置为输出口,则其C语言程序的语句为:DDRA=0xff;(2)A口、B口、E口上拉控制寄存器PUCRPUCR为8位寄存器,复位后的值为0。

当PUPAE、PUPBE、PUPEE被设置为1时,A口、B口、E口具有内部上拉功能;为0时,上拉无效。

当A口、B口、E口为地址/数据总线时,PUPAE和PUPBE无效。

(3)A口、B口、E口降功率驱动控制寄存器RDRIVRDRIV为8位寄存器,复位后的值为0,此时,A口、B口、E口驱动保持全功率;当RDPA、RDPB、RDPE为1时,A口、B口、E口输出引脚的驱动功率下降(4)数据寄存器PORTA、PORTB、PORTEPORTA、PORTB、PORTE均为8位寄存器,复位后的值为0,端口引脚输出低电平;要使引脚输出高电平,相应端口对应位应该置1。

由于PE0是/XIRQ、PE1是IRQ,因此,PE0和PE1只能设置为输入。

2、H口寄存器(1)H口I/O寄存器PTH任意时间读/写。

当某一引脚对就的数据方向位设置为1时,读操作返回的是这个端口寄存器的值;否则,读的是引脚的值。

S12设备介绍

未经本公司书面授权,任何人不得擅自传播、复制、交流与使用本文档的部分或全部内容。

未经本公司书面授权,任何人不得擅自传播、复制、交流与使用本文档的部分或全部内容。

未经本公司书面授权,任何人不得擅自传播、复制、交流与使用本文档的部分或全部内容。

未经本公司书面授权,任何人不得擅自传播、复制、交流与使用本文档的部分或全部内容。

未经本公司书面授权,任何人不得擅自传播、复制、交流与使用本文档的部分或全部内容。

未经本公司书面授权,任何人不得擅自传播、复制、交流与使用本文档的部分或全部内容。

未经本公司书面授权,任何人不得擅自传播、复制、交流与使用本文档的部分或全部内容。

未经本公司书面授权,任何人不得擅自传播、复制、交流与使用本文档的部分或全部内容。

未经本公司书面授权,任何人不得擅自传播、复制、交流与使用本文档的部分或全部内容。

未经本公司书面授权,任何人不得擅自传播、复制、交流与使用本文档的部分或全部内容。

未经本公司书面授权,任何人不得擅自传播、复制、交流与使用本文档的部分或全部内容。

未经本公司书面授权,任何人不得擅自传播、复制、交流与使用本文档的部分或全部内容。

未经本公司书面授权,任何人不得擅自传播、复制、交流与使用本文档的部分或全部内容。

未经本公司书面授权,任何人不得擅自传播、复制、交流与使用本文档的部分或全部内容。

未经本公司书面授权,任何人不得擅自传播、复制、交流与使用本文档的部分或全部内容。

未经本公司书面授权,任何人不得擅自传播、复制、交流与使用本文档的部分或全部内容。

未经本公司书面授权,任何人不得擅自传播、复制、交流与使用本文档的部分或全部内容。

图7-1. 数字交换机的接口、测试点、传输电平6.1.1. 用户侧接口未经本公司书面授权,任何人不得擅自传播、复制、交流与使用本文档的部分或全部内容。

未经本公司书面授权,任何人不得擅自传播、复制、交流与使用本文档的部分或全部内容。

未经本公司书面授权,任何人不得擅自传播、复制、交流与使用本文档的部分或全部内容。

S12的输入输出端口

(7)J口中断使能寄存器PIEJ

任意时间读/写。 PIEJ寄存器可设置端口J相应引脚的外部中断 边沿使能或禁止。 PIEJ某一位置1时,对应引脚的中断使能。 PIEJ某一位置0时,对应引脚的中断禁止。

(8)J口中断标志寄存器PIFJ

任意时间读/写。 当对应引脚出现活动的边沿时,PIFJ相应位 被置1。是上升沿或下降沿,由PPSJ寄存器相应 位的状态决定。 为了清除标志位,向PIFJ对应位写“1”。写 “0”无效。

Byteflight/CAN/BDLC强制将与其输出对应的 引脚置为输出状态;同时,将与其输入对应的引 脚置为输入状态。

(4)M口降功率驱动寄存器RDRM

(5)M口拉动装备使能寄存器PERM

任意时间读/写。 如果端口用于输入或“线或”输出,该寄存器 配置被激活的上拉或下拉装置。当端口用于推挽输 出时,相应位无效。

例如,将A口设置为输出口,则其C语言程序 的语句为:DDRA=0xff;

(2)A口、B口、E口上拉控制寄存器PUCR

PUCR为8位寄存器,复位后的值为0。当 PUPAE、PUPBE、PUPEE被设置为1时,A口、B 口、E口具有内部上拉功能;为0时,上拉无效。当 A口、B口、E口为地址/数据总线时,PUPAE和 PUPBE无效。

3、J口寄存器 (1)J口I/O寄存器PTJ

任意时间读/写。 当数据方向寄存器对应位置1时,读PTJ将返回 PTJ中的值;否则读返回对应引脚的值。

(2)J口输入寄存器PTIJ

只读不写。 读该寄存器将返回引脚的值。 该寄存器可检测相应引脚的输出是否过载或短 路。

(3)J口数据方向寄存器DDRJ (4)J口降功率驱动寄存器RDRJ

任意时间读/写。 该寄存器有两个作用:选择激活的中断边沿的极 性;选择上拉或下拉。 当PPSH某一位为1时,H口对应引脚信号上升沿 将使PIFH寄存器中相应位置位;当PERH对应位置1 且端口定义为输入口时,引脚和下拉装置连接。 当PPSH某一位为0时,H口对应引脚信号下降沿 将使PIFH寄存器中相应位置位;当PERH对应位置1 且端口定义为输入口时,引脚和上拉装置连接。

计算机维修工取证辅导06-微机接口、其它外设

北京信息职业技术学院

30

光驱的种类

CD-ROM:CD光驱,能够读取光盘数据 CD-R:可一次性刻录光盘,不能擦除。 CD-RW:可擦写光盘,擦除后重复使用。 DVD-ROM DVD-R DVD-RW Combo(康宝):整和了CD-ROM、CD刻 录机、DVD-ROM三者功能的驱动器。

北京信息职业技术学院

北京信息职业技术学院

18

硬盘跳线

硬盘出厂时默认的设置为主盘,只安装一个硬盘 时不需要改动;当安装多个硬盘时,要把第二个 硬盘设为从盘。 设置方法:改变硬盘跳线。 MA:主盘 SL:从盘

北京信息职业技术学院

19

声卡

声卡的功能

音频信息的采集和播放 电子合成音乐

声卡的种类

集成声卡 独立声卡

声卡的结构:包括声音处理芯片、音频放大 器、输入/输出端口。

北京信息职业技术学院

21

声卡的种类

板卡式:早期的板卡式产品多为ISA接口,目前 已被淘汰;PCI则取代了ISA接口成为目前的主 流。 集成式:集成在主板上,具有不占用PCI接口、 成本更为低廉、兼容性更好等优势,能够满足普 通用户的绝大多数音频需求。 外置式声卡:通过USB接口与PC连接,具有使用 方便、便于移动等优势。但这类产品主要应用于 特殊环境,如连接笔记本实现更好的音质等。

25

光盘驱动器原理

光盘驱动器俗称“光驱”,利用激光读出刻在光 盘上凹坑所表示的数据。 激光光源来自于一个激光二极管,它可以产生激 光束,光束经聚焦后 照射在光盘上,再由 光盘反射回来,经过 光检测器捕获信号。 光盘上凹坑改变了光束 的反射强度,不同的凹 坑表示出0、1数据。

北京信息职业技术学院

26

北京信息职业技术学院有4口(无 电源)和6口(有电源) 之分。 传送电源的两根线 之间的电压一般为8 ~40V, 最大电流 1.5A。

第5章 MC9S12XS输入输出端口模块及其应用实例PPT课件

5.2 输入/输出端口寄存器及设置

通用I/O口通过配置相应寄存器位,可以设置输入/输出端口、驱 动能力、内置上拉/下拉电阻使用、中断输入方式等多种功能。通过 对DDR、I/O、RDR、PE、PS和IE等寄存器的设置,用户可以获得 通用I/O口的不同工作方式。其中,DDR(数据方向寄存器)设定I/O 口为输入/输出端口。数据寄存器(I/O寄存器)用于设定I/O口的高低 电平。RDR(驱动控制寄存器)用于设定I/O口的输出驱动能力。PE (上拉/下拉使能寄存器)用于当I/O口为输入口时使能内置上拉电阻 或下拉电阻的使用。PS(上拉/下拉选择寄存器)当中断允许位置位 时,用于选择上升沿触发或下降沿触发中断;当使能内置上拉/下拉 电阻时,用于选择使用上拉电阻或下拉电阻。IE(中断使能寄存器) 用于使能I/O口的中断功能。

11 《MC9S12XS单片机原理及嵌入式系统开发》 单片机原理及嵌入式系统开发》单片机原理及嵌

5.2 输入/输出端口寄存器及设置

5.2.2 PORTT、PORTS、PORTM、PORTP、PORTH和PORTJ

4.驱动控制寄存器(RDRx)

如果端口为输出口时,RDRx可以设置端口对应引脚的输出驱动能力。如 果RDRx某位为“1”,则对应引脚的输出驱动能力为正常时的1/5;如果某位 为“0”,则对应引脚输出为正常驱动能力。复位后,驱动控制寄存器值为 0x00,即MCU复位后引脚默认为满功率驱动输出。

张 阳,吴 晔,滕 勤 Email:,, TEL:,

1 《MC9S12XS单片机原理及嵌入式系统开发》 单片机原理及嵌入式系统开发》单片机原理及嵌

第5章

MC9S12XS输入/输出端口模块 及其应用实例

S12芯片资料

一、端口主要功能概述:1:端口A、B、K作为通用的输入输出口使用2:端口E整合了1个外部IRQ(可屏蔽的)和XIRQ(不可屏蔽的)中断输入模块3:端口T整合了1个定时器TIM模块4:端口S整合了2个SCI(串行通信)和1个SPI(串行外设)模块5:端口M整合了1个MSCAN(CAN总线)模块6:端口P连接到内部的PWM(脉宽调制)模块,即PWM信号可以通过P口输出,同时P 口的输入也可以作为外部中断信号的输入。

7:端口H和J在作为通用输入输出口使用的同时也可以作为外部中断信号的输入口。

8:端口AD口整合了一个16通道的A TD模块即模拟量转数字量的模块。

二、PORTA(A口数据寄存器)、DDRA(A口数据方向寄存器)、PUCR(引脚上拉控制寄存器)、RDRIV(低功耗驱动寄存器)这些寄存器都是8位的寄存器,其名称可以直接在程序中使用,当然也可以只使用其中的个别数据位。

三、对于数据方向寄存器的使用只要记住:置1——输出置0——输入如果我们想把端口A作为输入口使用,我们只需写DDRA=0x00;即所有位都置0,如果我们想把端口A作为输出口使用,我们只需要写DDRA=0xff;即所有位都置1,而如果我们想要把端口A的高四位做输入口,低4位做输出口时我们就写DDRA=0x0f 对于数据寄存器的使用只要记住:置1——高电平,置0——低电平对于上拉控制寄存器的使用只要记住:置1——设置上拉置0——禁止上拉当我们将A口作输入口使用时需要设置A口内置上拉电阻时首先写PUCR_PUPAE=1 对于低功耗驱动寄存器的使用只要记住:置1——选择低功耗输出置0——正常功耗输出DDRA=0xff;//设置A口方向寄存器为数据输出RDRIV_RDPA=1;//选择A口为低功耗驱动。

I2S接口规范(可编辑修改word版)

I2S 接口规范I2S(Inter-IC Sound Bus)是飞利浦公司为数字音频设备之间的音频数据传输而制定的一种总线标准。

在飞利浦公司的I2S 标准中,既规定了硬件接口规范,也规定了数字音频数据的格式。

I2S 有3 个主要信号:1、串行时钟SCLK,也叫位时钟,即对应数字音频的每一位数据,SCLK 有1 个脉冲。

SCLK 的频率=2×采样频率×采样位数2、帧时钟LRCK,用于切换左右声道的数据。

LRCK 为“1”表示正在传输的是左声道的数据,为“0”则表示正在传输的是右声道的数据。

LRCK 的频率等于采样频率。

3、串行数据SDATA,就是用二进制补码表示的音频数据。

有时为了使系统间能够更好地同步,还需要另外传输一个信号MCLK,称为主时钟,也叫系统时钟(Sys Clock),是采样频率的256 倍或384 倍。

一个典型的I2S 信号见图3。

(图 3 I2S 信号)图 3I2S 格式的信号无论有多少位有效数据,数据的最高位总是出现在LRCK 变化(也就是一帧开始)后的第2 个SCLK 脉冲处。

这就使得接收端与发送端的有效位数可以不同。

如果接收端能处理的有效位数少于发送端,可以放弃数据帧中多余的低位数据;如果接收端能处理的有效位数多于发送端,可以自行补足剩余的位。

这种同步机制使得数字音频设备的互连更加方便,而且不会造成数据错位。

随着技术的发展,在统一的I2S 接口下,出现了多种不同的数据格式。

根据SDATA 数据相对于LRCK 和SCLK 的位置不同,分为左对齐(较少使用)、I2S 格式(即飞利浦规定的格式)和右对齐(也叫日本格式、普通格式)。

这些不同的格式见图4 和图5。

(图4 几种非I2S 格式)图4(图5 几种I2S 格式)图5为了保证数字音频信号的正确传输,发送端和接收端应该采用相同的数据格式和长度。

当然,对I2S 格式来说数据长度可以不同。

有了这些背景知识,让我们用示波器来观察一下CT7160 的输出波形。

飞思卡尔S12系列寄存器和中断讲解

S12的输入/输入端口(I/O 口)I/O端口功能可设置为通用I/O 口、驱动、内部上拉/下拉、中断输入等功能。

设置I/O口工作方式的寄存器有:DDR、10、RDR、PE、IE 和 PS。

DDR :设定I/O 口的数据方向。

IO :设定输出电平的高低。

RDR :选择I/O 口的驱动能力。

PE:选择上拉/下拉。

IE:允许或禁止端口中断。

PS: 1、中断允许位置位时,选择上升沿/下降沿触发中断;2、中断禁止时且PE有效时,用于选择上拉还是下拉。

I/O端口设置1、A 口、B 口、E 口寄存器(1)数据方向寄存器 DDRA、DDRB、DDREDDRA、DDRB、DDRE均为8位寄存器,复位后其值均为 0。

当 DDRA=0、DDRB=0、 DDRE=0 时 A 口、B 口和 E 口均为输入口。

否则,A 口、B口、E 口为输出口。

当 DDRA、DDRB、DDRE的任何一位置1时,则该位对应的引脚被设置为输出。

例如,将A 口设置为输出口,则其 C语言程序的语句为:DDRA=0xff ;(2) A 口、B 口、E 口上拉控制寄存器PUCRPUCR 初:PUPKE —— ----- --------- -——RUPEE ——-————-——PUPBE PUR\EWrite: | | |PUCR为8位寄存器,复位后的值为 0。

当PUPAE、PUPBE、PUPEE被设置为1时,A 口、B 口、E 口具有内部上拉功能;为0时,上拉无效。

当A 口、 B 口、E 口为地址/数据总线时,PUPAE和PUPBE无效。

(3)A 口、B 口、E 口降功率驱动控制寄存器RDRIVRDRIV 篇眾?RDPK 口| | 良DPE 口口| 嵐DPB RDPARDRIV为8位寄存器,复位后的值为 0,此时,A 口、B 口、E 口驱动保持全功率;当 RDPA、RDPB、RDPE为1时,A 口、B 口、E 口输出引脚的驱动功率下降(4)数据寄存器PORTA、PORTB、PORTEPORTA、PORTB、PORTE均为8位寄存器,复位后的值为 0,端口引脚输出低电平;要使引脚输出高电平,相应端口对应位应该置1。

了解电脑输入输出接口的种类和功能

了解电脑输入输出接口的种类和功能文章标题:了解电脑输入输出接口的种类和功能现代电脑作为人们生活和工作中必不可少的工具,其中输入输出接口的种类和功能在电脑运行和连接外部设备方面起到重要的作用。

本文将详细介绍电脑输入输出接口的种类和功能,帮助读者更好地了解和使用电脑。

一、串行接口串行接口是一种逐位传输数据的接口,其主要功能是用于连接外部设备,例如打印机和调制解调器。

串行接口的种类较多,其中较常见的是RS-232接口和USB接口。

1. RS-232接口RS-232接口是一种标准的串行通信接口,用于连接计算机和其他外部设备,常见的连接设备包括打印机、调制解调器和串口鼠标。

RS-232接口广泛应用于早期计算机,虽然速度较慢,但仍被某些特定设备所使用。

2. USB接口USB接口是一种通用串行总线接口,现已取代了RS-232接口成为主流连接电脑和外部设备的接口。

USB接口具有高速传输、热插拔和扩展性强等优点,适用于连接各种外部设备,如打印机、键盘、鼠标、摄像头和移动设备等。

二、并行接口并行接口是一种同时传输多个比特的接口,其主要功能是高速传输数据。

常见的并行接口包括并行打印接口(LPT接口)和SCSI接口。

1. 并行打印接口(LPT接口)LPT接口是一种常见的并行接口,用于连接电脑和打印机。

LPT接口传输速度相对较慢,但适用于连接一些需要大量数据传输的外部设备。

2. SCSI接口SCSI接口是一种高性能并行接口,用于连接计算机和外部设备,例如硬盘、光驱等。

SCSI接口传输速度较快,适用于对数据传输速度要求较高的设备。

三、视频接口视频接口是用于电脑图像和视频信号传输的接口,其主要功能是将电脑图像显示在外部显示器上。

常见的视频接口包括VGA接口、DVI 接口和HDMI接口。

1. VGA接口VGA接口是一种模拟视频接口,广泛用于连接电脑和显示器。

VGA接口能够传输标清图像信号,常用于老旧设备或低分辨率显示需求。

2. DVI接口DVI接口是一种数字视频接口,可传输高清图像信号。

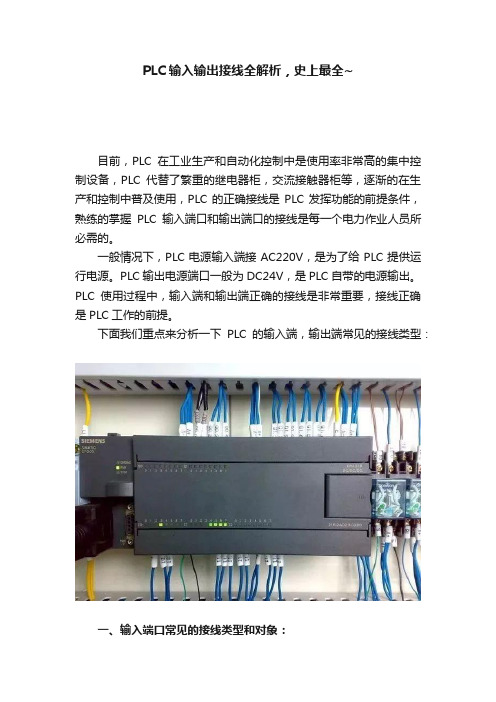

PLC输入输出接线全解析,史上最全~

PLC输入输出接线全解析,史上最全~目前,PLC在工业生产和自动化控制中是使用率非常高的集中控制设备,PLC代替了繁重的继电器柜,交流接触器柜等,逐渐的在生产和控制中普及使用,PLC的正确接线是PLC发挥功能的前提条件,熟练的掌握PLC输入端口和输出端口的接线是每一个电力作业人员所必需的。

一般情况下,PLC电源输入端接AC220V,是为了给PLC提供运行电源。

PLC输出电源端口一般为DC24V,是PLC自带的电源输出。

PLC使用过程中,输入端和输出端正确的接线是非常重要,接线正确是PLC工作的前提。

下面我们重点来分析一下PLC的输入端,输出端常见的接线类型:一、输入端口常见的接线类型和对象:PLC输入端口一般是输入:1,开关量信号:按钮,行程开关,转换开关,接近开关,拨码开关等等。

举个简单的例子更加容易说清楚:PLC与按钮开关接线图按钮或者接近开关的接线所示:PLC开关量接线,一头接入PLC 的输入端(X0,X1,X2等),另一头并在一起接入PLC公共端口(COM端)。

2,模拟量信号:一般为各种类型的传感器,例如:压力变送器,液位变送器,远传压力表,热电偶和热电阻等等信号。

模拟量信号采集设备不同,设备线制(二线制或者三线制)不同,接线方法也会稍有不同。

如图所示:图8-5 PLC与传感器组件的接口电路(a)两线式传感器;(b)三线式传感器二、输出端口接线。

PLC输出端口接线一般可以分为以下三种情况:1,继电器输出。

2,晶体管输出。

3,晶闸管输出。

PLC输出方式不同,输出负载所接的电源类型也不同。

如图所示:这是PLC输入端和输出端的基本接线,属于PLC基本知识。

三、PLC接线过程中的三点常识:1,PLC电源电路。

PLC控制系统的电源除了交流电源外,还包括PLC直流电源,一般而言,PLC交流电源可以由市电直接供应,而输入设备(开关,传感器等)的直流电源和输出设备(继电器)的直流电源等,最好采取独立的直流电源供电。

PC 机外接输入输出接口引脚定义

PC 机外接输入输出接口引脚定义(串口、并口、鼠标、键盘、显示、游戏接口等)RS-232串行接口定义计算机侧为25针公插:设备侧为25针母插:RS-422串行口定义计算机侧RS-422 串行接口的插口是25 针公插:设备侧RS-422 串行接口插头是25 针母插:PC 串行口定义PC/AT 机上的串行口是9 针公插座,引脚定义为:PC/XT 机上的串行口是25 针公插座,引脚定义为:PC 并行接口定义PC 并行接口外观是25 针母插座:ECP 是Extended Capabilities Port 的缩写,外观同并行口,是25 针母插座:PS/2 鼠标接口定义PS/2 鼠标接口为6 针母插,外观为:键盘接口定义键盘接口为 5 针母插座:PC/AT 键盘接口的引脚定义:PC/XT 键盘接口的引脚定义稍有不同:PS/2 键盘接口定义PS/2 键盘接口为6 针母插,外观为:PC 游戏杆接口PC 游戏杆接口为15 针母插座,外观为:PC 游戏杆为15 针公插头,外观为:游戏杆+MIDI 接口定义MIDI 接口和PC 游戏杆接口是共用的,外观为15 针母插座:插头为15 针公插头,外观为:MIDIRXD单色MDA 显示接口MDA 即Hercules(大力神)单色显示卡,显示卡端的接口为9 针母插座:显示器连线端的接口为9 针公插头:CGA 显示接口CGA 是Color Graphics Adapter 的缩写,信号类型为TTL,最多能显示16 色,显示卡端的接口为9 针母插座:显示器连线端的接口为9 针公插头:EGA 显示接口EGA 是Enhanced Graphics Adapter 的缩写,信号类型为TTL,颜色数为16/64 色,显示卡端的接口为9 针母插座:显示器连线端的接口为9 针公插头:9针VGA 显示接口VGA 是Video Graphics Adapter(Array) 的缩写,信号类型为模拟类型,显示卡端的接口为9 针母插座:显示器连线端的接口为9 针公插头:15针VGA 显示接口VGA 是Video Graphics Adapter(Array) 的缩写,信号类型为模拟类型,显示卡端的接口为15 针母插座:显示器连线端的接口为15 针公插头:VGA Vesa DDC显示接口VGA 是Video Graphics Adapter(Array) 的缩写,VESA 是Video Electronics Standards Association 的缩写,DDC 是Display Data Channel 的缩写,信号类型为模拟类型,显示卡端的接口为15 针母插座:显示器连线端的接口为15 针公插头:以太网10/100Base-T 接口网卡上以及Hub 上接口的外观为8 芯母插座(RJ45):网线上插头的外观为8 芯公插头(RJ45):以太网100Base-T4 接口网卡上以及Hub 上接口的外观为8 芯母插座(RJ45):网线上插头的外观为8 芯公插头(RJ45):。

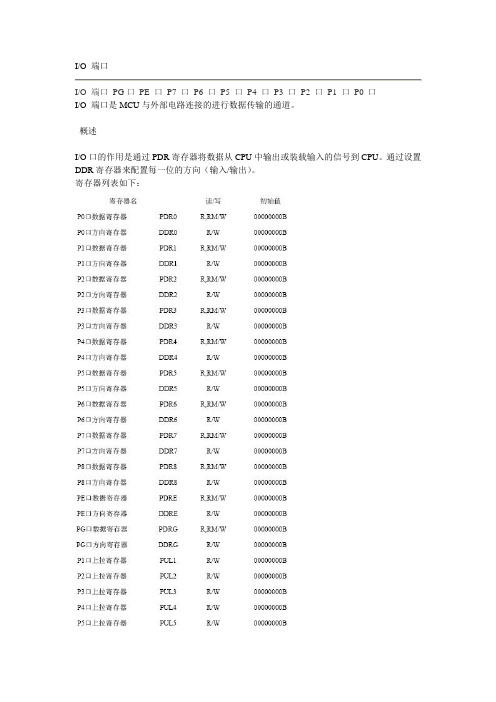

S12的输入输出端口

I/O 端口I/O端口PG口PE口P7口P6口P5口P4口P3口P2口P1口P0口I/O 端口是MCU与外部电路连接的进行数据传输的通道。

概述I/O口的作用是通过PDR寄存器将数据从CPU中输出或装载输入的信号到CPU。

通过设置DDR寄存器来配置每一位的方向(输入/输出)。

寄存器列表如下:R/W:可读/可写(读写的值相同)R,RM/W: 可读/可写(作为标志位被状态改变) 4.6.2 P0 口P0口是一个通用I/O口P0口配置:P0口由下面几个部分组成:通用I/O引脚/外围功能引脚P0口数据寄存器(PDR0)P0口方向寄存器(DDR0)该端口有8个引脚P0口的操作:作为输出引脚的操作:1.设置相应的DDRbit 为“1”,该引脚为输出引脚;2.作为外部复用功能,该设置无效;3.作为输出功能引脚,输出的数据是PDR中的数据4.数据写入PDR中,储存在输出锁存器,输出到引脚的值就是输出锁存器中的数据;5.读PDR返回PDR中的值。

作为输入引脚的操作:1.设置相应的DDRbit 为“0”,该引脚为输入引脚;2.作为外部复用功能,该设置无效;3.数据写入PDR中,储存在输出锁存器,不输出到引脚;4.读PDR返回外部引脚的值,读刷新写命令返回PDR的值。

作为外部功能输出引脚的操作:1.设置相应的使能位,引脚工作在外部功能输出模式;2.引脚的状态从PDR0读出作为外部功能输入引脚的操作:1.设置相应的DDRbit 为“0”,该引脚为外部功能输入引脚;2.读PDR0寄存器的时候返回引脚的状态,与外部功能设置无关。

复位时的操作:回到初始的状态,DDR0全部为”0”。

4.6.3 P1 口P1口是一个通用I/O口P1口配置:P1口由下面几个部分组成:通用I/O引脚/外围功能引脚P1口数据寄存器(PDR1)P1口方向寄存器(DDR1)P1口上拉寄存器(PUL1)输入级别选择寄存器(ILSR)该端口有5个引脚:P1口引脚点击查看图片P1口的操作:作为输出引脚的操作:1.设置相应的DDRbit为“1”,该引脚为输出引脚;2.作为外部复用功能,该设置无效;3.作为输出功能引脚,输出的数据是PDR中的数据;4.数据写入PDR中,储存在输出锁存器,输出到引脚的值就是输出锁存器中的数据;5.读PDR返回PDR中的值。

飞思卡尔S12系列寄存器和中断讲解

S12的输入/输入端口(I/O 口)I/O端口功能可设置为通用I/O 口、驱动、内部上拉/下拉、中断输入等功能。

设置I/O口工作方式的寄存器有:DDR、10、RDR、PE、IE 和 PS。

DDR :设定I/O 口的数据方向。

IO :设定输出电平的高低。

RDR :选择I/O 口的驱动能力。

PE:选择上拉/下拉。

IE:允许或禁止端口中断。

PS: 1、中断允许位置位时,选择上升沿/下降沿触发中断;2、中断禁止时且PE有效时,用于选择上拉还是下拉。

I/O端口设置1、A 口、B 口、E 口寄存器(1)数据方向寄存器 DDRA、DDRB、DDREDDRA、DDRB、DDRE均为8位寄存器,复位后其值均为 0。

当 DDRA=0、DDRB=0、 DDRE=0 时 A 口、B 口和 E 口均为输入口。

否则,A 口、B口、E 口为输出口。

当 DDRA、DDRB、DDRE的任何一位置1时,则该位对应的引脚被设置为输出。

例如,将A 口设置为输出口,则其 C语言程序的语句为:DDRA=0xff ;(2) A 口、B 口、E 口上拉控制寄存器PUCRPUCR 初:PUPKE —— ----- --------- -——RUPEE ——-————-——PUPBE PUR\EWrite: | | |PUCR为8位寄存器,复位后的值为 0。

当PUPAE、PUPBE、PUPEE被设置为1时,A 口、B 口、E 口具有内部上拉功能;为0时,上拉无效。

当A 口、 B 口、E 口为地址/数据总线时,PUPAE和PUPBE无效。

(3)A 口、B 口、E 口降功率驱动控制寄存器RDRIVRDRIV 篇眾?RDPK 口| | 良DPE 口口| 嵐DPB RDPARDRIV为8位寄存器,复位后的值为 0,此时,A 口、B 口、E 口驱动保持全功率;当 RDPA、RDPB、RDPE为1时,A 口、B 口、E 口输出引脚的驱动功率下降(4)数据寄存器PORTA、PORTB、PORTEPORTA、PORTB、PORTE均为8位寄存器,复位后的值为 0,端口引脚输出低电平;要使引脚输出高电平,相应端口对应位应该置1。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

PRO1

PRO2 PRO3

PRO4 LOOP ;循环回去

PRO1: PRO2: PRO3: PRO4:

重庆大学通信工程学院

任勇

6.3.1 独立式按键接口 ;***************************************************************************** 前图中拨位开关换为按键即可;程序也同前。 ;* 按键检查子程序:无键输入直接退出,有键输入时等松手后退出 * ;* 出口参数: Key_numb = 按键号, 0 无键, 1-4 键号 * 硬件---开关输入低有效,上拉, S12可直接用内部上拉 ;***************************************************************************** 软件---查询式,逐位检测每个I/O引脚状态; Test_key: 独立式按键结构特点: PSHA 检测简单;占用 I/O引脚多。按键数目较少时用 MOVB #0, Key_Numb

共阴、动态显示4位BCD码 ($2000开始存放)的程序示例: DISP: LDX #$2000 LDY #TABLE LDAB #$FE LP: LDAA #$FF STAA PTT ; 关LED LDAA X ;取数 LDAA A,Y ;查段码 STAA PTP ;P口输出 STAB PTT ;T口输出 SEC ROLB ;左移位选 BSR DELAY10ms INX ;指针加1 CPX #2004 ;比较 BNE LP ;4次循环 RTS ;返回

Key16Sub: ………… RTS

重庆大学通信工程学院 任勇

6.4 人机交互接口设计

6.4.1 LED数码管的工作原理 结构 7段(8段),8个发光二极管(字段),组合显示出数字、字符 分:共阴极(给1,段亮);共阳极(给0,段亮) 亮:提供段驱动电流,并加适当限流电阻 字形编码 段码,见表6-1 译码分类

上拉控制寄存器PUCR

4口共用,PUPAE、PUPBE、PUPEE、PUPKE位为1使上拉;0无

Bit7 PUPKE Bit6 \ Bit5 \ Bit4 PUPEE Bit3 \ Bit2 \ Bit1 Bit0 PUPBE PUPAE

降功率驱动控制寄存器RDRIV

4口共用,RDPA、RDPB、RDPE、RDPK位为使输出降功率;0不降

重庆大学通信工程学院 任勇

6.3.2 矩阵式键盘接口 也叫行列式键盘,行、列交叉处跨接按键;2x8,4x4,4x8,8x8等 按键响应方式:主程序循环查询、中断后检测 按键检测方法:

(1)行扫描法

右图,原理:

1、全扫描 各行送“0”,查 是否有键按下 2、逐行扫描 逐行送“0”,确 定哪行、哪列键按下

(2)行反转法

重庆大学通信工程学院

任勇

键值计算 按前图的接法可以得出键 值表,如右。键值可以通 过扫描法获得,由键值通 过查表法编程得到真正定 义值。 (即书例5-3和例5-10中的 TABLE2)

*

定义值

键值

行扫描法汇编程序 参见书例5-10的DISPLAY 子程序之前部分,读通

重庆大学通信工程学院

重庆大学通信工程学院

任勇

【例】根据拨位开关的状态,点 亮或熄灭对应的LED灯,并 转向不同的处理程序。(假设 同时只有一个开关接通)

(如图,与XDT512实验核心板一致)

START: LDAA #$F0 STAA DDRB ;设置B口 LOOP: LDAA PORTB LDAB PORTB LSLB ;逻辑左移 LSLB ;低位补0 LSLB LSLB STAB PORTB ;亮、灭灯 RORA BCC RORA BCC RORA BCC RORA BCC BRA …… …… …… …… ;循环右移 ;C=0转

Bit7

RDPK

Bit6

\

Bit5

\

Bit4

RDPE

Bit3

\

Bit2

\

Bit1

Bit0

RDPB RDPA

任勇

重庆大学通信工程学院

2. T口 数据方向寄存器DDRT

0---输入,1---输出

Bit7

Bit6

Bit5

Bit4

Bit3

Bit2

Bit1

Bit0

DDRT7 DDRT6DDRT5 DDRT4 DDRT3 DDRT2 DDRT1 DDRT0 Bit7 PTT7 Bit6 Bit5 Bit4 PTT4 Bit3 PTT3 Bit2 PTT2 Bit1 PTT1 Bit0 PTT0 I/OC0

重庆大学通信工程学院

任勇

补充:多分支结构程序设计

; 根据键号执行相应子程序。

KeyMain:

JSR Key16 LDAA Key_Numb LSLA LDX #Jmp_Table LDY A, X JMP Y

; A= A * 2 (分支编号)

Jmp_Table: FDB Key0Sub FDB Key1Sub …………………. FDB Key16Sub Key0Sub: RTS Key1Sub: ………… RTS ; 无键输入

如:BSET DDRP,$01

;设置P口第0位为输出

重庆大学通信工程学院 任勇

6.1.2 I/O端口的异常处理 S12复位时,GPIO默认为输入; 为避免:当输入转输出时,将数据寄存器的可能的激活电平(如1)输 出,引起误动作。先将非激活电平(如0)写如到数据寄存器 应先 BCLR PTP, $01 然后 BSET DDRP,$01 …… 再 BSET PORTP,#01 ; P口数据寄存器第0位置1,输出1

重庆大学通信工程学院 任勇

6.1.1 I/O端口功能 通过设置相应寄存器,实现以下功能:

DDR寄存器---数据方向,定义是输入还是输出 I/O寄存器---数据寄存器,定义电平的高低,如PORTA RDR寄存器---定义驱动能力 PER寄存器---当I/O口作为输入口时,定义是否使用内部上 拉或下拉 IE寄存器---定义有无中断功能 PPS寄存器--1、端口中断允许时:选择上升沿还是下降沿触发 2、PER有效时,选择上拉还是下拉

(复合功能,优先权左右递减 ) PORTH ---SPI/GPIO PORTJ ---CAN/I2C/GPIO PORTM ---CAN/BDLC/GPIO PORTS ---SCI/SPI/GPIO PORTP ---PWM/SPI/GPIO PORTT ---ECT/GPIO

注:GPIO=通用并行输入/输出

数据寄存器PTT (ECT)

I/O数据,复用ECT

PTT6 PTT5

输入寄存器PTIT

一直为读引脚

I/OC7 I/OC6 I/OC5 I/OC4

I/OC3 I/OC2 I/OC1

Bit7

Bit6

Bit5

Bit4

Bit3

Bit2

Bit1

Bit0

降功率驱动控制寄存器 RDRT

1---降功率为1/6,0-不降

PERT7 PERT6 PERT5 PERT4 PERT3 PERT2 PERT1 PERT0

极性选择寄存器PPST

1---下拉,0---上拉

Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 PPST7 PPST6 PPST5 PPST4 PPST3 PPST2 PPST1 PPST0

重庆大学通信工程学院 任勇

3. S口 4. M口 5. P口 6. H口 7. J口

作通用I/O口时与前述类似,作其它功能略过 (补充说明“线或”和“线与”的概念及原理)

8. 其它I/O AD口:作为A/D转换模块的模拟量输入口和外界触发脉冲的输 入口,也可以做为普通输入口

注:各寄存器,复位默认值:0000 0000B; 各口的数据方向为输入时,内部上、下拉才可设置有效; 各口的数据方向为输出时,内部上、下拉被禁止; 各寄存器情况可用时再行查阅,其复用功能放在相关功能模块中; 各寄存器的均有实际存储地址,但编程时使用寄存器名字即可

重庆大学通信工程学院 任勇

6.3 人机交互接口设计

MCU与外设如何连接---接口,解决信息传递、控制交互… 输入设备---如按键、开关,键盘等; 输出设备---如LED灯、蜂鸣器、LED数码管、LCD显示屏等; 基本原则:由外设确定硬件接口+软件配合

【例】点亮LED灯,并使蜂鸣器发声。

;************************** ORG $1000 main: START: LDAA #$FF STAA DDRB ;设置 LDAA #$FE STAA PORTB ;输出 BRA *

PTIT7 PTIT6 PTIT5 PTIT4 PTIT3 PTIT2 PTIT1 PBit5

Bit4

Bit3

Bit2

Bit1

Bit0

上下拉使能控制寄存器 PERT

1---使能,0---禁止

RDRT7 RDRT6RDRT5 RDRT4 RDRT3 RDRT2 RDRT1 RDRT0 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

LDAA PORTA 6.3.3 按键去抖动ORAA #$F0 抖动问题:按键在按下或抬起时,由于机械弹性的影响,通常所按的键在闭 COMA 合位置和断开位置之间抖动几下才稳定下来。抖动持续的时间因操作者和 BEQ Test_key_RTS ; 无键输入,直接退出 按键特性而异,一般为 ~10ms。 JSR 5 DELAY_20MS 去抖动:克服检测误判 Test_key_NEXT: INC Key_Numb 硬件方法---按键后端加双稳态触发器 LSRA ; 查键号,条件控制循环 BNE Test_key_NEXT 软件方法---检测到有键按下时,延时 10~20ms左右再检测,若该键保持在 按下状态,则确定为按键按下;松按检测同理。 Test_key_LP1: LDAA PORTA ; 判松手 ORAA #$F0 注:通常使用软件去抖动 COMA 键盘的其它问题还有:一键多能、多键同按 …… BNE Test_key_LP1 JSR DELAY_20MS Test_key_RTS: PULA RTS