placement的基本步骤和方法(精)

数字IC后端笔试面试题库(附知识星球活动)

1. 简述数字IC设计流程2. 阐述下数字后端如何选择工艺节点(process node),如何选择metal stack(比如是选用1P7M还是1P8M)?3. 如何做好floorplan?大概阐述下做floorplan的步骤?如何qualify floorplan?4. 当design中memory特别多,多到已经无法全部摆放在boundary的周围,请问是否可以把memory摆放在core区域,为什么?这样做的利弊分别是什么?5. 如何规划powerplan?衡量powerplan好坏的指标有哪些?6. 影响标准单元延迟的因素有哪些?net delay是否可以为负值?为什么?如果可以为负值,请解释原因。

7. 请阐述placement这个步骤的作用,干什么的?placement这步包含哪些子步骤?8. 在placement阶段,针对时钟clock和reset等信号,是否需要额外特殊处理?为什么?9. placement后,如果发现timing violation比较大,应该如何debug?应该从哪些方面着手分析?10. placement阶段优化timing的方法,策略有哪些?11. 如何qualify一个placement结果?12. placement阶段是否需要设置clock uncertainty?如果需要,应该设多少值?13. 何为congestion?如果design中有比较严重的congestion,应该如何处理?14. 阐述下时钟树综合(clock tree synthesis)的作用?为何要做时钟树综合?15. 时钟树上clock inverter或者buffer的类型应该如何确定?是否可以用clock buffer来长tree?16. 要想让工具长好某段tree,应该告诉工具哪些要素?如何qualify一段clock tree?17. Clock tree latency 和clock skew哪个更重要?18. Clock tree太长有何坏处?clock skew较大有何利弊?19. cts之后clock skew是有哪些部分组成?cto后的clock skew值和cts 后的clock skew值有何不一样?20. 对于一个时钟结构比较复杂的设计,给你一个placement的constraint,你能否编写出时钟树约束文件(并非是指定clock inverter类型,max transition值等)?详述下你是如何分析设计的时钟结构的?21. cts后如何分析时钟树是否合理?22. 给定一个timing report,要求判断这条path是setup还是hold的timing report? 要求判断当前的report是什么阶段的report?分析该条path 是否有异常(比如某个delay值比较大等等)?23. 阐述下clock inter-balance是干什么用的?分析其存在的合理性。

allegro布局放置模式placement mode

allegro从16.2版本开始支持placement mode,在该模式下,类似的模块可不用重复布局布线,布完第一个后,后面几个只要使用place replace apply就可以直接形成和第一个一样的走线和布局。

以下说明中以

步骤如下:

1.在原理图concepthdl中,作为模板的原理图部分和reuse的原理图部分中所采用的元器件是完全一致的,元器件之间的互联也是一致的,不一致的仅仅元器件的标识和互联net的标识

2.首先在setup-application mode中选中placement mode

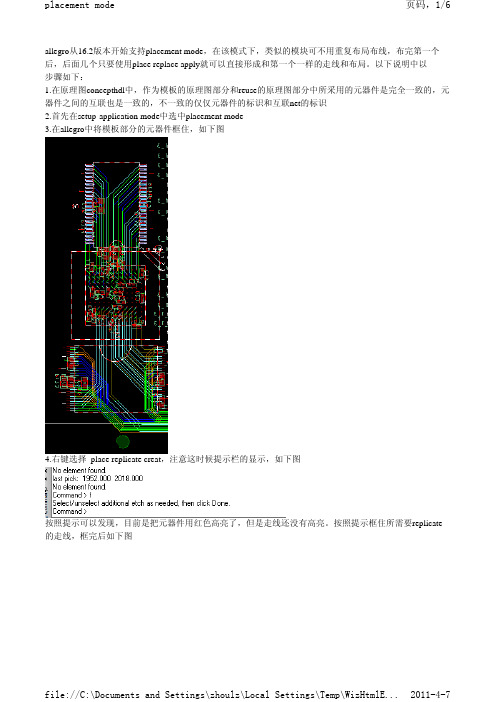

3.在allegro中将模板部分的元器件框住,如下图

4.右键选择 place replicate creat,注意这时候提示栏的显示,如下图

按照提示可以发现,目前是把元器件用红色高亮了,但是走线还没有高亮。

按照提示框住所需要replicate 的走线,框完后如下图

5.按照command栏的提示,右键-》done

6.按照command栏的提示,选择参考原点。

选择后弹出提示框要求保存该reuse模块为mdd文件,将其保存为mvb.mdd

7.将被replicate的器件集中起来,只要放在一起方便等下框住就好,别的没要求。

如下图

8。

左键框住所有待replicate的元器件,右键选择place replicate reuse,选择刚才保存的mvb.

9.放置后如下图,刚才框住的器件,其布局布线都自动完成,如下图。

rosetta stone 英语placement test -回复

rosetta stone 英语placement test -回复"Rosetta Stone 英语Placement Test" 是一个用来评估学生英语水平的测评工具。

本文将详细介绍该测试的步骤和如何回答问题。

第一步:注册和登录首先,需要在Rosetta Stone 的官方网站上注册一个账户,并登录到系统中。

选择英语学习为主题,以便获取与英语相关的测试。

第二步:测试设置一旦登录成功,系统会要求你进行个人设置。

这些设置包括学习目标、学习时间、学习方式等。

请根据个人需求选择适当的选项,并确认设置完成。

第三步:开始测试现在,你将进入到Rosetta Stone 的英语Placement Test。

该测试是根据标准英语水平评估体系(如CEFR)设计的,旨在评估你的读、写、听、说能力和语法知识。

第四步:听力和口语测试测试开始时,你会开始听一些对话和短文,然后需要回答一些与所听内容相关的问题。

这些问题旨在考察你的听力理解能力和口语表达能力。

记住,要仔细倾听并准确回答问题。

第五步:阅读测试接下来,你将阅读一些英文文章,并回答与文章内容相关的问题。

这些问题涉及文章的细节、推理和对文章主旨的理解。

在回答问题之前,确保仔细阅读文章。

第六步:写作测试在写作测试中,你将被要求写一篇短文,描述你们国家、家庭、爱好或其他感兴趣的话题。

试图使用正确的语法、词汇和语言结构来表达你的思想。

第七步:语法和词汇测试为了评估你的语法和词汇水平,系统将向你提供一些填空练习和句子改错练习。

请仔细考虑选项,并选择最合适的答案。

第八步:结果和建议一旦完成所有测试部分,你将收到一份详细的测评结果报告。

根据测试结果,系统将为你推荐一个适合你的学习课程和级别。

这个课程将帮助你进一步提高你的英语水平,并根据你的进展进行相应的调整。

总结:Rosetta Stone 英语Placement Test 是一个全面评估学生英语水平的测试工具。

placement策略

Placement策略1. 什么是Placement策略?Placement策略是指在广告投放过程中,根据广告主的要求和目标受众的特征,选择合适的广告投放位置和方式的一种策略。

通过Placement策略,广告主可以更好地控制广告的曝光范围和受众群体,提高广告的效果和回报。

2. Placement策略的重要性Placement策略在广告投放中起着至关重要的作用。

一个好的Placement策略可以帮助广告主更精准地将广告展示给目标受众,提高广告的曝光率和点击率,从而提升广告的效果和回报。

以下是Placement策略的几个重要方面:2.1 广告位置选择广告位置的选择是Placement策略中的重要环节。

不同的广告位置对广告的曝光和点击率有着直接的影响。

在选择广告位置时,需要考虑受众群体的特征、用户行为和网页布局等因素。

一般来说,广告主希望将广告展示在用户关注度高、曝光率高的位置,例如网页头部、侧边栏或文章中间等。

2.2 广告形式选择广告形式的选择也是Placement策略的一部分。

不同的广告形式适用于不同的场景和受众群体。

常见的广告形式包括横幅广告、原生广告、视频广告等。

在选择广告形式时,需要考虑广告主的宣传内容和目标受众的偏好,以及广告形式对用户体验的影响。

2.3 受众定位受众定位是Placement策略中的核心环节。

通过对目标受众的特征和行为进行分析,可以更好地选择广告投放的位置和方式。

受众定位可以基于用户的地理位置、兴趣爱好、行为习惯等因素进行,从而提高广告的精准度和效果。

3. Placement策略的实施步骤下面是一个基本的Placement策略实施步骤:3.1 确定广告目标在制定Placement策略之前,需要明确广告的目标。

广告目标可以是品牌宣传、产品销售、用户获取等。

不同的目标需要采取不同的Placement策略。

3.2 分析目标受众通过数据分析和市场调研等手段,了解目标受众的特征和行为习惯。

教育评价的概念、分类、步骤和基本模式

教育评价的概念、分类、步骤和基本模式陈福华第一部分教育价值与教育评价▲教育评价学教育评价学是教育科学的一个重要分支学科。

教育评价是从教育测量活动中发展出来的。

始于1934年至19432年美国心理学家泰勒(Tyler, R) 人的"八年研究"。

▲教育评价的四个发展阶段自19世纪中叶起到本世纪30年代的八十多年,为教育评价的第一个时期--"心理测验时期",教育测量的研究取得了一系列的成果,在考试的定量化、客观化与标准化方面,取得了重要的进展。

强调以量化的方法对学生学习状况进行测量。

然而,当时的考试与测验只要求学生记诵教材的知识内容,较为片面。

无法真正反映学生的学习过程。

到本世纪30年代-50年代是教育测量的第二个时期--"目标中心时期",泰勒(Tyler, R) 提出了以教育目标为核心的教育评价原理,即教育评价的泰勒原理,并明确提出了"教育评价"(education evaluation)的概念,从而把教育评价与教育测量区分开来,教育评价学就是在泰勒原理的基础上诞生与发展起来的。

在西方,一般人们都把泰勒称为"教育评价之父"。

60年代是教育测量的第三个时期--"标准研制时期"(20世纪50-70年代),以布卢姆为主的教育家,提出了对教育目标进行评价的问题,由美国教育学家斯克里文(Scriven, M.)、斯塔克(Stake, R. E.)和开洛洛(Kellogg, T. E.) 等人对教育评价理论作出巨大的贡献。

学习们把1967年界定为美国教育评价发展的转折点。

到了20世纪70年代以后,教育评价发展到第四个时期--"结果认同时期"。

这一时期在非常关注评价结果的认同问题。

关注评价过程,强调评价过程中评价给予个体更多被认可的可能。

总之,重视评价对个体发展的建构作用,因此,又称为"个体化评价时期"。

altium designer21的使用查询助手设置规则

在Altium Designer 21中,使用查询助手设置规则主要涉及到Placement(放置规则)和Signal Integrity (信号完整性规则)的设置。

以下是一些基本步骤和考虑因素:Placement(放置规则)设置:•Component Clearance(器件间距):这通常设置为0,意味着器件之间没有间距要求。

然而,根据实际的设计需求和元件的特性,你可能需要调整这个值以确保设计的合理性和可靠性。

Signal Integrity(信号完整性规则)设置:•Signal Integrity分析可以帮助你确保信号在传输过程中保持其原始特性。

这通常涉及到对信号的延迟、噪声、失真等参数的考虑。

Altium Designer提供了默认的Signal Integrity规则,但你也可以根据具体的设计需求进行调整。

区域线宽设置:•在Altium Designer中,你可以为不同的设计区域设置不同的线宽规则。

这有助于优化布线过程,确保布线满足设计要求和性能标准。

•要设置区域线宽,你可以点击“Design”菜单下的“Rooms”选项,选择“Place Rectangular Room”(放置矩形区域)。

然后,打开规则管理器(Rules Manager),在“Design”下的“Rules”中选择“Routing”下的“Width”线宽规则。

•在这里,你可以新建一个规则,将线宽更改为要设置的宽度。

在“Where the Object Matches”下的“All”更改为“Custom Query”(定制查询)。

在右边的对话框里输入“WithinRoom”并会弹出相应的Room名称,选择相应的Room点击应用。

这样,Room里的线宽就会和设置的线宽一致了。

请注意,以上步骤和设置仅供参考,具体的设置方法可能会因你的设计需求、元件类型和布线规则等因素而有所不同。

因此,建议在实际操作过程中参考Altium Designer的官方文档和教程,以获取更详细和准确的信息。

element引用组件input的placement用法

element引用组件input的placement用法1. 什么是element引用组件input?element引用组件input是一种基于Vue.js的前端UI框架,用于快速构建Web界面的开源库。

它提供了丰富的组件和工具,包括表单、按钮、弹窗、导航等,以及一套完整的样式和布局系统。

在element中,input组件是用于接收用户输入的文本框组件。

它支持多种输入类型,如文本、数字、密码等,并提供了丰富的属性和事件,以满足不同的业务需求。

2. input组件的基本使用在使用input组件之前,我们需要先引入element库,并在Vue实例中注册input组件。

以下是一个简单的示例:<template><div><el-input v-model="inputValue"></el-input></div></template><script>export default {data() {return {inputValue: ''}}}</script>在上述示例中,我们使用了el-input标签来创建一个input组件,并通过v-model指令将输入的值绑定到data中的inputValue属性上。

3. placement属性的作用在element的input组件中,有一个placement属性,它用于设置输入框中下拉框的弹出位置。

该属性有以下几种取值:•top:下拉框弹出在输入框上方•top-start:下拉框弹出在输入框左上方•top-end:下拉框弹出在输入框右上方•bottom:下拉框弹出在输入框下方•bottom-start:下拉框弹出在输入框左下方•bottom-end:下拉框弹出在输入框右下方通过设置placement属性,我们可以控制下拉框的弹出位置,以适应不同的布局需求。

手动布局和手动布线PlacementTools(放置工具栏)放置对象

栏)放置对象

10.1 放置对象

本节主要介绍Placement Tools(放置工具栏)各个放置对 象按钮的操作及各对象的属性的编辑。

放置工具栏中大部分按钮的功能,都可以通过执行主菜单 Place中的各命令来实现。

10.1.1 设置原点 绝对原点Absolute Origin :系统定义的坐标原点。

选中Locked项,试图删除元件时,系统弹出要求确认的对话框。

10.1.3 放置焊盘 单击放置工具栏中的

按钮,或执行菜单命令Place|Pan。

Shape:选择焊盘形状。

Round

Rectangle Octagonal

(圆形)

(正方形) (八角形)

Designator:设定焊盘的序号,从0开始。

放置工具条增加功能(Place)

• 1. Interactive Routing

• 的走线。

•

2.Line

•

用于画非电气连接线。例如:在机械层画外形线

。

•

3.Arc

•

新增以边放置任意角度弧和放置整圆弧两项功能

。

•

4.Keep Out

• ,并且可以用线、圆、圆弧、填充来方便的定义。

10.1.6 放置连线

10.1.2 放置元件

1.操作步骤

① 单击放置工具栏的 按钮,或执行菜单命令

Place|Component

② 系统弹出如图所示的Place Component放置元件对话框

封装形式

元件标号

元件标注

③ 设置完毕单击OK按钮,光标变成十字形,并在光标上连接了 所选的元件。此时可移动元件的位置,用空格键旋转元件的方向, 最后单击鼠标左键确定。 ④ 系统再次弹出放置元件的对话框,可继续放置元件。单击 Cancel按钮,结束命令状态。

stp营销过程名词解释

stp营销过程名词解释STP营销过程指的是分析市场的三个步骤:分割(Segmentation)、目标(Targeting)和定位(Placement),也称为“多步营销步骤”,它是市场营销策略的核心构成部分。

其目的是帮助企业通过分割、目标和定位来洞察市场,从而对客户群进行针对性营销。

STP营销过程的第一步是分割,也称作市场分割。

这是一种将一个大市场分割成若干个小市场的市场营销策略。

市场分割可以根据客户的某些特定需求或偏好来划分,以最大限度地满足客户的需求。

例如,如果一家公司生产多种产品,它可以按照客户的价格偏好,将其分割成价格较高的高端市场和价格较低的低端市场。

接下来的步骤是市场目标定位,也就是确定和定位特定的客户群,以最大限度地满足客户的需求。

目标市场可以是潜在客户群,也可以是现有客户群,可以是零售消费者,也可以是企业客户,也可以是专业市场,只要是企业所能处理的客户群,都可以作为目标市场。

例如,如果一家公司想要进行女性用品的营销,它可以把目标定位在女性市场。

STP营销过程的最后一步是定位,也就是确定企业产品或服务在市场中的位置。

它是指确定和描述企业的产品与市场中现有的竞争产品的差异,以及这种差异如何有利于满足客户的需求。

例如,如果一家公司想进行儿童家具的营销,它可以将产品定位在安全、安心、重视儿童健康的角度,以脱颖而出。

STP营销过程是市场营销策略的重要组成部分,它可以帮助企业更好地洞察市场,从而有效地实现“定位到精准,服务到优质”的营销目标。

因此,对于企业来说,要认真对待和深入研究STP营销过程,以最大程度地实现营销目标。

同时,还应加强监测,不断反思和改进营销策略,以确保企业在激烈竞争市场中处于领先行列。

STP营销过程是市场营销策略中重要的一个组成部分,它可以帮助企业洞察市场,更好地满足客户对产品和服务的需求。

STP营销过程的步骤包括市场分割、目标定位和市场定位。

分割是将市场划分为若干更小的分割市场,以满足客户的需求。

innovus reshape placement blockage -回复

innovus reshape placement blockage -回复如何解决Innovus reshape placement blockage【声明】本文所涉及的软件和工具为虚构,仅为演示解决问题的思路和方法。

Innovus Reshape Placement Blockage是在物理设计阶段中常遇到的问题之一,它可能导致整个电路设计的性能下降。

在本文中,我将为您提供一种解决这个问题的步骤。

步骤1:了解问题的背景首先,我们需要了解什么是Innovus Reshape Placement Blockage以及它为何会发生。

Innovus是一种常用的物理设计工具,它在电路设计中被广泛使用。

Reshape Placement Blockage是指在使用Innovus进行布局布线时,由于各种原因导致布局时存在障碍物。

这些障碍可能来自于其他器件的干扰、电路设计的限制或者设计规范的要求。

Reshape Placement Blockage的存在会导致路径的延迟增加、功耗增加或者信号完整性下降等问题。

步骤2:确定问题的具体表现在解决问题之前,我们需要明确Innovus Reshape Placement Blockage的具体表现。

具体来说,我们需要注意以下方面:a) 布局之间存在重叠或者冲突。

b) 路径延迟异常增加。

c) 信号完整性问题,如时钟抖动、信号噪声等。

通过详细观察和分析,我们可以更好地理解问题的性质,从而采取相应的解决方案。

步骤3:分析问题原因要解决Innovus Reshape Placement Blockage问题,我们需要分析问题的根本原因。

通过分析,我们可以确定如果问题是由设计本身造成的,还是由某些限制性要求所导致的。

对于设计本身的问题,我们需要仔细检查电路设计和约束。

检查电路设计是否存在错误或者不合适的器件布局,以及约束是否正确定义。

如果发现问题,我们需要进行调整和优化,以解决Innovus Reshape Placement Blockage。

AP测试的基本方法和内容

AP测试的基本方法和内容AP测试,即Advanced Placement测试,是由美国大学理事会(College Board)组织的一项标准化考试,旨在评估学生在高中阶段所学知识与能力的水平,以便为他们未来的大学学习提供适当的学分和教育进程。

一、基本方法:1.测试形式:AP测试主要采用笔试形式进行,每年5月份举行。

由于疫情原因,2024年的AP考试调整为在线形式。

测试时间是2至3个小时不等,其中包括选择题和开放性问题。

2.考试科目:AP测试一共有38个科目,涵盖了人文、社会科学、自然科学、数学、艺术等各个领域。

如英语文学、美国历史、化学、微积分等。

3.考试内容:AP测试的内容是基于美国高中的教学标准和大学水平的要求,包括课程内容、教学目标、学习方法和技能等。

二、基本内容:1.选择题:AP测试的一大部分是选择题,分为单项选择和多项选择。

这部分主要考察学生对知识点的掌握和理解能力,要求学生对题目进行分析和推理,选出正确的答案。

2.开放性问题:AP测试还包括一些开放性问题,要求学生在规定的时间内作答。

这部分主要考察学生的思维能力和解决问题的能力,要求学生进行综合分析、举例说明或写一篇短文等。

3.实验室报告:一些科目的AP测试还包括实验室报告的评估。

学生需要在实验中进行观察、实验设计、数据分析和实验结论等,然后书面报告给出实验的目的、方法、结果和结论。

三、测试的基本流程:1.报名:学生需要在提前规定的时间内通过学校报名或在线报名的方式报名参加AP测试。

2.考前准备:学生需要参照AP演示课程和课本进行系统学习和复习,掌握每个科目的知识和技能点。

3.考试进行:在测试当天,学生需要按照指定时间和地点参加测试,按照考试要求完成测试内容。

4.成绩公布:AP测试成绩一般在考试结束后的几个月内公布,学生可以通过官方网站或学校查询自己的成绩。

5.大学学分:根据学生在AP测试中的成绩,大学可以酌情给予学分或豁免相应的课程,使学生在大学期间有更多的选修课程或提前修完一些学分。

教育评价的概念

教育评价的概念、分类、步骤和基本模式陈福华第一部分教育价值与教育评价▲ 教育评价学教育评价学是教育科学的一个重要分支学科。

教育评价是从教育测量活动中发展出来的。

始于1934年至19432年美国心理学家泰勒(tyler, r) 人的"八年研究"。

▲ 教育评价的四个发展阶段自19世纪中叶起到本世纪30年代的八十多年,为教育评价的第一个时期--"心理测验时期",教育测量的研究取得了一系列的成果,在考试的定量化、客观化与标准化方面,取得了重要的进展。

强调以量化的方法对学生学习状况进行测量。

然而,当时的考试与测验只要求学生记诵教材的知识内容,较为片面。

无法真正反映学生的学习过程。

到本世纪30年代-50年代是教育测量的第二个时期--"目标中心时期",泰勒(tyler, r) 提出了以教育目标为核心的教育评价原理,即教育评价的泰勒原理,并明确提出了"教育评价"(education evaluation)的概念,从而把教育评价与教育测量区分开来,教育评价学就是在泰勒原理的基础上诞生与发展起来的。

在西方,一般人们都把泰勒称为"教育评价之父"。

60年代是教育测量的第三个时期--"标准研制时期"(20世纪50-70年代),以布卢姆为主的教育家,提出了对教育目标进行评价的问题,由美国教育学家斯克里文(scriven, m.)、斯塔克(stake, r. e.)和开洛洛(kellogg, t. e.) 等人对教育评价理论作出巨大的贡献。

学习们把1967年界定为美国教育评价发展的转折点。

到了20世纪70年代以后,教育评价发展到第四个时期--"结果认同时期"。

这一时期在非常关注评价结果的认同问题。

关注评价过程,强调评价过程中评价给予个体更多被认可的可能。

总之,重视评价对个体发展的建构作用,因此,又称为"个体化评价时期"。

集成电路设计步骤

集成电路设计步骤ASIC设计流程分为前端和后端两部分,前端主要包括设计输入、模拟/仿真、逻辑综合:后端包括门级仿真、版图规划、布局、布线、参数提取与后仿真。

前端(Front End)的工作主要是将电路的功能转换为用硬件描述语言来实现,然后把代码转综合成逻辑门级的电路。

而后端(Back End)的部分做的是布局(Place)与布线(Route)以及版图,后仿真主要是测试经过P&A后某些电路产生的延时对整个系统的影响。

下面简要介绍流程中各个阶段的任务。

设计输入(Design entry): 输入使用硬件描述语言(Verilog或VHDL)描述的设计或原理图。

用硬件描述语言描述产品的功能和编写测试模块。

良好的代码风格应该具有以下特点:足够的注释说明和有意义的命名,- -行不要太长,组合逻辑中没有必要用非阻塞赋值,利用参数定义提高可读性和可维护性,注意向量的宽度,在对向量赋值时也应当指明数值的宽度,符合代码可综合的原则。

模拟/仿真(simulation):又称功能仿真。

通过仿真检查设计功能是否符合要求。

在设计完成后,还必须对设计的正确性进行测试。

通常的方法是对设计模块施加激励,通过观察其输出波形来检验功能的正确性。

激励模块一般称为测试台,在仿真环节可以编写不同的测试台对设计进行全方位的验证。

激励模块同样可以使用硬件描述语言来编写。

逻辑综合(Logic synthesis): 通过逻辑综合工具(常用的是Synopsys公司的DC)将硬件描述语言描述的设计通过转译(translation)、优化(optimization)和映射(mapping)产生与实现工艺相关的网表(net list)文件。

网表文件是- -种记录有逻辑门之间连接关系以及延时信息的文件。

综合是连接电路高层与物理实现的桥梁,综合结果的好坏决定于电路的设计,综合给定的限制条件与综合之后的门级网表将送到后端工具用于布局布线。

前仿真(门级,Prelayout simulation): 进行版图设计之前通过仿真检查设计功能是否符合要求。

Protues使用教程

Protues使用教程目录第1章概述 (3)1。

1 进入Proteus ISIS (3)1。

2 工作界面 (3)1.3 基本操作 (4)图形编辑窗口 (4)预览窗口(The Overview Window) (5)对象选择器窗口 (6)图形编辑的基本操作 (6)参考1 (10)参考2作原理图仿真调试 (11)1.4 实例一 (15)电路图的绘制 (15)KeilC与Proteus连接调试 (20)1.5 实例二 (24)电路图的绘制 (24)使用元件工具箱 (29)使用状态信息条 (29)使用对话框 (29)使用仿真信息窗口 (30)关闭Proteus ISIS (30)第2章菜单命令简述 (31)主窗口菜单 (31)表格输出窗口(Table)菜单 (33)方格输出窗口(Grid)菜单 (33)Smith圆图输出窗口(Smith)菜单 (33)直方图输出窗口(Histogram)菜单 (33)第3章参考例子: (39)第1章概述Proteus ISIS是英国Labcenter公司开发的电路分析与实物仿真软件.它运行于Windows 操作系统上,可以仿真、分析(SPICE)各种模拟器件和集成电路,该软件的特点是:①实现了单片机仿真和SPICE电路仿真相结合。

具有模拟电路仿真、数字电路仿真、单片机及其外围电路组成的系统的仿真、RS232动态仿真、I2C调试器、SPI调试器、键盘和LCD系统仿真的功能;有各种虚拟仪器,如示波器、逻辑分析仪、信号发生器等。

②支持主流单片机系统的仿真。

目前支持的单片机类型有:68000系列、8051系列、A VR系列、PIC12系列、PIC16系列、PIC18系列、Z80系列、HC11系列以及各种外围芯片。

③提供软件调试功能。

在硬件仿真系统中具有全速、单步、设置断点等调试功能,同时可以观察各个变量、寄存器等的当前状态,因此在该软件仿真系统中,也必须具有这些功能;同时支持第三方的软件编译和调试环境,如Keil C51 uVision2等软件。

录单的全部流程及关键点

录单的全部流程及关键点When it comes to the process of recording a single, there are many key points and steps to consider. 针对录单的整个流程,有许多关键点和步骤需要考虑。

From the initial intake and assessment of the client's needs to the actual recording and post-production work, each step is crucial to the overall success of the project. 从最初的接待和客户需求评估到实际的录音和后期制作工作,每个步骤对于项目的整体成功都是至关重要的。

It is important for the recording process to be well-organized and efficient in order to produce high-quality and professional results. 为了能够产生高质量和专业结果,录音过程必须要有条不紊和高效。

First and foremost, the recording process begins with an initial consultation and intake with the client. 首先,录音过程始于与客户的初步咨询和接待。

This step is crucial in understanding the client's needs, expectations, and vision for the project. 这一步骤对于了解客户的需求、期望和项目愿景至关重要。

It is important for the recording team to establish clear and open communication with the client in order to ensure that their vision is accurately captured in the final product. 录音团队需要与客户建立明确和开放的沟通,以确保他们的愿景能够准确地体现在最终成品中。

SMT工艺流程

SMT工艺流程1. 引言表面贴装技术(Surface Mount Technology,SMT)是一种电子组件的安装方式,它将表面电阻、电容、集成电路等元件直接焊接在印刷电路板(Printed Circuit Board,PCB)的表面上,而不是通过插针插入孔内。

SMT工艺流程是将电子元器件安装到PCB上的一系列步骤,它的高效性和可靠性使得SMT成为现代电子制造中最主要的组装技术之一。

本文将介绍SMT工艺流程的基本步骤和关键要点。

2. SMT工艺流程概述SMT工艺流程主要包括以下几个步骤:•印刷贴胶(Stencil Printing):将SMT贴装胶(Solder Paste)通过印刷方法均匀地涂刷到PCB的焊盘位置上。

印刷贴胶的质量直接影响后续的焊接质量。

•贴装(Component Placement):将SMT元件按照布局图的要求,利用高精度的贴装机器将元件放置在印刷好贴装胶的焊盘上。

贴装机器通常使用视觉系统来确保准确的位置。

•回流焊接(Reflow Soldering):通过回流炉将焊盘上的贴装胶加热到熔点,使得焊盘与元件之间的接合面液化,然后冷却固化,完成焊接过程。

回流焊接可以使用气体或者电炉来加热。

•清洗(Cleaning):清洗是一个可选的步骤,它的目的是去除焊接过程中可能残留的贴装胶、焊接剂或者其他污染物。

清洗可以使用溶剂、超声波或者水等方法。

•检查(Inspection):通过视觉检查或者自动检测设备来检查焊接的质量。

不合格的焊接可以进行修复或者重新制造。

3. SMT工艺流程详细步骤3.1 印刷贴胶印刷贴胶是SMT工艺流程中的第一步。

通常使用金属制成的Stencil来进行印刷,Stencil上有小孔,孔的位置和数量与PCB焊盘的位置和数量相对应。

印刷贴胶的质量对后续的焊接质量有很大影响。

3.2 贴装贴装是将SMT元件放置到已印刷好贴装胶的焊盘上。

贴装机器通常是自动化的,并具有高精度的定位能力。

模拟集成电路与数字集成电路设计工具实用教程 ICC使用教程

(最好每做一个步骤,保存一次数据,如:save_mw_cel -as floorplan)ICC实验步骤步骤1:Design Setup1.1数据准备新建后端布局布线目录icc_40,准备好以下文件1)DC导出的网表文件(top_pad.mapped.v)2)DC导出的sdc文件(top_pad.sdc)3)手工编写的tdf文件(/tmp/dig_lab/top_pad.tdf)在icc_40目录内启动终端,在终端下输入:>source /opt/demo/synopsys.env>icc_shell -gui &1.2设置search path、target_library、link_library输入下面的命令:>source -echo /tmp/dig_lab/icc_lib_setup.tcl1.3为设计创建libraryTechnology file为:/home/smic/smic_40/SCC40NLL_HS_RVT_V0p2b/astro/tf/scc40nll_hs_8lm_2tm.tf 两个参考库分别为:/home/smic/smic_40/SCC40NLL_HS_RVT_V0p2b/astro/scc40nll_hs_rvt/home/smic/smic_40/SP40NLLD2RN_3P3V_V0p5/apollo/SP40NLLD2RN_3P3V_V0p1_8 MT_2TM1.4读入verilog网表1.5进行uniquify输入下面的命令:>uniquify_fp_mw_cel#确认当前顶层设计,输入命令:>current_design top_pad#将网表中例化的单元与参考库中的单元做连接,输入命令:>link1.6设置TLU+文件MAX_TLUPLUS_FILE:/home/smic/smic_40/SCC40NLL_HS_RVT_V0p2b/astro/tluplus/TD‐LO40‐XS‐2006v0R_1Px M_2TM9k_ALPA28k/1P8M_2TM/StarRC_40LL_1P8M_2TM_ALPA28K_RCMAX.tluplusMIN_TLUPLUS_FILE:/home/smic/smic_40/SCC40NLL_HS_RVT_V0p2b/astro/tluplus/TD‐LO40‐XS‐2006v0R_1Px M_2TM9k_ALPA28k/1P8M_2TM/StarRC_40LL_1P8M_2TM_ALPA28K_RCMIN.tluplusMAP_FILE:/home/smic/smic_40/SCC40NLL_HS_RVT_V0p2b/astro/tluplus/TD‐LO40‐XS‐2006v0R_1Px M_2TM9k_ALPA28k/1P8M_2TM/StarRC_40LL_1P8M_2TM_cell.map1.7读入SDC文件,设置芯片工作环境1.8 检查设计的合理性依次输入以下命令:>set_zero_interconnect_delay_mode true>report_timing>report_constraint ‐all_violators>set_zero_interconnect_delay_mode false步骤2:Floorplan2.1在设计中添加电源地IO及IO Corner1)I O Corner2)为Core供电的IO(VDD VSS)3)为IO供电的IO(VDD_IO VSS_IO)直接输入以下命令:create_cell {CORNER1 CORNER2 CORNER3 CORNER4} {PCORNERRN} create_cell {VDD} PVDD1RNcreate_cell {VSS} PVSS1RNcreate_cell {VDD_IO} PVDD2RNcreate_cell {VSS_IO} PVSS2RN2.2读入IO约束文件相应的命令为:read_pin_pad_physical_constraints /tmp/dig_lab/top_pad.tdf该文件内容如下:set_pad_physical_constraints -pad_name clk_block -side 1 -order 1set_pad_physical_constraints -pad_name data_in_block -side 1 -order 2 set_pad_physical_constraints -pad_name en_block -side 2 -order 1set_pad_physical_constraints -pad_name fsk_out_block -side 2 -order 2 set_pad_physical_constraints -pad_name VDD -side 3 -order 1set_pad_physical_constraints -pad_name VSS -side 3 -order 2set_pad_physical_constraints -pad_name VDD_IO -side 4 -order 1set_pad_physical_constraints -pad_name VSS_IO -side 4 -order 2set_pad_physical_constraints -pad_name CORNER1 -side 1 -order 0set_pad_physical_constraints -pad_name CORNER2 -side 2 -order 0 set_pad_physical_constraints -pad_name CORNER3 -side 3 -order 0 set_pad_physical_constraints -pad_name CORNER4 -side 4 -order 02.3创建floorplan相应的命令为:>create_floorplan -control_type aspect_ratio \ -core_aspect_ratio 1 \-core_utilization 0.5 \-row_core_ratio 1 \-left_io2core 30 \-bottom_io2core 30 \-right_io2core 30 \-top_io2core 30 \-start_first_row#移除terminal,输入命令:>remove_terminal *该操作之后的效果为:2.4加入pad filler相应的命令为:>insert_pad_filler -cell {PFILL20RN PFILL10RN PFILL5RN PFILL2RN PFILL1RN PFILL01RN PFILL001RN} -overlap_cell {PFILL01RN PFILL001RN}2.5添加Tap Cell>add_tap_cell_array \‐master_cell_name {FILLTIEHS} \ ‐distance 20 \‐pattern stagger_every_other_row \ ‐respect_keepout摆放完毕之后效果如下:2.6进行电源地逻辑连接相应的命令为:>derive_pg_connection ‐power_net {VDD} ‐power_pin {VDD} \‐ground_net {VSS} ‐ground_pin {VSS}derive_pg_connection ‐power_net {VDD} ‐ground_net {VSS} ‐tie 2.7创建Core PG Rings相应的命令为:>create_rectangular_rings ‐nets {VDD VSS} \‐left_segment_layer M6 ‐left_segment_width 4.5 \‐right_segment_layer M6 ‐right_segment_width 4.5 \‐bottom_offset 17 ‐bottom_segment_layer TM1 ‐bottom_segment_width 4.5 \ ‐top_offset 17 ‐top_segment_layer TM1 ‐top_segment_width 4.5 \‐offsets absolute2.8布IO的电源和地线相应的命令为:>preroute_instances -ignore_macros \-ignore_cover_cells \-connect_instances specified \-cells [get_cells -all {VDD VSS}]2.9布PG rail(给标准单元供电的电源和地线)效果为:相应的命令为:>preroute_standard_cells ‐nets {VDD VSS} \‐connect horizontal \‐fill_empty_rows \‐port_filter_mode off \‐cell_master_filter_mode off \‐cell_instance_filter_mode off \‐voltage_area_filter_mode off \‐route_type {P/G Std. Cell Pin Conn}2.10检查电源地网络1)检查IO的电源地连接以及PG Rail/Strap是否存在Floating:相应的命令为:verify_pg_nets ‐error_cel io_pg \‐std_cell_pin_connection ignore \‐macro_pin_connection all \‐pad_pin_connection all2)做电源网络分析(PNA)查看电源规划的IR Drop。

教育评价的概念、分类、步骤和基本模式.doc

assessment(常模参照性评价)和individual--referencedassessment(个体参照性评价)。

关于“个体参照性评价”该书是这样定义的:个体参照性评价是以学习者过去的(学习)表现如何,或他(她)的个人(学习)能力的估计怎么样为基准做出评价的。

(Individual--referencedassessmentisbasedonhowwellthelearnerisperformingrelativetohisorherownpreviousperformance,orrelativetoanestimateofhisorindividualability.)例如,一位学了好几个月的课程后,只能说几句英语的学生,经过另一个月的学习后,他能比较流利地说英语(即使是有些地方不那么准确),我们可以肯定地说他取得了很大的进步。

形成性评价(formativeevaluation)是通过诊断教育方案或计划、教育过程与活动在存在的问题,为正在进行的教育活动提供反馈信息,以提高实践中正在进行的教育活动的质量的评价。

一般说来,形成性评价不以区分评价对象的优良为目的,不重视对被评对象进行分等鉴定。

总结性(summativeevaluation)与此不同,它是在教育活动发生后关于教育效果的判断。

一般地说,它与分等鉴定、做出关于受教育者和教育者的决策,做出教育资源分配的决策相联系。

学生的毕业考试、教师的考核、学校的鉴定都是总结性评价的例子。

这两种评价的不同点如下:第一、评价的目的、职能(或者说期望的用途)(expected uses)不同。

布鲁姆指出,形成性观察的主要目的是决定给定的学习任务被掌握的程度、未掌握的部分,它的目的不是为了对学习者分等或鉴定,而是帮助学生和教师把注意力集中在为进一步提高所必需的特殊的学习上。

总结性评价“指向更一般的等级评定”.总结性评价与教学效能的核定联系在一起,它为关于个体的决策、教育资源投资优先顺序的抉择提供依据。

元件布局(Component Placement)操作

PADS教程:第七节–元件布局(Component Placement)操作在本教程的这一部分,你将使用元件布局命令以及在前一节中学到的方法,完成教程的设计布局。

另外还将向你介绍PADS Layout 的簇布局(Cluster Placement)功能。

在这一节中,你将学习:·进行预处理过程·建立和布放元件组合(Unions)·采用PADS Logic进行原理图驱动布局(Schematic Driven Placement)·采用查找(Find)命令放置元件·放置晶体管(Transistors)和去耦电容(Filter Capacitors)·进行元件的极坐标方式布局(Radial Placement)进行预处理过程在你继续之前,你必须先进行以下几个过程的操作。

打开设计文件为了继续操作,打开previewrules.pcb设计文件。

如果你是从前一节教程顺序学习过来的,你必须打开这个设计文件,以便不受前一节教程中改变的影响。

1. 从工具条中选择打开(Open)图标。

2. 当Save old file before reloading?提示出现后,选择No。

3. 在文件打开(File Open)对话框中,双击previewrules.pcb文件名。

设置布局栅格(Placement Grid)1. 通过键入G50,并且按回车(Enter),设置设计栅格(Design grid)为50 mils。

2. 通过键入GD50,并且按回车(Enter),设置显示栅格(Display grid)为50 mils。

执行自动元件推挤(Nudging)PADS Layout 的布局功能允许你自动地推挤或调整元件的位置,无论元件放置的有多近,甚至元件叠在一起都可以调整。

为了进行元件的自动推挤:1. 选择工具/选项(Tools/Options),选项(Options)对话框将出现。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

所有有相同包裝類型零件, 有極性之電容 (如電解電容、坦質電容)、二極體、電晶體 等, 零件放置方向盡量一致, 頂多2個方向, 不可任意擺 (朝上、朝下, 取其一, 朝左、 朝右, 取其一) .

1

19

SPACE SMD小 SMD大 DIP BGA SMD小 20mil 25mil 20mil 40mil SMD大 25mil 30mil 30mil 100mil DIP 20mil 30mil 0mil 150mil SMD小零件小於等於排阻的SMD 零件 SMD大零件大於排阻的SMD 零件 零件間距以實體和焊點較大者為主:

1

23

IC Chip每個電源腳(Power Pin)要放置一 個旁路電容(Bypass Cap) . 注意電源走向,要將旁路電容(Bypass Cap)置於進入Chip之前的路徑.

1

24

1

25

1

26

Tune Length拉等長線,要預 留足夠的空間,主機板需Tune Length的線路如下:

Placement 的基本步驟和方法

1

1

Content

1 Placement的基本步驟

2 MB Placement的基本步驟

3 Placement時需注意的事項

1

2

Placement的两个大方向: 对外:达到客户的要求. 对內:达到工厂制程的要求.

1

3

Placement 的基本步驟 1. 研讀線路圖 :將線路圖分門別類 (如 Power Block, Audio Chip Block, Lan Chip Block, IO Block 等),熟悉方塊圖. 2. 將零件依Block 分類置於板外:將零件依 照線 路圖分類置於板外,根據Placement基 本原則 (近,短,少)排好,只剩下外串之連線. 要參考HW 写在图旁边的注解。

1 20

1

21

I/O Connector 的EMI Power Plane切割的EMI 正面走線跨Moat (Layer 2 Power Plane 切割) 的EMI 確實遵守DFM規則

1

22

Differential的線要預留足夠的空間, 如 USB、LAN、1394、Clock、或其他HW 要求的訊號. CLK的線要預留足夠的空間, Tune Length(拉等長)和Differential. Damping電阻要靠近Source起始端. Termination電阻要靠近Load負載末端.

1

12

5 . 放F.M.為了SMD機器自動置放零件

之基準設定,因此必須在板子四周擺放 Fiducial Mark(F.M)。若板子上無SMD 零 件就不必加。一般我們於板邊4個角落放置 光學測試點(F.M.),涵蓋住所有SMD零 件,必須放在package keepin內.板邊之 Fiducial Mark需有3個以上,若無法放3 個,最少放2個對角的Fiducial Mark。

1 4

3 將板外零件Block排入板中依照外串 之連線(Connection),從固定零件(如I/O Connector、PCI、DDR等…)的相關零件 區塊(Component Block)先放。再依照 線 路圖,將零件區塊(Block),置入板中.

1

5

4 排零件區塊(Component Block)時要考慮走 線、卡件、限高和散熱等問題 走線問題:預留空間走線或打Via進入Plane層。 卡件問題:參考DFM (Design for manufacture) 規則。 限高問題:如高Comp不可置於PCI Slot旁。 散熱問題:考慮散熱風向和預留散熱空間。

1

9

1

10

MB Placement的基本步驟

1 . 輸入機構圖 AutoCad —DXF檔(R14) PROE —IDF檔 2 . 定外框建立板子外框Board Outline, Package Keepin ( 夾板邊內縮200mil,其 餘2邊50mil ),Route Keepin ( 板框內縮 25mil )

1

6

•電容與PCI延伸卡卡鍵

1

7

5 . 檢查錯誤排零件時要順便檢查有無空 Pin、沒有外接的Pin,電阻或電容的1,2 Pin 相連,net的信號連錯等.若查出錯誤要向 硬體工程師反應。

1

8

补充说明:同常情况下,HW在设计原理图, 基本上是按模块来画原理图的.所 以在Placement时,一般以page摆 放.

1 11

3 定Layer Stack疊層順序Setup / Cross section定出Top、VCC、 GND、Bottom 4 Net In Import \ Logical輸入Net list。Net list需包含機構孔和光學點, 要求HW在線路圖上加入(光學點我們自 己也可以加入,但在Export Pickplace 後 必須再添加)

1

17

所有SMD零件之實體 ( Placement Bound ) 或者焊點 ( Padstack ) , 至少離 軌跡板邊200mil以上, 其餘兩邊為50mil

所有DIP零件(外插90度零件除外)之實體 ( Placement Bound ) 不可超出板外, 焊點 ( Padstack ) 邊緣離板邊200mil以上

1

13

6 . 根據機構圖放置固定零件 機構孔。 PCI & AGP 插槽。 I/O Connector。 CPU若風扇固定於外殼,則位置需 固定。

1

14

7 . 放置非固定零件,但大致位置不變者 DIMM & DDR。 IDE(SATA) & FLOPPY。 P4 CPU,北橋North Bridge,南橋 South Bridge。 風扇Fan Connector,外接Jump

1

15

8 . 決定大零件位置如super IO、audio chip、LAN chip、clock generator、 VRM chip、Bios chip和MOS chip 等… 9 . 放置其餘剩下的零件

1

16

Placement 時需注意的事項 零件擺放時格點要開5以上(Grid>=

5mil). 建議:新圖排Placement時Grid= 10mil,部分修改或太密集時Grid=5mil. 嚴禁使用<5mil的格點.