201003_IT in TSMC

07- TSM V6.1 Monitoring and Reporting

Discovering the value of the IBM Tivoli Storage Manager v6.2 Product Family

Tivoli Storage Manager v6.x Monitoring and Reporting

An IBM Proof of Technology

The Tivoli Monitoring agent is installable on this OS

The agent is NOT installable on this OS but is able to monitor TSM remotely from the Tivoli Monitoring server The agent is NOT installable on this OS but is able to monitor TSM remotely from the Tivoli Monitoring server The agent is NOT installable on this OS but is able to monitor TSM remotely from the Tivoli Monitoring server The Tivoli Monitoring agent is installable on this OS

● Can monitor and report 5.4, 5.5 and 6.x servers ● No need to license DB2, Tivoli Monitoring or Tivoli Common Reporting separately

© 2010 IBM Corporation

IEEE拒绝收录的138个会议列表-推荐下载

IEEE拒绝收录的138个会议列表2011-10-27 14:54:18| 分类:EI、ISTP检索国际 | 标签:ieee 收录 138 会议列表 |字号大中小订阅IEEE拒绝收录的138个会议列表138个会议名单如下:2010 2nd Asia-Pacific Conference on Information Processing (APCIP)2010 2nd International Asia Symposium on Intelligent Interaction and Affective Computing & 2010 2nd International onInnovation Management (ASIA-ICIM)2010 2nd International Conference on Future Computer and Communication (FCC) 2010 2nd International Conference on Information and Multimedia Technology (ICIMT)2010 2nd International Conference on Intellectual Technique in Industrial Practice (ITIP 2010)2010 2nd International Conference on Multimedia and Computational Intelligence (ICMCI)2010 2nd International Conference on Research Challenges in Computer Science (ICRCCS)2010 2nd International Symposium on Computer Network and Multimedia Technology (CNMT 2010)2010 3rd International Conference on Computational Intelligence and Industrial Application (PACIIA)2010 3rd International Conference on Environmental and Computer Science (ICECS) 2010 3rd International Conference on Machine Vision (ICMV)2010 3rd International Conference on Power Electronics and Intelligent Transportation System (PEITS)2010 4th International Conference on Intelligent Information Technology Application (IITA)2010 6th International Conference on MEMS, NANO, and Smart Systems (ICMENS) 2010 First International Conference on Cellular, Molecular Biology, Biophysics and Bioengineering (CMBB)2010 IIS 2nd International Conference on Signal Processing, Robotics and Automation (ICSRA 2010)2010 International Asia Conference on Optical Instrument and Measurement (ACPIM)2010 International Conference on Bio-Inspired Systems and Signal Processing (ICBSSP)2010 International Conference on Biology, Environment and Chemistry (ICBEC) 2010 International Conference on Broadcast Technology and MultimediaCommunication (BTMC)2010 International Conference on Circuit and Signal Processing (ICCSP)2010 International Conference on Communication and Vehicular Technology (ICCVT)2010 International Conference on Computational Intelligence and Vehicular System (CIVS)2010 International Conference on Computer and Computational Intelligence (ICCCI) 2010 International Conference on Computer and Software Modeling (ICCSM)2010 International Conference on Computer Science and Sports Engineering (CSSE) 2010 International Conference on Computer-Aided Manufacturing and Design (CMD)2010 International Conference on Construction and Project Management (ICCPM) 2010 International Conference on Digital Enterprise and Digital Manufacturing (DEDM)2010 International Conference on E-business, Management and Economics (ICEME) 2010 International Conference on Economics, Business and Management (ICEBM) 2010 International Conference on Electrical Engineering and Automatic Control (ICEEAC)2010 International Conference on Embedded Systems and Microprocessors (ICESM) 2010 International Conference on Engineering Education and Educational Technology (EEET)2010 International Conference on Future Biomedical Information Engineering (FBIE) 2010 International Conference on Future Computer, Control and Communication (FCCC)2010 International Conference on Future Industrial Engineering and Application (ICFIEA)2010 International Conference on Future Information Technology (ICFIT)2010 International Conference on Future Information Technology and Computing (FITC)2010 International Conference on Graphic and Image Processing (ICGIP)2010 International Conference on Information and Finance (ICIF)2010 International Conference on Information Security and Artificial Intelligence (ISAI)2010 International Conference on Intelligence and Information Technology (ICIIT) 2010 International Conference on Intelligent Network and Computing (ICINC)2010 International Conference on Management Science (ICMS)2010 International Conference on Management Science and Information Engineering (ICMSIE)2010 International Conference on Manufacturing Science and Technology (ICMST) 2010 International Conference on Measurement and Control Engineering (ICMCE) 2010 International Conference on Mechanical and Aerospace Engineering (ICMAE) 2010 International Conference on Mechanical Engineering, Robotics and Aerospace (ICMERA)2010 International Conference on Modeling, Simulation and Control (ICMSC 2010)2010 International Conference on Nano Science and Technology (ICNST)2010 International Conference on Nanotechnology and Biosensors (ICNB)2010 International Conference on Nuclear Energy and Engineering Technology (NEET)2010 International Conference on Physics Science and Technology (ICPST)2010 International Conference on Psychology, Psychological Sciences and Computer Science (PPSCS)2010 International Conference on Remote Sensing (ICRS)2010 International Conference on Semiconductor Laser and Photonics (ICSLP)2010 International Conference on Services Science, Management and Engineering (SSME)2010 International Conference on Signal and Information Processing (ICSIP)2010 International Conference on Software and Computing Technology (ICSCT) 2010 International Conference on Sport Medicine, Sport Science, and Computer Science (SMSSCS)2010 ISECS International Colloquium on Computing, Communication, Control, and Management (CCCM 2010)2010 Second International Conference on E-Learning, E-Business, Enterprise Information Systems, and E-Government(EEEE)2010 Second International Conference on Test and Measurement (ICMT)2010 Second International Seminar on Business and Information Management (ISBIM)2010 Third International Conference on Computer and Electrical Engineering (ICCEE)2010 Third International Conference on Education Technology and Training (ETT) 2010 Third International Symposium on Intelligent Ubiquitous Computing and Education (IUCE)2010 Third Pacific-Asia Conference on Web Mining and Web-Based Application (WMWA)2011 15th Global Chinese Conference on Computers in Education (GCCCE)2011 2nd Asia-Pacific Conference on Wearable Computing Systems (APWCS)2011 2nd International Conference on Biomedical Engineering and Computer Science (ICBECS)2011 2nd International Conference on Biotechnology and Food Science (ICBFS) 2011 2nd International Conference on Data Storage and Data Engineering (DSDE) 2011 2nd International Conference on Environmental Science and Technology (ICEST)2011 2nd International Conference on Financial Theory and Engineering (ICFTE) 2011 2nd International Conference on Mechanical, Industrial, and Manufacturing Technologies (MIMT)2011 2nd Intl Conf on Innovative Computing & Communication and 2010 Asia-Pacific Conf on Information Technology &Ocean Engineering, (CICC-ITOE)2011 2nd World Congress on Computer Science and Information Engineering (CSIE) 2011 3rd IEEE International Conference on Information Management and Engineering (ICIME)2011 3rd International Conference on Bioinformatics and Biomedical Technology (ICBBT 2011)2011 3rd International Conference on Computer and Automation Engineering (ICCAE)2011 3rd International Conference on Computer and Network Technology (ICCNT) 2011 3rd International Conference on Computer Design and Applications (ICCDA 2011)2011 3rd International Conference on Computer Modeling and Simulation (ICCMS) 2011 3rd International Conference on E-business and Information System Security (EBISS)2011 3rd International Conference on Machine Learning and Computing (ICMLC) 2011 3rd International Conference on Networks Security, Wireless Communications and Trusted Computing (NSWCTC)2011 3rd International Conference on Signal Acquisition and Processing (ICSAP) 2011 3rd International Workshop on Education Technology and Computer Science (ETCS)2011 4th IEEE International Conference on Computer Science and Information Technology (ICCSIT 2011)2011 IEEE International Conference on Information and Education Technology (ICIET)2011 IEEE International Conference on Smart Grid and Clean Energy Technologies (ICSGCE)2011 International Conference on Applied Physics and Mathematics (ICAPM 2011) 2011 International Conference on Bioinformatics and Computational Biology (ICBCB)2011 International Conference on Bioscience, Biochemistry and Bioinformatics (ICBBB)2011 International Conference on Communication and Electronics Information (ICCEI)2011 International Conference on Computer and Communication Devices (ICCCD) 2011 International Conference on Computer Applications and Network Security (ICCANS)2011 International Conference on Computers, Communications, Control and Automation (CCCA)2011 International Conference on Control, Robotics and Cybernetics (ICCRC)2011 International Conference on Data Engineering and Internet Technology (DEIT) 2011 International Conference on Database and Data Mining (ICDDM)2011 International Conference on Digital Convergence (ICDC)2011 International Conference on Economics and Finance Research (ICEFR)2011 International Conference on Economics, Business and Marketing Management (CEBMM)2011 International Conference on Economics, Trade and Development (ICETD) 2011 International Conference on Electrical Energy and Networks (ICEEN)2011 International Conference on Energy and Environment (ICEE)2011 International Conference on Engineering and Information Management (ICEIM) 2011 International Conference on Environment Science and Engineering (ICESE) 2011 International Conference on Environmental Science and Development (ICESD) 2011 International Conference on Future Environment and Energy (ICFEE 2011) 2011 International Conference on Fuzzy Systems and Neural Computing (FSNC) 2011 International Conference on Information and Computer Applications (ICICA) 2011 International Conference on Information and Computer Networks (ICICN) 2011 International Conference on Information and Industrial Electronics (ICIIE) 2011 International Conference on Information Engineering and Mechanical Engineering (IEME)2011 International Conference on Innovation and Information Management (ICIIM) 2011 International Conference on Intelligent Information Networks (ICIIN)2011 International Conference on Knowledge Discovery (ICKD)2011 International Conference on Life Science and Technology (ICLST)2011 International Conference on Manufacturing and Industrial Engineering (ICMIE) 2011 International Conference on Mechanical and Aerospace Engineering (ICMAE) 2011 International Conference on Medical Information and Bioengineering (ICMIB) 2011 International Conference on Network Communication and Computer (ICNCC) 2011 International Conference on Product Development and Renewable Energy Resources (ICPDRE)2011 International Conference on Security Science and Technology (ICSST)2011 International Conference on Social Science and Humanity (ICSSH)2011 International Conference on Solid-State and Integrated Circuit (ICSIC)2011 International Conference on System Design and Data Proceesing (ICSDDP) 2011 International Conference on System。

tms320vc5416数据手册

TMS320VC5416Fixed-Point Digital Signal Processor Data ManualPRODUCTION DATA information is current as of publication date.Products conform to specifications per the terms of the TexasInstruments standard warranty.Production processing does notnecessarily include testing of all parameters.Literature Number:SPRS095PMarch1999–Revised October2008Revision HistoryTMS320VC5416Fixed-Point Digital Signal ProcessorSPRS095P–MARCH 1999–REVISED OCTOBER 2008NOTE:Page numbers for previous revisions may differ from page numbers in the current version.This data sheet revision history highlights the technical changes made to the SPRS095O device-specific data sheet to make it an SPRS095P revision.Scope:This document has been reviewed for technical accuracy;the technical content is up-to-date as of the specified release date with the following corrections.2Revision History Submit Documentation FeedbackContentsTMS320VC5416Fixed-Point Digital Signal ProcessorSPRS095P–MARCH 1999–REVISED OCTOBER 2008Revision History ...........................................................................................................................1TMS320VC5416Features.......................................................................................................2Introduction.......................................................................................................................2.1Description ..................................................................................................................2.2PinAssignments............................................................................................................2.2.1TerminalAssignments forthe GGUPackage...............................................................2.2.2Pin AssignmentsforthePGEPackage......................................................................2.2.3Signal Descriptions ..............................................................................................3Functional Overview ...........................................................................................................3.1Memory ......................................................................................................................3.1.1Data Memory .....................................................................................................3.1.2Program Memory ................................................................................................3.1.3Extended Program Memory ...................................................................................3.2On-Chip ROM With Bootloader ...........................................................................................3.3On-Chip RAM ...............................................................................................................3.4On-Chip Memory Security .................................................................................................3.5Memory Map ................................................................................................................3.5.1Relocatable Interrupt Vector Table ............................................................................3.6On-Chip Peripherals .......................................................................................................3.6.1Software-Programmable Wait-State Generator .............................................................3.6.2Programmable Bank-Switching ................................................................................3.6.3Bus Holders ......................................................................................................3.7Parallel I/O Ports ...........................................................................................................3.7.1Enhanced 8-/16-Bit Host-Port Interface (HPI8/16)..........................................................3.7.2HPI Nonmultiplexed Mode ......................................................................................3.8Multichannel Buffered Serial Ports (McBSPs)..........................................................................3.9Hardware Timer ............................................................................................................3.10Clock Generator ............................................................................................................3.11Enhanced External Parallel Interface (XIO2)...........................................................................3.12DMA Controller .............................................................................................................3.12.1Features ..........................................................................................................3.12.2DMA External Access ...........................................................................................3.12.3DMA Memory Maps .............................................................................................3.12.4DMA Priority Level ...............................................................................................3.12.5DMA Source/Destination Address Modification .............................................................3.12.6DMA in Autoinitialization Mode ................................................................................3.12.7DMA Transfer Counting .........................................................................................3.12.8DMA Transfer in Doubleword Mode ..........................................................................3.12.9DMA Channel Index Registers .................................................................................3.12.10DMA Interrupts ..................................................................................................3.12.11DMA Controller Synchronization Events .....................................................................3.13General-Purpose I/O Pins .................................................................................................3.13.1McBSP Pins as General-Purpose I/O .........................................................................3.13.2HPI Data Pins as General-Purpose I/O ......................................................................3.14Device ID Register .........................................................................................................3.15Memory-Mapped Registers ...............................................................................................3.16McBSP Control Registers and Subaddresses ..........................................................................3.17DMA Subbank Addressed Registers ....................................................................................3.18Interrupts ....................................................................................................................4Support .............................................................................................................................Contents3TMS320VC5416Fixed-Point Digital Signal ProcessorSPRS095P–MARCH1999–REVISED 4.1Documentation Support...................................................................................................4.2Device and Development-Support Tool Nomenclature................................................................5Electrical Specifications......................................................................................................5.1Absolute Maximum Ratings...............................................................................................5.2Recommended Operating Conditions...................................................................................5.3Electrical Characteristics.................................................................................................5.3.1Test Loading.....................................................................................................5.3.2Timing Parameter Symbology............................................................................................5.3.3Internal Oscillator With External Crystal.................................................................................5.4Clock Options...............................................................................................................5.4.1Divide-By-Two and Divide-By-Four Clock Options..........................................................5.4.2Multiply-By-N Clock Option(PLL Enabled)...................................................................5.5Memory and Parallel I/O Interface Timing..............................................................................5.5.1Memory Read....................................................................................................5.5.2Memory Write....................................................................................................5.5.3I/O Read..........................................................................................................5.5.4I/O Write..........................................................................................................5.5.5Ready Timing for Externally Generated Wait States..................................................................5.5.6and Timings...............................................................................................5.5.7Reset,BIO,Interrupt,and MP/MC Timings.............................................................................5.5.8Instruction Acquisition and Interrupt Acknowledge Timings..........................................5.5.9External Flag(XF)and TOUT Timings..................................................................................5.5.10Multichannel Buffered Serial Port(McBSP)Timing...................................................................5.5.10.1McBSP Transmit and Receive Timings....................................................................5.5.10.2McBSP General-Purpose I/O Timing.......................................................................5.5.10.3McBSP as SPI Master or Slave Timing....................................................................5.5.11Host-Port Interface Timing...............................................................................................5.5.11.1HPI8Mode.....................................................................................................5.5.11.2HPI16Mode....................................................................................................6Mechanical Data.................................................................................................................6.1Package Thermal Resistance Characteristics..........................................................................4Contents Submit Documentation FeedbackTMS320VC5416Fixed-Point Digital Signal Processor SPRS095P–MARCH1999–REVISED OCTOBER2008List of Figures2-1144-Ball GGU MicroStar BGA™(Bottom View).............................................................................2-2144-Pin PGE Low-Profile Quad Flatpack(Top View).......................................................................3-1TMS320VC5416Functional Block Diagram..................................................................................3-2Program and Data Memory Map................................................................................................3-3Extended Program Memory Map...............................................................................................3-4Process Mode Status Register..................................................................................................3-5Software Wait-State Register(SWWSR)[Memory-Mapped Register(MMR)Address0028h].........................3-6Software Wait-State Register(SWWSR)[Memory-Mapped Register(MMR)Address0028h].........................3-7Bank-Switching Control Register BSCR)[MMR Address0029h]...........................................................3-8Host-Port Interface—Nonmulltiplexed Mode.................................................................................3-9HPI Memory Map.................................................................................................................3-10Multichannel Control Register(MCR1).........................................................................................3-11Multichannel Control Register(MCR2).........................................................................................3-12Pin Control Register(PCR)......................................................................................................3-13Nonconsecutive Memory Read and I/O Read Bus Sequence.............................................................3-14Consecutive Memory Read Bus Sequence(n=3reads)..................................................................3-15Memory Write and I/O Write Bus Sequence.................................................................................3-16DMA Transfer Mode Control Register(DMMCRn)...........................................................................3-17On-Chip DMA Memory Map for Program Space(DLAXS=0and SLAXS=0).........................................3-18On-Chip DMA Memory Map for Data and IO Space(DLAXS=0and SLAXS=0)....................................3-19DMPREC Register................................................................................................................3-20General-Purpose I/O Control Register(GPIOCR)[MMR Address003Ch]................................................3-21General-Purpose I/O Status Register(GPIOSR)[MMR Address003Dh].................................................3-22Device ID Register(CSIDR)[MMR Address003Eh].........................................................................3-23IFR and IMR Registers...........................................................................................................5-1Tester Pin Electronics............................................................................................................5-2Internal Divide-By-Two Clock Option With External Crystal...............................................................5-3External Divide-By-Two Clock Timing.........................................................................................5-4Multiply-By-One Clock Timing..................................................................................................5-5Nonconsecutive Mode Memory Reads.......................................................................................5-6Consecutive Mode Memory Reads............................................................................................5-7Memory Write(MSTRB=0)....................................................................................................5-8Parallel I/O Port Read(IOSTRB=0).........................................................................................5-9Parallel I/O Port Write(IOSTRB=0)..........................................................................................5-10Memory Read With Externally Generated Wait States.....................................................................5-11Memory Write With Externally Generated Wait States.....................................................................5-12I/O Read With Externally Generated Wait States...........................................................................5-13I/O Write With Externally Generated Wait States...........................................................................5-14HOLD and HOLDA Timings(HM=1).........................................................................................List of Figures5TMS320VC5416Fixed-Point Digital Signal ProcessorSPRS095P–MARCH1999–REVISED 5-15Reset and BIO Timings.........................................................................................................5-16Interrupt Timing..................................................................................................................5-17MP/MC Timing...................................................................................................................5-18Instruction Acquisition(IAQ)and Interrupt Acknowledge(IACK)Timings................................................5-19External Flag(XF)Timing......................................................................................................5-20TOUT Timing.....................................................................................................................5-21McBSP Receive Timings.......................................................................................................5-22McBSP Transmit Timings.......................................................................................................5-23McBSP General-Purpose I/O Timings........................................................................................5-24McBSP Timing as SPI Master or Slave:CLKSTP=10b,CLKXP=0....................................................5-25McBSP Timing as SPI Master or Slave:CLKSTP=11b,CLKXP=0....................................................5-26McBSP Timing as SPI Master or Slave:CLKSTP=10b,CLKXP=1....................................................5-27McBSP Timing as SPI Master or Slave:CLKSTP=11b,CLKXP=1....................................................5-28Using HDS to Control Accesses(HCS Always Low)........................................................................5-29Using HCS to Control Accesses...............................................................................................5-30HINT Timing......................................................................................................................5-31GPIOx Timings...................................................................................................................5-32Nonmultiplexed Read Timings.................................................................................................5-33Nonmultiplexed Write Timings.................................................................................................5-34HRDY Relative to CLKOUT....................................................................................................6List of Figures Submit Documentation FeedbackTMS320VC5416Fixed-Point Digital Signal Processor SPRS095P–MARCH1999–REVISED OCTOBER2008List of Tables2-1Terminal Assignments for the TMS320VC5416GGU(144-Pin BGA Package).........................................2-2Signal Descriptions...............................................................................................................3-1Standard On-Chip ROM Layout...............................................................................................3-2Processor Mode Status(PMST)Register Bit Fields........................................................................3-3Software Wait-State Register(SWWSR)Bit Fields.........................................................................3-4Software Wait-State Control Register(SWCR)Bit Fields..................................................................3-5Bank-Switching Control Register(BSCR)Fields..............................................................................3-6Bus Holder Control Bits..........................................................................................................3-7Sample Rate Input Clock Selection...........................................................................................3-8Clock Mode Settings at Reset.................................................................................................3-9DMD Section of the DMMCRn Register......................................................................................3-10DMA Reload Register Selection...............................................................................................3-11DMA Interrupts...................................................................................................................3-12DMA Synchronization Events..................................................................................................3-13DMA Channel Interrupt Selection..............................................................................................3-14Device ID Register(CSIDR)Bits................................................................................................3-15CPU Memory-Mapped Registers................................................................................................3-16Peripheral Memory-Mapped Registers for Each DSP Subsystem........................................................3-17McBSP Control Registers and Subaddresses.................................................................................3-18DMA Subbank Addressed Registers...........................................................................................3-19Interrupt Locations and Priorities................................................................................................5-1Input Clock Frequency Characteristics.........................................................................................5-2Clock Mode Pin Settings for the Divide-By-2and By Divide-By-4Clock Options.......................................5-3Divide-By-2and Divide-By-4Clock Options Timing Requirements.......................................................5-4Divide-By-2and Divide-By-4Clock Options Switching Characteristics...................................................5-5Multiply-By-N Clock Option Timing Requirements..........................................................................5-6Multiply-By-N Clock Option Switching Characteristics......................................................................5-7Memory Read Timing Requirements..........................................................................................5-8Memory Read Switching Characteristics.....................................................................................5-9Memory Write Switching Characteristics.....................................................................................5-10I/O Read Timing Requirements................................................................................................5-11I/O Read Switching Characteristics...........................................................................................5-12I/O Write Switching Characteristics............................................................................................5-13Ready Timing Requirements for Externally Generated Wait States......................................................5-14Ready Switching Characteristics for Externally Generated Wait States..................................................5-15HOLD and HOLDA Timing Requirements....................................................................................5-16HOLD and HOLDA Switching Characteristics...............................................................................5-17Reset,BIO,Interrupt,and MP/MC Timing Requirements..................................................................5-18Instruction Acquisition(IAQ)and Interrupt Acknowledge(IACK)Switching Characteristics...........................List of Tables7TMS320VC5416Fixed-Point Digital Signal ProcessorSPRS095P–MARCH1999–REVISED 5-19External Flag(XF)and TOUT Switching Characteristics...................................................................5-20McBSP Transmit and Receive Timing Requirements.......................................................................5-21McBSP Transmit and Receive Switching Characteristics..................................................................5-22McBSP General-Purpose I/O Timing Requirements........................................................................5-23McBSP General-Purpose I/O Switching Characteristics...................................................................5-24McBSP as SPI Master or Slave Timing Requirements(CLKSTP=10b,CLKXP=0).................................5-25McBSP as SPI Master or Slave Switching Characteristics(CLKSTP=10b,CLKXP=0).............................5-26McBSP as SPI Master or Slave Timing Requirements(CLKSTP=11b,CLKXP=0).................................5-27McBSP as SPI Master or Slave Switching Characteristics(CLKSTP=11b,CLKXP=0).............................5-28McBSP as SPI Master or Slave Timing Requirements(CLKSTP=10b,CLKXP=1).................................5-29McBSP as SPI Master or Slave Switching Characteristics(CLKSTP=10b,CLKXP=1).............................5-30McBSP as SPI Master or Slave Timing Requirements(CLKSTP=11b,CLKXP=1).................................5-31McBSP as SPI Master or Slave Switching Characteristics(CLKSTP=11b,CLKXP=1).............................5-32HPI8Mode Timing Requirements.............................................................................................5-33HPI8Mode Switching Characteristics..........................................................................................5-34HPI16Mode Timing Requirements............................................................................................5-35HPI16Mode Switching Characteristics.......................................................................................6-1Thermal Resistance Characteristics............................................................................................8Submit Documentation Feedback List of Tables1TMS320VC5416FeaturesTMS320VC5416 Fixed-Point Digital Signal Processor SPRS095P–MARCH1999–REVISED OCTOBER2008Reads•Advanced Multibus Architecture With ThreeSeparate16-Bit Data Memory Buses and One•Arithmetic Instructions With Parallel Store and Program Memory Bus Parallel Load•40-Bit Arithmetic Logic Unit(ALU)Including a•Conditional Store Instructions40-Bit Barrel Shifter and Two Independent•Fast Return From Interrupt 40-Bit Accumulators•On-Chip Peripherals•17-×17-Bit Parallel Multiplier Coupled to a–Software-Programmable Wait-State 40-Bit Dedicated Adder for Non-Pipelined Generator and ProgrammableSingle-Cycle Multiply/Accumulate(MAC)Bank-SwitchingOperation–On-Chip Programmable Phase-Locked •Compare,Select,and Store Unit(CSSU)for the Loop(PLL)Clock Generator With External Add/Compare Selection of the Viterbi Operator Clock Source–One16-Bit Timer•Exponent Encoder to Compute an Exponent–Six-Channel Direct Memory Access(DMA) Value of a40-Bit Accumulator Value in aControllerSingle Cycle–Three Multichannel Buffered Serial Ports •Two Address Generators With Eight Auxiliary(McBSPs)Registers and Two Auxiliary Register–8/16-Bit Enhanced Parallel Host-Port Arithmetic Units(ARAUs)Interface(HPI8/16)•Data Bus With a Bus Holder Feature•Power Consumption Control With IDLE1,•Extended Addressing Mode for8M×16-Bit IDLE2,and IDLE3Instructions With Maximum Addressable External ProgramPower-Down ModesSpace•CLKOUT Off Control to Disable CLKOUT •128K×16-Bit On-Chip RAM Composed of:•On-Chip Scan-Based Emulation Logic,IEEE –Eight Blocks of8K×16-Bit On-ChipStd1149.1(JTAG)Boundary Scan Logic(1) Dual-Access Program/Data RAM•144-Pin Ball Grid Array(BGA)(GGU Suffix)–Eight Blocks of8K×16-Bit On-ChipSingle-Access Program RAM•144-Pin Low-Profile Quad Flatpack(LQFP)(PGE Suffix)•16K×16-Bit On-Chip ROM Configured forProgram Memory• 6.25-ns Single-Cycle Fixed-Point InstructionExecution Time(160MIPS)•Enhanced External Parallel Interface(XIO2)•8.33-ns Single-Cycle Fixed-Point Instruction •Single-Instruction-Repeat and Block-RepeatExecution Time(120MIPS) Operations for Program Code• 3.3-V I/O Supply Voltage(160and120MIPS)•Block-Memory-Move Instructions for BetterProgram and Data Management• 1.6-V Core Supply Voltage(160MIPS)•Instructions With a32-Bit Long Word Operand• 1.5-V Core Supply Voltage(120MIPS)(1)IEEE Standard1149.1-1990Standard-Test-Access Port and •Instructions With Two-or Three-OperandBoundary Scan ArchitectureTMS320C54x,TMS320are trademarks of Texas Instruments.All other trademarks are the property of their respective owners.PRODUCTION DATA information is current as of publication date.Copyright©1999–2008,Texas Instruments Incorporated Products conform to specifications per the terms of the TexasInstruments standard warranty.Production processing does notnecessarily include testing of all parameters.。

超大规模集成电路秋段成华老师第四次作业

1.Shown below are buffer-chain designs.(1) Calculate the minimum delay of a chain of inverters for the overall effectivefan-out of 64/1.(2) Using HSPICE and TSMC 0.18 um CMOS technology model with 1.8 Vpower supply, design a circuit simulation scheme to verify them with their correspondent parameters of N, f, and t p.N=3.6 ∴N=3.246(1)γ=1 F=64∴f=√F所以最佳反相器数目约为3通过仿真可以得到tphl=1.3568E-11 tplh=1.7498E-11 tp0=1.5533E-11(2)N=1时,tphl= 5.2735E-10 tplh= 8.1605E-10 tpd= 6.7170E-10N=2时,tplh=2.2478E-10 tphl=2.5567E-10 tpd=2.4023E-10N=3时,tphl=2.0574E-10 tplh=2.1781E-10 tpd=2.1178E-10N=4时,tplh=2.1579E-10 tphl=2.2189E-10 tpd=2.1884E-10从仿真结果可以看出N=3或者N=4时延迟时间最优,且N=2、3、4得到的仿真延迟时间与理论推导的时间比较接近,比例基本上是18、15、15.3,而N=1时仿真得到的延迟时间远小于理论推导的时间,但是最优结果依旧是N=3,f=4,tp=15。

* SPICE INPUT FILE: Bsim3demo1.sp--a chain of inverters.param Supply=1.8.lib 'C:\synopsys\Hspice_A-2007.09\tsmc018\mm018.l' TT.option captab.option list node post measout.tran 10p 6000p************************************************************.param tdval=10p.meas tran tplh trig v(in) val=0.9 td=tdval rise=2+targ v(out) val=0.9 rise=2.meas tran tphl trig v(in) val=0.9 td=tdval fall=2+targ v(out) val=0.9 fall=2.meas tpd param='(tphl+tplh)/2'*macro definitions**************************************************************nmos1.subckt nmos1 n1 n2 n3mn n1 n2 n3 Gnd nch l=0.2u w=0.4u ad=0.2p^2 pd=0.4u as=0.2p^2 ps=0.4u.ends nmos1**pmos1*.subckt pmos1 p1 p2 p3mp p1 p2 p3 Vcc pch l=0.2u w=0.8u ad=0.4p^2 pd=0.8u as=0.4p^2 ps=0.8u.ends pmos1*.subckt inv1 in outxmn out in Gnd nmos1xmp out in Vcc pmos1vcc Vcc Gnd Supply.ends inv1**nmos2*.subckt nmos2 n1 n2 n3mn n1 n2 n3 Gnd nch l=0.2u w=1.12u ad=0.56p^2 pd=1.12u as=0.56p^2 ps=1.12u .ends nmos2**pmos2*.subckt pmos2 p1 p2 p3mp p1 p2 p3 Vcc pch l=0.2u w=2.24u ad=1.12p^2 pd=2.24u as=1.12p^2 ps=2.24u .ends pmos2*.subckt inv2 in outxmn out in Gnd nmos2xmp out in Vcc pmos2vcc Vcc Gnd Supply.ends inv2**nmos3*.subckt nmos3 n1 n2 n3mn n1 n2 n3 Gnd nch l=0.2u w=3.2u ad=1.6p^2 pd=3.2u as=1.6p^2 ps=3.2u.ends nmos3**pmos3.subckt pmos3 p1 p2 p3mp p1 p2 p3 Vcc pch l=0.2u w=6.4u ad=3.2p^2 pd=6.4u as=3.2p^2 ps=6.4u.ends pmos3*.subckt inv3 in outxmn out in Gnd nmos3xmp out in Vcc pmos3vcc Vcc Gnd Supply.ends inv3**nmos4*.subckt nmos4 n1 n2 n3mn n1 n2 n3 Gnd nch l=0.2u w=9.04u ad=4.52p^2 pd=9.04u as=4.52p^2 ps=9.04u.ends nmos4**pmos4*.subckt pmos4 p1 p2 p3mp p1 p2 p3 Vcc pch l=0.2u w=18.08u ad=9.04p^2 pd=18.08u as=9.04p^2 ps=18.08u .ends pmos4*.subckt inv4 in outxmn out in Gnd nmos4xmp out in Vcc pmos4vcc Vcc Gnd Supply.ends inv4*main circuit netlistxinv1 in out1 inv1xinv2 out1 out2 inv2xinv3 out2 out3 inv3xinv4 out3 out inv4cl out Gnd 154.24fVin in Gnd 0.9 pulse(0.0 1.8 219p 40p 40p 1100p 2400p).print tran v(in) v(out).end2.Consider the logic network below, which may represent the critical path of a morecomplex logic block. The output of the。

中国最先进集成电路芯片工艺指标

中国最先进集成电路芯片工艺指标下载提示:该文档是本店铺精心编制而成的,希望大家下载后,能够帮助大家解决实际问题。

文档下载后可定制修改,请根据实际需要进行调整和使用,谢谢!本店铺为大家提供各种类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by this editor. I hope that after you download it, it can help you solve practical problems. The document can be customized and modified after downloading, please adjust and use it according to actual needs, thank you! In addition, this shop provides you with various types of practical materials, such as educational essays, diary appreciation, sentence excerpts, ancient poems, classic articles, topic composition, work summary, word parsing, copy excerpts, other materials and so on, want to know different data formats and writing methods, please pay attention!随着科技的不断发展,集成电路芯片作为电子设备的核心配件,其制造工艺也在不断升级。

Application_note_for_customized_cells

T SMC C o n f i d e n t i a l I n f o r m a t i o n 330194T si n g h u a U n i v e r s i t y 01/25/2010Application Note for Customized Device inTSMC PDK4/21/2004 v0.1IntroductionThis document is an application note for TSMC PDK users who want to add customized devices or 3rd IP into TSMC PDK. There are three parts for users from data preparation, adding devices flow, to design flow.1. Data preparationLayoutNetlist or model i. Simulation netlist for IP or model for device ii. LVS netlist for IP or device iii. Pin order, name and position2. Add customized devices into TSMC PDK Layout view Symbol viewSimulation views (hpsiceS, spectre, ads, eldo ….) LVS views (auCdl, auLvs ..)3. Design flow for customized devicesSchematic entry Artist simulationVirtuosoXL layout driven flow Assura LVS flow Assura RCX flow Assura Extract view Calibre LVS flow Calibre RCX flowThe limitations of this method are1. Parameterized device is not includes in the document.2. The black box flow will skip the parasitic RC which over or near the customized cells._________________ TSMC Confidential Information 330194 Tsinghua University 01/25/2010 _________________T SMC C o n f i d e n t i a l I n f o r m a t i o n 330194T si n g h u a U n i v e r s i t y 01/25/20101. Data PreparationLayoutAfter the layouts ready, user needs to stream them into TSMC PDK library by using TSMC virtuoso tech file. And the cell name must be assigned to a corresponding name. There are two important steps need to be added in the layout.1. Create shape pin, the pin layer number must be the same as input/output layer. To add the pin layer is essential for Virtuoso XL and Assura LVS.2. Create label pin, the labels are used for Hercules/Calibre/Assura LVS recognized. User needs to follow TSMC layer definition to add corresponding label layer. For example, metal1’s label layer is ("METAL1" "pin"). Those names must be all the same as symbol._________________ TSMC Confidential Information 330194 Tsinghua University 01/25/2010 _________________T SMC C o n f i d e n t i a l I n f o r m a t i o n 330194T si n g h u a U n i v e r s i t y 01/25/2010 Netlist or modelIf the customized cell is a primitive device, it is necessary to prepare corresponding simulation model and LVS sub-circuit. The following is an example for a customized devicea. model for my_ind cellsubckt my_ind PLUS MINUSR1 (PLUS MINUS) resistor r=1000ends my_ind b. LVS sub-circuit.SUBCKT my_ind PLUS MINUS .ENDSNOTE : The cell name, pin names and order of pin name must be all the same at any place._________________ TSMC Confidential Information 330194 Tsinghua University 01/25/2010 _________________T SMC C o n f i d e n t i a l I n f o r m a t i o n 330194T si n g h u a U n i v e r s i t y 01/25/20102. Add customized devices into TSMC PDKLayout viewStream into TSMC PDK library as a cell, then and add shape pin and label.Please refer to layout of data preparation section. Symbol viewUse Virtuoso Symbol Editor to edit a symbol view, the pins must be correctly assigned. And the pin name must be the same with others.Other views (spectre, hspiceS, auLVS, auCdl ….)User needs to copy symbol view to other views, then loading a corresponding CDF (component description file). The sample CDF file is attached below. The red ink means they need to be modified case by case./****************************************************/ LIBRARY = "my_lib " CELL = "my_ind "_________________ TSMC Confidential Information 330194 Tsinghua University 01/25/2010 _________________T SMC C o n f i d e n t i a l I n f o r m a t i o n 330194T si n g h u a U n i v e r s i t y 01/25/2010/****************************************************/let( ( libId cellId cdfId )unless( cellId = ddGetObj( LIBRARY CELL ) error( "Could not get cell %s." CELL ) )when( cdfId = cdfGetBaseCellCDF( cellId ) cdfDeleteCDF( cdfId ) )cdfId = cdfCreateBaseCellCDF( cellId ) ;;; Parameters cdfCreateParam( cdfId?name "model"?prompt "Model name" ?defValue "my_ind " ?type "string" ?display "t" ?editable "nil" ?parseAsCEL "yes" )cdfCreateParam( cdfId?name "macro"?prompt "Hspice S model name" ?defValue "my_ind " ?type "string" ?display "nil" ?editable "nil" ?parseAsCEL "yes" )cdfCreateParam( cdfId?name "macroArgumentStyle" ?prompt "macroStyles" ?defValue "hspiceS" ?type "string" ?display "nil" ?editable "nil" ?parseAsCEL "yes"_________________ TSMC Confidential Information 330194 Tsinghua University 01/25/2010 _________________T SMC C o n f i d e n t i a l I n f o r m a t i o n 330194T si n g h u a U n i v e r s i t y 01/25/2010 ) ;;; Simulator Information cdfId->simInfo = list( nil ) cdfId->simInfo->Cdl = '( nilnetlistProcedure tsmcCdlSubcktCall componentName my_indtermOrder (PLUS MINUS ) namePrefix "X"modelName "model" )cdfId->simInfo->auCdl = '( nilnetlistProcedure tsmcCdlSubcktCall componentName my_indtermOrder (PLUS MINUS ) namePrefix "X"modelName "model" )cdfId->simInfo->auLvs = '( nilnetlistProcedure tsmcCdlSubcktCall componentName my_indtermOrder (PLUS MINUS ) namePrefix "X"modelName "model" )cdfId->simInfo->hspiceS = '( nil otherParameters (macro)termOrder (PLUS MINUS ) netlistProcedure ansHspiceSsubcktCall componentName subcircuit macroArguments nil namePrefix "X" )cdfId->simInfo->spectre = '( nil otherParametes (model)termOrder (PLUS MINUS ) termMapping (nil PLUS ":1" MINUS ":2") )_________________ TSMC Confidential Information 330194 Tsinghua University 01/25/2010 _________________T SMC C o n f i d e n t i a l I n f o r m a t i o n 330194T si n g h u a U n i v e r s i t y 01/25/2010 ;;; PropertiescdfId->formInitProc = "" cdfId->doneProc = "" cdfId->buttonFieldWidth = 340 cdfId->fieldHeight = 35 cdfId->fieldWidth = 350 cdfId->promptWidth = 175cdfId->paramLabelSet = "-model n r widthW " cdfId->opPointLabelSet = "cap "cdfId->modelLabelSet = "c " cdfSaveCDF( cdfId ))_________________ TSMC Confidential Information 330194 Tsinghua University 01/25/2010 _________________T S MC C o n f i d e n t i a l I n f o r m a t i o n 330194T si n g h u a U n i v e r s i t y 01/25/20103. Design flowSchematic EntryJust use the customized cells as normal device. Instance customized cells then connect them with other cells in a schematic. The following schematic is a simple example. It will be used as a demo case for explaining design flow.Artist simulation (analog design environment)Include the customized model when doing simulation. The following spectre and spice netlists are generated from Cadence Analog Enviroment, it shows us the connectivity are all correct.Spectre netlist….include "/export/home/jwchen/PDK/project/IP_solution/data/my_ind.scs"// Library name: test// Cell name: test_my_ind // View name: schematic I1 (net6 net9) my_ind_________________ TSMC Confidential Information 330194 Tsinghua University 01/25/2010 _________________T SMC C o n f i d e n t i a l I n f o r m a t i o n 330194T si n g h u a U n i v e r s i t y 01/25/2010R1 (net9 OUT) rnpo1w l=9.36u w=420.0n mf=(1)R0 (IN net6) rnpo1rpo l=8.92u w=2u mf=(1)…Spice netlistXI1 NET6 NET9 MY_INDXR1 NET9 OUT RNPO1W W=420E-9 L=9.36E-6 MF=1XR0 IN NET6 RNPO1RPO W=2E-6 L=8.92E-6 MF=1VirtuosoXL layout driven flowThe layout driven flow can work well. One important thing needs to take care is, the interconnect must connect to pin shape. The following layout is modified to let interconnect connect to pin shape after auto-router.Assura LVS flow for DFII flow and batch modei. Need to assign “blackBoxCell” to let LVS deck know it should not beextracted inside of the customized cell.ii. If the LVS deck has not defined pinLayer before, users have to modifyit. The pinLayer is essential for black box. (Please refer Cadence manual for the detail)_________________ TSMC Confidential Information 330194 Tsinghua University 01/25/2010 _________________T S MC C o n f i d e n t i a l I n f o r m a t i o n 330194T si n g h u a U n i v e r s i t y 01/25/2010extract.rullayerDefs( "df2"…metal2_player = pinLayer( "METAL2") metal3_player = pinLayer( "METAL3")…)layerDefs( "gds2"…metal2_player = pinLayer( 18)metal3_player = pinLayer( 28)…)M2=geomOr(M2 metal2_player)M3=geomOr(M3 metal3_player)…In batch model, the LVS.rsf need to be modified as following_________________ TSMC Confidential Information 330194 Tsinghua University 01/25/2010 _________________T SMC C o n f i d e n t i a l I n f o r m a t i o n330194T si n g h u a U n i v e r s i t y 01/25/2010LVS.rsfavParameters(..?blackBoxCell ("my_ind")..?textPriOnly nil ..)Assura RCX flowUse the same setup method as Assura LVSExtracted viewThe Assura extracted view will use layout view as symbol. The following picture is extracted view and extracted simulation netlist.Calibre LVS flowi. Output a CDL netlist then include LVS sub-circuit. The complete LVSis as below “test_my_ind.cdl”.ii. Insert a line “LVS BOX cell_name” into LVS deckiii.Different pins should not be shorted inside of blackbox, user can use_________________ TSMC Confidential Information 330194 Tsinghua University 01/25/2010 _________________T SMC C o n f i d e n t i a l I n f o r m a t i o n 330194T si n g h u a U n i v e r s i t y 01/25/2010RMDUMMY to let LVS avoid the pin short problem.Test_my_ind.cdl.SUBCKT test_my_ind IN OUT *.PININFO IN:I OUT:I XI1 net6 net9 my_indRR1 net9 OUT 164.914 $[NS]RR0 IN net6 1.30232K $[NR].ENDS.SUBCKT my_ind PLUS MINUS .ENDS LVS deck…LVS BOX my_ind …Calibre RCX flowi. Insert a line “LVS BOX cell_name” into RCX deck ii. Prepare PEX X-Cells file iii. Change extract type to gate level extractionThe Calire RCX extracted netlist is as below, customized cell has been extracted as a sub-circuit..subckt test_my_ind IN OUT *xRR0 IN net6 rnpo1rpo $w=2e-06 $l=8.92e-06xRR1 net9 OUT rnpo1w $w=4.2e-07 $l=9.36e-06xI1 net6 net9 MY_IND c_3 IN 0 2.46362f c_6 net6 0 2.04346f c_7 net9 0 0.674213f c_10 OUT 0 2.94089f *_________________ TSMC Confidential Information 330194 Tsinghua University 01/25/2010 _________________T SMC C o n f i d e n t i a l I n f o r m a t i o n 330194T si n g h u a U n i v e r s i t y 01/25/2010.include test_my_list.TEST_MY_IND.pxi *_________________ TSMC Confidential Information 330194 Tsinghua University 01/25/2010 _________________。

IBM与TSMC在32纳米技术上展开竞争

种应 变工 程手段 ,而这 同我们获得 低功 耗移动产 品的方案

正好相反 ,用户期待的正是成本非常低 的方案 。”

I M的工 程人员介绍 ,由于高k 以在 3 m B 可 2n 工艺 中带

论的却是如果在3 m工艺代 ,I 2r i BM及其伙伴采用先制作栅 来大量好处 ,很多客户将跳过4/ m 5 0n 技术代而直接进入3 4 2

a 工艺 。P t n b m a o  ̄充说 ,3 m t 2n 的工艺流程还考虑到了易于 K a l: “ hrJ 我们的集成方法可以让流程适用于4或4 1 e ̄ 5 @

有 引入 其他 流程 。这与其他高l金属栅 方案有着极大不同 , √

低功耗移动 市场 已成为高速增长的市场分支 , B I M副总 向2 半节点转移的便利性 。 8m a

了获得不错 的性能 ,他们必须采用很薄 的氧化层 ,而这将增

3 m 2a 技术世代如果采用氮氧化技术 ,那么短沟效应将 变得更 加显著 。Seg n t e' e  ̄绍说 : “ 是控制短沟的关键 , 高k

加漏电。”他还指 出,埋置式 S e i 应变技术也会增加成本。 G

IM高k B / 金属栅技术的项 目 经理Mu e hr : “ ks K a 说 我 而使用氮 氧化层 则短 沟效应将 是个大麻 烦 。我们可 以进 行 h e 们在 引入一个重要元素 :高k 料 。坚持使用氧化多 晶方 法 栅长 的缩 减 以及 多 晶硅 的缩 减 ,并 比氮 氧化技术 获得更 好 材

Pt n at 认为T MC o S 是在倒退 ,并指 出 “2a 3 m工艺 中多晶 度 ( ) 以达到lA。更薄的栅氧化层厚度提 高了性能 , T 可 4

氮氧化层将比高k / 金属栅极还要 昂贵”。在3 采用多晶氮 可 以将栅长降低  ̄3 m,同时还可将S A 2m a ] n 10 R M的V 保持在优 氧化层的公 司将不得不转向三次氧化工艺 ,他补充道 : “ 为 化的量级。可以将接触孔靠得更近而不会出现短路的危险。

TSM103_03资料

ELECTRICAL CHARACTERISTICS

Symbol Parameter Total Supply Current, excluding Current in the Voltage Reference VCC+ = 5V, no load Tmin. < Tamb < Tmax. VCC+ = 30V, no load Tmin. < Tamb < Tmax Min. Typ. Max. Unit

Package Part Number TSM103I/AI Temperature Range D -40°C, +105°C •

PIN CONNECTIONS (top view)

Output 1

1

OP1

Inverting Input 1 2 Non-inverting Input 1 3 V - 4 CC

ICC

1.2 0.7 2

mA

2/9

元器件交易网

TSM103/A

OPERATOR 2 (independent op-amp) VCC+ = +5V, VCC = Ground, V o = 1.4V,T amb = 25°C (unless otherwise specified)

3/9

元器件交易网

TSM103/A

OPERATOR 1 (op-amp with non-inverting input connected to the internal Vref) VCC+ = +5V, VCC- = Ground, Tamb = 25°C (unless otherwise specified)

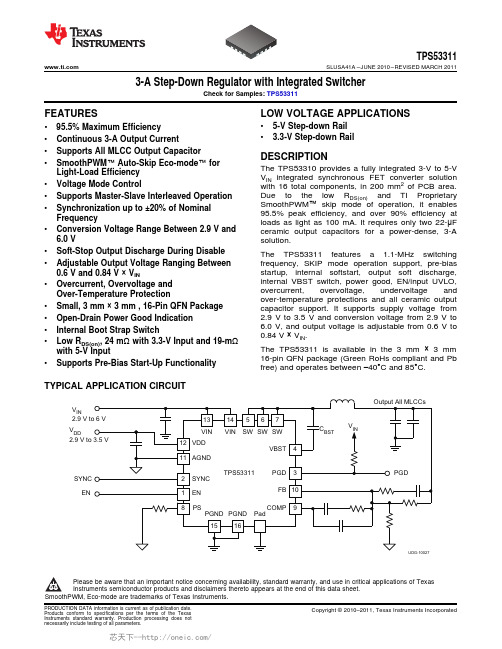

TPS53311RGTT,TPS53311RGTT,TPS53311RGTT,TPS53311RGTR, 规格书,Datasheet 资料