sopc习题练习

形式逻辑练习题(一)

形式逻辑练习题(一)一、填空题(每空1分,共10分)1、与“并非只有外国人当顾问,才能把企业办好”这一负判断等值的判断是。

2、“所有S不是P”这一判断的逻辑常项是:逻辑变项是。

3、任何概念都有两个逻辑特征,即和。

4、当“P→q”为假时,“P∧q”为,“P∨q”为。

5、根据性质判断对当关系进行直接推理,当SOP取值为真时,则SAP取值为、SEP取值为、SIP取值为。

二、单项选择题(每题2分,共20分)1、“无论什么困难都不是不可克服的”和“有些困难是可以克服的”这两个判断之间是(C )。

A、反对关系B、矛盾关系C、差等关系D、下反对关系2、在“杭州人是爱美的”和“王芳是杭州人”这两个判断中,“杭州人”这个概念( A )。

A、前者是集合概念,后者是非集合概念B、前者是非集合概念,后者是集合概念C、前者是集合概念,后者也是集合概念D、前者是非集合概念,后者也是非集合概念3、在性质判断中,判定判断形式的是(D )。

A、主项和谓项B、主项和量项C、谓项和联项D、量项和联项4、在论证中,违反“论题必须明确”的规则,所犯的逻辑错误是()。

A、虚假论据B、预期理由C、论题含混不清D、循环论证5、断定“有S是P”与“所有的S不是P”同假,则()。

A、违反同一律B、违反不矛盾律C、违反排中律D、不违反普通逻辑的基本规律6、下列各组概念依据箭头所示的推演关系,属于正确限制的是()。

A、A、学生→大学生→电大学生B、电大学生→大学生→学生B、B、C、概念→集合概念→非集合概念D、三段论←性质判断←复合判断7、当相容选言判断为假时,则它的肢判断的真假情况是()。

A、P真q假B、P真q真C、P假q真D、P假q 假8、“没有一个学者不认为逻辑作用相当大”。

这个判断的逻辑形式是()。

A、所有S是PB、所有的S不是PC、有S是PD、有S 不是P9、相容选言推理的错误推理形式是()。

A、肯定否定式B、肯定前件式C、否定肯定式D、否定后件式10、以“所有的商品都是劳动产品”为前提进行换位法直接推理,其正确结论是()。

嵌入式复习题

选择题1、嵌入式系统有硬件和软件部分构成,以下(C)不属于嵌入式系统软件.A。

系统软件 B. 驱动 C. ADS软件 D。

嵌入式中间件2、ARM处理器的工作模式有( C )种.A. 5 B。

6 C. 7 D。

83、ARM寄存器组有(D )个寄存器。

A、7B、32C、6D、374、下列CPSR寄存器标志位的作用说法错误的是(D)。

A。

N:负数 B. Z:零 C. C: 进位 D. V: 借位5、ARM复位异常的入口地址是( A ).A、0x00000000B、0x00000008C、0x00000018D、0x000000146、下列描述不属于RISC计算机的特点的是(C)。

A.流水线每周期前进一步. B.更多通用寄存器。

C.指令长度不固定,执行需要多个周期.D.独立的Load和Store指令完成数据在寄存器和外部存储器之间的传输。

7、关于μCOS-II应用,以下说法不正确的是(B )。

A、任务可以有类型说明B、任务可以返回一个数值C、任务可以有形参变量D、任务是一个无限循环8、μCOS-II操作系统不属于( C).A、RTOSB、占先式实时操作系统C、非占先式实时操作系统D、嵌入式实时操作系统9、实时操作系统中,两个任务并发执行,一个任务要等待其合作伙伴发来信息,或建立某个条件后再向前执行,这种制约性合作关系被成为(A).A。

同步 B。

互斥 C。

调度 D. 执行10、每种嵌入式操作系统都有自身的特点以吸引相关用户,下列说法错误的是(D)。

A. 嵌入式Linux提供了完善的网络技术支持;B. μCLinux是专门为没有MMU的ARM芯片开发的;C. μC/OS—Ⅱ操作系统是一种实时操作系统(RTOS);D. WinCE提供完全开放的源代码。

11、存储一个32位数0x12345678到2000H~2003H四个字节单元中,若以大端模式存储,则2000H存储单元的内容为( D).A、0x21B、0x68C、0x65D、0x0212、ARM指令集和Thumb指令集分别是(D )位的。

gmpssop练习题模拟考试及答案(最新)

食品安全管理体系内审员模拟考试题一、名词解释121.关键控制点2.危害3.关键限值4.SSOP二、判断题:(请在你认为正确的括弧内打“√”,不正确的打“×”)。

181.HACCP体系体现预防为主的管理理念。

()2.有些危害需多个关键控制点来控制,有的关键控制点能同时控制多个危害。

()3.食品中发现头发、苍蝇、玻璃、金属碎片等恶性杂质都属于安全危害。

()4.由于高温灭菌能消除细菌危害,因此,如产品最后有高温灭菌工序,此前的工序就不必控制细菌的繁殖和污染。

()5.只要食品品种及其加工工艺相同,其CCP点的数量和位置一定相同。

()6.微生物实验通常用于CCP的监控以及产品的验证和判定。

()7.HACCP体系要求任何贯彻HACCP管理体系的组织必须完全消除食品中存在的一切危害因素。

()8.由于加工用水的卫生状况直接影响所加工食品的安全,因此企业必须将水的卫生控制纳入HACCP计划。

()9.美国有关HACCP法规中规定,制定HACCP计划、重新评估和修改HACCP计划、CCP监控、复审记录等工作必须由经过有效的HACCP培训的人员承担。

()10.美国现行的GMP法规中包含了SSOP应该包含的各个方面,企业制定SSOP计划的法律依据是GMP法规。

()11.HACCP体系所关注的是食品的质量是否合格。

()12.HACCP体系所阐述的纠偏措施即纠正措施。

()13.HACCP体系所阐述的关键控制点即产品生产加工过程中的关键工序。

()14.HACCP体系所规定的流程描述即组织的产品生产工艺流程图。

()15.第三方验证可以作为企业HACCP体系验证的组成部分。

()16.不合格报告没有必要让受审方确认,由审核组长签字确认即可。

()17.审核就是寻找受审方存在的不符合审核准则的证据。

()18.审核过程抽样可以由审核员与受审方协商确定。

()三、选择题(请在你认为对的符号上打“√”,每题只能选一个答案)201.以下计划哪一个不属于HACCP计划的前提计划:()A.培训与教育计划B.员工健康体检计划C.加工设备维修保养计划D.HACCP体系的验证计划P的监控方法包括:()A.温度监测、计时、测定蒸汽压力等B.测定输送带速度、检查产地证明、营养成分分析等C.PH值监测、细菌检验、水活度检测等D.水分含量测定、病原体检验、供应商声明的检查等3.出口食品加工企业实验室应开展的工作:()A.食品接触表面的卫生监测B.成品检验C.HACCP计划和体系的验证D.以上都包括4.建立HACCP验证程序的目的:()A.验证各CCP的监控、记录、纠偏是否正常进行B.确认HACCP计划对安全危害的控制确实有效C.验证HACCP体系是否正常运行D.以上都是5.下列哪项验证活动属于CCP的验证:()A.HACCP计划的重新审核B.运行HACCP计划的效果确认C.关键控制点监控用具/设备的定期校准D.卫生监控计划的实施情况检查6.HACCP体系的官方验证中,现场验证的内容包括:()A.企业是否符合GMP法规B.企业是否有严密的SSOP计划,并有效实施C.HACCP计划及其实施情况D.以上都是7.HACCP计划中的显著性危害的特点体现在:()A.危害发生的可能性、危害的严重性、GMP/SSOP无法控制B.危害的特殊性、GMP/SSOP无法控制C.危害的严重性、危害发生的可能性、危害的不变性D.以上都不对8.下列哪些措施是进行纠偏行动时必须采取的:()A.消除使CL产生偏离的因素、对偏离期间加工的产品进行重新评价和处理B.对偏离期间加工的产品进行重新评价和处理、停产整顿C.对监控人员进行处罚、对职工进行再培训D.维修设备、隔离产品9.HACCP记录至少应包括:()A.CCP监控记录、卫生监控记录、验证记录B.CCP纠偏记录、原料验收记录、CCP监控记录C.CCP监控记录、验证记录、纠偏记录D.纠偏记录、卫生监控记录、CCP监控记录10.不属于危害分析时考虑的因素是:()A.原料的养殖、种植环境B.食品的组成(配方)C.实验室的检测能力D.加工工序的温度三、简答题301.简述HACCP小组的组成及其主要职能。

ARM嵌入式系统开发与应用课后题答案与习题

课后题答案:第一章1.写出下列英文缩写的英文原文及中文含义。

RAM随机存储器 DRAM动态随机存储器 ROM只读存储器PROM可编程只读存储器 EPROM可插除可编程只读存储器 CANCAN总线RTOS实时操作系统 SOPC片上可编程系统 ICE硬件调试器 FI快速终端请求EEPROM电可插除可编程只读存储器 API应用程序接 DMA直接内存存取RISC精简指令集计算机 SPI串行万维指令 MMU存储管理单元UART异步接受发送装置 ARM先进RISC存储器 SWI软件终端指令2、什么是嵌入式系统? P3嵌入式系统是用于检测、控制、辅助、操作机械设备的装置。

以应用为中心,一计算机技术为基础,软硬件可裁剪,适应应用系统对功能、可靠性、成本、体积和功耗等严格要求的专用计算机系统。

3、是比较嵌入式系统与通用PC的区别。

P3(1)嵌入式系统是专用的计算机系统,而PC是通用的计算机系统。

(2)技术要求不同,通用PC追求高速、海量的数据运算;嵌入式要求对象体系的智能化控制。

(3)发展方向不同,PC追求总线速度的不断提升,存储容量不断扩大;嵌入式追求特定对象系统的智能性,嵌入式,专用性。

4、嵌入式体统有哪些部分组成?简单说明各部分的功能与作用(1)硬件层是整个核心控制模块(由嵌入式微处理器、存储系统、通信模块、人机接口、其他I/O 接口以及电源组成),嵌入式系统的硬件层以嵌入式微处理器为核心,在嵌入式微处理器基础上增加电源电路、时钟电路、和存储器电路(RAM和ROM等),这就构成了一个嵌入式核心控制模块,操作系统和应用程序都可以固化在ROM中。

(2)中间层把系统软件与底层硬件部分隔离,使得系统的底层设备驱动程序与硬件无关。

一般包括硬件抽象层(Hardware Abstract Layer,HAL)和板级支持包(Board Support Package,BSP)。

(3)软件层由实时操作系统(Real Time Operating System,RTOS)、文件系统、图形用户接口(Graphical User Interfaces,GUI)、网络组件组成。

最新SOPC试题资料

习题练习一、填空题1、Altrea公司于21世纪初推出SOPC技术,其SOPC称为___可编程片上系统__________。

2、Altera公司的SOPC集成了_硬核______或软核CPU、DSP、锁相环(PLL)、_存储器_____、I/O接口及可编程逻辑,SOPC开发工具将软、____硬件___的设计结合起来,为用户提供很好的开发环境。

3、SOPC的设计包括,设计准备(方案论证,系统设计,器件选择)、设计输入(图文、文本、存储器、波形灯TOP-DOWN)、设计编译(分析综合、适配、编程、时序分析)、设计仿真(功能仿真、时序仿真)、器件编程(将设计处理的编程数据文件下载到pld),_硬件测试(在开发系统中对设计的系统进行测试)等设计流程。

4、用FPGA实现DSP并不是指用FPGA来构造一个_DSP____芯片,是直接用__FPGA_______硬件来实现DSP功能。

5、Altera公司的DSP Builder可以帮助开发者完成基于FPGA的DSP设计,自动完成大部分的设计过程和仿真,直至把设计文件下载至___FPGA______中。

6、DSP Builder将用户设计的DSP模块转换成__硬件_____描述语言(HDL),最终在FPGA上实现。

二、单项选择题1、SOPC Builder是Altera公司推出的一种可加快在PLD内实现___1_____嵌入式处理器及其相关接口的设计工具。

(1)Nios II;(2)ARM9;(3)Intel;(4)ARM7。

2、Nios II是一个用户可以自行定制的CPU,用户可以增加新的外设,增加新的指令,分配外设的地址等。

Nios II的硬件开发就是由用户定制合适的___4_____。

(1)处理器芯片;(2)输入输出设备;(3)HAL及API;(4)CPU和外设。

3、SOPC Builder界面分成三个部分,界面左边是组件选择栏,用树型结构列出了SOPC Builder的组件;右边空白处用于加入用户定制___1_____;下方是提示栏,用于显示SOPC Builder的提示信息和警告错误信息。

《法律逻辑》习题

《法律逻辑》习题一、选择题1.在性质判断中,决定其逻辑形式和逻辑性质的是()A.主项和谓项B.主项和联项C.量项和谓项D.量项和联项2.若两个性质判断的变项完全相同,而常项完全不同,则这两个判断之间具有()A.等值关系B.反对关系C.矛盾关系D.差等(蕴涵)关系3.如果两个性质判断的主项、谓项、联项都相同,而量项不同,则这两个判断之间具有()A.等值关系B.反对关系C.矛盾关系D.差等(蕴涵)关系4.“这个班没有同学是少数民族人”,这一判断的形式可以写作()A.所有S是PB.所有S不是PC.有S是PD.有S不是P5.“没有人是完人”这一判断的主谓项的周延情况是()A.主谓项都周延B.主谓项都不周延C.主项周延谓项不周延D.主项不周延谓项周延6.已知“有S不是P”为真,可以必然推出()A.“所有S是P”为假B.“有S是P”为真C.“所有S不是P”为假D.“所有S不是P”为真7、“正当防卫不是犯罪行为”这个判断的主、谓周延情况是()。

A. 主、谓项都周延B. 主、谓项都不周延C. 主项周延,谓项不周延D.主项不周延,谓项周延8、与"并非有些贪污罪不是故意犯罪"等值的判断是()。

A.所有贪污罪都是故意犯罪B. 所有贪污罪都不是故意犯罪C. 有些贪污罪是故意犯罪D. 有些贪污罪不是故意犯罪9、"并非某甲或某乙有罪"等值的判断是()。

A. 某甲和某乙都有罪B. 某甲和某乙都无罪C. 某甲或某乙有罪D. 某甲或某乙无罪10、若"某甲必然不是凶手"为真,则()为真。

A. 某甲必然是凶手B. 某甲可能是凶手C. 某甲可能不是凶手D. 某甲不必然不是凶手11、下列各组概念按箭头所示方向,属于正确概括的是()。

A、法院→刑事审判庭→法官B、法官→刑事审判庭→法院C、司法机关→法院→人民法院D、人民法院→法院→司法机关12、“所有拾金不昧的人都是有道德的人,老张是有道德的人,所以,老张是拾金不昧的人。

SOPC助理工程师认证考试试题及答案

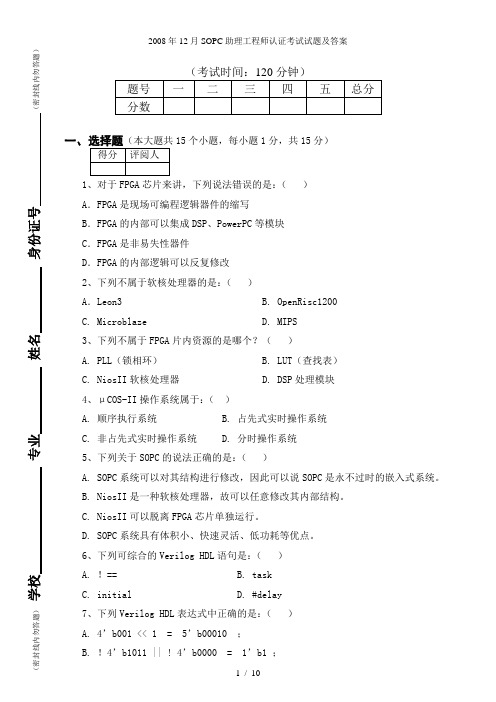

2008年12月SOPC 助理工程师认证考试试题及答案15个小题,每小题1分,共15分) 1、对于FPGA 芯片来讲,下列说法错误的是:( ) A .FPGA 是现场可编程逻辑器件的缩写 B .FPGA 的内部可以集成DSP 、PowerPC 等模块 C .FPGA 是非易失性器件 D .FPGA 的内部逻辑可以反复修改 2、下列不属于软核处理器的是:( ) A .Leon3 B. OpenRisc1200 C. Microblaze D. MIPS 3、下列不属于FPGA 片内资源的是哪个?( ) A. PLL (锁相环) B. LUT (查找表) C. NiosII 软核处理器 D. DSP 处理模块 4、μCOS-II 操作系统属于:( ) A. 顺序执行系统 B. 占先式实时操作系统 C. 非占先式实时操作系统 D. 分时操作系统 5、下列关于SOPC 的说法正确的是:( ) A. SOPC 系统可以对其结构进行修改,因此可以说SOPC 是永不过时的嵌入式系统。

B. NiosII 是一种软核处理器,故可以任意修改其内部结构。

C. NiosII 可以脱离FPGA 芯片单独运行。

D. SOPC 系统具有体积小、快速灵活、低功耗等优点。

6、下列可综合的Verilog HDL 语句是:( ) A. !== B. task C. initial D. #delay7、下列Verilog HDL 表达式中正确的是:( )A. 4’b001 << 1 = 5’b00010 ;B. !4’b1011 || ! 4’b0000 = 1’b1 ;C. 4’b1010 & 4’b1101 = 1’b1 ;D. 4’b1011 && 4’b0100 = 4’b1111 ;8、下列选项中哪个不是嵌入式系统软硬件划分的原则。

()A. 系统优化原则B. 资源利用率原则C. 性能原则D. 性价比原则9、NiosII的系统中SDRAM的IP核时钟与系统全局时钟相差多少度?()A. -60度B. -50度C. -70度D. -90度10、下列描述可以在FPGA中稳定运行的是:()A. 状态机编码中采用二进制编码方式B. 在时钟上升沿到来时 A的值由“1001”变为“0110”C. 大量采用异步电路设计D. 采用时钟的正负沿调整采样11、下列关于Verilog HDL模块连接正确的是:()Module1 Module2(.a (code1 ) ,.clk (clk) ,.rst (rst ) ,.b ( k1 )) ;A. a是顶层模块,code1是底层模块。

(完整word版)年6月SOPC助理工程师理论考试试题1.0

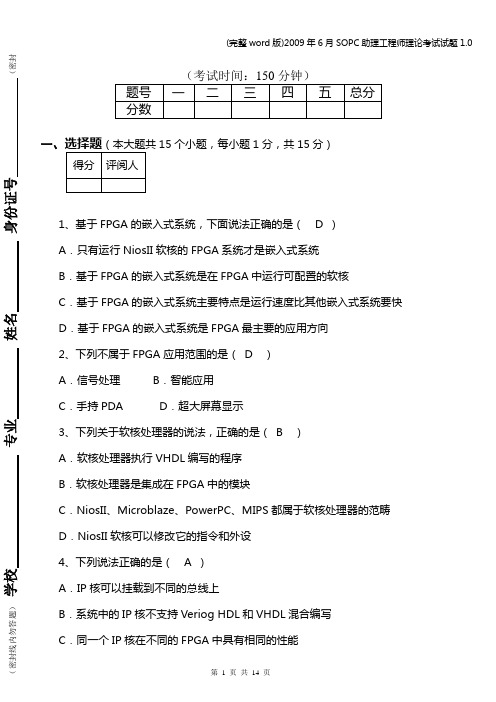

15个小题,每小题1分,共15分) 1、基于FPGA 的嵌入式系统,下面说法正确的是( D ) A .只有运行NiosII 软核的FPGA 系统才是嵌入式系统 B .基于FPGA 的嵌入式系统是在FPGA 中运行可配置的软核 C .基于FPGA 的嵌入式系统主要特点是运行速度比其他嵌入式系统要快 D .基于FPGA 的嵌入式系统是FPGA 最主要的应用方向 2、下列不属于FPGA 应用范围的是( D ) A .信号处理 B .智能应用 C .手持PDA D .超大屏幕显示 3、下列关于软核处理器的说法,正确的是( B ) A .软核处理器执行VHDL 编写的程序 B .软核处理器是集成在FPGA 中的模块 C .NiosII 、Microblaze 、PowerPC 、MIPS 都属于软核处理器的范畴 D .NiosII 软核可以修改它的指令和外设 4、下列说法正确的是( A ) A .IP 核可以挂载到不同的总线上B .系统中的IP 核不支持Veriog HDL 和VHDL 混合编写C .同一个IP 核在不同的FPGA 中具有相同的性能D.嵌入式软核处理器并不属于IP核的范畴*5、关于SOPC的说法,错误的是(B )A.SOPC的系统中至少包含一个NiosII软核B.SOPC技术包含了嵌入式设计的全部,除了硬件PCB外,还包括处理器和实时多任务操作系统(RTOS)C.SOPC可以体现软硬件协同设计技术D.如果FPGA中集成了硬核处理器,无论是否使用,系统都属于SOPC系统6、下列不属于FPGA片内资源的是(A )A.高速串行收发器B.PLL(数字锁相环)C.RAM D.FIFO(先进先出)7、下面哪项不属于NiosII软核的可定制性(D )A.可以修改基于NiosII的IP核B.提高或降低工作频率C.增加或取消MMU(内存管理单元)D.自定义NiosII指令8、关于FPGA的配置问题下列说法的正确的是(A )A.EPCS16的容量是16MbB.FPGA仅支持EPCS配置C.FPGA的配置优先级最高的是EPCSD.EPCS配置FPGA属于PS(被动)方式9、关于NiosII软核启动过程,下列说法错误的是( D )A.NiosII软核的启动过程主要分为FPGA器件的配置和NiosII程序的加载B.CFI Flash可以保存FPGA的配置文件、NiosII程序和其他文件数据C.FPGA配置文件(.sof)和NiosII程序(.elf)都可以保存在EPCS中D.使用CFI Flash做为NiosII启动的器件时,FPGA把配置数据从CFI Flash读出并加载,然后执行Bootloader把保存的NiosII程序复制SDRAM执行10、下列可以在FPGA中稳定运行的是(B )A.在设计中同时存在大量同步和异步设计B.状态机编码采用二进制码和独热码混合形式C.使用很多已经验证好的IP核,但没有做整体的仿真D.有的模块采用时钟上升沿,有的模块采用时钟下降沿11、uC/OS-II的任务调度策略是( A )A.哪个任务的优先级高就先执行哪个任务B.高优先级的任务会被低优先级的任务抢占C.各自轮流执行一段时间再让出CPUD.如果某个任务一直得不到CPU资源,就会进入等待状态12、在FPGA设计中不属于软件硬件协同设计的是( C )A.C2H(C to Hardware)硬件加速编译器B.难于用软件实现的部分功能用硬件实现C.在C程序中使用自定义外设的函数D.根据顶层设计要求,合理划分软硬件结构13、在uC/OS-II系统中不属于信号量用途的是(D )A.共享资源的控制B.用来表示一个事件的发生C.实现两个任务之间信息的传递D.实现两个任务的同步14、关于SystemC和SystemVerilog的说法正确的是(C )A.SystemC适合顶层建模,SystemVerilog适合验证B.SystemVerilog适合顶层建模,SystemC适合验证C.SystemVerilog是Verilog的升级版本D.SystemC可以直接转换为RTL代码15、下列关于uClinux的说法正确的是(D )A.uClinux是在linux的基础上裁剪了内核和应用程序库。

片上可编程系统复习

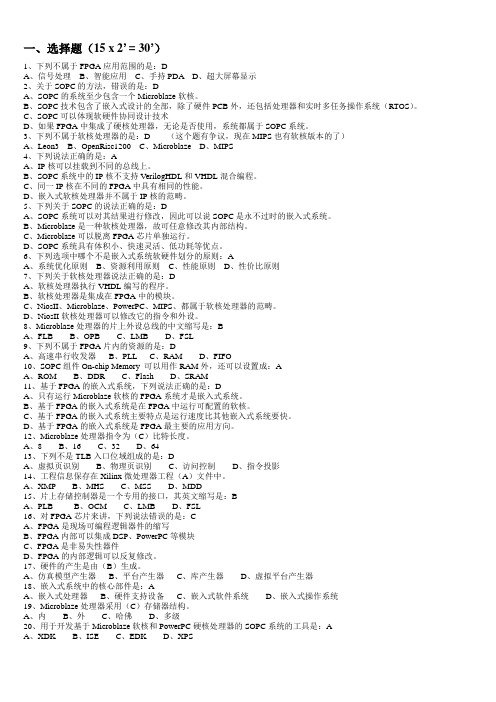

一、选择题(15 x 2’ = 30’)1、下列不属于FPGA应用范围的是:DA、信号处理B、智能应用C、手持PDAD、超大屏幕显示2、关于SOPC的方法,错误的是:DA、SOPC的系统至少包含一个Microblaze软核。

B、SOPC技术包含了嵌入式设计的全部,除了硬件PCB外,还包括处理器和实时多任务操作系统(RTOS)。

C、SOPC可以体现软硬件协同设计技术D、如果FPGA中集成了硬核处理器,无论是否使用,系统都属于SOPC系统。

3、下列不属于软核处理器的是:D (这个题有争议,现在MIPS也有软核版本的了)A、Leon3B、OpenRisc1200C、MicroblazeD、MIPS4、下列说法正确的是:AA、IP核可以挂载到不同的总线上。

B、SOPC系统中的IP核不支持VerilogHDL和VHDL混合编程。

C、同一IP核在不同的FPGA中具有相同的性能。

D、嵌入式软核处理器并不属于IP核的范畴。

5、下列关于SOPC的说法正确的是:DA、SOPC系统可以对其结果进行修改,因此可以说SOPC是永不过时的嵌入式系统。

B、Microblaze是一种软核处理器,故可任意修改其内部结构。

C、Microblaze可以脱离FPGA芯片单独运行。

D、SOPC系统具有体积小、快速灵活、低功耗等优点。

6、下列选项中哪个不是嵌入式系统软硬件划分的原则:AA、系统优化原则B、资源利用原则C、性能原则D、性价比原则7、下列关于软核处理器说法正确的是:DA、软核处理器执行VHDL编写的程序。

B、软核处理器是集成在FPGA中的模块。

C、NiosII、Microblaze、PowerPC、MIPS、都属于软核处理器的范畴。

D、NiosII软核处理器可以修改它的指令和外设。

8、Microblaze处理器的片上外设总线的中文缩写是:BA、FLBB、OPBC、LMBD、FSL9、下列不属于FPGA片内的资源的是:DA、高速串行收发器B、PLLC、RAMD、FIFO10、SOPC组件On-chip Memory 可以用作RAM外,还可以设置成:AA、ROMB、DDRC、FlashD、SRAM11、基于FPGA的嵌入式系统,下列说法正确的是:DA、只有运行Microblaze软核的FPGA系统才是嵌入式系统。

SOPC试题

习题练习一、填空题1、Altrea 公司于21 世纪初推出SOPC 技术,其SOPC 称为可编程片上系统。

2、Altera 公司的SOPC 集成了_硬核或软核CPU 、DSP 、锁相环(PLL )、_存储器_ 、I/O 接口及可编程逻辑,SOPC 开发工具将软、硬件的设计结合起来,为用户提供很好的开发环境。

3、SOPC 的设计包括,设计准备(方案论证,系统设计,器件选择)、设计输入(图文、文本、存储器、波形灯TOP-DOWN)、设计编译(分析综合、适配、编程、时序分析)、设计仿真(功能仿真、时序仿真)、器件编程(将设计处理的编程数据文件下载到pld),_硬件测试(在开发系统中对设计的系统进行测试)等设计流程。

4 、用FPGA 实现DSP 并不是指用FPGA 来构造一个_DSP_ 芯片,是直接用__FPGA_ 硬件来实现DSP 功能。

5、Altera 公司的DSP Builder 可以帮助开发者完成基于FPGA 的DSP 设计,自动完成大部分的设计过程和仿真,直至把设计文件下载至FPGA _ 中。

6、DSP B uilder 将用户设计的DSP 模块转换成__硬件描述语言(HDL),最终在FPGA 上实现。

二、单项选择题1、SOPC Builder 是Altera 公司推出的一种可加快在PLD 内实现 1 嵌入式处理器及其相关接口的设计工具。

(1)Nios II;(2)ARM9 ;(3)Intel ;(4)ARM7。

2、Nios II 是一个用户可以自行定制的CPU ,用户可以增加新的外设,增加新的指令,分配外设的地址等。

Nios II 的硬件开发就是由用户定制合适的 4 。

(1)处理器芯片;(2)输入输出设备;(3)HAL 及API;(4)CPU 和外设。

3、SOPC Builder 界面分成三个部分,界面左边是组件选择栏,用树型结构列出了SOPC Builder 的组件;右边空白处用于加入用户定制 1 ;下方是提示栏,用于显示SOPC Builder 的提示信息和警告错误信息。

基于fpga的嵌入式系统设计——复习题

基于fpga的嵌入式系统设计——复习题————————————————————————————————作者: ————————————————————————————————日期:《基于fpga的嵌入式系统设计》复习题1、名词概念解释:(1)ASIC,FPGA,SOC,SOPC,NIOS II,I/O ,IP ;(2)VHDL,verilog HDL,HDL,EDA ;(3)功能仿真,后仿真,设计综合,设计验证;(4)嵌入式系统的定义:以应用为中心、以计算机技术为基础、软硬件可裁剪、适应应用系统对功能、可靠性、成本、体积、功耗等严格要求的专用计算机系统。

(5)嵌入式系统的组成:嵌入式系统主要由嵌入式处理器、外围设备、嵌入式操作系统及应用软件等组成,它是集软硬件于一体的可独立工作的“器件”。

其中:嵌入式处理器是嵌入式系统的核心部件,具有小型化、高效率、高可靠性、高集成度等特点。

外围设备是嵌入式系统中用于完成存储、通信、调试、显示等辅助功能的部件。

2、填空题(1)NiosII处理器有三种运行模式: ___________ ,___________ ,_____________。

(2)CycloneII FPGA支持串行配置器件的isp编程,该特性是通过_____________利用JTAG接口实现的。

(3)在SOPCBuilder中,复位地址的偏移量是________,异常地址的偏移量是________。

(4)在NiosII的多处理器系统中,最常用的共享资源是____________。

(5)根据Flash是否支持处理器的直接读操作,NiosII处理的bootloader分成两种模式:________________bootloader、________________ bootloader。

(6)用uC/OS-II操作系统实现以太网与轻量IP功能的时候,以太网的中断号至少是____________。

SOPC期末考试-整理

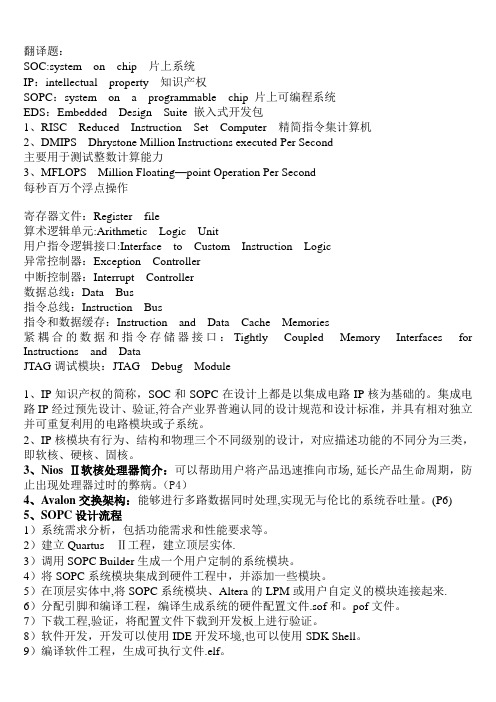

翻译题:SOC:system on chip 片上系统IP:intellectual property 知识产权SOPC:system on a programmable chip 片上可编程系统EDS:Embedded Design Suite 嵌入式开发包1、RISC Reduced Instruction Set Computer 精简指令集计算机2、DMIPS Dhrystone Million Instructions executed Per Second主要用于测试整数计算能力3、MFLOPS Million Floating—point Operation Per Second每秒百万个浮点操作寄存器文件:Register file算术逻辑单元:Arithmetic Logic Unit用户指令逻辑接口:Interface to Custom Instruction Logic异常控制器:Exception Controller中断控制器:Interrupt Controller数据总线:Data Bus指令总线:Instruction Bus指令和数据缓存:Instruction and Data Cache Memories紧耦合的数据和指令存储器接口:Tightly Coupled Memory Interfaces for Instructions and DataJTAG调试模块:JTAG Debug Module1、IP知识产权的简称,SOC和SOPC在设计上都是以集成电路IP核为基础的。

集成电路IP经过预先设计、验证,符合产业界普遍认同的设计规范和设计标准,并具有相对独立并可重复利用的电路模块或子系统。

2、IP核模块有行为、结构和物理三个不同级别的设计,对应描述功能的不同分为三类,即软核、硬核、固核。

3、NiosⅡ软核处理器简介:可以帮助用户将产品迅速推向市场,延长产品生命周期,防止出现处理器过时的弊病。

sopc考试复习

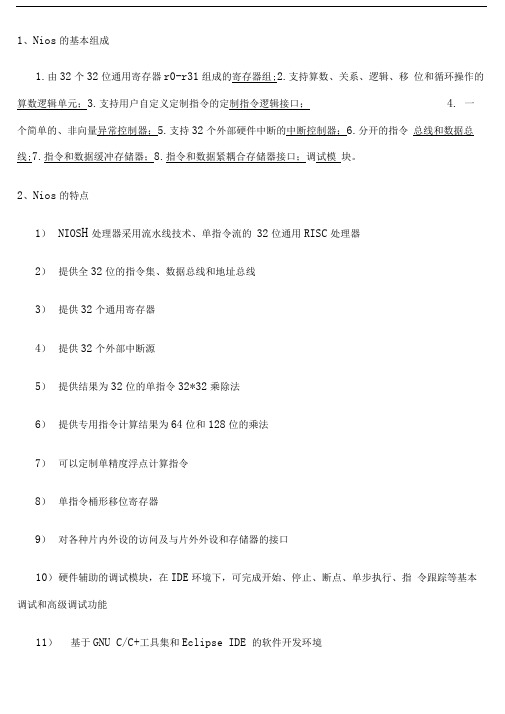

1、Nios的基本组成1.由32个32位通用寄存器r0-r31组成的寄存器组;2.支持算数、关系、逻辑、移位和循环操作的算数逻辑单元;3.支持用户自定义定制指令的定制指令逻辑接口;4. 一个简单的、非向量异常控制器;5.支持32个外部硬件中断的中断控制器;6.分开的指令总线和数据总线;7.指令和数据缓冲存储器;8.指令和数据紧耦合存储器接口;调试模块。

2、Nios的特点1)NIOS H处理器采用流水线技术、单指令流的32位通用RISC处理器2)提供全32位的指令集、数据总线和地址总线3)提供32个通用寄存器4)提供32个外部中断源5)提供结果为32位的单指令32*32乘除法6)提供专用指令计算结果为64位和128位的乘法7)可以定制单精度浮点计算指令8)单指令桶形移位寄存器9)对各种片内外设的访问及与片外外设和存储器的接口10)硬件辅助的调试模块,在IDE环境下,可完成开始、停止、断点、单步执行、指令跟踪等基本调试和高级调试功能11)基于GNU C/C+工具集和Eclipse IDE 的软件开发环境12) A LTERA 公司的SignalTap H 逻辑分析仪,实现对指令、数据、FPGA 设计中的逻辑信号进行实时分析13) 所有NISO H 处理器均兼容的指令系统 14) 高达218DMIPS 的性能3、什么是SoPC 英文全称是什么列举3种构成SoPQ 的方案System On Programmable Chip ,可编程的片上系统。

是 Altera 公司提出来的一种灵活、高效的SOC 解决方案。

SOPC 各处理器、存储器、I/O 、LVDS CDF 等系统设计需要 的功能模块集成到一个可编程器件上,构成一个可编程的片上系统。

现今 SOP (可以认为是基于FPGA 解决方案的SOC方案:基于FPGA 嵌入IP 硬核的SOP (系统;基于FPGA 嵌入IP 软核的SOPC 系统; 基于HardCopy 技术的SOP (系统4、Nios 的三种操作模式管理模式:除了不能访问与调试有关的寄存器(bt 、ba 和bstatus )夕卜,无其它访问 限制。

形式逻辑练习题2答案

形式逻辑练习题2答案一、单项选择题。

1、“群众是真正的英雄”一句话中,“群众”是A、单独、集合概念B、单独、非集合概念C、普遍、集合概念D、普遍、非集合概念2、“美国”和“纽约”这两个概念的外延关系是A、真包含B、真包含于C、交叉D、全异3、在S与P可能具有的五种外延关系中,下列命题形式真假情况为二真三假的是A、SAPB、SEPC、SIPD、SOP4、若两个性质命题变项都相同,而常项都不同,则这两个性质命题对当关系是A、差等关系B、反对关系C、矛盾关系D、下反对关系5、“《藤野先生》”和“《朝花夕拾》”的外延关系是A、真包含于B、真包含C、交叉D、全异6、乒乓球比赛和象棋比赛中的“输”和“赢”这两对概念的外延关系分别是A、都是矛盾关系B、前者是矛盾关系,后者是反对关系C、都是反对关系D、前者是反对关系,后者是矛盾关系7、如果有的A是B,有的A不是B,那么A与B的外延关系是A、交叉B、真包含于C、真包含D、真包含或交叉8、定义过宽中的“定义项”和“被定义项”的外延关系是A、全同B、真包含于C、真包含D、交叉9、性质命题逻辑形式之间的区别,取决于A、量项和谓项B、主项和谓项C、联项和量项D、主项和联项10、SOP命题的“主项”和“谓项”的周延情况分别是A、周延、周延B、周延、不周延C、不周延、周延D、不周延、不周延11、如果S真包含于P,则下列命题均为真的是A、SAP、SIPB、SEP、SOPC、SIP、SOPD、SEP、SIP12、具有下反对关系的两个性质命题之间的关系是A、可同真、可同假B、可同真、不可同假C、不可同真、可同假D、不可同真、不可同假13、下列推理形式正确的是A、SAP——PASB、SOP——POSC、SIP——POSD、SOP——PIS14、“鲸不是鱼,因为鲸不是用鳃呼吸的,而鱼是用鳃呼吸的。

”这一三段论的格式是A、第二格EAE式B、第三格EAE式C、第二格AEE式D、第三格AEE式15、下列为有效的三段论格式的是A、第一格AEE式B、第二格AI I式C、第三格AAA式D、第四格IAI式16、概念外延间的交叉关系的关系性质是A、对称、传递关系B、非对称、非传递关系C、对称、非传递关系D、反对称、反传递关系17、已知POS真,SEP假,则S与P外延间关系的全部可能性是A、真包含、全异B、交叉、全异C、真包含、交叉D、真包含于、交叉18、如果一个由两个选言肢组成的不相容的选言命题是真的,那么它的两个选言肢A、可同真、可同假B、可同真、不可同假C、不可同真、可同假D、不可同真、不可同假19、两个假言命题的逻辑形式相同,是指相同。

消化SOP第二阶段测评练习题

消化SOP第二阶段测评练习题您的姓名: [填空题] *_________________________________岗位: [填空题] *_________________________________1. 明月司训看___了、___好了、______了,马上就___!______加______!要不就______,干就_________! [填空题] *空1答案:准空2答案:想空3答案:决策空4答案:干空5答案:苦干空6答案:巧干空7答案:不干空8答案:干一流答案解析:明月司训看准了、想好了、决策了,马上就干!苦干加巧干!要不就不干,干就干一流!2. 明月追求______无______ ______无______ [填空题] *空1答案:改善空2答案:止境空3答案:创新空4答案:穷期答案解析:明月追求改善无止境创新无穷期3. 明月集团各系统“八荣八耻”通用部分以______明月为荣,以______明月为耻;以______担当为荣,以______诿过为耻;以______协作为荣,以______利已为耻;以______价值为荣,以______无为为耻。

[填空题] *空1答案:热爱空2答案:危害空3答案:忠诚空4答案:揽功空5答案:团结空6答案:自由空7答案:创造空8答案:碌碌答案解析:明月集团各系统“八荣八耻”通用部分以热爱明月为荣,以危害明月为耻;以忠诚担当为荣,以揽功诿过为耻;以团结协作为荣,以自由利已为耻;以创造价值为荣,以碌碌无为为耻。

4. 生产制造系统以______生产为荣,以______事故为耻;以______求精为荣,以______进取为耻;以______降耗为荣,以______滴漏为耻;以______交货为荣,以______低效为耻。

[填空题] *空1答案:安全空2答案:违章空3答案:精益空4答案:不思空5答案:节能空6答案:跑冒空7答案:按时空8答案:延迟答案解析:生产制造系统以安全生产为荣,以违章事故为耻;以精益求精为荣,以不思进取为耻;以节能降耗为荣,以跑冒滴漏为耻;以按时交货为荣,以延迟低效为耻。

EDA复习题练习

EDA复习题练习EDA练习一、名词解释及回答问题:写出下列缩写的中文(或者英文)含义:1.VHDL2.FPGA3.RTL4.SOPC5.EDA6.CPLD7.HDL8.LUT9.ASIC10.SOC11.JTAG12.IP13.LPM14.EDA与传统设计方法的区别?15.硬件描述语言编译综合后的结果是什么?16.时序仿真与功能仿真的区别?二、程序填空:(仅以一例说明题型)下面程序是参数可定制带计数使能异步复位计数器的VHDL描述,试补充完整。

--N-bitUpCounterwithLoad,CountEnable,and--AynchronouReetlibraryieee;ueIEEE.td_logic_1164.all;ueIEEE.______ __________.all;ueIEEE.td_logic_arith.all;entitycounter_niarchite cturebehaveof_______________iignalcount:td_logic_vector(width-1downto0);beginproce(clk,rt)beginifrt='1'thencount<=____________ ___;――清零elif_______________________then――边沿检测ifload='1'thencount<=data;count<=count+1;___________en='1'thenge neric(width:integer:=8);port(data:intd_logic_vector(width-1downto0);load,en,clk,rt:______td_logic;q:outtd_logic_vector(___ __________downto0));endcounter_n;_____________;endif;endproce;__ ______________endbehave;三、程序改错:(仅以一例说明题型)23456789LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;ENTITYCNT10ISPORT(CLK:INSTD_LOGIC;Q:OUTSTD_LOGIC_VECTOR(3DOWNTO0));ENDCNT10;ARCHITECTUREbhvOFCNT10ISSIGNALQ1:STD_LOGIC_VECTOR(3DOWNTO0);10BEGIN11PROCESS(CLK)BEGIN12IFRISING_EDGE(CLK)begin13IFQ1<9THEN14Q1<=Q1+1;15ELSE16Q1<=(OTHERS=>'0');17ENDIF;18ENDIF;19ENDPROCESS;20Q<=Q1;21E NDbhv;1.在MA某+PluII中编译时,提示的第一条错误为:Error:Line12:Filee:\\mywork\\tet\\cnt10.vhd:VHDLynta某error:IftatementmuthaveTHEN,butfoundBEGINintead指出并修改相应行的程序(如果是缺少语句请指出大致的行数):错误1行号:程序改为:错误2行号:程序改为:2.若编译时出现如下错误,请分析原因。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

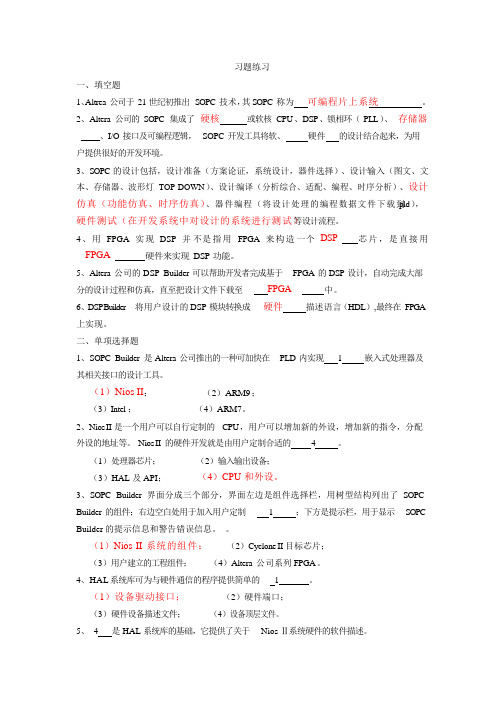

习题练习一、填空题1、Altrea公司于21世纪初推出SOPC技术,其SOPC称为___可编程片上系统__________。

2、Altera公司的SOPC集成了_硬核______或软核CPU、DSP、锁相环(PLL)、_存储器_____、I/O接口及可编程逻辑,SOPC开发工具将软、____硬件___的设计结合起来,为用户提供很好的开发环境。

3、SOPC的设计包括,设计准备(方案论证,系统设计,器件选择)、设计输入(图文、文本、存储器、波形灯TOP-DOWN)、设计编译(分析综合、适配、编程、时序分析)、设计仿真(功能仿真、时序仿真)、器件编程(将设计处理的编程数据文件下载到pld),_硬件测试(在开发系统中对设计的系统进行测试)等设计流程。

4、用FPGA实现DSP并不是指用FPGA来构造一个_DSP____芯片,是直接用__FPGA_______硬件来实现DSP功能。

5、Altera公司的DSP Builder可以帮助开发者完成基于FPGA的DSP设计,自动完成大部分的设计过程和仿真,直至把设计文件下载至___FPGA ______中。

6、DSP Builder将用户设计的DSP模块转换成__硬件_____描述语言(HDL),最终在FPGA 上实现。

二、单项选择题1、SOPC Builder是Altera公司推出的一种可加快在PLD内实现___1_____嵌入式处理器及其相关接口的设计工具。

(1)Nios II;(2)ARM9;(3)Intel;(4)ARM7。

2、Nios II是一个用户可以自行定制的CPU,用户可以增加新的外设,增加新的指令,分配外设的地址等。

Nios II的硬件开发就是由用户定制合适的___4_____。

(1)处理器芯片;(2)输入输出设备;(3)HAL及API;(4)CPU和外设。

3、SOPC Builder界面分成三个部分,界面左边是组件选择栏,用树型结构列出了SOPC Builder的组件;右边空白处用于加入用户定制___1_____;下方是提示栏,用于显示SOPC Builder的提示信息和警告错误信息。

(1)Nios II系统的组件;(2)Cyclone II目标芯片;(3)用户建立的工程组件;(4)Altera公司系列FPGA。

4、HAL系统库可为与硬件通信的程序提供简单的__1______。

(1)设备驱动接口;(2)硬件端口;(3)硬件设备描述文件;(4)设备顶层文件。

5、_4___是HAL系统库的基础,它提供了关于Nios Ⅱ系统硬件的软件描述。

(1)System.h文件;(2)NiosⅡIDE;(3)stdio.h;(4)ANSI C。

6、系统标识system ID是SOPC中的一个___1_____。

(1)简单只读组件;(2)IP外围设备;(3)运行程序的ID号;(4)FPGA中的硬件电路。

7、__2___调试方式面向对象,通过直观的软件界面上按钮来完成调试的各种操作。

(1)IDE;(2)SOPC Builder;(3)Quartus II;(4)SDK。

8、通用___1_____ PIO包括输入、输出和双向三态IO。

(1)输入输出端口;(2)可编程接口;(3)外围设备接口;(4)可编程外围设备接口。

9、SOPC Builder允许用户修改已经存在的设计,为其添加新的___4_____。

(1)用户程序;(2)IP组件;(3)Nios II系统的组件(4)设备和功能。

10、Nios II的硬件开发就是由用户定制合适的___4_____。

(1)FPGA器件;(2)FPGA目标芯片;(3)IP软、硬核;(4)CPU和外设。

11、___1____是Altera公司推出的一种可加快在PLD内实现Nios II嵌入式处理器及其相关接口的设计工具。

(1)SOPC Builder;(2)DSP Builde;(3)Nios II IDE;(4)Quartus II。

12、___4_____是一个用户可以自行定制的CPU,用户可以增加新的外设,增加新的指令,分配外设的地址等。

Nios II的硬件开发就是由用户定制合适的CPU和外设。

(1)SOPC Builder;(2)Cyclone II;(3)ED2开发板;(4)Nios II。

13、SOPC Builder界面分成三个部分,界面左边是组件选择栏,用树型结构列出了SOPC Builder的组件;右边空白处用于加入用户定制___1_____;下方是提示栏,用于显示SOPC Builder的提示信息和警告错误信息。

(1)Nios II系统的组件;(2)目标芯片;(3)用户建立的工程组件;(4)Altera公司系列FPGA。

14、HAL系统库可为与___1_____的程序提供简单的设备驱动接。

(1)硬件通信口;(2)硬件设备;(3)硬件设备描述文件;(4)设备顶层文件。

15、System.h文件是HAL系统库的基础,它提供了关于Nios Ⅱ系统硬件的__4______。

(1)软件描述;(2)NiosⅡIDE调试;(3)描述;(4)HAL的API程序。

16、系统标识__1______是SOPC中的一个简单只读组件。

(1)system ID;(2)IP外围设备;(3)运行程序的ID号;(4)FPGA中的目标芯片。

17、__2___调试方式面向过程,通过各种命令的执行来完成程序的调试和运行。

(1)IDE;(2)SOPC Builder;(3)Quartus II;(4)SDK。

18、通用输入输出端口PIO包括输入、输出和___1_____。

(1)双向三态IO;(2)可编程接口;(3)外围设备接口;(4)可编程外围设备接口。

19、SOPC Builder允许用户修改已经存在的设计,为其添加新的__4______。

(1)用户程序;(2)IP组件;(3)Nios II系统的组件(4)设备和功能。

20、Nios II的硬件开发就是由用户定制合适的____4____。

(1)FPGA器件;(2)FPGA目标芯片;(3)IP软、硬核;(4)CPU和外设。

三、问答题1、Avalon总线是ALTERA公司提出的,用于在基于FPGA片上系统中连接哪些组件或设备的总线结构?答:Avalon总线是ALTERA公司提出的,用于在基于FPGA片上系统中连接片内处理器和片内外设的总线结构。

连接到Avalon总线的设备分为主从设备,并各有其工作方式。

2、说出可以帮助用户完成基于FPGA的DSP系统的设计工具。

使用该设计工具进行DSP 系统开发必须要安装哪两种软件?答:用户首先利用Matlab进行DSP模块设计,然后用DSP Builder将用户设计的DSP模块转换成硬件描述语言(HDL),最终在FPGA上实现。

使用Matlab/DSP Builder进行DSP 系统的开发必须要安装Matlab和DSP Builder软件。

3、在SOPC Builder的组件库中,提供的Nios II系列微处理器有几个成员?通常选用的成员是哪种类型?答:提供了三个成员供选择:①NiosⅡ/e(经济型)成员,具有占用最小逻辑的优化,占用600~700逻辑元件。

②NiosⅡ/f(快速型)成员,具有高性能的优化,占用1400~1800逻辑元件。

③NiosⅡ/s(标准型)成员,在占用逻辑和高性能优化方面的性能居中,占用1200~1400逻辑元件。

、通常选用的成员是NiosⅡ/s(标准型)成员。

4、Nios Ⅱ系统中,需要一块复位电路Reset_Delay实现系统的复位操作,为什么还需要一块锁相环电路SDRAM_PLL产生系统时钟?答:因为需要给外部时钟倍频给cpu5、Avalon总线是由哪个公司提出的?在基于FPGA片上系统中有哪些用途?答:Avalon总线是ALTERA公司提出的,用于在基于FPGA片上系统中连接片内处理器和片内外设的总线结构。

连接到Avalon总线的设备分为主从设备,并各有其工作方式。

6、说出HAL支持的外围设备有哪几种?答:①字符模式设备,包括UART核、JTAG核和LCD16207显示控制器。

②Flash存储器设备,包括通用Flash接口芯片和Altera EPCS串行配置设备控制器。

③文件子系统,包括只读文档系统。

④定时器设备,包括定时器核。

⑤DMA设备,包括DMA控制器核。

⑥以太网设备,包括LABN91C111以太网MAC/CHY控制器。

7、Nios II IDE调试分为几个步骤?分别是哪些步骤?答:Nios II IDE调试分为四个步骤,分别是新建软件工程、编译工程、调试工程和运行工程。

8、锁相环电路SDRAM_PLL在Nios Ⅱ系统中的作用是什么?答:给外部时钟倍频给cpu四、简答题.1、在DE2开发板上,有哪些常用的支持Nios II系统的外部设备?答:在DE2开发板上,支持Nios II系统的外部设备包括SDRAM、SRAM、FLASH、LCD、七段数码管、开光二极管、按钮开关、电平开关、VGA、ISP1362、I²C器件等。

2、简要说明硬件抽象层(HAL)的用途及HAL支持的外围设备。

答:用途:作为支持Nios II处理器系统的软件包,为用户的嵌入式系统上的外围设备提供了与之相匹配的接口程序。

用户不用自己建立或复制HAL文件,也不需要编辑HAL中的任何源代码,使用时只需要在C/C++源程序中指明代表这些接口程序的库函数包含的头文件即可。

支持的外围设备:①字符模式设备,包括UART核、JTAG核和LCD16207显示控制器。

②Flash存储器设备,包括通用Flash接口芯片和Altera EPCS串行配置设备控制器。

③文件子系统,包括只读文档系统。

④定时器设备,包括定时器核。

⑤DMA设备,包括DMA 控制器核。

⑥以太网设备,包括LABN91C111以太网MAC/CHY控制器。

3、生成Nios II硬件系统要完成的工作。

答:生成Nios II核后还要将其下载到目标芯片中,转换成实际的硬件电路并进行调试,验证设计的正确性。

生成Nios II硬件系统需要建立相应的顶层设计文件,顶层设计文件可以用原理图编辑法实现,也可以用HDL文本编辑法实现。

基于DE2开发板的Nios II硬件系统的顶层文件,采用Verilog HDL文本编辑方式实现。

4、试简要说明Nios II的IDE与SDK调试方法的区别。

答:IDE调试方式面向对象,通过直观的软件界面上的按钮来完成调试的各种操作,但编译程序和进入运行程序的时间较长;SDK调试方式是面向过程,通过各种命令的执行来完成程序的调试和运行,但编译程序和进入运行程序的时间较短。

5、简述HAL系统库的构成。

答:HAL可以为与硬件进行通信的程序提供简单的设备驱动接口。